**PRELIMINARY** July 1998

# TP3094 COMBO® **Quad PCM Codec/Filter**

# **General Description**

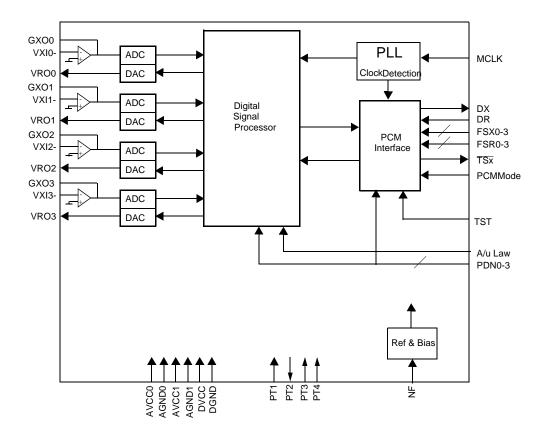

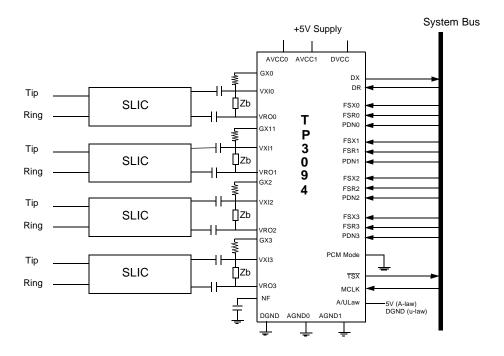

The TP3094 is a monolithic PCM Codec and Filter device implemented using a digital signal processing architecture. It provides four voice channels, combining transmit bandpass and receive low pass channel filters with companding Alaw or m-law PCM encoders and decoders. The device is fabricated using National's advanced CMOS process.

The device includes anti-aliasing filters and sigma-delta converters dedicated to each channel, and by a common signal processing unit which performs all the remaining filtering and processing for the four channels.

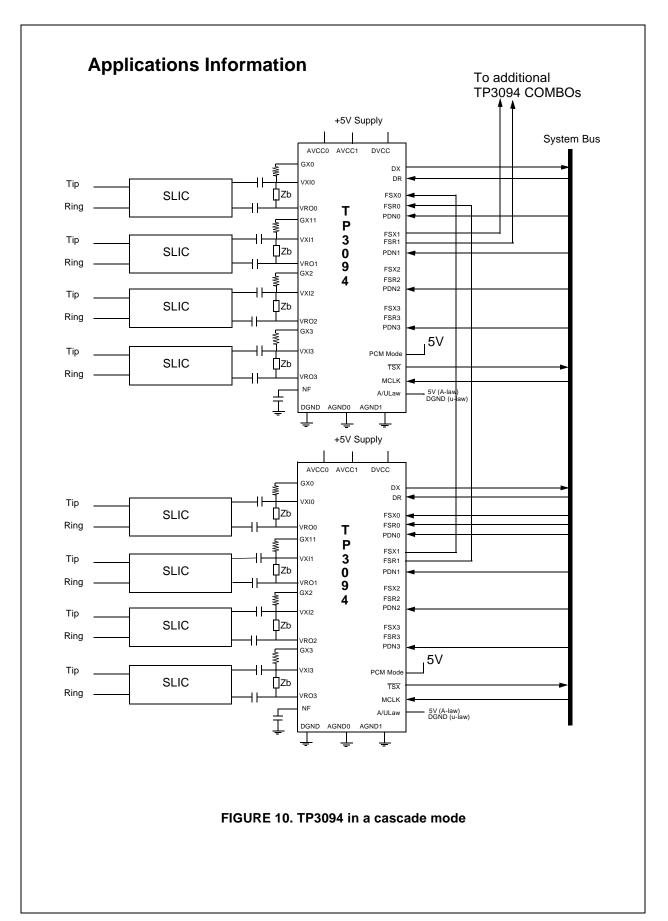

The TP3094 includes a flexible PCM digital interface, which allows the device to be connected to PCM busses of different formats. It can also be connected with other TP3094 devices in a cascade fashion, for a system with up to 128 POTS interfaces (when a 2.048MHz PCM bus is used).

# **Features**

- Handles four voice channels

- Complete Codec and Filter system including:

- Transmit and receive channel filters

- A-law or μ-law companding encoder/decoder

- Power down mode for low power consumption

- · Compatible to standard time division multiplexed PCM bus

- 8 bit mode, frame signal from external reference

- 32 bit mode, internal TSA, with consecutive TS

- Up to 128 channels (32 devices) can be cas-

- Programmable functions (common for all 4 channels):

- A-law or μ-law

- Single MCLK clock, automatically selectable from 8.192MHz, 4.096MHz, 2.048MHz and 1.536/1.544MHz

- Digital and Analog loopback test modes

- Designed for CCITT and LSSGR applications

- Single +5V power supply

- 44 lead PLCC surface mount package

- · Maximize line card circuit density

- Use in Central Office, Loop Carrier, and PBX equipment subscriber line and trunk cards

- Wide operating temperature range -40°C to 85°C

# **Connection Diagram**

See NS Package V44A

COMBO® and TRI-STATE® are registered trademarks of National Semiconductor Corporation

# **Simplified Block Diagram**

FIGURE 1. Simplified block diagram

# Pin Descriptions

# MCLK (input)

Master and PCM bit clock input. Must be either 1.536MHz/1.544MHz, 2.048MHz, 4.096MHz or 8.192MHz. Its value is automatically detected internally on power up with the valid frame sync input.

#### AVCC0, AVCC1

Positive supply pins for the analog circuitry. AVCC0 is for channel 0 and channel 1. AVCC1 is for channel 2 and channel 3.

AVCC0=AVCC1=+5V ±5%. These two pins should be connected together outside the device.

#### AGND0, AGND1

Analog ground. All analog signals are referenced to AGND0 and AGND1. AGND0 is the analog ground for channel 0 and channel 1. AGND1 is the analog ground for channel 2 and channel 3. These two pins should be connected together outside the device.

#### **DVCC**

Positive supply for the digital circuitry. DVCC=+5V ±5%.

#### **DGND**

Digital ground. All logic signals are referenced to DGND. This ground has to be connected to the ground of other digital devices at board level.

# Analog ports

# **VXI0-, VXI1-, VXI2-, VXI3-** (inputs)

Inverting analog inputs of the transmit input amplifiers of channels 0-3. They are referenced to an internal reference voltage of about 2.4V.

# GXO0, GXO1, GXO2, GXO3 (outputs)

Outputs of the transmit input amplifiers of channels 0-3. They are referenced to an internal reference voltage of about 2.4V

# VRO0, VRO1, VRO2, VRO3 (ouputs)

Analog outputs of the receive amplifiers for channels 0-3. They are referenced to an internal reference voltage of about 2.4V

# **PCM Port**

#### DX (ouput)

Transmit PCM data output. Serial PCM data is shifted out on the rising edge of MCLK during the assigned transmit time-slot. Tristated when the assigned transmit time-slot is not active.

# TSx (ouput)

Open drain output that pulses low during the as-

signed transmit time-slots (for all four channels).

# DR (input)

Receive PCM data input. Serial PCM data is shifted into the device on the falling edge of MCLK during the assigned receive time-slot.

# FSX0, FSR0 (inputs)

Transmit and Receive Frame synchronization inputs for channel 0. They identify the beginning of a new frame in the transmit and receive direction. They are 8 KHz logic signals, and must be synchronous to MCLK. Short Frame Sync and Long Frame Sync are both supported.

In 32-bit mode these signals constitute the 8kHz reference for all channels. Only Short Frame Sync is supported in 32-bit mode.

#### FSX1, FSR1 (inputs/outputs)

Transmit and Receive Frame synchronization inputs for channel 1.

In 32-bit mode these pins become outputs and generate a frame sync signal with the last bit of the 32-bit stream, in order to allow to cascade another TP3094 in 32-bit mode. FSX1 is the Transmit Frame output and FSR1 is the Receive Frame output.

# FSX2,FSX3, FSR2,FSR3 (inputs)

Transmit and Receive Frame synchronization inputs for channel 2 and 3. These pins are recommended to be connected to analog ground when in 32-bit mode.

# A/u LAW select (input)

A/u law select. Through this pin either A-law (+5V) or u-law (0V) is selected.

# PDN0-3 (input)

Power Down control signals. Each channel has a dedicated Power Down input. When active high, these pins set the low power mode, shutting down most of the circuitry dedicated to it and reducing the power consumption. The relative analog outputs VROi and GXOi, and the digital output DX are put in high impedance.

#### TST (input)

Test Modes Enable. When active (HIGH), together with the PDNi pins selects one of the available test modes (see the text for a full description of these modes).

# PCMMode (input)

PCM Mode selection. When this signal is LOW (0V), the 8 bit mode is selected and each channel

# Pin Descriptions (continued)

expects its individual transmit and receive frame signal. When it is HIGH, the 32 bit mode is selected; in this mode FSX0 and FSR0 are used as framing signals and the TS are allocated consecutively from these frames, starting from Ch0 to Ch3. In this mode FSX1 and FSR1 become outputs and produce 1 bit long frame signals with the last bit of the 32 bit stream. These Frame signals can be used to cascade another device in 32 bit mode.

#### NF

Noise Filter Pin. For optimal noise rejection a 100nF capacitor must be connected between this pin and the analog ground AGND0.

# PT1, PT2, PT3, PT4 (inputs)

These pins are used by National for internal manufacturing test. They must be connected to digital ground for normal device operation.

#### NC

All NC pins must be connected to nearest analog ground, to reduce the device noise sensitivity.

# **Functional Description**

The TP3094 performs the complete CODEC/filter functions for four voice channels using a digital signal processing architecture. MCLK provides the clock reference to the whole circuitry and the bit clock for the PCM bus. Its value can be either 8.192MHz, 4.096MHz, 2.048MHz or 1.536/1.544MHz, and it is automatically selected internally. The TP3094 handles the conversion between the analog signals on the subscriber line and the PCM data samples on a PCM highway. Digital filters are used to band-limit the voice signals.

The device can work in a 8 bit mode where each channel has an independently selected Time Slot, or in the 32 bit mode, where the four channels use four consecutive Time Slots. The time-division multiplexed PCM data is transferred to the PCM highway through the standard serial PCM bus.

Each channel has its dedicated Power Down input.

#### **Power Initialization**

When power is first applied to the device, poweron reset circuitry initializes the device and places it in the power down state. All non-essential circuits are de-activated. PCM output DX and analog outputs VRO<sub>0-3</sub> are placed in the high impedance state, while FSX1 and FSR1 outputs are held low (in case 32-bit mode is selected). In the power down mode, power consumption is reduced to a minimum, typically 2mW. The device will remain in this state as long as no MCLK is applied and no Frame Signal is applied (just FSX0 and FSR0 in case of 32-bit mode).

For each channel, when the PDN input is not active, MCLK is applied, and a FS (receive or transmit) pulse is running, the device enters the active power up mode. The MCLK frequency is detected with any available FS signal; the clock rate detection may last for up to 4ms, after which the device is ready for powering up. Analog and PCM output signals will be available after a few frames; it will take about 100ms until the first activated channel is fully functional.

The device will only power up when at least one of the FS signals and the MCLK signal are in a valid frequency ratio.

# **Power Down and Reset**

When one channel is in Power Down Mode, the DX output will remain in high impedance state and the input on the DR will be ignored when its FS signal is active; the analog output VRO will be in high impedance.

Each channel will enter the power down mode when at least one of the following conditions occurs

- The PDN signal is active for more than 16 MCLK cycles (and TST is not active at the same time)

- More than 4 pulses of the respective FS are missing.

- MCLK is missing for a 12us.

When the PDN input is active (HIGH) for at least 16 MCLK clock cycles, the channel will go into power down mode and reset its state within a frame sync. The channel will recover from Power Down, after having detected the PDN signal inactive (LOW) for at least 16 MCLK clock cycles and after 1 frame sync pulse.

This power down mode will work only in presence of the master clock at the pin MCLK.

When both the transmit and receive frame sync of a channel are missing the channel will go into Power Down Mode (if only one of them is missing the channel will not go into Power Down). A maximum of 32 frame sync pulses must be missing for power down and the channel will achieve its reset state after 32.5us. The channel will recover from power down, within the time of 4ms after the frame syncs (transmit or receive) will be active.

When the device is in 32-bit mode, missing FSX0, FSR0 for 512us, will force all channels in power down mode.

When the master clock MCLK is missing, all the channels will go into the Global Power Down Mode, with the lowest possible power consumption. The device will recover from this mode, when the clock signal comes back (and at least one frame sync is present), and then the active channels will operate after less than 100ms.

The device will go into the same Global Power Down Mode when all the frame syncs (of all the channels, in case of 8bit mode, the FSX0, FSR0 in case of 32-bit mode) are not present or when all 4 PDN signals are active. The recovery time from this mode for the first active channel is less than 100ms.

# **Transmit Section**

The transmit section input is an operational amplifier, with provision for gain adjustment using two external resistors. Only the inverting input is provided (together with the output), this allows, beside the adjustment of the gain, to implement the echo balance function with external passive components.

The opamp drives the antialiasing input filter, followed by the A to D converter, which provides the digital input to the signal processing unit.

The signal processing unit accepts the signal samples from each channel input stage, performs the necessary decimation and filtering function, PCM compression and provides the eight bit samples to the PCM interface block.

The analog input is dc biased at the value of 2.4V. A DC decoupling is necessary between this input and the SLIC output. The maximum analog signal level, at the op-amp output, is 1.12Vrms.

Maximum recommended transmit gain is 20dB (10x).

# **Receive Section**

This section takes the 8 bit samples from the PCM interface block and performs all the signal

processing functions, such as PCM expansion according to the ALaw or uLaw and signal filtering. Then, for each channel it drives the Digital to Analog converter, through the proper interpolation stages and filters. Finally the signal is filtered and buffered to the output receive pin. The maximum output level voltage on the VRO pins on a load of 5kOhm+100pF is 1.12Vrms.

#### **PCM** Interface

The PCM interface consists of the following signals

- DX, DR transmit and receive digital signals, carrying the pcm samples

- FSX0-3, FSR0-3 transmit and receive frame signals

- TSX output time slots signal, indicating the time slot occupied on the DX by the device

- PCMMode PCM interface select

| PCMMode = HIGH | PCMMode = LOW |  |  |  |  |

|----------------|---------------|--|--|--|--|

| 32 bit         | 8 bit         |  |  |  |  |

A/uLaw - A-law/ u-law select signal

•

TABLE 1. A/uLaw Coding

| A/uLaw = HIGH | A/uLaw = LOW |

|---------------|--------------|

| A-law         | u-law        |

• MCLK - bit clock signal

MCLK is both the system master clock and the PCM bus bit clock, and it is selected internally to be either 8.192MHz, 4.096MHz, 2.048MHz, or 1.536/1.544MHz.

The internal clock selection is perfomed, based on the relative ratio between the frame signals (FS) and the clock signals. For proper functionality all the channel FS must have the same valid rate of 8kHz (giving a valid clock rate). In case one of the frame syncs runs other than 8kHz, the device will not function properly.

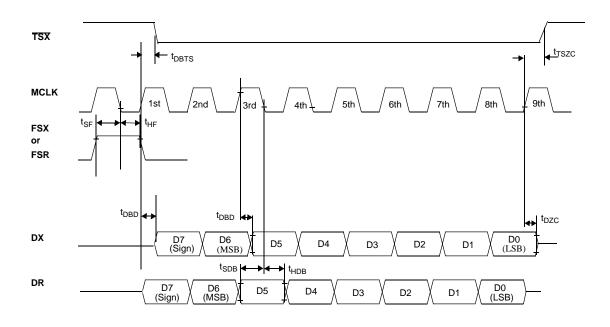

Each bit on DX is clocked out on the rising edges of the bit clock (MCLK), starting from the Most Significant Bit (Sign bit). Each bit on DR is clocked in on the falling edges of the bit clock, starting from the MSB.

The device may operate on to the PCM bus in two modes, selected by the input pin PCMMode; when PCMMode is "0V" the 8bit mode is selected and when PCMMode is "+5V" the 32-bit mode is selected.

# Functional Description (continued)

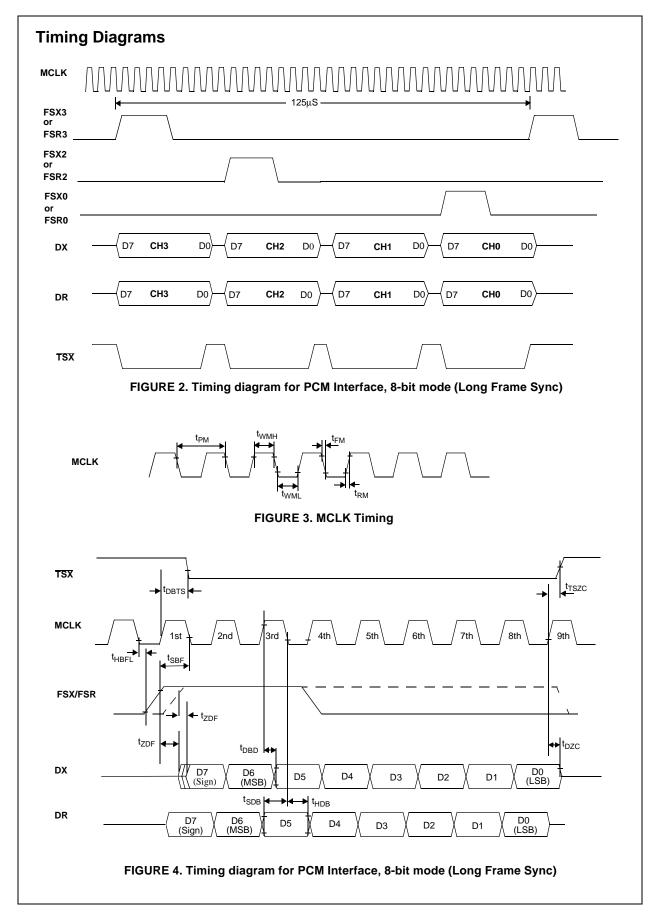

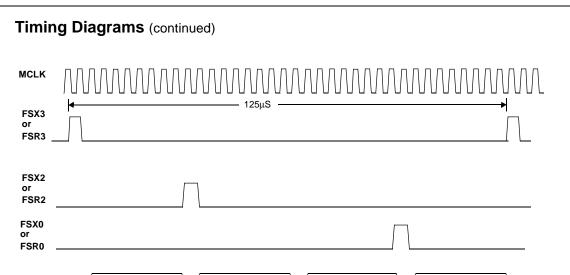

#### 8-bit Mode

In the 8-bit mode, PCM data is transferred independently for each of the four channels. Each channel has its dedicated transmit and receive frame signals, which determine the time-slots to be taken on the PCM bus. Both short sync and long sync frame are supported.

All the channels must have the same FS format (either short or long sync), in case a channel will have a valid frame with different FS format, the device will not function properly.

In the short sync, the frame signals must be one bit long; with FSX high during a falling edge of MCLK, the next rising edge of MCLK enables the DX tristate output buffer, which will output the sign bit. The following 7 rising edges clock out the remaining 7 bits, and the next rising edge (9th) disables the DX output. With FSR high during a falling edge of MCLK, the next falling edge of MCLK latches in the sign bit. The following 7 negative edges of MCLK will then latch the remaining 7 bit of the incoming byte.

In the long sync frame, the Frame signals must be at least three bits long. The DX output buffer is enabled with the rising edge of FSX or on the rising edge of MCLK, whichever comes later, and the first bit (sign) is clocked out. The following 7 rising edges of MLCK clock out the remaining 7 bits. The DX output is disabled by the 9th rising edge of MCLK. A rising edge on FSR will cause the PCM data at DR to be latched in on the next falling edges of MCLK.

For timing diagrams refer to Fig.2, Fig.4, Fig.5 and Fig.6.

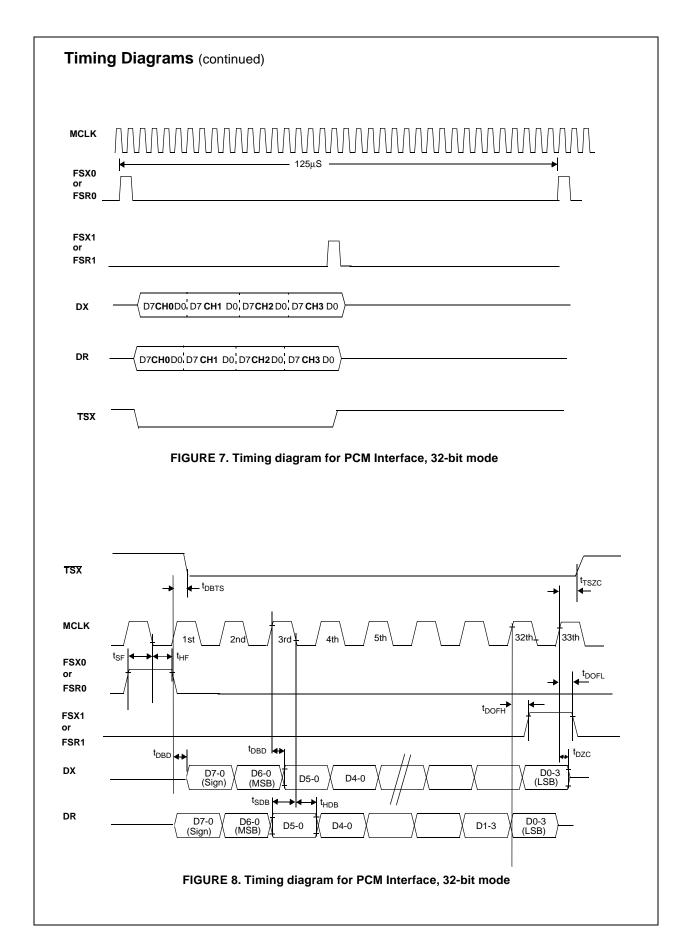

#### 32-bit Mode

In the 32-bit mode, the four PCM data bytes of the four channels are treated as a single 32-bit data word. The PCM transfer is started by the positive pulses on the transmit or receive frame sync (FSX0, FSR0) inputs. The following 32 negative edges of MCLK will then latch the input PCM data at DR, for all 4 channel starting from channel 0; while the positive edges will clock out the transmit PCM data at DX, from channel 0 to channel 3. In this mode the pins FSX1 and FSR1 become the frame signal carry-out signals, providing a single-bit-long frame pulse during the last bit of the 32-bit stream and allowing another TP3094 to be connected in 32-bit mode.

In case any channel is powered down (through the PDN pin) during its assigned time slot the DX pin will be set in tristate and the DR signal will be ignored.

In case all the channels are placed in power down, the device will still generate the FS carry output on FSX1, FSR1. For timing diagrams refer to Fig.7 and Fig.8.

# **Test Modes**

The TP3094 includes the following test modes

- digital loopback

- analog loopback

- DC conversion

These modes can be programmed per channel or for all 4 channels simultaneously.

The device is programmed into any test mode by exercising the pins TST, PDN0, PDN1, PDN2, PDN3 together. The signals to this pins must be stable for at least 16 MCLK cycles before the device enters any selected test mode. When exiting the test mode, the PDN must return to the previous state to resume the original operating state. During any test mode (TST=1), it will not be possible to change the PU/PD state for any channel not involved in the test mode configuration (e.g. not in test mode). The channel(s) under test must be placed in power up prior the test mode selection, in case left in power down, any programmed test mode will not be operational.

When the device exits the test mode, normal operation will return, and the PU/PD programmability will be available, by the state of the PDN signals.

The programming of the test modes is according to the table below.

The digital loopback is a bit true feedback from the PCM highway to the PCM highway, performed exactly at the PCM internal interface. Each byte is looped back from RX to TX on the programmed time slot (FS). The analog output is forced to 0Vac level (typically 2.4Vdc), with low output impedance.

The analog loopback is performed from the output of the D/A converter (before the output amplifier) and the input of the A/D, so the RX signal is looped back towards the TX direction, through the device. The analog output is at 0Vac level, with high output impedance.

In the DC conversion mode, the channel under test is programmed to transfer any DC signal (within the available range) in the TX direction, from the analog GXO to the DX digital output, by

# Functional Description (continued)

bypassing the low frequency filter.

| Test Modes                      | TST | PDN0 | PDN1 | PDN2 | PDN3 | Description                |

|---------------------------------|-----|------|------|------|------|----------------------------|

| Normal Operation                | 0   | Х    | Х    | Х    | Х    |                            |

| Single Channel Digital Loopback | 1   | 1    | 1    | A0   | A1   | Ch. select with PDN2, PDN3 |

| Single Channel Analog Loopback  | 1   | 0    | 1    | A0   | A1   | Ch. select with PDN2, PDN3 |

| Single Channel DC Conversion    | 1   | 1    | 0    | A0   | A1   | Ch. select with PDN2, PDN3 |

| 4 Channels Digital Loopback     | 1   | 0    | 0    | 0    | 0    |                            |

| 4 Channels Analog Loopback      | 1   | 0    | 0    | 0    | 1    |                            |

| 4 Channels DC Conversion        | 1   | 0    | 0    | 1    | 0    |                            |

| Invalid States                  | 1   | 0    | 0    | 1    | 1    |                            |

Where A0, A1 select the channel under test, according to the following table

| A0 | A1 | Channel Selected |

|----|----|------------------|

| 0  | 0  | Channel 0        |

| 1  | 0  | Channel 1        |

| 0  | 1  | Channel 2        |

| 1  | 1  | Channel 3        |

FIGURE 5. Timing diagram for PCM Interface, 8-bit mode (Short Frame Sync)

FIGURE 6. Timing diagram for PCM Interface, 8-bit mode (Short Frame Sync) for each channel

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

V<sub>CC</sub> to DGND

V<sub>CC</sub> +0.3V to DGND -0.3V V<sub>CC</sub> +0.3V to AGND-0.3V -65°C to +150°C Voltage at any digital inputs or outputs Voltage at any analog inputs or outputs

Storage temperature range

260°C Lead temperature(Soldering, 10 Sec) ESD (human body model) 2000 V Latch-up immunity on any pin 200 mA

# **Electrical Characteristics**

Unless otherwise noted, limits printed in **bold** characters are guaranteed for  $V_{CC}(all\ supplies)=5.0V\pm5\%$ , DGND=AGND=0V, T<sub>A</sub>=-40°C to 85°C by correlation with 100% electrical testing at T<sub>A</sub>=25°C. All other limits are assured by correlation with other production tests and/or product design and characterization. All digital signals are referenced to DGND, and all analog signals are referenced to AGND. Typical are specified at V<sub>CC</sub>=+5V,  $T_A=25$ °C.

# **Digital Interface**

| Symbol          | Parameter                              | Conditions                                                             | Min        | Тур | Max | Units  |

|-----------------|----------------------------------------|------------------------------------------------------------------------|------------|-----|-----|--------|

| V <sub>IL</sub> | Input low voltage                      | All digital inputs                                                     |            |     | 0.8 | V      |

| V <sub>IH</sub> | Input high voltage                     | All digital inputs                                                     | 2.2        |     |     | V      |

| V <sub>OL</sub> | Output low voltage                     | IL=2mA                                                                 |            |     | 0.4 | V      |

| V <sub>OH</sub> | Output high voltage                    | IL=-2mA<br>IL=-100uA                                                   | 2.4<br>3.5 |     |     | V<br>V |

| I <sub>IL</sub> | Input low current                      | DGND <v<sub>IN<v<sub>IL, all digital inputs</v<sub></v<sub>            | -10        |     | 10  | μΑ     |

| I <sub>IH</sub> | Input high current                     | V <sub>IH</sub> <v<sub>IN<v<sub>CC, all digital inputs</v<sub></v<sub> | -10        |     | 10  | μΑ     |

| I <sub>OZ</sub> | Output current in high impedance state | DGND <v<sub>O<v<sub>CC (DX)</v<sub></v<sub>                            | -10        |     | 10  | μА     |

| Ci              | Input Capacitance                      |                                                                        |            |     | 10  | pF     |

# **Analog Interface**

| I <sub>XI</sub>   | Input leakage current                    | 1V <v<sub>XI&lt;4V, all analog inputs in</v<sub> | -200  |       | 200  | nA   |

|-------------------|------------------------------------------|--------------------------------------------------|-------|-------|------|------|

|                   |                                          | Power UP mode                                    |       |       |      |      |

| $R_{XI}$          | Input resistance                         | 1V <v<sub>XI&lt;4V, all analog inputs</v<sub>    | 10    |       |      | МΩ   |

| C <sub>XI</sub>   | Input capacitance                        | 1V <v<sub>XI&lt;4V, all analog inputs</v<sub>    |       | 10    |      | pF   |

| V <sub>CMXI</sub> | Transmit input common mode voltage range |                                                  | -10%  | 2.375 | +10% | V    |

| V <sub>CMXO</sub> | Receive input common mode voltage range  |                                                  | -10%  | 2.375 | +10% | V    |

| R <sub>RO</sub>   | Output resistance                        | All analog outputs                               |       | 5     | 10   | Ω    |

| R <sub>ROZ</sub>  | Output resistance in PDN                 |                                                  | 2000  |       |      | Ω    |

| RL <sub>RO</sub>  | Load resistance                          | 0.7V <v<sub>RO&lt;4.1V, VROi</v<sub>             | 5000  |       |      | Ω    |

| CL <sub>RO</sub>  | Load capacitance                         | VRO                                              |       |       | 100  | pF   |

| A <sub>V</sub> XA | Voltage Gain                             | VXI to GXO,RL on GXO>10kΩ                        | 5000  |       |      | V/V  |

| F <sub>U</sub> XA | Unity Gain Bandwidth                     |                                                  | 1     | 2     |      | MHz  |

| RL <sub>GXO</sub> | Load resistance                          | 0.7V <v<sub>GX&lt;4.1V, GXOi</v<sub>             | 10000 |       |      | Ω    |

| CL <sub>GXO</sub> | Load capacitance                         | GXO                                              |       |       | 50   | pF   |

| V <sub>RO</sub>   | RX output drive level                    | R <sub>L</sub> =5000Ω                            | 1.12  |       |      | Vrms |

# **Electrical Characteristics** (continued)

| Symbol            | Parameter                                    | Conditions                                                         | Min | Тур | Max | Units |

|-------------------|----------------------------------------------|--------------------------------------------------------------------|-----|-----|-----|-------|

| Power Dissi       | ipation                                      |                                                                    |     |     |     |       |

| I <sub>CC</sub> 0 | Power down current (all channels down)       | Measured after having first achieved power-up state. MCLK=2.048MHz |     | 0.9 | 1.5 | mA    |

| I <sub>CC</sub> 1 | Power up active current (all channel active) | No load, MCLK=2.048MHz                                             |     | 35  | 50  | mA    |

# **Amplitude Response**

|                    | Absolute Levels                                                                    | Nominal 0dBm0 level is 0dBm at the analog inputs/outputs                                                                                                       |                                | 0.7746 |                                                           | V <sub>rms</sub>                             |

|--------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------|-----------------------------------------------------------|----------------------------------------------|

| t <sub>max</sub>   | Virtual decision value defined per ITU G.711                                       | Max overload level<br>3.17dBm0 (μ-law)<br>3.14dBm0 (A-law)                                                                                                     |                                |        | 1.116<br>1.112                                            | V <sub>rms</sub>                             |

| G <sub>XA</sub>    | Transmit gain, absolute                                                            | T <sub>A</sub> =25°C, V <sub>CC</sub> =5V,<br>Input at VXI=0dBm0 at<br>1015.625Hz                                                                              | -0.15                          |        | 0.15                                                      | dB                                           |

| G <sub>XAT/V</sub> | Cumulative Transmit<br>gain Variation with sup-<br>plies and temperature<br>ranges | $T_A$ =0°C to 70°C, $V_{CC}$ =5 $V$ ±5%, TA=-40°C to +85°C, $V_{CC}$ =5 $V$ ±5% Input at GXO=0dBm0 at 1015.625Hz                                               | -0.2<br>-0.3                   |        | 0.2                                                       | dB<br>dB                                     |

| G <sub>XR</sub>    | Transmit gain, relative to $G_{XA}$                                                | f=16Hz<br>f=50Hz<br>f=60Hz<br>f=200Hz<br>f=300-3000Hz<br>f=3300Hz<br>f=3400Hz<br>f=4000Hz<br>f=4.6KHz and up (Note 2),<br>measure response from 0 to<br>4000Hz | -1.8<br>-0.15<br>-0.35<br>-0.7 |        | -35<br>-30<br>-30<br>0<br>0.15<br>0.15<br>0<br>-14<br>-32 | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| G <sub>XAL</sub>   | Transmit gain variation with level                                                 | Sinusoidal test method, reference level = -10dBm0 at VXI GXO=-40dBm0 to +3dBm0 GXO=-50dBm0 to -40dBm0 GXO=-55dBm0 to -50dBm0                                   | -0.2<br>-0.4<br>-1.0           |        | 0.2<br>0.4<br>1.0                                         | dB<br>dB<br>dB                               |

| G <sub>RA</sub>    | Receive gain, absolute                                                             | T <sub>A</sub> =25°C, V <sub>CC</sub> =5V±5%<br>Input PCM level at DR=0dBm0 at<br>1015.625Hz                                                                   | -0.15                          |        | 0.15                                                      | dB                                           |

| G <sub>RAT/V</sub> | Cumulative Receive gain<br>Variation with supplies<br>and temperature ranges       | $T_A$ =0°C to 70°C, $V_{CC}$ =5V±5%, $T_A$ =-40°C to 85°C, $V_{CC}$ =5V±5%, Input PCM level at DR=0dBm0 at 1015.625Hz                                          | -0.2<br>-0.3                   |        | 0.2                                                       | dB                                           |

| G <sub>RR</sub>    | Receive gain, relative to $G_{RA}$                                                 | f=0-3000Hz<br>f=3300Hz<br>f=3400Hz<br>f=4000Hz                                                                                                                 | -0.15<br>-0.35<br>-0.7         |        | 0.15<br>0.15<br>0<br>-14                                  | dB<br>dB<br>dB<br>dB                         |

# **Electrical Characteristics** (continued)

| Symbol           | Parameter                         | Conditions                   | Min  | Тур | Max | Units |

|------------------|-----------------------------------|------------------------------|------|-----|-----|-------|

|                  |                                   |                              |      |     |     |       |

| G <sub>RAL</sub> | Receive gain variation with level | Sinusoidal test method,      |      |     |     |       |

|                  |                                   | PCM level=-40dBm0 to +3dBm0  | -0.2 |     | 0.2 | dB    |

|                  |                                   | PCM Level=-50dBm0 to -40dBm0 | -0.4 |     | 0.4 | dB    |

|                  |                                   | PCM Level=-55dBm0 to -50dBm0 | -1.0 |     | 1.0 | dB    |

Note 2: Measure voiceband image signal, stimulus signal level is -25dBm0.

# **Distortion**

| STD <sub>XP</sub> | Transmit signal to total distortion  | Sinusoidal test method, A-law (psophometric filter), u-Law (C message filter), FSX=FSR, f <sub>XI</sub> =1015.625Hz GXO=+3dBm0 GXO=0 to -30dBm0 GXO= -40dBm0 GXO= -45dBm0 GXO= -50dBm0 GXO= -55dBm0 GXO= -55dBm0                    | 33<br>36<br>29<br>25<br>20<br>14 |                   | dB<br>dB<br>dB<br>dB<br>dB |

|-------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------|----------------------------|

| SFD <sub>X</sub>  | Transmit single frequency distortion | Sinusoidal test method, PCM code for all channels equals to positive zero, FSX=FSR, f <sub>XI</sub> =1015.625Hz, GXO=0dBm                                                                                                           |                                  | -46               | dB                         |

| STD <sub>RP</sub> | Receive signal to total distortion   | Sinusoidal test method, A-law, (psophometric filter), u-Law (C message filter), FSX=FSR, f=1015.625Hz, PCM level=+3dBm0 PCM level=-40dBm0 PCM level=-40dBm0 PCM level=-45dBm0 PCM level=-50dBm0 PCM level=-50dBm0 PCM level=-55dBm0 | 33<br>36<br>29<br>25<br>20<br>15 |                   | dB<br>dB<br>dB<br>dB       |

| SFD <sub>R</sub>  | Receive single frequency distortion  | Sinusoidal test method, PCM code for all channels equals to 0dBm0, FSX=FSR, f=1015.625Hz, GXO=0Vrms                                                                                                                                 |                                  | -46               | dB                         |

| SOS <sub>RS</sub> | Receive spurious out of band signals | Single frequency, PCM code for<br>all channels equals 0 dBm0,<br>300Hz-3.4KHz, FSX=FSR,<br>GXO=0Vrms<br>f=4.6KHz-7.6KHz<br>f=7.6KHz-8.4KHz<br>f=8.4KHz-100KHz                                                                       |                                  | -30<br>-40<br>-30 | dB<br>dB<br>dB             |

| Symbol            | Parameter                                   | Conditions                                                                                                                     | Min        | Тур                            | Max                      | Units                      |

|-------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------|--------------------------|----------------------------|

| Envelope de       | elay distortion                             |                                                                                                                                |            |                                |                          |                            |

| D <sub>XA</sub>   | Transmit delay, absolute                    | f=1400Hz,                                                                                                                      |            | 275                            | 330                      | μS                         |

| D <sub>XR</sub>   | Transmit delay, relative to D <sub>XA</sub> | GXO=-10dBm0<br>f=500-600Hz<br>f=600-1000Hz<br>f=1000-2600Hz<br>f=2600-2800Hz                                                   |            | 150<br>85<br>50<br>80          | 220<br>145<br>100<br>140 | μs<br>μs<br>μs<br>μs       |

| D <sub>RA</sub>   | Receive delay, absolute                     | f=1400Hz,                                                                                                                      |            | 112                            | 220                      | μS                         |

| D <sub>RR</sub>   | Receive delay, relative to D <sub>RA</sub>  | PCM level=-10dBm0<br>f=500-600Hz<br>f=600-1000Hz<br>f=1000-2600Hz<br>f=2600-2800Hz<br>f=2800-3000Hz                            | -40<br>-40 | -15<br>-10<br>75<br>105<br>145 | 90<br>125<br>175         | μs<br>μs<br>μs<br>μs<br>μs |

| Noise             |                                             |                                                                                                                                |            |                                |                          |                            |

| N <sub>XP</sub>   | Transmit Idle channel noise, A-law          | Psophometric weighted, PCM code for all channels equals to positive zero, FSX=FSR, GXO=0Vrms                                   |            | -73                            | -69                      | dBm0p                      |

| N <sub>XC</sub>   | Transmit Idle channel noise, μ-law          | C-message weighted, PCM code<br>for all channels equals to alternat-<br>ing positive and negative zeros,<br>FSX=FSR, GXO=0Vrms |            | 12                             | 16                       | dBrnC                      |

| N <sub>RP</sub>   | Receive Idle channel<br>noise, A-law        | Psophometric weighted, PCM code for all channels equals to positive zero, FSX=FSR, GXO=0Vrms                                   |            | -83                            | -79                      | dBm0p                      |

| N <sub>RC</sub>   | Receive Idle channel noise, μ-law           | C-message weighted, PCM code<br>for all channels equals to alternat-<br>ing positive and negative zeros,<br>FSX=FSR, GXO=0Vrms |            | 7                              | 11                       | dBrnC                      |

| N <sub>XR</sub>   | Analog to Analog Noise                      | DX connected to DR, f=0-100kHz<br>FSX=FSR, GXO=0Vrms                                                                           |            | -70                            | -53                      | dBm0                       |

| Dowar supp        | oly rejection                               |                                                                                                                                |            |                                |                          |                            |

| PPSR <sub>X</sub> | Positive power supply                       | PCM code for all channels equals                                                                                               |            |                                |                          |                            |

| ΙΙΟΝΧ             | rejection, transmit                         | to positive zero, A-law, FSX=FSR, GXO=0Vrms, V <sub>CC</sub> =5.0V+100mV <sub>rms</sub> f=0-4000Hz f=4.6KHz-25KHz              | 40<br>40   | 45<br>45                       |                          | dB<br>dB                   |

| PPSR <sub>R</sub> | Positive power supply rejection, receive    | PCM code for all channels equals to positive zero, A-law, FSX=FSR, GXO=0Vrms, V <sub>CC</sub> =5.0V+100mV <sub>rms</sub>       |            |                                |                          |                            |

f=0-4000Hz

f=4.6KHz-25KHz

dB dB

45 45

40

40

# **Electrical Characteristics** (continued)

| Symbol            | Parameter                                                         | Conditions                                                                                                                                                           | Min | Тур | Max | Units |

|-------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Crosstalk         |                                                                   |                                                                                                                                                                      |     |     |     |       |

| CT <sub>R-X</sub> | Receive to transmit<br>crosstalk (Intra-channel<br>Crosstalk)     | PCM code for stimulated channel equals to 0dBm0, 300Hz-3.4KHz, PCM code for all other channels equals to positive zero, FSX=FSR, Measure PCM response.               |     | -80 | -75 | dB    |

| CTFE <sub>X</sub> | Far end crosstalk with analog stimulus (Interchannel crosstalk)   | PCM code for all channels equals<br>to positive zero, FSX=FSR,<br>Stimulating signal GXO=0dBm0,<br>f=750Hz<br>All other channels GXO=0V <sub>rms</sub>               |     | -80 | -73 | dB    |

| CTNE <sub>X</sub> | Near end crosstalk with digital stimulus (Interchannel crosstalk) | PCM code for stimulated channel equals to 0dBm0, f=750Hz, PCM code for all other channels equals to positive zero, FSX=FSR, All other channels GXO=0V <sub>rms</sub> |     | -80 | -73 | dB    |

| CT <sub>X-R</sub> | Transmit to receive crosstalk (Intra-channel crosstalk)           | PCM code for all channels equals to positive zero, FSX=FSR, Stimulating signal GXO=0dBm0, 300Hz-3.4KHz, all other channels GXO=0V <sub>rms</sub> ,                   |     | -80 | -75 | dB    |

| CTFE <sub>R</sub> | Far end crosstalk with digital stimulus (Interchannel crosstalk)  | PCM code for stimulated channel equals to 0dBm0, f=750Hz, PCM code for all other channels equals to positive zero, FSX=FSR, All other channels GXO=0V <sub>rms</sub> |     | -80 | -76 | dB    |

| CTNE <sub>X</sub> | Near end crosstalk with analog stimulus (Interchannel crosstalk)  | PCM code for all channels equals<br>to positive zero, FSX=FSR,<br>Stimulating signal GXO=0dBm0,<br>f=750Hz<br>All other channels GXO=0V <sub>rms</sub>               |     | -80 | -76 | dB    |

# **Timing Specifications**

| Symbol Paramete | Conditions | Min | Тур | Max | Units |

|-----------------|------------|-----|-----|-----|-------|

|-----------------|------------|-----|-----|-----|-------|

# **Clock and Data Timing**

All timing parameters are measured at  $V_{OH}$ =2.0V and  $V_{OL}$ =0.7V

| 1/t <sub>PM</sub>  | Frequency of MCLK                    | OH THE SHOP OF                     |                    | 1.536 |    | MHz |

|--------------------|--------------------------------------|------------------------------------|--------------------|-------|----|-----|

|                    |                                      |                                    |                    | 1.544 |    | MHz |

|                    |                                      |                                    |                    | 2.048 |    | MHz |

|                    |                                      |                                    |                    | 4.096 |    | MHz |

|                    |                                      |                                    |                    | 8.192 |    | MHz |

| DC <sub>MCLK</sub> | MCLK Duty Cycle                      |                                    | 40                 |       | 60 | %   |

| t <sub>RM</sub>    | Rise time of MCLK                    |                                    |                    |       | 10 | ns  |

| t <sub>FM</sub>    | Fall time of MCLK                    |                                    |                    |       | 10 | ns  |

| t <sub>SDB</sub>   | Setup time DR valid to MCLK low      |                                    | 20                 |       |    | ns  |

| t <sub>HDB</sub>   | Hold time DR valid from MCLK low     |                                    | 20                 |       |    | ns  |

| t <sub>DBD</sub>   | Delay from MCLK high to DX valid     | C <sub>L</sub> =100pF+2LSTTL loads | 0                  |       | 35 | ns  |

| t <sub>DZC</sub>   | Delay from MCLK high to DX disabled  | C <sub>L</sub> =100pF+2LSTTL loads |                    |       | 20 | ns  |

| t <sub>TSZC</sub>  | Delay from MCLK high to TSX disabled | C <sub>L</sub> =100pF+2LSTTL loads |                    |       | 20 | ns  |

| t <sub>DBTS</sub>  | Delay time to TS <sub>X</sub> low    | $C_L = 0pF \text{ to } 150pF$      |                    |       | 50 | ns  |

| t <sub>PDN</sub>   | PDN persistence                      |                                    | 16xt <sub>PM</sub> |       |    |     |

| t <sub>SF</sub>    | Set-up Time from FS                  | Short Frame Sync Pulse             | 20                 |       |    | ns  |

|                    | to MCLK Low                          |                                    |                    |       |    |     |

| t <sub>HF</sub>    | Hold Time from MCLK                  | Short Frame Sync Pulse             | 20                 |       |    | ns  |

|                    | Low to FS Low                        | ,                                  |                    |       |    |     |

# **Long Frame Timing**

| Symbol            | Parameter           | Conditions           | Min | Тур | Max | Units |

|-------------------|---------------------|----------------------|-----|-----|-----|-------|

| t <sub>HBFL</sub> | Holding time from   | Long Frame Only      | 10  |     |     | ns    |

|                   | Clock to Frame Sync |                      |     |     |     |       |

| t <sub>SBF</sub>  | Set-up time from    | Long Frame Only      | 35  |     |     | ns    |

|                   | Frame Sync to Clock |                      |     |     |     |       |

|                   | low                 |                      |     |     |     |       |

| t <sub>ZDF</sub>  | Delay time Valid    | $C_L = 0pF$ to 150pF |     |     | 50  | ns    |

|                   | Data from FS or     |                      |     |     |     |       |

|                   | MCLK, whichever     |                      |     |     |     |       |

|                   | comes later         |                      |     |     |     |       |

Note: when measuring signals going to TRI-STATE®, the timing delay is measured when the signal is 10% away from the starting level.

# **Applications Information**

FIGURE 9. Typical application in a non cascaded mode

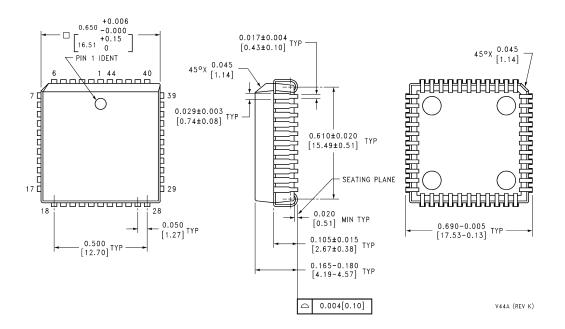

# Physical Dimensions inches (millimeters) unless otherwise noted

# 44-Lead Molded Plastic Chip Carrier (PLCC) Order Number TP3094V NS Package Number V44A

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be

- reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or ef-

National Semiconductor Corporation

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com National Semiconductor Europe

Fax: (+49) 0-180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: (+49) 0-180-530 85 85

English Tel: (+49) 0-180-532 78 32

National Semiconductor Asia Pacific Customer Response Group Tel: 65-254-4466

Fax: 65-250-4466

Email: sea.support@nsc.com

National Semiconductor Japan Ltd. Tel: 81-3-5620-6175

Tel: 81-3-5620-6175 Fax: 81-3-5620-6179