# PCM16C00 Configurable Multiple Function PCMCIA Interface Chip

## **General Description**

National's PCM16C00 acts as a standard interface between the PCMCIA bus and card-side local bus for I/O and memory PCMCIA cards. This device allows the card designer to focus on the design of the dual I/O functions while providing a one-chip solution for I/O memory window control, concurrent interrupt control, EEPROM interfacing, and power management. In addition to being configurable to interface to any two ISA compatible I/O functions, the PCM16C00 supports logic necessary to simplify a design that uses the National DP83902A ST-NIC Ethernet Controller as one of the functions

The PCM16C00 is fully compliant with PCMCIA version 2.1 and is compatible with serial 4-kbit and 16-kbit EEPROMs with 8-bit and 16-bit organizations that use the MICROW-IRE™ protocol. This multi-function interface IC allows the system software to setup I/O decode windows and provides the Attribute memory decode control that allow attribute read and write data transfers.

## **Features**

- PCMCIA Bus Interface

- Compliant with multi-function extension to PCMCIA Standards 3.X

- PCMCIA version 2.1 configuration registers

- Serial EEPROM interface compatible with MICROWIRE EEPROM protocol

- 2-kbyte on chip RAM for attribute memory which shadows the CIS and is used for loading static registers

- Address decoding and control for 2 I/O functions

- Logic to support any two interrupt capable I/O functions on a PCMCIA card

- Power management and clock control

- Programmable arbitration unit for PCMCIA host and two functions

- Common memory logic

- National DP83902A Ethernet LAN support logic

- 4 Bit, direction programmable, generic digital port

- ISA-like interface to card function

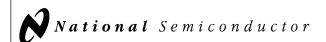

## 1.0 System Diagram

FIGURE 1-1

TRI-STATE® is a registered trademark of National Semiconductor Corporation. MICROWIRE™ is a trademark of National Semiconductor Corporation.

# **Table of Contents**

| GENERAL DESCRIPTION AND PRODUCT FEATURES                    |

|-------------------------------------------------------------|

| 1.0 SYSTEM DIAGRAM                                          |

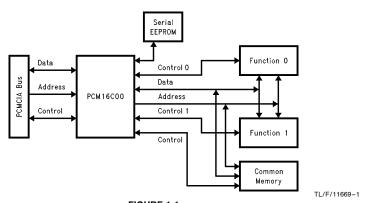

| 2.0 CONNECTION DIAGRAM                                      |

| 3.0 PINOUT DESCRIPTION AND DETAILED TABLES                  |

| 4.0 BLOCK DIAGRAM                                           |

| 5.0 FUNCTIONAL DESCRIPTION8                                 |

| 5.1 Address Maps8                                           |

| 5.1.1 Attribute Memory Addressing8                          |

| 5.1.2 I/O Memory Addressing                                 |

| 5.1.3 Common Memory Addressing                              |

| 5.2 Registers9                                              |

| 5.2.1 PCMCIA Registers                                      |

| 5.2.2 PCM16C00 Specific Registers                           |

| 5.2.2.1 Standard Mode Register Set                          |

| 5.2.2.2 LAN (National ST-NIC) Mode Register Set             |

| 5.3 Logic Descriptions                                      |

| 5.3.1 I/O Card Interface Logic for PCMCIA Host I/O Accesses |

| 5.3.2 EEPROM Interface                                      |

| 5.3.2.1 CIS Data Security                                   |

| 5.3.3 Power Management                                      |

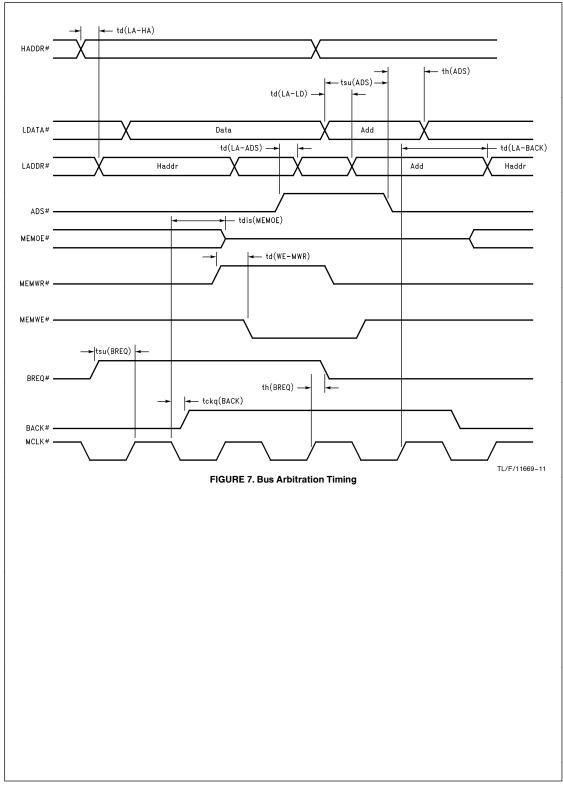

| 5.3.4 Bus Arbitration                                       |

| 5.3.5 Common Memory Management                              |

| 6.0 OPERATIONAL MODES                                       |

| 6.1 Initial Setup (reset) and Configuration                 |

| 6.2 Reset Conditions                                        |

| 6.3 Interrupt Control                                       |

| 6.4 Functional Concurrency                                  |

| 6.5 16-Bit/8-Bit Operation                                  |

| 6.6 Special Testability Modes                               |

| SOFTWARE                                                    |

| ABSOLUTE MAXIMUM RATINGS                                    |

| RECOMMENDED OPERATING CONDITIONS                            |

| RELIABILITY REQUIREMENTS                                    |

| DC ELECTRICAL CHARACTERISTICS                               |

| TYPICAL APPLICATIONS                                        |

| REFERENCES                                                  |

# 3.0 Pinout Description

**TABLE 3-1. PCMCIA Host-Side Pins**

| Pin<br>Name | Pin<br>Type | Pin<br>No.                                              | Level<br>Compatibility | Internal<br>Resistor     | Description                                                                                                                                                                                                               |

|-------------|-------------|---------------------------------------------------------|------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDATA(15:0) | 1/0         | 112–109,<br>107, 74–72,<br>102–106,<br>76, 78, 79       | TTL 6 mA               | > 100k to GND            | PCMCIA Host Data Bus.                                                                                                                                                                                                     |

| HADDR(15:0) | l           | 90, 93, 94,<br>89, 98, 100,<br>96, 95, 88,<br>87, 85–80 | TTL                    | > 100k to GND            | PCMCIA Host Address Bus.                                                                                                                                                                                                  |

| HOE#        | I           | 99                                                      | TTL                    | >100k to V <sub>CC</sub> | PCMCIA Host uses this pin to read common or attribute memory space.                                                                                                                                                       |

| HWE#        | I           | 92                                                      | TTL                    | >100k to V <sub>CC</sub> | PCMCIA Host uses this pin to write common or attribute memory space.                                                                                                                                                      |

| HIORD#      | I           | 115                                                     | TTL                    | >100k to V <sub>CC</sub> | PCMCIA Host uses this pin to read I/O memory space.                                                                                                                                                                       |

| HIOWR#      | I           | 116                                                     | TTL                    | >100k to V <sub>CC</sub> | PCMCIA Host uses this pin to write I/O memory space.                                                                                                                                                                      |

| IREQ#       | 0           | 91                                                      | CMOS 6 mA              |                          | Interrupt Request signal to PCMCIA Host.                                                                                                                                                                                  |

| HWAIT#      | 0           | 66                                                      | CMOS 6 mA              |                          | This pin allows the PCM16C00 to insert wait states in a PCMCIA transaction.                                                                                                                                               |

| IOIS16#     | 0           | 75                                                      | CMOS 6 mA              |                          | Low indicates this I/O access to the card is capable of 16-bit access. Function 0 and 1 may use their IOCS16(1:0) # respectively to control this signal and inform the host if a 16-bit access to the target is feasible. |

| INPACK#     | 0           | 67                                                      | CMOS 6 mA              |                          | Signals a valid I/O read.                                                                                                                                                                                                 |

| CE1#        | ı           | 101                                                     | TTL                    | >100k to V <sub>CC</sub> | Indicates even address byte. Odd addresses are not released. CE1# and CE2# assertion encodings are specified by the PCMCIA Specification.                                                                                 |

| CE2#        | I           | 114                                                     | TTL                    | >100k to V <sub>CC</sub> | Indicates odd addressing only. CE1# and CE2# assertion encodings are specified by the PCMCIA Specification.                                                                                                               |

| REG#        | I           | 68                                                      | TTL                    | >100k to V <sub>CC</sub> | Indicates access to attribute memory space or I/O address space. REG# must be high to access common memory space.                                                                                                         |

| RESET       | ı           | 65                                                      | TTL Schmitt            | >100k to V <sub>CC</sub> | Asynchronously resets the PCM16C00.                                                                                                                                                                                       |

| SPKR#       | 0           | 70                                                      | CMOS 6 mA              |                          | If Audio bits are set in the Card Configuration Status Register and in either of the Function Configuration Status Registers 0,1, then SPKR# is invert of SPK IN pin, else SPKR# is high.                                 |

| STSCHG#     | 0           | 71                                                      | CMOS 6 mA              |                          | STSCHG# is asserted when the Changed bit and SigChg bit are set in the Card Configuration Status Register.                                                                                                                |

# 3.0 Pinout Description (Continued)

TABLE 3-2. Serial EEPROM Interface Pins

| Pin<br>Name | Pin<br>Type | Pin<br>No. | Level<br>Compatibility | Internal<br>Resistor     | Description                                                                                             |

|-------------|-------------|------------|------------------------|--------------------------|---------------------------------------------------------------------------------------------------------|

| EEDO        | I           | 119        | TTL                    |                          | Serial Data in from EEPROM.                                                                             |

| EEDI        | 0           | 120        | CMOS 6 mA              |                          | Serial Data out to EEPROM.                                                                              |

| EECS        | 0           | 122        | CMOS 6 mA              |                          | EEPROM Chip Select.                                                                                     |

| EESK        | 0           | 121        | CMOS 6 mA              |                          | EEPROM Clock. Freq = MCLK(0)/32.                                                                        |

| EESize      | I           | 117        | TTL                    | >100k to V <sub>CC</sub> | EEPROM Size. If high, the EEPROM size is 16-kbit, else the size is 4-kbit.                              |

| EEORG       | I           | 118        | TTL                    | >100k to V <sub>CC</sub> | EEPROM Organization pin. If high, the EEPROM is organized as 16-bit words, else organization is 8 bits. |

Note: The Enable EEPROM function is performed in software by writing to the EEPROM Control Register. The Enable EEPROM bit will default to low (disabled) upon power on.

**TABLE 3-3. Card-Side Interface Pins**

| Pin<br>Name | Pin<br>Type | Pin<br>No.               | Level<br>Compatibility | Internal<br>Resistor     | Description                                                                                                                                                                                                                       |  |

|-------------|-------------|--------------------------|------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LDATA(15:0) | 1/0         | 13–7,<br>5–1,<br>144–141 | TTL 6 mA               | Hold Circuit<br>(Note 1) | Card-side Data Bus.                                                                                                                                                                                                               |  |

| DPORT(3:0)  | 1/0         | 20, 19,<br>18, 17        | TTL 6 mA               |                          | Generic, Direction programmable function port for additional user signals. In LAN Mode, these signals are assigned specific meaning for use with an Ethernet LAN IC.                                                              |  |

| EARD#       | 0           | 128                      | CMOS 6 mA              |                          | Chip select for external attribute memory not shadowed in PCM16C00 IC.                                                                                                                                                            |  |

| SPK IN      | ı           | 127                      | TTL Schmitt            |                          | Input Audio Signal.                                                                                                                                                                                                               |  |

| RIIN(0)#    | I           | 53                       | TTL Schmitt            |                          | Ring Indicator for function 0. In LAN Mode, this is a packet indicator input.                                                                                                                                                     |  |

| RI_IN(1)#   | ı           | 129                      | TTL Schmitt            |                          | Ring Indicator for function 1.                                                                                                                                                                                                    |  |

| CIORD#      | 0           | 23                       | CMOS 6 mA              |                          | I/O read signals are passed through from HIORD# according to the expression shown below when a valid address is decoded.  (CIORD# = HIORD# + REG# + (CE1# * CE2#)                                                                 |  |

| CIOWR#      | 0           | 22                       | CMOS 6 mA              |                          | I/O write signals are passed through from HIOWR# according to the expression shown below when a valid address is decoded. CIOWR# = HIOWR# + REG# + (CE1# * CE2#)                                                                  |  |

| CWAIT(1:0)  | I           | 140, 64                  | TTL                    |                          | Card-side transaction wait state inputs.                                                                                                                                                                                          |  |

| CS(1:0)#    | 0           | 139, 63                  | CMOS 6 mA              |                          | Chip select for each function.                                                                                                                                                                                                    |  |

| BHE#        | 0           | 21                       | CMOS 6 mA              |                          | Byte high enable. When de-asserted and CS()# asserted, an 8-bit access on LDATA(7:0) is in progress. This holds for both odd and even addresses. When asserted and CS()# asserted, a 16-bit access on LDATA(15:0) is in progress. |  |

| READY(1:0)  | I           | 136, 60                  | TTL                    | >100k to V <sub>CC</sub> | Indicates that the function is either READY or ~ READ (i.e Busy). This signal is used to assert the Rdy/Bsy#bit in Pin Replacement Registers.                                                                                     |  |

| CINT(1:0)   | I           | 138, 62                  | TTL Schmitt            |                          | Card-side interrupt input signals.                                                                                                                                                                                                |  |

| SRESET(1:0) | 0           | 137, 61                  | CMOS 6 mA              |                          | Signals reset to Card-side functions.                                                                                                                                                                                             |  |

# 3.0 Pinout Description (Continued)

TABLE 3-3. Card-Side Interface Pins (Continued)

| Pin<br>Name  | Pin<br>Type | Pin<br>No.                 | Level<br>Compatibility | Internal<br>Resistor     | Description                                                                                                                                                        |

|--------------|-------------|----------------------------|------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOCS16(1:0)# | I           | 135, 59                    | TTL                    |                          | This pin is asserted during an access to a function if that function is capable of a 16-bit access.                                                                |

| BREQ(1:0)    | 1           | 131, 55                    | TTL                    |                          | Bus requests for local and remote DMA.                                                                                                                             |

| BACK(1:0)    | 0           | 130, 54                    | CMOS 6 mA              |                          | Bus grants for local and remote DMA.                                                                                                                               |

| LA(15:0)     | O Tri       | 51-48,<br>46-37,<br>35, 34 | CMOS 6 mA              | Hold Circuit<br>(Note 1) | Local Address Bus. This may be equivalent to the HADDR(15:0) bus for PCMCIA Host reads/writes or a latched address from a DMA controller such as a LAN controller. |

| ADS          | 1           | 52                         | TTL                    |                          | Address Strobe to latch LDATA(15:0) onto LA(15:0).                                                                                                                 |

| PCNTL(1:0)   | 0           | 15, 14                     | CMOS 6 mA              |                          | Power management control signals or general outputs.                                                                                                               |

| MCLK(1:0)    | 1           | 134, 56                    | TTL Schmitt            |                          | Input clocks for function 0 and function 1.                                                                                                                        |

| FCLK(1:0)    | 0           | 132, 57                    | CMOS 6 mA              |                          | Output clock signals for function 0 and function 1.<br>These may be gated on/off or be a divided value of<br>MCLK(1:0).                                            |

| MEMWR#       | 1           | 30                         | TTL                    | >100k to V <sub>CC</sub> | Common Memory write input for one function.                                                                                                                        |

| MEMWEH#      | O Tri       | 31                         | CMOS 6 mA              | >10k to V <sub>CC</sub>  | Common Memory write output for upper byte of data word.                                                                                                            |

| MEMWEL#      | O Tri       | 32                         | CMOS 6 mA              | >10k to V <sub>CC</sub>  | Common Memory write output for lower byte of data word.                                                                                                            |

| MEMOE#       | O Tri       | 33                         | CMOS 6 mA              | >10k to V <sub>CC</sub>  | Common Memory read signal.                                                                                                                                         |

| PRQ          | Ι           | 29                         | TTL                    | >100k to GND             | Port Request from LAN Device for Remote DMA Access mode to I/O Register.                                                                                           |

| PRD#         | 1           | 24                         | TTL                    | >100k to V <sub>CC</sub> | Port Read from LAN Device to I/O Register.                                                                                                                         |

| RACK#        | 0           | 25                         | CMOS 6 mA              |                          | Read Acknowledge from the PCM16C00 signaling to the LAN that the PCMCIA Host has read the entire I/O Register.                                                     |

| PWR#         | I           | 27                         | TTL                    | >100k to V <sub>CC</sub> | Port Write from LAN Device to I/O Register.                                                                                                                        |

| WACK#        | 0           | 28                         | CMOS 6 mA              |                          | Write Acknowledge from the PCM16C00 signaling to the LAN that the PCMCIA Host has placed data in the entire I/O Register.                                          |

Note 1: The Hold Circuit will hold the signal to the logic value it was last set to when the line is TRI-STATE®. This will insure that inputs do not float during a TRI-STATE condition.

**TABLE 3-4. Miscellaneous Pins**

| Pin<br>Name           | Pin<br>Type | Pin<br>No.                               | Level<br>Compatibility | Internal<br>Resistor | Description                                                             |

|-----------------------|-------------|------------------------------------------|------------------------|----------------------|-------------------------------------------------------------------------|

| TEST(2:0)             | I           | 126, 125,<br>124                         | TTL                    | >100k to GND         | Test pins. These pins should be left disconnected for normal operation. |

| V <sub>CC</sub> (5:0) | Power       | 16, 36,<br>58, 86,<br>108, 123           |                        |                      | Power Voltage.                                                          |

| GND(7:0)              | Power       | 6, 26, 47,<br>69, 77,<br>97, 113,<br>133 |                        |                      | Return Voltage.                                                         |

## 3.0 Pinout Description (Continued)

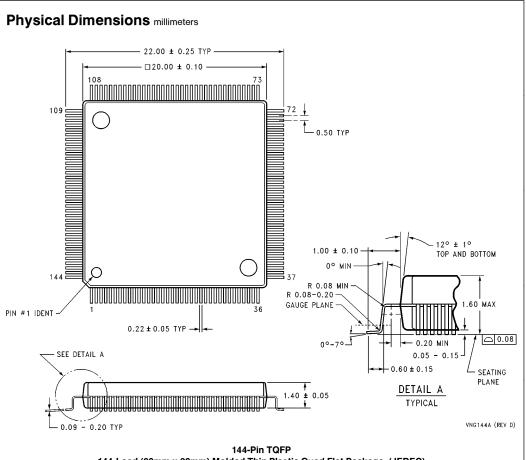

Pin Total

Host-Side Interface Pins

46

EEPROM Interface Pins

6

Card-Side Interface Pins

75

Miscellaneous Pins

17

Total Pins

144

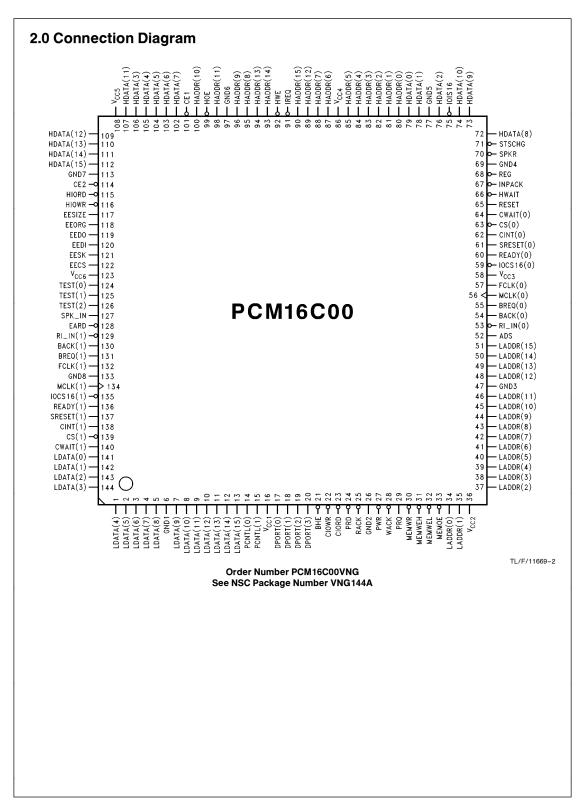

## 4.0 Block Diagram

## **5.0 Functional Description**

The Multi-function PCMCIA card interface IC (integrated circuit) provides an integrated solution to interfacing dual function I/O cards with the PCMCIA Bus. The part has a continguous 2-kbyte RAM block to store attribute memory. The IC also provides an EEPROM interface to serial EEPROMs that use the MICROWIRE protocol. At a minimum, a 4-kbit serial EEPROM is required. The 16-kbit EEPROM is optional. The part allows I/O address windows to be programmed independently for each function.

### 5.1 ADDRESS MAPS

#### 5.1.1 Attribute Memory Addressing

The Attribute Memory space contains both the Card Information Structure (CIS), PCMCIA Registers for both functions, and PCM16C00 implementation specific registers. Note that PCMCIA specifies that Attribute memory may only be accessed on even address byte boundaries. The Attribute Memory space fragmentation is shown in Table 5-1.

TABLE 5-1. Attribute Memory Map

| Register Description                     | Register Type     | Address (Hex) | EEPROM   |

|------------------------------------------|-------------------|---------------|----------|

| Card Information Structure               | PCMCIA CIS        | 0x000-0x03E2  | Yes      |

| Pin Polarity Register                    | PCM16C00 Specific | 0x03E4        | Yes      |

| PMGR and Clock Register                  | PCM16C00 Specific | 0x03E6        | Yes      |

| CTERM 0 Register                         | PCM16C00 Specific | 0x03E8        | Yes      |

| CTERM 1 Register                         | PCM16C00 Specific | 0x03EA        | Yes      |

| Arbiter Priority Register                | PCM16C00 Specific | 0x03EC        | Yes      |

| Arbiter Latency Register                 | PCM16C00 Specific | 0x03EE        | Yes      |

| Miscellaneous Register                   | PCM16C00 Specific | 0x03F0        | Yes      |

| Digital Port Direction Register          | PCM16C00 Specific | 0x03F2        | Yes      |

| Digital Port Register                    | PCM16C00 Specific | 0x03F4        | Yes      |

| Wait State Timer Register                | PCM16C00 Specific | 0x03F6        | Yes      |

| Reserved for Future Use Registers        | PCM16C00 Specific | 0x03F8-0x03FE | Yes      |

| Card Information Structure               | PCMCIA CIS        | 0x0400-0x0FFE | Optional |

| ID Register                              | PCM16C00 Specific | 0x1000        | No       |

| EEPROM Control Register                  | PCM16C00 Specific | 0x1002        | No       |

| Reserved for Future Use Registers        | PCM16C00 Specific | 0x1004-0x101E | No       |

| Function 0 Configuration Option Register | PCMCIA            | 0x1020        | No       |

| Function 0 Configuration Status Register | PCMCIA            | 0x1022        | No       |

| Function 0 Pin Replacement Register      | PCMCIA            | 0x1024        | No       |

| Unused                                   | PCMCIA            | 0x1026        | No       |

| Function 0 I/O Event Register            | PCMCIA            | 0x1028        | No       |

| Function 0 Base A Register               | PCMCIA Extension  | 0x102A        | No       |

| Function 0 Base B Register               | PCMCIA Extension  | 0x102C        | No       |

| Unused                                   | PCMCIA Extension  | 0x102E-0x1030 | No       |

| Function 0 Limit Register                | PCMCIA Extension  | 0x1032        | No       |

| Reserved for Future Use Registers        | PCMCIA Extension  | 0x1034-0x103E | No       |

| Function 1 Configuration Option Register | PCMCIA            | 0x1040        | No       |

| Function 1 Configuration Status Register | PCMCIA            | 0x1042        | No       |

| Function 1 Pin Replacement Register      | PCMCIA            | 0x1044        | No       |

| Unused                                   | PCMCIA            | 0x1046        | No       |

| Function 1 I/O Event Register            | PCMCIA            | 0x1048        | No       |

| Function 1 Base A Register               | PCMCIA Extension  | 0x104A        | No       |

TABLE 5-1. Attribute Memory Map (Continued)

| Register Description              | Register Type    | Address (Hex) | EEPROM |

|-----------------------------------|------------------|---------------|--------|

| Function 1 Base B Register        | PCMCIA Extension | 0x104C        | No     |

| Unused                            | PCMCIA Extension | 0x104E-0x1050 | No     |

| Function 1 Limit Register         | PCMCIA Extension | 0x1052        | No     |

| Reserved for Future Use Registers | PCMCIA Extension | 0x1054-0x105E | No     |

#### 5.1.2 I/O Memory Addressing

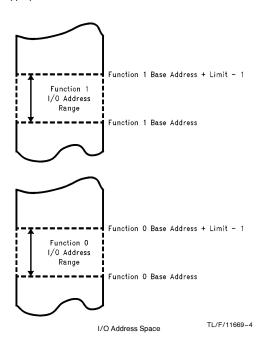

National's PCM16C00 uses a pair of address base and limit registers to fragment the I/O Address space. This allows I/O transactions from the PCMCIA Host to be steered to the appropriate function.

FIGURE 5-1. I/O Address Decoding for two functions on a PCMCIA Card

#### 5.1.3 Common Memory Addressing

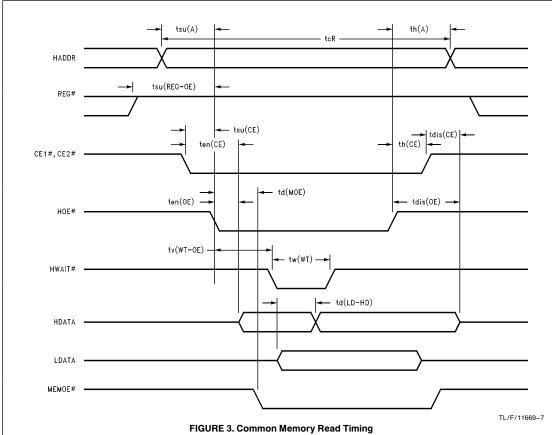

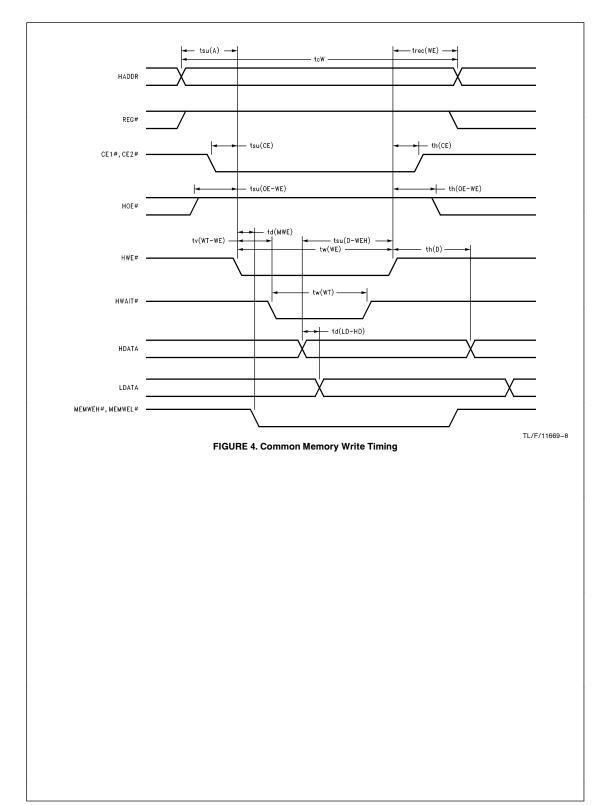

National's PCM16C00 does not specifically decode common memory address accesses initiated by the host. Rather, it will pass host accesses HADDR(15:0) through to LADDR(15:0) and HDATA(15:0) through to LDATA(15:0) once the host is granted access to the card using the arbiter. In addition, the PCM16C00 will pass the HOE# signal assertion through to the MEMOE# signal and the host HWE# signal assertion to the MEMWEH#/MEMWEL# signals appropriately. The assertion of MEMWEH#, MEMWEL#, or both is determined by an 8-bit or 16-bit access

and the address boundary as specified in the PCMCIA Specification. The functions are free to use common memory by arbitrating for the card local bus. If granted, the PCM16C00 will relinquish the LADDR(15:0) and LDA-TA(15:0) bus to the function.

If a function is mapped to common memory, such as a FLASH device, and requires further address lines, it may use the HADDR(25:16) lines from the PCMCIA socket as appropriate even though these signals do not go into the PCM16C00. These signals can be considered to be sideband to the PCM16C00. The card design is free to use external decoding logic for common memory.

For an Ethernet LAN card that desires to have a FLASH device, HADDR(16) may be used to fragment the Common Memory space into 2 pieces. When HADDR(16) is zero (0), the LAN SRAM buffers (up to 64-kbyte max) may be selected. When HADDR(16) is one (1), a 64-kbyte FLASH device may be selected. This use of one address line does not require an additional IC. If a FLASH device greater than 64k is desired, minimal decoding logic would become necessary.

#### **5.2 REGISTERS**

#### 5.2.1 PCMCIA Registers

The PCMCIA register's context is for its respective function. Each function (0,1) has its own set of Configuration Registers so that each function may be configured and operated on independently from a programming model viewpoint.

#### **CIS (CARD INFORMATION STRUCTURE)**

[0x000-0x03E2]

When the PCM16C00 powers on, the contents of the lower 2.0/0.5-kbyte of the EEPROM are loaded into the device's shadow RAM. This not only allows attribute memory accesses to the CIS, but, it also provides defaults for 10 PCM16C00 specific registers to be loaded. This allows default loading of parameters that are transparent to system or device software. The best use is for the card manufacturer to determine what values these should be and program them into the EEPROM when the CIS is programmed. Either system software such as Card Services/Socket Services or device software may read and parse the CIS by accessing attribute memory on the PC Card. If desired, this software agent may write to the CIS or default EEPROM registers and, if desired, have these new values saved to the EEP-ROM. The actual contents of the CIS and the static registers is PC Card design dependent.

#### 5.2.2 PCM 16C00 Specific Registers

These registers are defined specifically for National's PCM16C00 IC and are not part of the PCMCIA specification.

#### 5.2.2.1 Standard Mode Register Set

These registers allow the PCM16C00 IC to perform its base functionality of supporting two general functions on a PC Card

#### Pin Polarity Register

[0x03E4]

This register sets the polarity of the card side interface signals.

| D7    | D6    | D5      | D4      | D3  | D2     | D1     | D0     |

|-------|-------|---------|---------|-----|--------|--------|--------|

| CIOWR | CIORD | SRESET1 | SRESET0 | BHE | Memls8 | CWAIT1 | CWAIT0 |

**CIOWR, CIORD**—Sets the polarity of the CIOWR# and CIORD# pins respectively. A high indicates active high. The default polarity is active-low.

SRESET1, SRESET0—Sets the polarity of the SRESET(1) and SRESET(0) pins respectively. When this bit is set to a zero (0), the output signal is asserted in the high (1) state. When this bit is set to a one (1), the output signal is asserted in the low (0) state. The bit default is zero (0), i.e. the SRESET() signal is active high.

**BHE**—Sets the polarity of the BHE# pin. A high indicates active-high. The default polarity is active-low.

MemIs8—This bit is set to one (1) if common memory is organized for 8-bit access. This bit is set to zero (0) if common memory is organized for 16-bit access. The default value is zero (0). This information allows the PCM16C00 to properly access memory using the MEMWEH#, MEMWEL#, and MEMOE# signals.

**CWAIT1, CWAIT0**—When this bit is set to one (1), the PCM16C00 interprets this input signal active when it is low (0). When this bit is set to zero (0), the PCM16C00 interprets this input signal as active when it is high (1). The default bit value is zero (0), i.e. the CWAIT() input signal is asserted high (1).

#### PMGR and Clock Register [0x03E6]

The Power Manager (PMGR) and Clock Register is used for controlling the PCNTL(1:0) pins for either power management purposes or general purpose digital output only. Unlike the Digital Port Register, there is no associated direction register since only outputs are allowed.

Hardware power management is enabled using the Function Configuration Option Register's Function Configuration Index values. Its use is intended for functions that can be sequenced on/off or into idle or sleep states with a quick (< 10  $\mu s$ ) response time when powered on again. That is, the function may use its CWAIT() signal to extend a transaction that caused the PCM16C00 to turn it on. Use of the READY() signal in a dynamic hardware power managed environment to set the RRdy/Bsy bits in order to achieve > 10  $\mu s$  response times for power on is not guaranteed to work since system software may not inspect the RRdy/Bsy bit in all such instances.

| D7      | D6   | D5    | D4       | D3      | D2   | D1    | D0       |

|---------|------|-------|----------|---------|------|-------|----------|

| F1CLKEN | DIV1 | PPOL1 | PCNTL(1) | F0CLKEN | DIV0 | PPOL0 | PCNTL(0) |

F1CLKEN, F0CLKEN—If set, these enable the pins FCLK(1:0) to receive a clock out. If clear, the respective pins FCLK(1:0) will be forced low. These are set and cleared by software if desired or statically loaded upon card power up from the EEPROM.

**DIV1, DIV0—**If set, the respective clock output from FCLK(1:0) will be divided by 32 from the input clocks MCLK(1:0). If clear, the clock output FCLK(1:0) will equal the respective clock input MCLK(1:0). These are set and cleared by software if desired or statically loaded upon card power up from the EEPROM.

PPOL1, PPOL0—Sets the active polarity of the PCNTL(1) and PCNTL(0) signals such that the function is asserted. If PPOL is set to zero (0), PCNTL() is asserted when in the high state. If set to one (1), PCNTL() is asserted when in the low state. The default is set to zero (0), i.e. PCNTL() defaults to active high.

PCNTL(1), PCNTL(0)—These bits control the pins PCNTL(1) and PCNTL(0) respectively. If hardware power management is not selected in the Function Configuration Option Register's Function Configuration Index, then these bits may be used as output signals by software for general purposes. If the hardware power management configuration is selected, these bits are de-asserted (defined by PPOL1, 0) when the PCM16C00's CTERM 1 or 0 counter expires. These bits will be asserted if a transaction occurs to the function through an I/O window, the function requests the card-side bus using BREQ() or the function issues a RI\_IN(). In either strategy, software may always write and read back these bits. These bits default to zero (0) during poweron until the PMGR and Clock Register can be loaded from the EEPROM.

#### CTERM Registers 0, 1 [0x03E8, 0x03EA]

These registers are used to define the value of function 0's and function 1's power time-out counters respectively. If a function's power time-out counter expires, the PCNTL bit for that function in the PMGR and Clock Register is de-asserted. This will occur if a function is in-active long enough for it's power time-out counter to expire. Active is defined as having either an I/O access from the host, receiving a BREQ() or a RI\_IN()#. Devices that may operate for long periods of time without a host I/O access and that do not use BREQ() should follow a software controlled power management strategy that uses the PwrDn bits in the Function Configuration Status Registers 0, 1.

| D7-D0                                     |

|-------------------------------------------|

| N = Time-Out Counter Terminal Count Value |

Each function's terminal counter is 8 bits wide and counts at a rate of MCLK(0)/(2<sup>17</sup>). For example, if the MCLK(0) frequency is 30 MHz the device can be programmed to time-out between 0.0s to 1.114s. The general formula is:

Time =

$$(1/\text{mclk}(0)) * 2^{17} * N$$

,

where

$$N = \{0, 1, 2, \dots, 255\}$$

For a 5 MHz MCLK(0) frequency, the equation is:

Time = N (26.2144 ms) where  $N = \{0,1,2,...,255\}$

Note: A value of zero implies the function is powered down.

#### **Arbiter Priority Register**

0x03E0

This register controls the priority (from the set  $\{00,01,10,11\}$ ) for each possible card-bus master from the set  $\{PCMCIA \mid Host, Function 0, Function 1\}$ . The value of  $\{3\}$  is the highest priority whereas  $\{0\}$  is the lowest priority.

| D7         | D6         | D5-D4       | D3-D2      | D1-D0      |

|------------|------------|-------------|------------|------------|

| ArbiterCLK | PreemptEnb | PCMCIA Host | Function 1 | Function 0 |

|            |            | Priority    | Priority   | Priority   |

ArbiterCLK—This bit is set to one (1) to increment the Arbiter Latency Register using MCLK(0)/16. This bit is set to zero (0) to increment the Arbiter Latency Register using MCLK(0)/1.

**PreemptEnb**—If this bit is set to one (1), the arbiter will allow pre-emption of bus masters. If this bit is set to zero (0), the arbiter will allow a bus master to complete before granting the bus to another master as determined by the priority scheme used.

#### **Arbiter Latency Register**

[0x03EE]

This register programs a latency timer such that when a card-bus master is in control of the bus and another unit requests and wins access to the bus (following priority scheme), the timer will allow the current bus owner to retain the bus until the timer expires. This is useful when pre-emptions are allowed using the PreemptEnb bit in the Arbiter Priority Register. The timer does not start counting down until the arbiter queues another device for bus ownership.

| D7-D0                           |

|---------------------------------|

| N = Arbiter Latency Timer Value |

**Arbiter Latency Timer Value (N)**—This value is used by an arbiter counter. Therefore, the latency time until the BREQ() is relinquished (or internal host BREQ) when PreemptEnb is set to one (1) is:

Latency Time =  $16(N)/f_{MCLK(0)}$  when ArbiterCLK = (1) Latency Time =  $(N)/f_{MCLK(0)}$  when ArbiterCLK = (0)

#### Miscellaneous Register

[0x03F0]

| D7     | D6           | D5           | D4-D0           |

|--------|--------------|--------------|-----------------|

| FastEE | LA_TRI_Func1 | LA_TRI_Func0 | EEPROMStartAddr |

FastEE—If this bit is set to one (1), then the clock used to access the EEPROM shall be MCLK(0)/2. If this bit is set to zero (0), the clock used to access the EEPROM shall be MCLK(0)/32.

LA\_TRI\_Func1, LA\_TRI\_Func0—This bit should be set to one (1) when a bus master function will multiplex address and data on the LDATA() bus and will use ADS to strobe the address phase on this bus to the LADDR() bus. In this case, the PCM16C00 will drive the LADDR() bus and latch the LDATA() bus to the LADDR() bus on an ADS strobe. This bit should be set to a zero (0) when a bus master function will drive the LADDR() bus directly. In this case, the PCM16C00 will TRI-STATE (not drive) the LADDR() bus when it is granted to function 0 or function 1 in expectation that the function will control the LADDR() bus.

**EEPROMStartAddr**—This field contains a starting address for EEPROM read or write access. This is ordinarily set to zero and is used for debug/test purposes.

#### **Digital Port Direction Register**

[0x03F2]

This register is a read/write register that controls the direction for each individual bit in the Digital Port Register.

| D7-D4    | D3     | D2     | D1     | D0     |

|----------|--------|--------|--------|--------|

| Reserved | DPDIR3 | DPDIR2 | DPDIR1 | DPDIR0 |

**DPDIR3,2,1,0—**DPDIRi defines the direction of the corresponding DPORT(i) pin and, hence, the direction of the DPORTi bit in the Digital Port Register. If DPDIRi is set to zero (0)(default), then the DPORT(i) pin is a digital input. If DPDIRi is set to one (1), then the DPORT(i) pin is a digital output.

#### **Digital Port Register**

0x03F4

The Digital Port Register is a read/write register connected to the DPORT(3:0) pins of the PCM16C00 chip. Each bit is direction programmable through software using the Digital Port Direction Register.

| D7-D4    | D3     | D2     | D1     | D0     |

|----------|--------|--------|--------|--------|

| Reserved | DPORT3 | DPORT2 | DPORT1 | DPORT0 |

DPORT3,2,1,0—If DPDIR is set to one (1) then DPORT may be written to. The value written will be sourced by the corresponding DPORT pin. When DPORT is read, the value returned will be the last value written to DPORT. If DPDIR is reset to zero (0) then DPORT will assume the value externally driven into the corresponding DPORT pin. Therefore, when DPORT is read, it returns the value being driven into the DPORT pin. When written, the value is unaffected and retains the value driven on DPORT.

#### Wait State Timer Register

[0x03F6]

This register allows the insertion of default wait states from the PCM16C00 using HWAIT#. It is intended to be used in situations where either the function is too slow to respond with a CWAIT() or the unique wait timing constraints between the system and PC Card design necessitate a default wait state.

| D7-D4    | D3-D2     | D1-D0     |

|----------|-----------|-----------|

| Reserved | Func1Wait | Func0Wait |

Func1Wait, Func0Wait—This value is the number (0, 1, 2, or 3) of MCLK(0) time periods that the PCM16C00 will assert HWAIT# during a valid access to a particular function. For Zero wait states, program these values to 00b.

#### ID Register

[0x1000]

This read only register provides the software with IC revision information.

| D7-D3                  | D2-D0                |  |

|------------------------|----------------------|--|

| PCM16C00 Code = 00000b | Revision Code = 000b |  |

National PCM16C00 Code—This code may be used to identify the PCM16C00 IC. The value of this register is 00000b.

**Revision Code**—This will uniquely identify the silicon version of the PCM16C00 IC as 000b.

#### **EEPROM Control Register**

[0x1002

This register controls reading and writing the EEPROM as well as the EEPROM enable.

| D7          | D6         | D5-D1    | D0            |

|-------------|------------|----------|---------------|

| WriteEEPROM | ReadEEPROM | Reserved | Enable EEPROM |

WriteEEPROM—When set, this tells the EEPROM controller to copy the contents of the PCM16C00 Shadow RAM to the EEPROM. Once done, the EEPROM controller clears this bit

ReadEEPROM—When set, this tells the EEPROM controller to copy the contents of the EEPROM to the shadow RAM. Once done, the EEPROM controller clears this bit. Any data modified in the Shadow RAM that has not first been written back to the EEPROM will be lost.

**Enable EEPROM**—This must be set to allow EEPROM writes. If clear, the EEPROM may not be written. The default value at reset is low. The EEPROM may be read independent of the value of this bit.

Note 1: Upon power-up, the Cobra EEPROM controller copies the entire contents of the EEPROM (size dependent) into the Shadow RAM.

Note 2: The PCM16C00 EEPROM controller stores data in a 16-bit organized EEPROM in low/high format. Although Attribute Memory is on even byte boundaries only, the entire EEPROM's address space is used. This eliminates waste of EEPROM memory. Therefore the Attribute space used by the Shadow RAM is double the actual size of the EEPROM. For example, if a 16-bit EEPROM is pre-programmed, the low byte at word 0 in the EEPROM will be shadowed at Attribute location 0x0000 and the high byte will be shadowed at Attribute location 0x0000. The low byte at EEPROM word 1 will be shadowed to Attribute location 0x0004, etc. For EEPROM organizations of 8 bits, EEPROM byte 0 will be shadowed to Attribute location 0x0000 and byte 1 will be shadowed to Attribute location 0x0000 and byte 1 will be shadowed to Attribute location 0x0000.

#### Function Configuration Option Registers 0,1

[0x1020,0x1040]

| D7     | D6      | D5-D0                        |

|--------|---------|------------------------------|

| SRESET | LevIREQ | Function Configuration Index |

**SRESET**—If the host sets this field to one (1), the PCM16C00 shall place the given function in the reset state. When the host returns this field to zero (0), the function shall enter the same unconfigured, reset state as it does following a power-up and hardware reset.

LevIREQ—When the PCM16C00 is being used as a PCMCIA I/O interface and this field is set to one (1), the PCM16C00 shall generate Level Mode interrupts for the function using the IREQ# signal. If the PCM16C00 is being used as a PCMCIA I/O interface and this field is set to zero (0), the PCM16C00 shall generate Pulse Mode interrupts for the function. Use of Level Mode interrupts for both functions when the PCM16C00 is configured for multi-function operation is strongly recommended. Since there is only one PCMCIA Bus interface, the LevIREQ bits for Function 0 Configuration Option Register are Aliased. The PCM16C00 will also only allow a write to the LevIREQ bit value to change the interfaces Interrupt level mode if the given function is configured using ConfFunc and interrupts are enabled using EnbIREQ.

In addition, the PCM16C00 provides an enhanced interrupt protocol scheme described by the IntrReset bit in the Function Configuration Status Registers 0, 1. The PCM16C00 implements a shared interrupt scheme in multi-function operation. Single function configurations may use Level Mode or Pulse Mode interrupt schemes. Pulsed Mode interrupt width is given by:

TwidthIREQ = 16/(FreqMCLK(0))

Using MCLK(0) from 5 MHz–30 MHz will insure pulse widths from 0.53  $\mu$ s–3.2  $\mu$ s which exceed the 0.5  $\mu$ s minimum requirement for PCMCIA.

Function Configuration Index—When the host system sets this field to the value of the Configuration Entry Number field of a Configuration Table Entry Tuple, the function shall enter the configuration described by that tuple. This field shall be reset to zero (0) by the PCM16C00 when the host sets the SRESET field to one (1) or the host asserts RESET. If this field is set to zero (0) explicitly by the host or implicitly by SRESET or RESET, the function shall use the Memory Only interface and I/O cycles from the host shall be ignored by the function.

The following configurations are supported by the Function Configuration Index 0, 1:

ConfFunc (D0)—If this is set to one (1), then the Card is configured for that function.

EnbBase\_Limit (D1)—If this is set to a one (1), the base and limit register pair for the function is enabled. That is, the PCM16C00 will only pass I/O transactions whose address falls within the I/O window specified by the base and limit pair. If this is set to a zero (0), the PCM16C00 will not test transactions' addresses against the base and limit pair for that function and will, therefore, pass all I/O transactions to the function. For single function operation, the EnbBase\_ Limit would be enabled for operation with host controllers that support overlapping windowing and the INPACK# signal. For host controllers that do not support INPACK# but are capable of windowing granularity required for the function, EnbBase\_Limit may be set to zero (0) so that all I/O transactions are passed to the function. For multifunction operation, the EnbBase\_Limit bits for both functions should be set to one (1).

EnbIREQ (D2)—When the PCM16C00 is being used as a PCMCIA I/O interface and this field is set to one (1), the PCM16C00 shall enable this function to interrupt the host using the IREQ# signal. Normally this bit would be set to one (1). In environments where the function's software driver will use a polling technique for status information, this bit could be set to zero (0) to disable interrupts from that function

**PMGMT\_EN (D3)**—This bit, if set to a one (1), enables the hardware power management controller to control the PCNTL() pin for that function. See the PMGR and Clock Register description.

LAN Mode (D4 for Function 0 Configuration Option Register only)—When this bit is set to a one (1), the Function 0 interface on the PCM16C00 will fully support National's DP83902AVJG Ethernet LAN IC. Function 0 is said to be in LAN Mode.

### Function Configuration Status Registers 0,1

[0x1022,0x1042]

These PCMCIA registers are used for function control/status information.

| D7      | D6     | D5    | D4       | D3    | D2    | D1   | D0        |

|---------|--------|-------|----------|-------|-------|------|-----------|

| Changed | SigChg | IOis8 | Reserved | Audio | PwrDn | Intr | IntrReset |

Changed—If one or more of the state change signals in the Function Pin Replacement Register are set to one (1), the PCM16C00 shall set this field to a one (1). If the PCM16C00 is being operated as a I/O interface, (PC Card using I/O Interface), and both the Changed and SigChg fields are set to one (1), the PCM16C00 shall assert the STSCHG# signal. If the PC Card, and hence PCM16C00, is not using the I/O interface, this field is undefined and ignored.

SigChg—This field serves as a gate for asserting the STSCHG signal. If the PCM16C00 is operated as an I/O interface, and both the Changed and SigChg fields are set to one (1), the PCM16C00 shall assert the PCMCIA STSCHG# signal. If the PCM16C00 is operated as an I/O interface and this field is reset to a zero (0), the PCM16C00 shall not assert the STSCHG# signal. If the PCM16C00 is not operated as an I/O interface, this field is undefined and should be ignored. Either Function Configuration Status Register 0 or 1 is capable of asserting STSCHG# if it satisfies the above requirements.

**IOis8**—When the host can only provide I/O cycles with an 8-bit D0-D7 path, the host shall set this bit to a one (1). The card is guaranteed that accesses to 16-bit registers will occur as two, byte accesses rather than a single 16-bit access. This information is useful when 16-bit and 8-bit registers overlap.

**Audio**—Sampling of the signal SPK\_IN and control of SPKR# is accomplished using the Audio bit. SPKR# will equate to SPK\_IN anytime either of the Audio bits is set to one (1) and the function is configured.

PwrDn—When the host sets this field to one (1), the PCM16C00 shall set the given function to a power-down state by de-asserting the PCNTL() signal for that function. While this field is a one (1), the host shall not access the function on the PC Card. The host shall return this field to zero (0) before attempting to access the function. The system shall not place the card into a power-down state while the card's RDY/BSY# line is in the low (Busy) state. All input/output signals particular to the function are TRI-STATE.

Intr—If the function is requesting interrupt servicing (CINT() asserted), the PCM16C00 shall set this field to one (1). The PCM16C00 shall reset this field to zero (0) when the interrupt request has been serviced (CINT() de-asserted).

IntrReset—If IntrReset is set to zero (0), Intr shall be set to one (1) when an interrupt condition occurs and shall be reset to zero (0) when the interrupt condition has been serviced. A write to the Intr bit will do nothing. If IntrReset is set to one (1), Intr shall be set to one (1) when an interrupt condition occurs (CINT() pin) and be cleared to a zero (0) when the interrupt (CINT() pin) is serviced, however, a write of value zero (0) to any FCSR's Intr bit where IntrReset is set to one (1) shall cause the PCM16C00 to evaluate all CINT() signals and generate another interrupt to the system if an interrupt is pending. Note that the write of zero (0) to any FCSR's Intr bit where IntrReset is set to one (1) is an indication to the PCM16C00 that it must evaluate all CINT()

pins and generate a specified pulse to the system on the IREQ line. This protocol will work in either pulse or level mode (state of aliased LevIREQ controlling IREQ#PCMCIA signal mode). Functions operate by asserting their CINT() signal when an interrupt condition occurs. If interrupts are enabled for a given function, then that function's CINT() pin, when asserted, may generate an interrupt within the PCM16C00.

National's PCM16C00 has access to an internal interrupt line that represents the OR of all interrupts that have been asserted and enabled. Since functions use a level mode interrupt approach, this OR'd internal interrupt signal represents a level mode ORing of the interrupts. When the OR'd signal is asserted, the PCM16C00 will generate either a pulse mode or level mode interrupt on the IREQ# line. Before EOI processing by the functions ISR, the function's interrupt condition will be cleared and its CINT() pin will deassert. If no other interrupts are being asserted, the PCM16C00's internal line will de-assert IREQ#. If other interrupts are pending, the internal line remains asserted (and hence IREQ#). Since the standard PC compatible interrupt controller requires a positive edge to trigger an interrupt, system software based on using the IntrReset protocol for the PCM16C00 may write a zero (0) to any Intr bit where IntrReset is set to one (1) after EOI processing is done. This will cause the PCM16C00 to generate a pulse on the IREQ# line if any CINT() that's enabled is still asserted. In other words, if the internal line is still asserted at this point. If in pulse mode, this is a single pulse that goes high-low-high with at least 0.5  $\mu s$  low time. If in level mode, this pulse is a low-high-low pulse to trigger the interrupt controller and then remain low (IREQ# asserted) and be maintained low by the level mode interrupt. This protocol solves both the need for two positive edges during level mode interrupts when an interrupt occurs during an interrupt in-service and solves the need for separate-distinct pulse interrupts that do not overlap during two interrupt events close in time.

Note: For consistency, the PCM16C00 will alias all IntrReset bits on a write to insure that both functions operate in the same mode. Also, the Intr bits are aliased on writes as an indicator to the PCM16C00 that interrupt status must be checked and pulses generated per the above protocol.

### Function Pin Replacement Registers 0,1

[0x1024,0x1044]

These PCMCIA registers replace the signals missing from a PCMCIA Memory Card interface due to using the PCMCIA I/O interface

| D7    | D6    | <b>D</b> 5 | D4     | <b>D</b> 3 | D2    | D1       | D0     |

|-------|-------|------------|--------|------------|-------|----------|--------|

| CBVD1 | CBVD2 | CRdy/Bsy   | CWProt | RBVD1      | RBVD2 | RRdy/Bsy | RWProt |

CBVD1,CBVD2—These bits are not implemented.

CRdy/Bsy—This bit is set to one (1) when RRdy/Bsy bit changes state.

CWProt-This bit is not implemented.

**RBVD1,RBVD2,Rdy,Bsy,RWProt**—Only RRdy/Bsy is implemented for each function. This bit reflects the state of the functions READY() input pin on the PCM16C00.

Function I/O Event Registers 0,1

[0x1028,0x1048]

| D7-D6    | D5    | D4    | D3-D2    | D1     | D0     |

|----------|-------|-------|----------|--------|--------|

| Reserved | PIEvt | RIEvt | Reserved | PIEnab | RIEnab |

**PIEvt**—In normal operation (not LAN Mode), the PIEvt bit is unused. In LAN Mode of operation, the PIEvt bit for Func-

tion I/O Event Register 0 is set to a one (1) if the RI\_ IN(0) # signal is asserted. The PIEvt bit for Function 1 I/O Event Register is unused.

RIEvt—In normal operation PCM16C00 latches a one (1) to the Card I/O Event Register's RIEvt bit when the RI\_IN(0)# is set for the Function 0 I/O Event Register or when the RI\_IN(1)# is set for Function 1 I/O Event Register. In LAN Mode of operation, the RIEvt bit for Function 0 I/O Event Register is unused.

**PIEnab**—When this bit is set to a one (1), a latched value of one (1) on the PIEvt bit shall cause the Changed bit in the Function's Configuration Status Register to be set to a one (1).

**RIEnab**—When this bit is set to a one (1), a latched value of one (1) on the RIEvt bit shall cause the Changed bit in the Function's Configuration Status Register to be set to a one (1).

#### Function Base Address Registers 0,1 [0x102A-0x102C,0x104A-0x104C]

The base address for each function is comprised of 4 bytes (2 bytes implemented) that specify the base I/O address from which to begin decoding for chip selection of a particular function.

#### **Base A Register**

| D7-D0                                            |

|--------------------------------------------------|

| Byte 0 (Base Address bits 7-0) of 32-bit Address |

This register comprises the low 8 bits of the base address for the Function I/O decode selection.

#### Base B Register

| D7-D0                                             |

|---------------------------------------------------|

| Byte 1 (Base Address bits 15-8) of 32-bit Address |

This register comprises the next 8 bits of the base address for the Function I/O decode selection.

#### Base C Register

| D7-D0                                              |

|----------------------------------------------------|

| Byte 2 (Base Address bits 23-16) of 32-bit Address |

This register is unused in the PCM16C00.

#### **Base D Register**

| D7-D0                                              |

|----------------------------------------------------|

| Byte 3 (Base Address bits 31-24) of 32-bit Address |

This register is unused in the PCM16C00.

Using Base A and Base B Registers for each function supported by the PCM16C00 allows a 16 bit base address to be specified for I/O decoding and selection of function 0 and function 1 separately.

#### Function Limit Address Registers 0,1 [0x1032,0x1052]

The value placed in this register is a bit mask used to indicate which address bits the PCM16C00 will not decode. A value of one (1), indicates that the PCM16C00 will not decode the corresponding address line. A value of zero (0) indicates the PCM16C00 shall decode the corresponding address line. For proper operation, only contiguous sequences of ones (1) starting at bit 0 and moving leftward are allowed. For example, 00001001 is illegal whereas 00000111 is legal. This implies that the window size must be equal to a value of 2 raised to a integer power.

| D7-D0              |

|--------------------|

| Limit Address Size |

The following Limit Address Size values are legal and correspond to a particular I/O address decoding window size.

|                                                                                                                | · ·         |

|----------------------------------------------------------------------------------------------------------------|-------------|

| Limit Address<br>Size Value                                                                                    | Window Size |

| 0000 0000 NULL. Do not pass any I/O transactions to unless base and limit checking is disabled function's COR. |             |

| 0000 0001                                                                                                      | 2 bytes     |

| 0000 0011                                                                                                      | 4 bytes     |

| 0000 0111                                                                                                      | 8 bytes     |

| 0000 1111                                                                                                      | 16 bytes    |

| 0001 1111                                                                                                      | 32 bytes    |

| 0011 1111                                                                                                      | 64 bytes    |

| 0111 1111                                                                                                      | 128 bytes   |

| 1111 1111                                                                                                      | 256 bytes   |

**Note:** The window created using the Base Register in conjuction with the Limit Register is naturally aligned to the size of the window (as specified by the Limit Register) and not to the value programmed in the Base Register. For example:

| Base Register | Limit Register | Window Range | Aligned to Base |

|---------------|----------------|--------------|-----------------|

| 0374h         | 07h            | 0370h-0377h  | No              |

| 03F8h         | 07h            | 03F8h-03FFh  | Yes             |

#### 5.2.2.2 LAN (National DP83902A) Mode Register Set

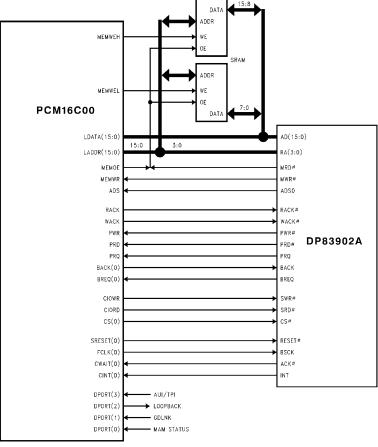

The LAN (National's DP83902A) Registers are only instantiated when the LAN Mode bit in the Function 0 Configuration Option Register is set to one (1). In LAN Mode, the Data I/O Register, the Miscellaneous Status Register, and the Reset Register support LAN functionality required within the PCM16C00. The LAN DP83902A feature also requires the PCM16C00 configuration registers to be set to the values shown in Table 5-2. This feature eases the use of existing National DP83902A software drivers and eliminates external glue logic. When in LAN Mode, a Remote DMA I/O Port and LDATA(15:0) to LADDR(15:0) latch mechanism is enabled for use by the DP83902A. The National DP83902A should be connected as function 0 on the PC Card and the use of the LAN registers is strongly recommended. Refer to Figure 5-2 for PCM16C00 and DP83902A hardware connections.

# Data I/O Register (Low and High Byte) [I/O: function 0 base + 0x010, 0x011]

This PCM16C00 register is 16 bits and is located in the I/O address space. The low byte of the Data I/O Register is located at I/O Address offset 0x10h above function 0's base address as given by the Function Base Address Register 0. The high byte is located at I/O Address offset 0x11h above function 0's base address.

This register is used by the DP83902A and the Client Driver when the DP83902A is operated in Programmed I/O Mode. In this mode, the Remote DMA I/O Port in the PCM16C00 is controlled by the DP83902A to read and/or write data into the Data I/O Register from local buffer SRAM on the PC Card. The DP83902 uses a local DMA controller to move data into and out of the SRAM. It then uses a remote DMA controller to handshake data between the SRAM and the system using this register as the posting space and the Remote DMA I/O Port.

FIGURE 5-2. PCM16C00 and DP83902A Connection Schematic

Note: The FCLK(0) connection requires that MCLK(0) frequency is within the operating range of the DP83902A (typically 20 MHz). This schematic assumes that two 32k x 8 SRAMs are organized as shown to form a word-wide ring buffer and a 16-bit memory organization. For detailed pin descriptions refer to the NSC DP83902A datasheet.

TL/F/11669-12

TABLE 5-2. Configuring the PCM16C00 Register

| Register Name              | Register Offset<br>(Hex) | Register Setting<br>(Binary) | Comment                                                        |  |

|----------------------------|--------------------------|------------------------------|----------------------------------------------------------------|--|

| Pin Polarity Register      | 03E4                     | 00X100X0                     | SRESET(0), CIOWR, CIORD, BHE active low; CWAIT(0) active high. |  |

| PMGR and FCLK              | 03E6                     | XXXX1001                     | FCLK(0) enabled; PCTL(0) on.                                   |  |

| BUS ARB                    | 03EC                     | 0001XX00                     | Pre-empt off; host- priority 1; f0- priority 0.                |  |

| MISC REG                   | 03F0                     | 0X1XXXXX                     | f0 Bus multiplexing enabled.                                   |  |

| Configuration Option Reg 0 | 1020                     | 01010111                     | f0 configured; Level IREQ; Base & limit enabled; IREQ enabled. |  |

Note: The CIS structure for the LAN function must be written such that bit 4 of Configuration Option Register 0 is set to a 1 (LAN-Mode enabled) when function 0 is configured during card enabling. The register values programmed into registers 3e4–3f0 are stored in EEPROM, and will be configured at boot-up. Function 1 values are listed as don't care (X), their settings have no effect on function 0.

# NATIONAL'S DP83902A PROGRAMMED I/O MODE OPERATION

#### **Packet Reception**

Once a packet has been received into the on-card SRAM, the DP83902A will issue an interrupt. The driver software will determine if a valid packet has been received by checking the DP83902A interrupt status register. The driver will then setup the Remote DMA Read operation (see Section 9.0 of the DP83902A data sheet). Note, the DP83902A should always be operated in 16-bit mode. The PCM16C00 will handle 8-bit accesses to the Data I/O Register. A Remote DMA Read is accomplished as follows:

- The DMA Setup Information is written into the DP83902A by the host.

- The DP83902A issues BREQ(0) to the PCM16C00.

- The PCM16C00 replies with a BACK(0) to the DP83902A.

- The DP83902A places the proper SRAM Address on LDATA(15:0).

- The DP83902A Latches this onto LA(15:0) by strobing ADS.

- The DP83902A issues a MRD# to the SRAM and the SRAM places the data on the LDATA(15:0) bus.

- The DP83902A asserts PWR# to the PCM16C00 which writes the data into the PCM16C00 Data I/O Register.

- The DP83902A issues a PRQ to the PCM16C00 telling the host that a DMA cycle needs acknowledged.

- Once the host began the DMA operation, it stays in polling mode waiting for the data to become valid in the Data I/O Register. In this interim, if the host tries to read the Data I/O Register, the PRQ remains low and WAIT# states are generated to extend the PCMCIA bus cycle.

- With PRQ asserted and the host trying to read the Data I/O Register, the PCM16C00 supplies the data to the host.

- Once both bytes are read by the host, the PCM16C00 issues a RACK# to the DP83902A.

- Once complete, the entire cycle is repeated until the entire packet has been transferred from the on-card SRAM to the host.

#### **Packet Transmission**

- The host assembles a packet for transmission and transfers them to the Data I/O register via I/O writes.

- The host sets-up a remote DMA channel by sending the starting address and byte count of the desired transfer to the DP83902A Remote DMA Registers.

- The host issues a Remote DMA Write command to the DP83902A.

- The DP83902A responds with a PRQ.

- The host writes into the Data I/O Register. If, however, the host attempts to write to the Data I/O Register before the DP83902A issues the PRQ, PRQ remains low and HWAIT# is asserted to extend the PCMCIA write cycle.

- Once the data is written into the Data I/O Register, the PCM16C00 issues a WACK# to the DP83902A.

- The DP83902A then asserts BREQ(0).

- The PCM16C00 replies with BACK(0).

- The DP83902A now places the on-card SRAM Address on LDATA(15:0) and asserts ADS to latch it onto LA(15:0).

- The DP83902A then issues a PRD# to place the Data I/O Register contents on LDATA(15:0).

- Then, the DP83902A issues a MEMWR# to the PCM16C00 which issues MEMWH# and MEMWL# to the SRAM.

- Finally, the DP83902A ends the cycle by deasserting PRD# and MEMWR#.

- This continues until the packet has been transferred from the host to on-card SRAM.

#### **DP83902A SHARED MEMORY MODE OPERATION**

In the Shared Memory Mode, the DP83902A uses its local DMA controller to move data between itself and the local buffer SRAM. In this mode, the SRAM is memory mapped into the system's memory space. The Data I/O Register will not be used to transfer data. Rather, common memory accesses from the host system are required.

#### **Packet Reception**

- During reception, the DP83902A Local DMA Controller will request the LDATA(15:0) bus by asserting BREQ(0).

- The PCM16C00 will respond with BACK(0).

- The DP83902A places the appropriate SRAM Address on the LDATA(15:0) bus and then strobes ADS to latch the address on LADDR(15:0).

- The DP83902A places the data onto LDATA(15:0).

- The DP83902A issues a MEMWR# to the PCM16C00 which asserts MEMWEH# and MEMWEL# to the SRAM

- The cycle ends when the DP83902A deasserts MEMWR#.

- This continues until the packet has been transferred into the SRAM

- At the end of the packet reception, the DP83902A determines if the packet should be accepted or rejected and then issues an interrupt to the host through the PCM16C00

- If accepted, the driver software operating on the host will transfer the packet data out of the SRAM to system memory. If not accepted, the error is recorded and the buffer space is recycled.

#### Packet Transmission

- The host transfers a packet from system memory to oncard SRAM.

- The host driver informs the DP83902A that a packet requires transmission.

- The DP83902A begins responding by requesting the bus using BREQ(0).

- The PCM16C00 asserts BACK(0) to the DP83902A.

- The DP83902A places an address on LDATA(15:0).

- The DP83902A latches this address to LADDR(15:0) by strobing ADS.

- The DP83902A issues MRD# to the SRAM and reads the SRAM data into the DP83902A FIFO. The FIFO data is serialized and transmitted over the network.

- This continues until the entire packet is transmitted over the network.

For a detailed description of remote DMA on the National DP83902A, refer to the National DP83902A Datasheet [1].

#### Miscellaneous Status Register

[I/O: Function 0 Base + 0x018]

This register is located at an I/O Address offset of 0x018h above the base address for function 0 when the LAN Mode bit is set to one (1) in the Function 0 Configuration Option Register. This register provides specific Ethernet LAN input and output through the DPORT(3:0) pins and includes a HWAIT# time-out watchdog timer.

| pe         |

|------------|

| out Enable |

| out Status |

| pa         |

|            |

| oopback    |

|            |

| Status     |

|            |

**Wait\_Tout Enable—**When this bit is set to a one (1), the HWAIT# time-out watchdog timer is enabled. In addition, the ability to set Intr in the Function Configuration Option Register 0, Intr in the Card Configuration Register, and IREQ# is enabled once the watchdog timer expires. The watchdog timer may expire if HWAIT# is asserted for more than approximately 11.2  $\mu$ s when MCLK(0) is set to 20 MHz for Ethernet LAN operation. This prevents the system from hanging due to prolonged HWAIT# assertions.

If this bit is reset to zero (0), Wait\_\_Tout and its associated interrupt capability is disabled.

Wait\_Tout Status—This bit indicates that a HWAIT# time out error has occurred. Software reads this bit in response to an interrupt to determine if a HWAIT# time out has occurred. If desired, a diagnostic error recovery routine may be implemented. If this bit is set to a one (1), a time-out has occurred. If zero (0), no time-out has occurred. Note, a write to any value in this register or a de-assertion of HWAIT# will clear this bit and reset the time-out counter. This bit is read only.

**AUI/TPI**—This read only bit is set to zero (0) if the Ethernet is in TPI Mode and set to one (1) if in AUI Mode.

**Loopback**—This write only bit is set to one (1) to perform DP83902A loopback mode testing. This bit is set to zero (0) otherwise.

**GDLNK**—This read only bit is only valid if in TPI mode (AUI/TPI is zero (0)). If reset to zero (0), the twisted pair link is good, if set to one (1), the twisted pair link fails.

**Mam Status—**This read only bit is set to zero (0) if no MAM is connected. The bit is set to one (1) if the MAM is connected (Twisted pair or Coax).

Note: The Miscellaneous Status Register bits 3 through 0 use the Digital Port Register bits 3 through 0 for physical connection to the AUI/TPI, Loopback, GDLNK, and Mam Status signals. When in LAN Mode, the Digital Port Direction Register (Attribute space) defaults to the following. It may not be read/written to in the attribute memory space when in I AN Mode.

| D7-D4    | D3        | D2         | D1        | D0        |

|----------|-----------|------------|-----------|-----------|

| Reserved | DPDIR3    | DPDIR2     | DPDIR1    | DPDIR0    |

| 0        | 0 (Input) | 1 (Output) | 0 (Input) | 0 (Input) |

The Digital Port Register (Attribute space) should be connected as follows

| D7-D4                 | D3         | D2          | D1       | D0                                       |

|-----------------------|------------|-------------|----------|------------------------------------------|

| Reserved              | DPORT3     | DPORT2      | DPORT1   | DPORT0                                   |

| No Pin<br>Connections | AUI/TPI to | Loopback to | GDLNK to | Connect MAM<br>Status to<br>DPORT(0) pin |

#### Reset Register

#### [I/O: Function 0 Base + 0x01F]

This read only register located at I/O Address offset 0x01Fh above the base address for function 0 is used to initiate a software reset to the DP83902A. When this register is read, the SRESET(0) (Note, in LAN Mode, the SRESET0 bit in the Pin Polarity Register should be programmed to one (1) to insure SRESET(0) is active low) bit is asserted. This forces National's DP83902A to enter the reset state.

#### 5.3 LOGIC DESCRIPTIONS

# 5.3.1 I/O Card Interface Logic for PCMCIA Host I/O Accesses

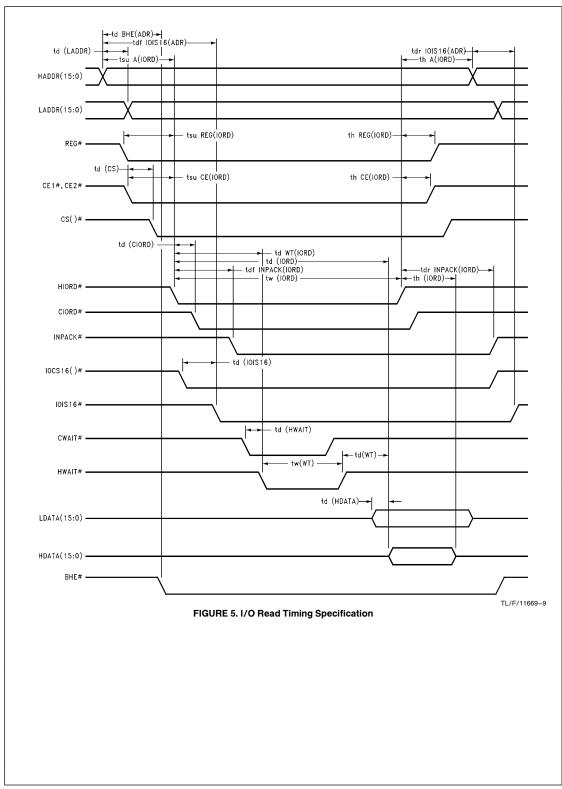

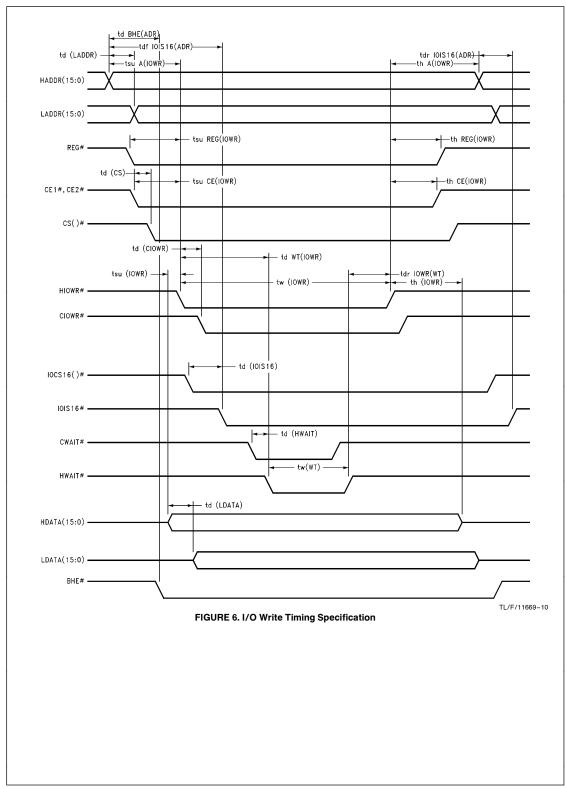

This block of logic generates card-side bus control and the appropriate chip-select signals based on the inputs from the PCMCIA host bus. The block's main function is I/O address decoding and operates with the PCMCIA version 2.1 standard. The Function's Base Registers 0,1 and Function Limit Registers 0,1 determine the location and size of the I/O window. Once set up, only PCMCIA accesses to the given function's I/O window will be passed to the device. All control signals are generated for the device for both read and write transactions. The selection of which function receives the PCMCIA transaction is implicit in the PCMCIA address and the particular I/O window the address falls within.

When a function is not selected, CIORD# and CIOWR# are forced to the in-active state. The chip selects CS(0)# and CS(1)# are held in-active for that port also. Once a valid PCMCIA access (read or write) occurs, the control and chip select signals become active.

The condition for an I/O read when a valid address is decoded is:

CIORD# = HIORD# + REG# + (CE1# \* CE2#)

The condition for an I/O write when a vald address is decoded is:

CIOWR# = HIOWR# + REG# + (CE1# \* CE2#)

#### **5.3.2 EEPROM INTERFACE**