## **PRELIMINARY**

March 1995

# PC87334VLJ/PC87334VJG SuperI/O™ 3.3V/5V Floppy Disk Controller, Dual UARTs, Infrared, IEEE1284 Parallel Port, and IDE Interface

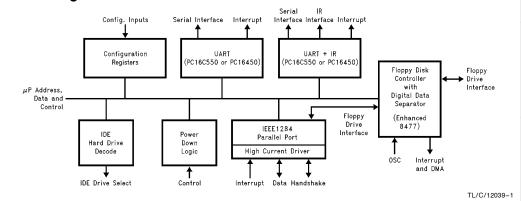

# **General Description**

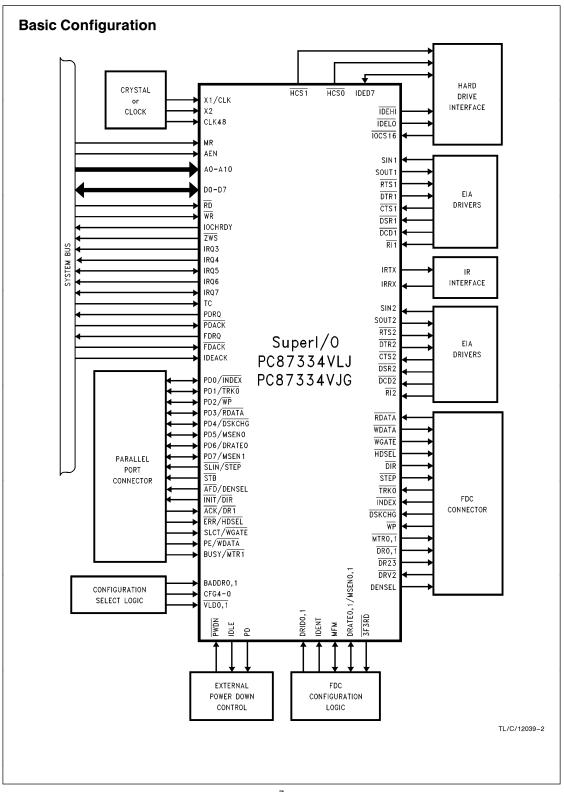

The PC87334VLJ/PC87334VJG is a single chip solution for most commonly used I/O peripherals in ISA, EISA and MicroChannel® based computers. It incorporates a Floppy Disk Controller (FDC), two full featured UARTs, an IEEE 1284 compatible parallel port and all the necessary control logic for an IDE interface. Standard PC-AT® address decoding for all the peripherals and a set of configuration registers are also implemented in this highly integrated member of the SuperI/O family. Advanced power management features, mixed voltage operation and integrated Serial-Infra-Red (SIR) support makes the PC87334 an ideal choice for low-power and/or portable personal computer applications.

The PC87334 FDC uses a high performance digital data separator eliminating the need for any external filter components. It is fully compatible with the PC8477 and incorporates a superset of DP8473, NEC  $\mu$ PD765 and N82077 floppy disk controller functions. All popular 5.25" and 3.5" floppy drives, including the 2.88 MB 3.5" floppy drive, are supported. In addition, automatic media sense and 2 Mbps tape drive support are provided by the FDC.

The two UARTs are fully NS16450 and NS16550 compatible. Both ports support MIDI baud rates and one port also supports IrDA and the HP SIR compliant signaling protocol. The parallel port is fully IEEE 1284 level 2 compatible. The SPP (Standard Parallel Port) is fully compatible with ISA, EISA and MicroChannel parallel ports. In addition to the

pabilities Port) modes are supported by the parallel port.

All IDE control signals with DMA support are provided by the PC87334. Only external signal buffers are required to implement a complete IDE interface. (Continued)

SPP, EPP (Enhanced Parallel Port) and ECP (Extended Ca-

### **Features**

- 100% compatible with ISA, EISA, and MicroChannel architectures

- The Floppy Disk Controller:

- Software compatible with the DP8473, the 765A and the N82077

- 16-byte FIFO (disabled by default)

- Burst and Non-Burst modes

- Perpendicular Recording drive support

- New high-performance internal digital data separator (no external filter components required)

- Low-power CMOS with enhanced power-down mode

- Automatic media-sense support, with full IBM TDR (Tape Drive Register) implementation

- Supports fast 2 Mbps and standard 1 Mbps/ 500 kbps/250 kbps tape drives

- The Bidirectional Parallel Port:

- Enhanced Parallel Port (EPP) compatible

- Extended Capabilities Port (ECP) compatible, including level 2 support

- Bidirectional under either software or hardware control

- Compatible with ISA, EISA, and MicroChannel architectures

Ability to multipley EDC signals on parallel part of the company of the compa

- Ability to multiplex FDC signals on parallel port pins allows use of an external Floppy Disk Drive (FDD)

- Includes protection circuit to prevent damage to the parallel port when a connected printer is powered up or is operated at a higher voltage (Continued)

## **Block Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation. SuperI/O™ is a trademark of National Semiconductor Corporation.

IBM®, MicroChannel®, PC-AT® and PS/2® are registered trademarks of International Business Machines Corporation

# **General Description (Continued)**

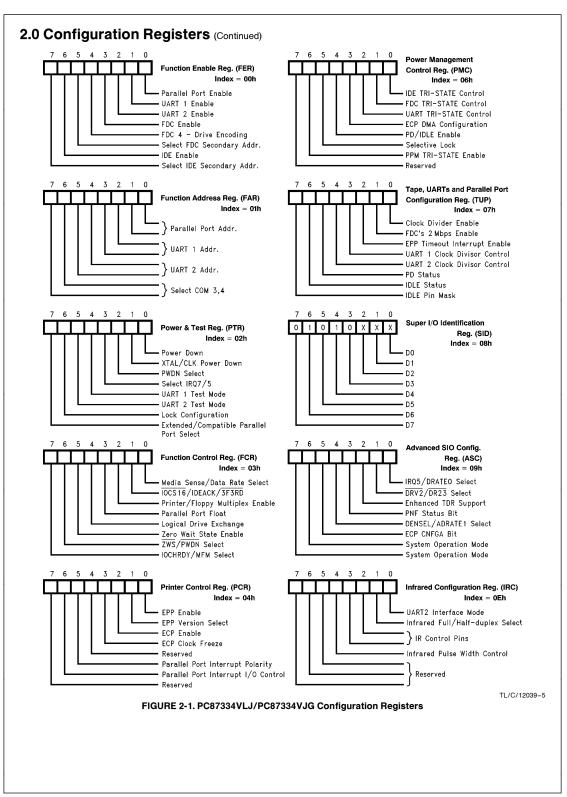

A set of eight configuration registers are provided to control various functions of the PC87334. These registers are accessed using two 8-bit wide index and data registers. The ISA I/O address of the register pair can be relocated using a power-up strapping option.

When idle, advanced power management features allows the PC87334 to enter extremely low power modes under hardware or software control. The PC87334 can operate from a 5V or a 3.3V power supply. An unique I/O cell structure allows the PC87334 to interface directly with 5V external components while operating from a 3.3V power supply.

## Features (Continued)

- The UARTs:

- Software compatible with the PC16550A and PC16450

- MIDI baud rate support

- Infrared support on UART2 (IrDA-compliant)

- The IDE Control Logic:

- All IDE control signals with DMA support provided.

Only external signal buffers required to implement full IDE interface

- The Address Decoder:

- Provides selection of all primary and secondary ISA addresses including COM1-4 and LPT1-3

- Enhanced Power Management:

- Special configuration registers for power-down

- Enhanced programmable power-down FDC command

- Auto power-down and wake-up modes

- 3 special pins for power management

- Typical current consumption during power-down is less than 10  $\,\mu\mathrm{A}$

- Reduced pin leakage current

- Mixed Voltage Support:

- Supports standard 5V operation

- Supports 3.3V operation

- Supports mixed internal 3.3V operation with 3.3V/5V external configuration

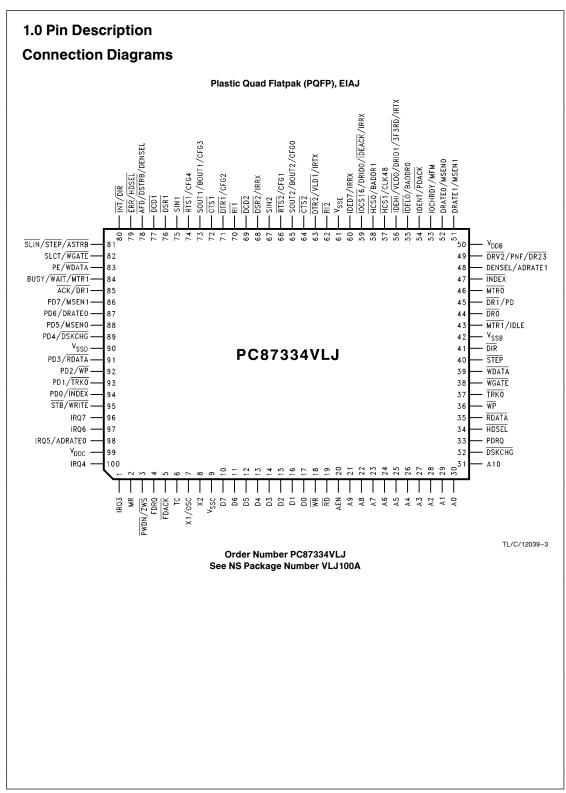

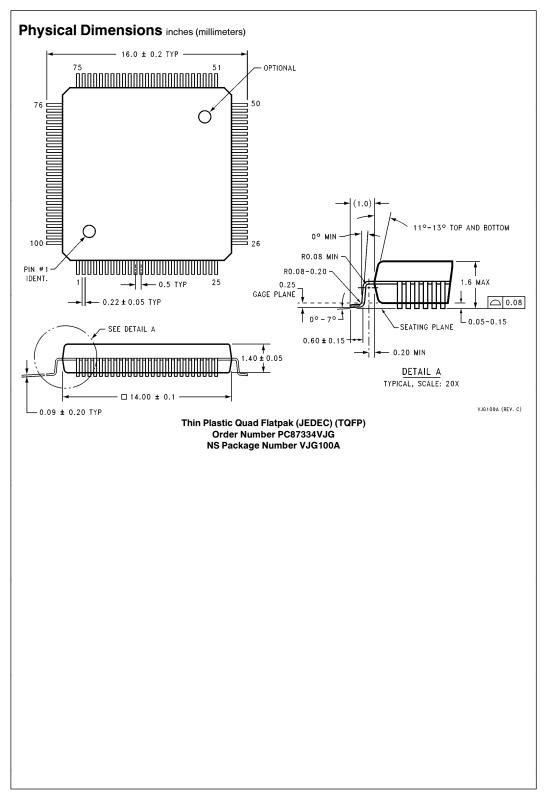

- 100-Pin TQFP package—PC87334VJG

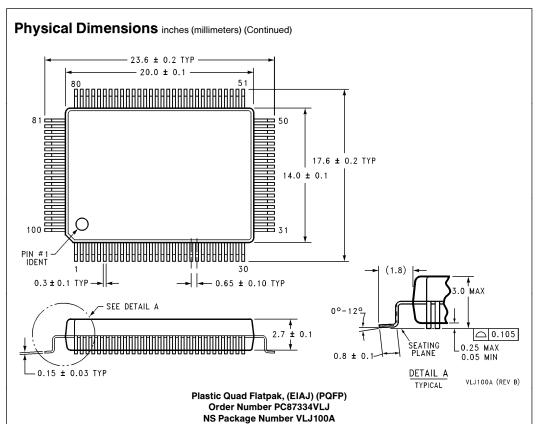

- 100-Pin PQFP package—PC87334VLJ

## **Table of Contents**

#### 1.0 PIN DESCRIPTION

## 2.0 CONFIGURATION REGISTERS

- 2.1 Overview

- 2.2 Software Configuration

- 2.3 Hardware Configuration

- 2.4 Index and Data Registers

- 2.5 Base Configuration Registers

- 2.5.1 Function Enable Register (FER)

- 2.5.2 Function Address Register (FAR)

- 2.5.3 Power and Test Register (PTR)

- 2.5.4 Function Control Register (FCR)

- 2.5.5 Printer Control Register (PCR)

- 2.5.6 Power Management Control Register

- 2.5.7 Tape, UARTs and Parallel Port

- Configuration Register (TUP) 2.5.8 SIO Identification Register (SID)

- 2.5.9 Advanced SuperI/O Configuration Register (ASC)

- 2.5.10 Infrared Configuration Register (IRC)

- 2.6 Power-Down Options

- 2.6.1 Recommended Power-Down Methods—Group 1

- 2.6.2 Recommended Power-Down Methods—Group 2

- 2.7 Power-Up Procedure and Considerations

- 2.7.1 Crystal Stabilization

- 2.7.2 UART Power-Up

- 2.7.3 FDC Power-Up

## 3.0 FDC REGISTER DESCRIPTION

- 3.1 FDC Control Registers

- 3.1.1 Status Registger A (SRA) Read Only

- 3.1.2 Status Register B (SRB) Read Only

- 3.1.3 Digital Output Register (DOR) Read/Write

- 3.1.4 Tape Drive Register (TDR) Read/Write

- 3.1.5 Main Status Register (MSR) Read Only

- 3.1.6 Data Rate Select Register (DSR) Write Only

- 3.1.7 Data Register (FIFO) Read/Write

- 3.1.8 Digital Input Register (DIR) Read Only

- 3.1.9 Configuration Control Register (CCR) Write Only

- 3.2 Result Phase Status Registers

- 3.2.1 Status Register 0 (ST0)

- 3.2.2 Status Register 1 (ST1)

- 3.2.3 Status Register 2 (ST2)

- 3.2.4 Status Register 3 (ST3)

## 4.0 FDC COMMAND SET DESCRIPTION

- 4.1 Command Description

- 4.1.1 Configure Command

- 4.1.2 Dumpreg Command

- 4.1.3 Format Track Command

- 4.1.4 Invalid Command

- 4.1.5 Lock Command

- 4 1 6 Mode Command

- 4.1.7 NSC Command

- 4.1.8 Perpendicular Mode Command

- 4.1.9 Read Data Command

- 4.1.10 Read Deleted Data Command

- 4.1.11 Read ID Command

- 4.1.12 Read A Track Command

- 4.1.13 Recalibrate Command

- 4.1.14 Relative Seek Command

- 4.1.15 Scan Commands

- 4.1.16 Seek Command

- 4.1.17 Sense Drive Status Command

- 4.1.18 Sense Interrupt Command

- 4.1.19 Set Track Command

- 4.1.20 Specify Command

- 4.1.21 Verify Command

- 4.1.22 Version Command

- 4.1.23 Write Data Command

- 4.1.24 Write Deleted Data

- 4.2 Command Set Summary

- 4.3 Mnemonic Definitons for FDC Commands

## **5.0 FDC FUNCTIONAL DESCRIPTION**

- 5.1 Microprocessor Interface

- 5.2 Modes of Operation5.3 Controller Phases

- 5.3.1 Command Phase

- 5.3.2 Execution Phase

- 5.3.2.1 DMA Mode—FIFO Disabled

- 5.3.2.2 DMA Mode—FIFO Enabled

- 5.3.2.3 Interrupt Mode—FIFO Disabled

- 5.3.2.4 Interrupt Mode—FIFO Enabled

- 5.3.2.5 Software Polling

- 5.3.3 Result Phase

- 5.3.4 Idle Phase

- 5.3.5 Drive Polling Phase

- 5.4 Data Separator

- 5.5 Crystal Oscillator

- 5.6 Perpendicular Recording Mode

- 5.7 Data Rate Selection

- 5.8 Write Precompensation

- 5.9 FDC Low Power Mode Logic

- 5.10 Reset Operation

# **Table of Contents (Continued)**

## **6.0 SERIAL PORTS**

- 6.1 Serial Port Registers

- 6.2 Line Control Register (LCR)

- 6.3 Programmable Baud Rate Generator

- 6.4 Line Status Register (LSR)

- 6.5 FIFO Control Register

- 6.6 Interrupt Identification Register (IIR)

- 6.7 Interrupt Enable Register (IER)

- 6.8 MODEM Control Register (MCR)

- 6.9 MODEM Status Register (MSR)

- 6.10 Scratchpad Register (SCR)

## 7.0 PARALLEL PORT

- 7.1 Introduction

- 7.2 Data Register (DTR)

- 7.3 Status Register (STR)

- 7.4 Control Register (CTR)

- 7.5 Enhanced Parallel Port Operation

- 7.6 Extended Capabilities Parallel Port (ECP)

- 7.6.1 Introduction

- 7.6.2 Software Operation

- 7.7 Register Definitions

- 7.8 Software Controlled Data Transfer (Modes 000 and 001)

- 7.9 Automatic Data Transfer (Modes 010 and 011)

- 7.9.1 Forward Direction (Bit 5 of DCR = 0)

- 7.9.2 ECP (Forward) Write Cycle

- 7.9.3 Backward Direction (bit 5 of DCR is 1)

- 7.9.4 ECP (Backward) Read Cycle

- 7.10 FIFO Test Access (Mode 110)

- 7.11 Configuration Registers Access (Mode 111)

- 7.12 Interrupt Generation

# 8.0 INTEGRATED DEVICE ELECTRONICS INTERFACE (IDE)

- 8.1 Introduction

- 8.2 IDE Signals

## 9.0 SERIAL INFRARED INTERFACE (SIR)

## 10.0 ELECTRICAL CHARACTERISTICS

- 10.1 DC Electrical Characteristics

- 10.2 DC Electrical Characteristics

- 10.3 AC Electrical Characteristics

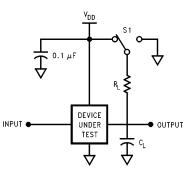

- 10.3.1 AC Test Conditions

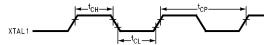

- 10.3.2 Clock Timing

- 10.3.3 Microprocessor Interface Timing

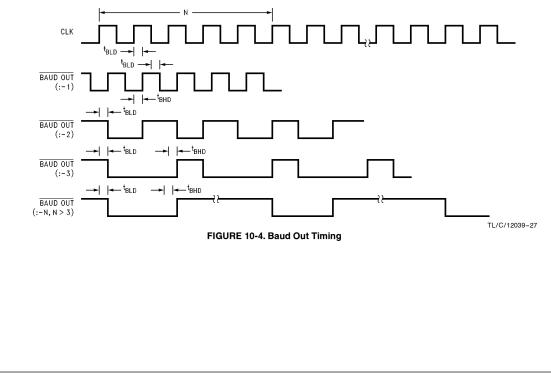

- 10.3.4 Baud Out Timing

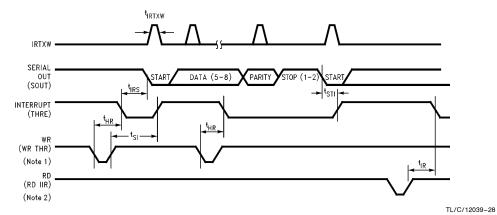

- 10.3.5 Transmitter Timing

- 10.3.6 Receiver Timing

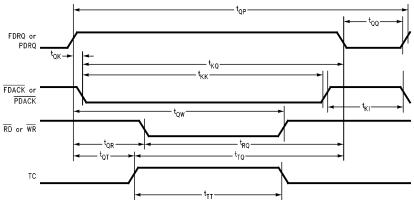

- 10.3.7 MODEM Control Timing

- 10.3.8 DMA Timing

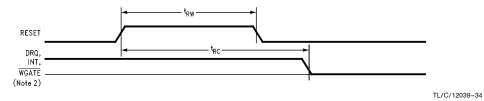

- 10.3.9 Reset Timing

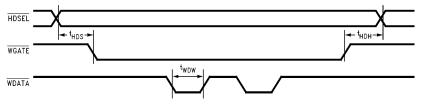

- 10.3.10 Write Data Timing

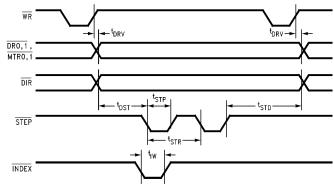

- 10.3.11 Drive Control Timing

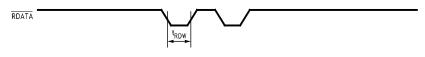

- 10.3.12 Read Data Timing

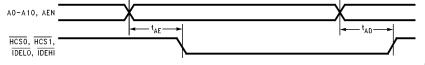

- 10.3.13 IDE Timing

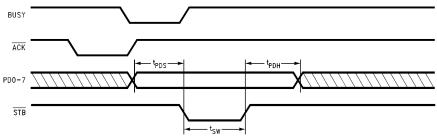

- 10.3.14 Parallel Port Timing

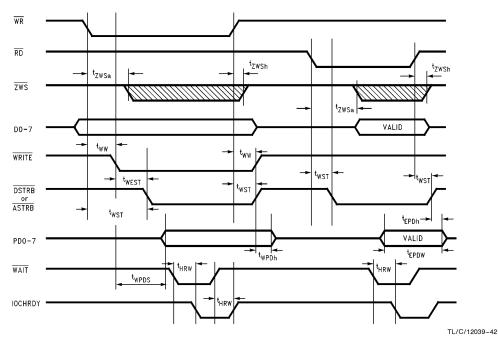

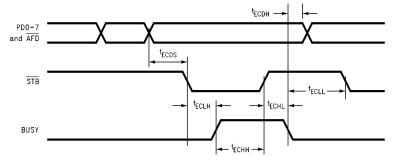

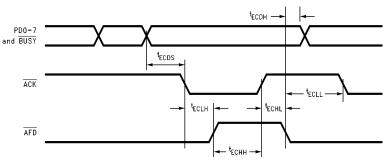

- 10.3.15 Enhanced Parallel Port Timing

- 10.3.16 Extended Capabilities Port Timing

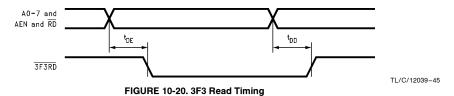

- 10.3.17 3F3 Read Timing

# **List of Figures**

|              | List of Figures                                                     |

|--------------|---------------------------------------------------------------------|

| FIGURE 2-1   | PC87334 Configuration Registers                                     |

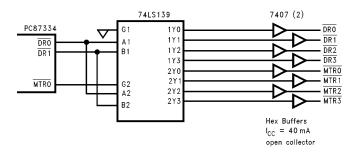

| FIGURE 2-2   | PC87334 Four Floppy Drive Circuit Example                           |

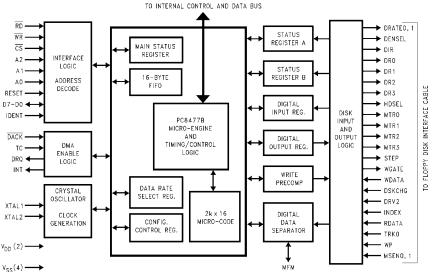

| FIGURE 3-1   | FDC Functional Block Diagram                                        |

| FIGURE 4-1   | FDC Command Structure                                               |

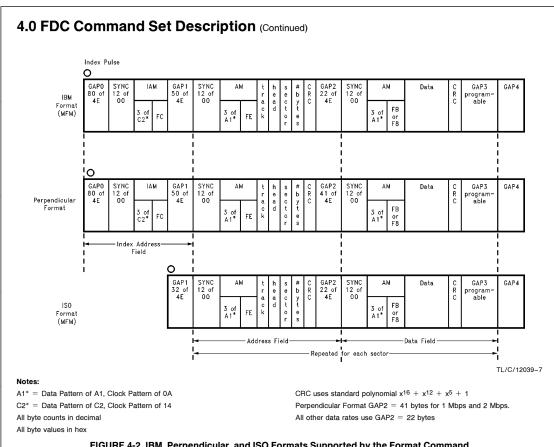

| FIGURE 4-2   | IBM, Perpendicular, and ISO Formats Supported by the Format Command |

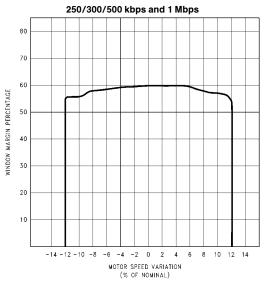

| FIGURE 5-1   | PC87334 Dynamic Window Margin Performance                           |

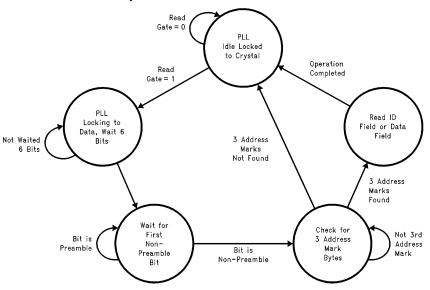

| FIGURE 5-2   | Read Data Algorithm—State Diagram                                   |

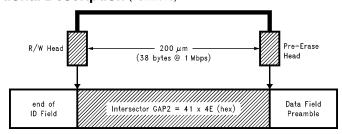

| FIGURE 5-3   | Perpendicular Recording Drive R/W Head and Pre-Erase Head           |

| FIGURE 6-1   | PC87334 Composite Serial Data                                       |

| FIGURE 6-2   | Reciever FIFO Trigger Level                                         |

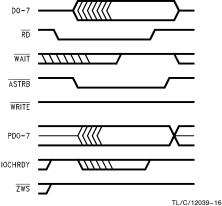

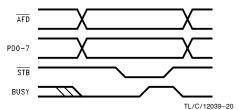

| FIGURE 7-1   | EPP 1.7 Address Write                                               |

| FIGURE 7-2   | EPP 1.7 Address Read                                                |

| FIGURE 7-3   | EPP Write with ZWS                                                  |

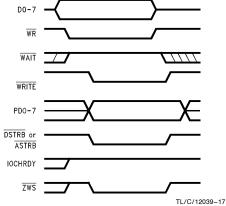

| FIGURE 7-4   | EPP 1.9 Address Write                                               |

| FIGURE 7-5   | EPP 1.9 Address Read                                                |

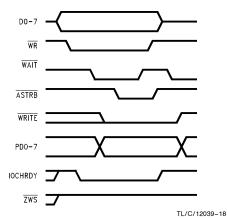

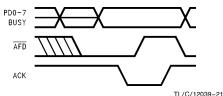

| FIGURE 7-6   | ECP (Forward) Write Cycle                                           |

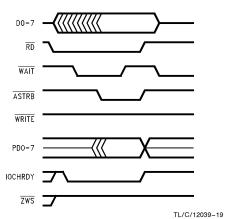

| FIGURE 7-7   | ECP (Backward) Read Cycle                                           |

| FIGURE 8-1   | IDE Interface Signal Equations (Non-DMA)                            |

| FIGURE 10-1  | Clock Timing                                                        |

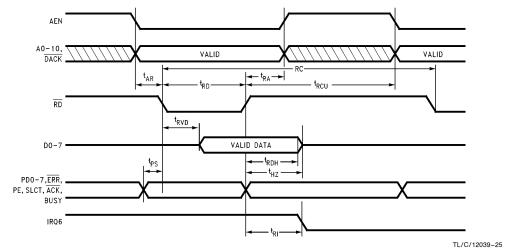

| FIGURE 10-2  | Microprocessor Read Timing                                          |

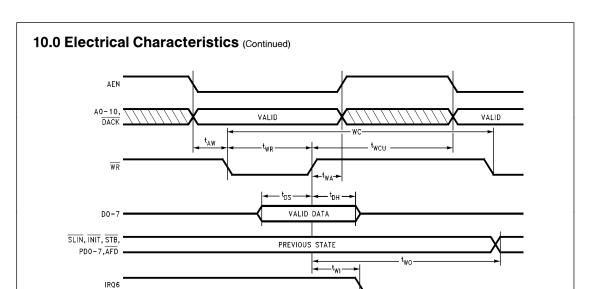

| FIGURE 10-3  | Microprocessor Write Timing                                         |

| FIGURE 10-4  | Baud Out Timing                                                     |

| FIGURE 10-5  | Transmitter Timing                                                  |

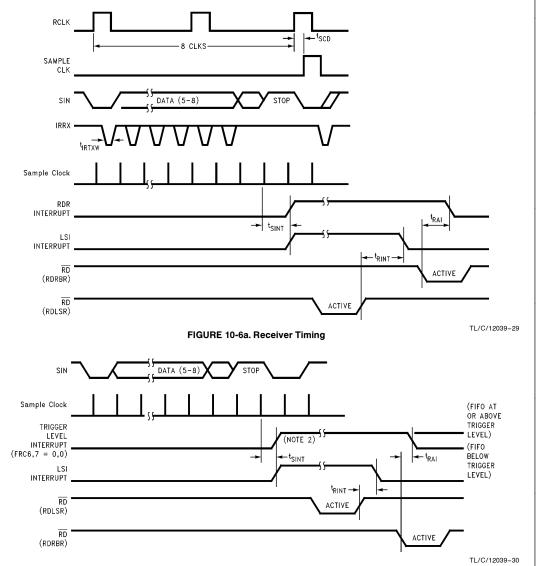

| FIGURE 10-6a | Receiver Timing                                                     |

| FIGURE 10-6b | Mode Receiver Timing                                                |

| FIGURE 10-6c | Timeout Receiver Timing                                             |

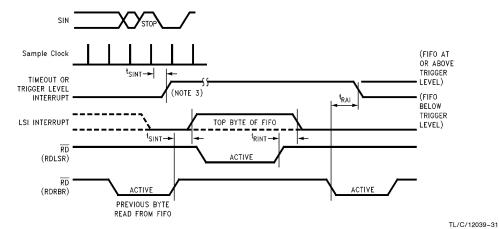

| FIGURE 10-7  | MODEM Control Timing                                                |

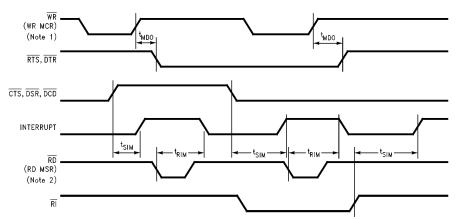

| FIGURE 10-8  | DMA Timing                                                          |

| FIGURE 10-9  | Reset Timing                                                        |

| FIGURE 10-10 | Write Data Timing                                                   |

| FIGURE 10-11 | Drive Control Timing                                                |

| FIGURE 10-12 | Read Data Timing                                                    |

| FIGURE 10-13 | IDE Timing                                                          |

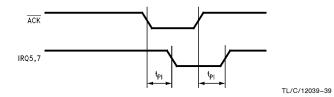

| FIGURE 10-14 | Compatible Mode Parallel Port Interrupt Timing                      |

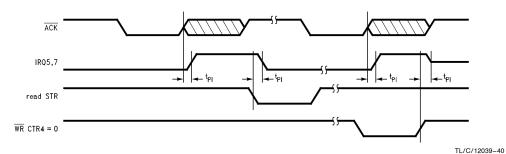

| FIGURE 10-15 | Extended Mode Parallel Port Interrupt Timing                        |

| FIGURE 10-16 | Typical Parallel Port Data Exchange                                 |

| FIGURE 10-17 | Enhanced Parallel Port Timing                                       |

| FIGURE 10-18 | ECP Parallel Port Forward Timing Diagram                            |

| FIGURE 10-19 | ECP Parallel Port Backward Timing Diagram                           |

| FIGURE 10-20 | 3F3 Read Timing                                                     |

|              |                                                                     |

| - |                         |                                                                              |

|---|-------------------------|------------------------------------------------------------------------------|

|   |                         | List of Tables                                                               |

|   | TABLE 1-1               | Pin Descriptions (Alphabetical)                                              |

|   | TABLE1-2                | SIR Pin Allocation                                                           |

|   | TABLE 2-1               | Default Configurations Controlled by Hardware                                |

|   | TABLE 2-2               | Index and Data Register Optional Locations                                   |

|   | TABLE 2-3               | Encoded Drive and Motor Pin Information                                      |

|   | TABLE 2-4               | Primary and Secondary Drive Address Selection                                |

|   | TABLE 2-5               | Parallel Port Addresses                                                      |

|   | TABLE 2-6               | COM Port Selection for UART1                                                 |

|   | TABLE 2-7               | COM Port Selection for UART2                                                 |

|   | TABLE 2-8               | Address Selection for COM3 and COM4                                          |

|   | TABLE 2-9               | Logical Drive Exchange                                                       |

|   | TABLE 2-10              | Parallel Port Mode                                                           |

|   | TABLE 2-11              | Methods to Achieve Group 1 Power-Down Modes                                  |

|   | TABLE 3-1               | Register Description and Addresses                                           |

|   | TABLE 3-2               | Drive Enable Values                                                          |

|   | TABLE 3-3               | TDR Operation Modes                                                          |

|   | TABLE 3-4               | Media ID Bit Functions                                                       |

|   | TABLE 3-5               | Tape Drive Assignment Values                                                 |

|   | TABLE 3-6               | Write Precompensation Delays                                                 |

|   | TABLE 3-7               | Default Precompensation Delays                                               |

|   | TABLE 3-8               | Data Rate Select Encoding                                                    |

|   | TABLE 4-1               | Typical Format Gap Length Values                                             |

|   | TABLE 4-2               | Typical Format GAP3 Length Values Based on PC Compatible Diskette Media      |

|   | TABLE 4-3               | DENSEL Default Encoding                                                      |

|   | TABLE 4-4               | DENSEL Encoding                                                              |

|   | TABLE 4-5               | Head Settle Time Calculation                                                 |

|   | TABLE 4-6               | Effect of Drive Mode and Data Rate on Format and Write Commands              |

|   | TABLE 4-7               | Effect of GAP and WG on Format and Write Commands                            |

|   | TABLE 4-8               | Sector Size Selection                                                        |

|   | TABLE 4-9               | SK Effect on the Read Data Command                                           |

|   | TABLE 4-10              |                                                                              |

|   | TABLE 4-11              | SK Effect on the Read Deleted Data Command                                   |

|   | TABLE 4-12              | •                                                                            |

|   | TABLE 4-13              |                                                                              |

|   | TABLE 4-14              | ·                                                                            |

|   | TABLE 4-15              | ·                                                                            |

|   |                         | Step Rate Time (SRT) Values                                                  |

|   | TABLE 4-17              |                                                                              |

|   | TABLE 4-18              |                                                                              |

|   | TABLE 4-19              | •                                                                            |

|   | TABLE 6-1               | PC87334 UART Register Addresses (AEN = 0)                                    |

|   | TABLE 6-2               | PC87334 Register Summary for an Individual UART Channel                      |

|   | TABLE 6-3               | PC87334 UART Reset Configuration                                             |

|   | TABLE 6-4               | PC87334 UART Divisors, Baud Rates and Clock Frequencies                      |

|   | TABLE 6-5               | PC87334 Interrupt Control Functions                                          |

|   | TABLE 7-1               | Parallel Interface Register Addresses Standard Parallel Port Modes Selection |

|   | TABLE 7-2<br>TABLE 7-3  |                                                                              |

|   |                         | SPP Data Register Read and Write Modes                                       |

|   | TABLE 7-4               | Parallel Port Reset States  EDD Pogisters                                    |

|   | TABLE 7-5               | EPP Registers Parallel Port Pin Out                                          |

|   | TABLE 7-6               |                                                                              |

|   | TABLE 7-7               | ECP Registers Summary  IDE Registers and Their ISA Addresses                 |

|   | TABLE 8-1<br>TABLE 10-1 | ·                                                                            |

|   |                         | Nominal t <sub>ICP</sub> , t <sub>DRP</sub> Values                           |

|   |                         |                                                                              |

TABLE 10-2 Minimum t<sub>WDW</sub> Values

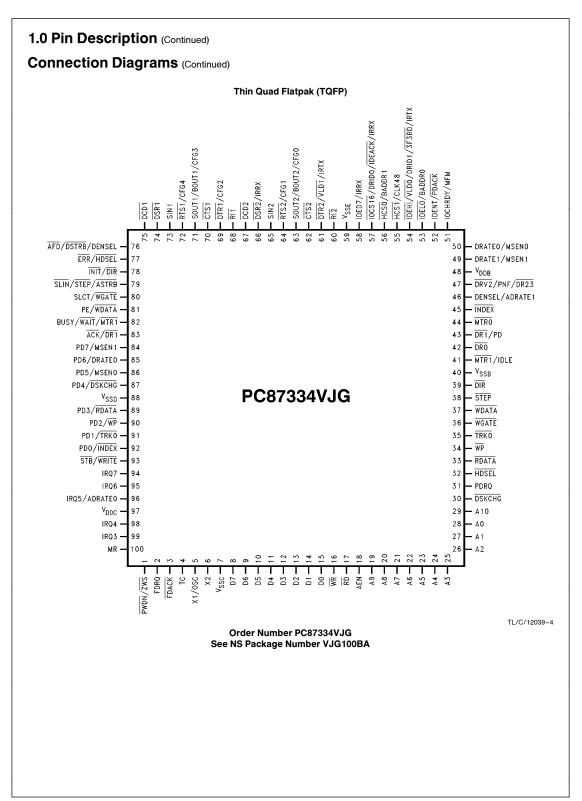

# 1.0 Pin Description (Continued)

TABLE 1-1. Pin Descriptions (Alphabetical)

| Symbol    | PQFP<br>Pin              | TQFP<br>Pin             | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|-----------|--------------------------|-------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3F3RD     | 56                       | 54                      | 0   | 3F3 Read. This pin is used to implement the 3F3 Tape Drive Register (TDR) externally. 3F3RD is active when read PIO, from 3F3 hex address, is active (A10 is not decoded) and AEN = 0. This pin is configured when bit 1 of Function Control Register (FCR) is 1. (This pin is shared with the IDEHI, IRTX and DRID1 signals.)                                                                                                                                                                  |  |  |  |  |

| ADRATE0,1 | 98, 48                   | 96, 46                  | 0   | Additional Data Rate 0,1. These outputs are similar to DRATE0,1. They are provided in addition to DRATE0,1. They reflect the currently selected FDC data rate (bits 0 and 1 in the Configuration Control Register (CCR) or the Data Rate Select Register (DSR), whichever was written to last). ADRATE0 is configured when bit 0 of ASC is 1. ADRATE1 is configured when bit 4 of the Advanced SIO Configuration Register (ASC) is 1. (These pins are shared with the IRQ5 and DENSEL signals.) |  |  |  |  |

| A10-A0    | 21–31                    | 19-29                   | ı   | Address. These microprocessor address lines determine which internal register is accessed. A0–A10 are don't cares during a DMA transfer.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| ACK       | 85                       | 83                      | 1   | <b>Acknowledge.</b> This input is pulsed low by a connected printer to indicate that it has received data from the parallel port. This pin has a nominal 25 k $\Omega$ pull-up resistor attached to it. (This pin is shared with $\overline{DR1}$ . See Table 7-5 for further information.)                                                                                                                                                                                                     |  |  |  |  |

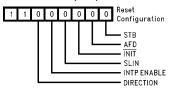

| ĀFD       | 78                       | 76                      | 1/0 | <b>Automatic Feed XT.</b> When this signal is low the connected printer should automatically line feed after each line is printed. This pin is in a TRI-STATE® condition 10 ns after a 0 is loaded into the corresponding Control Register bit. The system should pull this pin high using a 4.7 k $\Omega$ resistor. (See DSTRB and Table 7-5 for further information.)                                                                                                                        |  |  |  |  |

| AEN       | 20                       | 18                      | 1   | Address Enable. This input disables function selection via A10-A0 when it is high. Access during DMA transfer is NOT affected by this pin.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

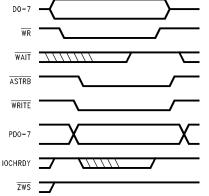

| ASTRB     | 81                       | 79                      | 0   | Address Strobe. This signal is used in EPP mode as an address strobe. It is active low. (See SLIN and Table 7-5 for further information.)                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| BADDR0,1  | 55, 58                   | 53, 56                  | I   | <b>Base Address.</b> These bits determine one of four base addresses from which the Index and Data Registers are offset (See Table 2-2). An internal pull-down resistor of 30 k $\Omega$ is present on this pin. Use a 10 k $\Omega$ resistor to pull this pin to V <sub>CC</sub> .                                                                                                                                                                                                             |  |  |  |  |

| BOUT1,2   | 73, 65                   | 71, 63                  | 0   | <b>BAUD Output.</b> This multi-function pin provides the associated serial channel Baud Rate generator output signal, when test mode is selected in the Power and Test Configuration Register and the DLAB bit (LCR7) is set. After Master Reset this pin provides the SOUT function. (See SOUT and CFG0-4 for further information.)                                                                                                                                                            |  |  |  |  |

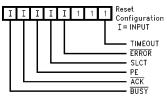

| BUSY      | 84                       | 82                      | I   | <b>Busy.</b> This pin is set high by the printer when it cannot accept another character. It has a nominal 25 $\rm K\Omega$ pull-down resistor attached to it. (See $\rm \overline{WAIT}$ and Table 7-5 for further information.)                                                                                                                                                                                                                                                               |  |  |  |  |

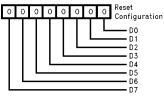

| CFG0-4    | 65, 66,<br>71, 73,<br>74 | 63, 64<br>69, 71,<br>72 | ı   | <b>Configuration on Power-up.</b> These CMOS inputs select 1 of 32 default configurations in which the PC87334VLJ/PC87334VJG powers-up (See Table 2-1). An internal pull-down resistor of 30 k $\Omega$ is present on each pin. Use a 10 k $\Omega$ resistor to pull these pins to V <sub>CC</sub> .                                                                                                                                                                                            |  |  |  |  |

| CLK48     | 57                       | 55                      | I   | <b>Clock 48.</b> This pin is the CLK48 reset strap option. During reset the value of this pin is latched into bit 0 of TUP (CLK48 bit). A 30 k $\Omega$ internal pull-down resistor is present on this pin. Use a 10 k $\Omega$ resistor to pull it high during reset.                                                                                                                                                                                                                          |  |  |  |  |

| CTS1,2    | 72, 64                   | 70, 62                  | I   | Clear to Send. When low this indicates that the MODEM or data set is ready to excha data. The CTS signal is a MODEM status input whose condition the CPU can test by reading bit 4 (CTS) of the MODEM Status Register (MSR) for the appropriate serial channel. Bit 4 is the complement of the CTS signal. Bit 0 (DCTS) of the MSR indicates whether the CTS input has changed state since the previous reading of the MSR. CTS no effect on the transmitter.                                   |  |  |  |  |

| D7-D0     | 10–17                    | 8–15                    | 1/0 | Note: Whenever the DCTS bit of the MSR is set an interrupt is generated if MODEM Status interrupts are enabled.  Data. Bi-directional data lines to the microprocessor. D0 is the LSB and D7 is the MSB.  These signals all have 24 mA (sink) buffered outputs.                                                                                                                                                                                                                                 |  |  |  |  |

| Symbol                     | PQFP<br>Pin | TQFP<br>Pin | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|----------------------------|-------------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DCD1,2                     | 77, 69      | 75, 67      | I   | Data Carrier Detect. When low this signal indicates that the MODEM or data set has detected the data carrier. The $\overline{DCD}$ signal is a MODEM status input whose condition the CPU can test by reading bit 7 (DCD) of the MODEM Status Register (MSR) for the appropriate serial channel. Bit 7 is the complement of the $\overline{DCD}$ signal. Bit 3 (DDCD) of the MSR indicates whether the $\overline{DCD}$ input has changed state since the previous reading of the MSR.  Note: Whenever the DDCD bit of the MSR is set, an interrupt is generated if MODEM Status interrupts are enabled. |  |  |  |

| DENSEL<br>Normal<br>Mode   | 48          | 46          | 0   | Density Select. Indicates that a high FDC density data rate (500 kbps, 1 Mbps or 2 Mbps) or a low density data rate (250 kbps or 300 kbps) is selected. DENSEL is active high for high density (5.25" drives) when IDENT is high, and active low for high density (3.5" drives) when IDENT is low. DENSEL is also programmable via the Mode command (see Section 4.2.6).                                                                                                                                                                                                                                 |  |  |  |

| DENSEL<br>PPM<br>Mode      | 78          | 76          | 0   | ity Select. This pin provides an additional Density Select signal in PPM Mode when = 0. (See AFD and Table 7-5 for further information.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| DIR<br>Normal<br>Mode      | 41          | 39          | 0   | ection. This output determines the direction of the floppy disk drive (FDD) head vement (active = step in, inactive = step out) during a seek operation. During reads or tes, DIR is inactive.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| DIR<br>PPM<br>Mode         | 80          | 78          | 0   | <b>rection.</b> This pin provides an additional direction signal in PPM Mode when PNF $= 0$ . ( $\overline{\text{IT}}$ and Table 7-5 for further information.)                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| DR0,1<br>Normal<br>Mode    | 44, 45      | 42, 43      | 0   | <b>Drive Select 0,1.</b> These are the decoded Drive Select outputs that are controlled by the Digital Output Register bits D0, D1. The Drive Select outputs are gated with DOR bits 4–7. These are active low outputs. They are encoded with information to control four FDDs wher bit 4 of the Function Enable Register (FER) is set. (See MTR0,1 for more information.) DR0 exchanges logical drive values with DR1 when bit 4 of Function Control Register (FCR) is set (See Table 7-5 for further information.)                                                                                     |  |  |  |

| DR1<br>PPM<br>Mode         | 85          | 83          | 0   | Drive Select 1. This pin provides an additional Drive Select signal in PPM Mode when PNF = 0. It is drive select 1 when bit 4 of FCR is 0. It is drive select 0 when bit 4 of FCR is 1. This signal is active low. (See ACK and Table 7-5 for further information.)                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| DRATE0,1<br>Normal<br>Mode | 52, 51      | 50, 49      | 0   | Data Rate 0,1. These outputs reflect the currently selected FDC data rate (bits 0 and 1 in the Configuration Control Register (CCR) or the Data Rate Select Register (DSR), whichever was written to last). The pins are to                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| DRATE0<br>PPM<br>Mode      | 87          | 85          | 0   | $\label{eq:DataRate 0.} \textbf{Data Rate 0.} \ \textbf{This pin provides an additional Data Rate signal, in PPM mode, when PNF} = 0. \\ \textbf{(See PD6 and Table 7-5 for further information.)}$                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| DRID0,1                    | 59, 56      | 54, 54      | ı   | <b>Drive ID.</b> These pins accept input from the floppy disk drive which indicates the type of drive in use. These pins should be tied low if they are not used. DRID1 is configured when bit 2 of ASC is 1 and bit 1 of ASC is 0. (See <u>IOCS16</u> , <u>IDEACK</u> , <u>IDEHI</u> , <u>VLD0</u> , <u>3F3RD</u> , IRTX and IRRX for further information.)                                                                                                                                                                                                                                             |  |  |  |

| DRV2                       | 49          | 47          | I   | Drive2. This input indicates whether a second floppy disk drive has been installed. The state of this pin is available from Status Register A in PS/2® mode. (See PNF for further information.)                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| DR23                       | 49          | 47          | I   | Drive 2 or 3. DR23 is asserted when either Drive 2 or Drive 3 is accessed (except during logical drive exchange, see bit 3 of TDR). This pin is configured when bit 1 of ASC is 0. (See DRV2 and PNF for further information.)                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Symbol                   | PQFP<br>Pin | TQFP<br>Pin | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------------------------|-------------|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DSKCHG<br>Normal<br>Mode | 32          | 30          | I   | Disk Change. This input indicates if the drive door has been opened. The state of this pin is available from the Digital Input register. This pin can also be configured as the Read Gate (RGATE) data separator diagnostic input via the Mode command (see Section 4.2.6).                                                                                                                                                                                                                                                  |  |  |  |  |

| DSKCHG<br>PPM<br>Mode    | 89          | 87          | ı   | Disk Change. This pin provides an additional Disk Change signal in PPM Mode when PNF = 0. (See PD4 and Table 7-5 for further information.)                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| DSR1,2                   | 76, 68      | 74, 66      | I   | Data Set Ready. When low this signal indicates that the data set or MODEM is ready to establish a communications link. The $\overline{DSR}$ signal is a MODEM status input whose condition the CPU can test by reading bit 5 (DSR) of the MODEM Status Register (MSR) for the appropriate channel. Bit 5 is the complement of the $\overline{DSR}$ signal. Bit 1 (DDSR) of the MSR indicates whether the $\overline{DSR}$ input has changed states since the previous reading of the MSR (See IRRX for further information.) |  |  |  |  |

| DSTRB                    | 78          | 76          | 0   | ote: Whenever the DDSR bit of the MSR is set, an interrupt is generated If MODEM Status interrupts are enabled.  Pata Strobe. This signal is used in EPP mode as a data strobe. It is active low. (See $\overline{\text{AFD}}$ are lable 7-5 for further information.)                                                                                                                                                                                                                                                       |  |  |  |  |

| DTR1,2                   | 71, 63      | 69, 61      | 0   | Data Terminal Ready. When low, this output indicates to the MODEM or data set that the UART is ready to establish a communications link. The DTR signal can be set to an active loby programming bit 0 (DTR) of the MODEM Control Register to a high level. A Master Rese operation sets this signal to its inactive (high) state. Loop mode operation holds this signal to its inactive state. (See CFG4–0 and IRTX for further information.)                                                                               |  |  |  |  |

| ERR                      | 79          | 77          | ı   | <b>Error.</b> A connected printer sets this input low when it has detected an error. This pin has a nominal 25 k $\Omega$ pull-up resistor attached to it. (See $\overline{\text{HDSEL}}$ and Table 7-5 for further information.)                                                                                                                                                                                                                                                                                            |  |  |  |  |

| FDACK                    | 5           | 3           | I   | DMA Acknowledge. Active low input to acknowledge the FDC DMA request and enable th RD and WR inputs during a DMA transfer. When in PC-AT® or Model 30 mode, this signal is enabled by bit D3 of the Digital Output Register (DOR). When in PS/2 mode, FDACK is always enabled, and bit D3 of the DOR is reserved. FDACK should be held high during I/O accessed.                                                                                                                                                             |  |  |  |  |

| FDRQ                     | 4           | 2           | 0   | <b>DMA Request.</b> Active high output to signal the DMA controller that a FDC data transfer is needed. When in PC-AT or Model 30 mode, this signal is enabled by bit D3 of the DOR. When in PS/2 mode, FDRQ is always enabled, and bit D3 of the DOR is reserved.                                                                                                                                                                                                                                                           |  |  |  |  |

| HCS0                     | 58          | 56          | 0   | Hard Drive Chip Select 0. This output is active in the AT mode when 1) the hard drive registers from 1F0–1F7h are selected and the primary address is used or 2) the hard drive registers from 170–177h are selected and the secondary address is used. This output is inactive if the IDE interface is disabled via the Configuration Register. (See BADDR1 for further information.)                                                                                                                                       |  |  |  |  |

| HCS1                     | 57          | 55          | 0   | Hard Drive Chip Select 1. This output is active in the AT mode when 1) the hard drive registers from 3F6–7 are selected and the primary address is used or 2) the hard drive registers from 376–377 are selected and the secondary address is used. This output is also inactive, if the IDE interface is disabled via the Configuration Register. (See CLK48 for further information.)                                                                                                                                      |  |  |  |  |

| HDSEL<br>Normal<br>Mode  | 34          | 32          | 0   | <b>Head Select.</b> This output determines which side of the FDD is accessed. When active, the head selects side 1. When inactive, the head selects side 0.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| HDSEL<br>PPM<br>Mode     | 79          | 77          | 0   | <b>Head Select.</b> This pin provides an additional Head Select signal in PPM Mode when PNF = 0. (See ERR and Table 7-5 for further information.)                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| IDEACK                   | 59          | 57          |     | IDE DMA Acknowledge. This is the IDE DMA acknowledge input pin when bit 1 of FCR is 1. In this case IOCS16 is assumed 0. It is the IOCS16 input pin when bit 1 of FCR is 0. (See IOCS16, DRIDO, and IRRX for further information.)                                                                                                                                                                                                                                                                                           |  |  |  |  |

| IDED7                    | 60          | 58          | 1/0 | IDE Bit 7. This pin provides the data bus bit 7 signal to the IDE hard drive during accesses in the address range 1F0–1F7h, 170–177h, 3F6h and 376h. This pin is in TRI-STATE during read or write accesses to 3F7h and 377h.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Symbol                  | PQFP<br>Pin | TQFP<br>Pin | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|-------------------------|-------------|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| ĪDEHĪ                   | 56          | 54          | 0   | IDE High Byte. This output enables the high byte data latch during a read or write to the hard drive if the hard drive returns IOCS16. This output is inactive if the IDE interface is disabled via the Configuration Register. (See VLD0 and IRTX for further information.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| ĪDELO                   | 55          | 53          | 0   | IDE Low Byte. This output enables the low byte data latch during a read or write to the hard drive. This output is inactive if the IDE interface is disabled via the Configuration Register. (See BADDR0 for further information.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| IDENT                   | 54          | 52          | I   | <b>Identity.</b> During chip reset, the IDENT and MFM pins are sampled to determine the desired mode of operation according to the following table:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|                         |             |             |     | IDENT MFM MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                         |             |             |     | 1 1 or NC PC-AT Mode 1 0 Illegal 0 1 or NC PS/2 Mode 0 0 Model 30 Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                         |             |             |     | <b>AT Mode</b> —The DMA enable bit in the DOR is valid. TC is active high. Status Registers A and B are disabled (TRI-STATE).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                         |             |             |     | <b>Model 30 Mode</b> —The DMA enable bit in the DOR is valid. TC is active high. Status Registers A and B are enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                         |             |             |     | <b>PS/2 Mode</b> —The DMA enable bit in the DOR is a don't care, and the FDRQ and IRQ6 signals are always enabled. TC is active low. Status Registers A and B are enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                         |             |             |     | After chip reset, the state of IDENT determines the polarity of the DENSEL output. When IDENT is a logic "1", DENSEL is active high for the 500 kbps/1 Mbps/2 Mbps data rates. When IDENT is a logic "0", DENSEL is active low for the 500 kbps/1 Mbps/2 Mbps data rates. (See Mode command for further explanation of DENSEL.)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| IDLE                    | 43          | 41          | 0   | IDLE. This pin is IDLE output when bit 4 of PMC is 1. IDLE indicates that the FDC is in the IDLE state and can be powered down. Whenever the FDC is in IDLE state, or whenever the FDC is in power-down state, the pin is active high. This bit is MTR1 when bit 4 of the Power Management Control Register (PMC) is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| INDEX<br>Normal<br>Mode | 47          | 45          | I   | Index. This input signals the beginning of a FDD track.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| INDEX<br>PPM<br>Mode    | 94          | 92          | ı   | Index. This pin provides an additional Index signal in PPM Mode when PNF = 0. (See PD0 and Table 7-5 for further information.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| INIT                    | 80          | 78          | 1/0 | <b>Initialize.</b> When this signal is low it causes the printer to be initialized. This pin is in a TRI-STATE condition 10 ns after a 1 is loaded into the corresponding Control Register bit. The system should pull this pin high using a 4.7 k $\Omega$ resistor. (See $\overline{\text{DIR}}$ and Table 7-5 for further information.)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| IOCHRDY                 | 53          | 51          | 0   | I/O Channel Ready. This is the I/O Channel Ready open drain output when bit 7 of FCR is 0 When IOCHRDY is driven low, the EPP extends the host cycle. This pin is the MFM output pir when bit 7 of FCR is 1. (See MFM pin for further information.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| IOCS16                  | 59          | 57          | I   | I/O Chip Select 16-bit. This input is driven by the peripheral device when it can accommodate a 16-bit access. (See DRID0, IDEACK and IRRX for further information.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| IRQ3,4                  | 1, 100      | 99, 98      | 0   | Interrupt 3 and 4. These are active high interrupts associated with the serial ports. presents the signal if the serial port has been designated as COM2 or COM4. IRQ4 the signal if the serial port is designated as COM1 or COM3. The appropriate interru active whenever it is enabled via the Interrupt Enable Register (IER), the associated Enable bit (Modem Control Register bit 3, MCR3), and any of the following condition active: Receiver Error, Receive Data available, Transmitter Holding Register Empty, Modem Status Flag is set. The interrupt is reset low (inactive) after the appropriate in service routine is executed, after being disabled via the IER, or after a Master Reset interrupt can be disabled, putting them into TRI-STATE, by setting the MCR3 bit low |  |  |  |  |  |  |

| PQFP<br>Pin     | TQFP<br>Pin                                                                                       | 1/0                                                                                                   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 98              | 96                                                                                                | 1/0                                                                                                   | Interrupt 5. Active high output that indicates a parallel port interrupt. When enabled this bit follows the $\overline{ACK}$ signal input. When bit 4 in the parallel port Control Register is set and the parallel port address is designated as shown in Table 2-5, this interrupt is enabled. When it is not enabled this signal is TRI-STATE. This pin is I/O only when ECP is enabled, and IRQ5 is configured. For ECP operation, refer to the interrupt ECP Section 7.11.1.                      |  |  |  |  |

| 97              | 95                                                                                                | 0                                                                                                     | Interrupt 6. Active high output to signal the completion of the execution phase for certain FDC commands. Also used to signal when a data transfer is ready during a Non-DMA operation. When in PC-AT or Model 30 mode, this signal is enabled by bit D3 of the DOR. When in PS/2 mode, IRQ6 is always enabled, and bit D3 of the DOR is reserved.                                                                                                                                                     |  |  |  |  |

| 96              | 94                                                                                                | 1/0                                                                                                   | <b>Interrupt 7.</b> Active high output that indicates a parallel port interrupt. When enabled this bit follows the $\overline{ACK}$ signal input. When bit 4 in the parallel port Control Register is set and the parallel port address is designated as shown in Table 2-5, this interrupt is enabled. When it is not enabled this signal is TRI-STATE. This pin is I/O only when ECP is enabled, and IRQ7 is configured. For ECP operation, refer to the interrupt ECP Section 7.11.1.               |  |  |  |  |

| 59, 68          | 57, 66                                                                                            | I                                                                                                     | nfrared Receive. One of these pins (see Table 1-1 for pin allocation) is the infrared serial ata input. (See DSR2, IOCS16, DRIDO, and IDEACK for further information.)                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 56, 63          | 54, 61                                                                                            | 0                                                                                                     | Infrared Transmit. One of these pins (see Table 1-1 for pin allocation) is the infrared serial data output. (See DTR2, VLD1, IDEHI, VLD0, DRID1, and 3F3RD for further information.)                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 2               | 100                                                                                               | ı                                                                                                     | Master Reset. Active high input that resets the controller to the idle state, and resets all disk interface outputs to their inactive states. The DOR, DSR, CCR, Mode command, Configure command, and Lock command parameters are cleared to their default values. The Specify command parameters are not affected. The Configuration Registers are set to their selected default values.                                                                                                              |  |  |  |  |

| 53              | 51                                                                                                | 1/0                                                                                                   | MFM (Modified Frequency Modulation). During a chip reset, when IDENT is low, this pin is sampled to select the PS/2 mode (MFM high), or the Model 30 mode (MFM low). An international pull-down 10k resistor selects between the two PS/2 modes. When the PC-AT mode is desired, (IDENT high), MFM should be left pulled high internally. MFM reflects the current data encoding format when RESET is inactive. MFM = high. Defaults to low after a chip reset. (See IOCHRDY for further information.) |  |  |  |  |

| 46, 43          | 44, 41                                                                                            | 0                                                                                                     | Motor Select 0,1. These are the motor enable lines for drives 0 and 1, and they are controlled by bits D7–D4 of the Digital Output register. They are active low outputs. They are encoded with information to control four FDDs when bit 4 of the Function Enable Register (FER) is set. MTR0 exchanges logical motor values with MTR1 when bit 4 of FCR is set. (See DR0,1).                                                                                                                         |  |  |  |  |

| 84              | 82                                                                                                | 0                                                                                                     | <b>Motor Select 1.</b> This pin provides an additional Motor Select 1 signal in PPM Mode when PNF = 0. This pin is the motor enable line for drive 1 when bit 4 of FCR is 0. It is the motor enable line for drive 0 when bit 4 of FCR is 1. This signal is active low. (See BUSY and Table 7-5 for further information.)                                                                                                                                                                              |  |  |  |  |

| 52, 51          | 50, 49                                                                                            | ı                                                                                                     | <b>Media Sense.</b> These pins are Media Sense input pins when bit 0 of FCR is 0. Each pin has a 10 k $\Omega$ internal pull-up resistor. When bit 0 of FCR is 1, these pins are Data Rate output pins, and the pull-up resistors are disabled. (See DRATE0,1 for further information.)                                                                                                                                                                                                                |  |  |  |  |

| 88, 86          | 86, 84                                                                                            | ı                                                                                                     | Media Sense. These pins provide additional Media Sense signals for PPM Mode and PNF = 0. (See PD5, 7 and Table 7-5 for further information.)                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 45              | 43                                                                                                | 0                                                                                                     | <b>Power-Down.</b> This pin is PD output when bit 4 of PMC is 1. It is $\overline{DR1}$ when bit 4 of PMC is 0. PD is active high whenever the FDC is in power-down state, either via bit 6 of DSR (or bit 3 of FER, or bit 0 of PTR), or via the mode command. See $\overline{DR1}$ for further information.                                                                                                                                                                                          |  |  |  |  |

| 94–91,<br>89–86 | 92-89,<br>87-84                                                                                   | 1/0                                                                                                   | Parallel Port Data. These bidirectional pins transfer data to and from the peripheral data bus and the parallel port Data Register. These pins have high current drive capability. (See DC Electrical Characteristics.)                                                                                                                                                                                                                                                                                |  |  |  |  |

|                 | 98<br>97<br>96<br>59, 68<br>56, 63<br>2<br>53<br>46, 43<br>84<br>52, 51<br>88, 86<br>45<br>94–91, | 98 96 97 95 96 94 59,68 57,66 56,63 54,61 2 100 53 51 46,43 44,41 84 82 52,51 50,49 88,86 86,84 45 43 | Pin         Pin           98         96         I/O           97         95         O           59, 68         57, 66         I           56, 63         54, 61         O           2         100         I           46, 43         44, 41         O           84         82         O           52, 51         50, 49         I           88, 86         86, 84         I           45         43         O                                                                                          |  |  |  |  |

| Symbol                  | PQFP<br>Pin | TQFP<br>Pin | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------------------------|-------------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PDACK                   | 54          | 52          | -   | Printer DMA Acknowledge. Active low input to acknowledge the printer DMA request, and enable the RD and WR inputs during a DMA transfer. This pin is PDACK input pin when bit 3 of PMC is 1. It is IDENT when bit 3 of PMC is 0. PDACK input pin is ECP DMA acknowledge.  PDACK is assumed to be 1 when bit 3 of PMC is 0.                                                                                                                                                                                                                                  |  |  |  |  |

|                         |             |             |     | IDENT is assumed to be 1 when bit 3 of PMC is 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                         |             |             |     | This input is valid only in ECP mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |