National Semiconductor

# LMC6009 9 Channel Buffer Amplifier for TFT-LCD

#### **General Description**

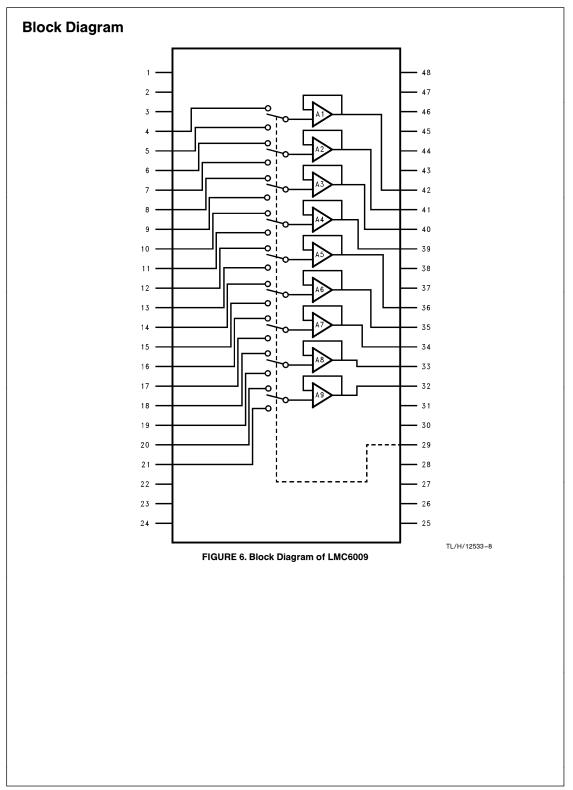

The LMC6009 is a CMOS integrated circuit that buffers 9 reference voltages for gamma correction in a Thin Film Transistor Liquid Crystal Display (TFT-LCD). Guaranteed to operate at both 3.3V and 5V supplies, this integrated circuit contains nine, independent unity gain buffers that can source 130 mA into a capacitive load without oscillation.

The LMC6009 is useful for buffering gamma voltages into column drivers that employ the resistor-divider architecture. High output current capability and fast settling characteristics of this device improve display quality by minimizing rise time errors at the outputs of the column driver. The integration of nine buffers and a multiplexer eliminates the need for discrete buffers and a separate multiplexer (MUX) chip on the panel.

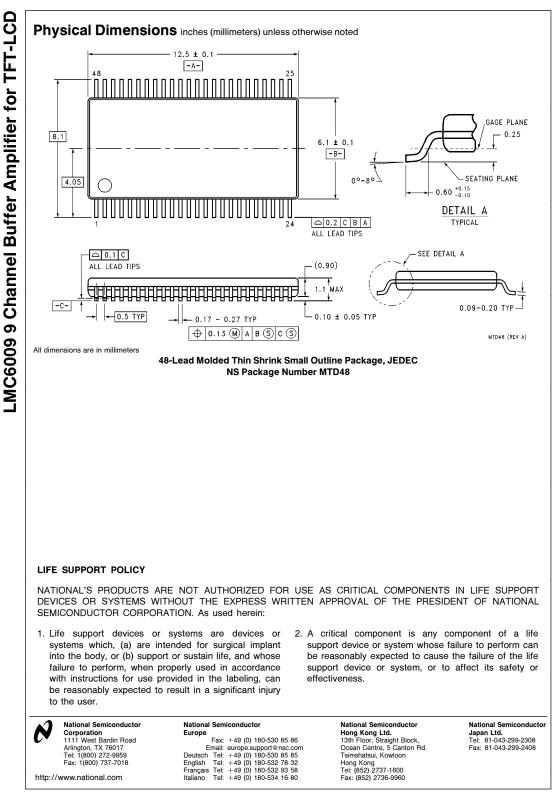

The LMC6009 is available in 48-pin surface mount TSSOP.

### Features

- Number of inputs

- 3.3V and 5V operation

- Supply current

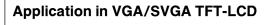

Settling time

- A/B channel inputs for asymmetrical Gamma

**ADVANCE INFORMATION**

April 1996

18

3.5 mA

3 µs

9

Number of outputs

\_MC6009 9 Channel Buffer Amplifier for TFT-LCD

- Number of control inputs

- Built-in thermal shutdown protection

### Applications

- VGA/SVGA TFT-LCD drive circuits

- Electronic Notebooks

- Electronic Games

- Personal Communication Devices

- Personal Digital Assistants (PDA)

A/B Switch V<sub>REF1-9</sub> LMC6009 LMC6000

## **Ordering Information**

| Package      | Temperature Range        | Transport Media | NSC Drawing |

|--------------|--------------------------|-----------------|-------------|

| 48-pin TSSOP | -20°C-+75°C<br>LMC6009MT |                 | MTD48       |

|              | LMC6009MTX               | Tape and Reel   |             |

©1996 National Semiconductor Corporation TL/H/12533

RRD-B30M56/Printed in U. S. A.

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications. ESD Tolerance 1.0 kV

### **Operating Ratings** (Note 1)

| Supply Voltage                       | $2.7V \leq V_{DD} \leq 5.5V$ |

|--------------------------------------|------------------------------|

| Frequency                            | DC-50 kHz                    |

| Thermal Resistance ( $\theta_{JA}$ ) |                              |

| Derating                             | 8.70 mW/°C                   |

|                                      |                              |

### **3V DC Electrical Characteristics**

Input Voltage

Supply Voltage (V<sub>DD</sub>)

Operating Temperature

Storage Temperature Range Maximum Junction Temperature (T<sub>J</sub>)

Maximum Power Dissipation (PD)

Unless otherwise specified, all limits are guaranteed for  $T_{J}$  = 25°C, and  $V_{DD}$  = 3.0V\_{DC}.

$GND\text{--}0.3V \leq V^+ \\ \leq V_{DD}\text{+-}0.3V_{DC}$

-0.3 to +6.5 V<sub>DC</sub>

-20°C to +75°C -55°C to +150°C

+150°C

1.09W

| Symbol          | Parameter                         | Conditions                                             | Min                  | Тур | Max     | Units |

|-----------------|-----------------------------------|--------------------------------------------------------|----------------------|-----|---------|-------|

| V <sub>DD</sub> | Supply Voltage                    |                                                        | 2.7                  | 3.0 | 3.3     | V     |

| V <sub>OS</sub> | Offset Voltage                    | $R_{S} = 10k$                                          |                      |     | 20      | mV    |

| IB              | Input Bias Current                |                                                        |                      |     | 1500    | nA    |

| V <sub>OL</sub> | Output Voltage, Low               | Amp A8 and A9<br>I <sub>SINK</sub> = 13 mA             |                      |     | GND+0.2 | v     |

|                 |                                   | Amp A1-A7<br>I <sub>SINK</sub> = 13 mA                 |                      |     | GND+0.6 | v     |

| V <sub>OH</sub> | Output Voltage, High              | Amp A1 and A2<br>$I_{SOURCE} = 13 \text{ mA}$          | V <sub>DD</sub> -0.2 |     |         | v     |

|                 |                                   | Amp A3-A9<br>I <sub>SOURCE</sub> = 13 mA               | V <sub>DD</sub> -0.6 |     |         | v     |

| I <sub>SC</sub> | Output Short Circuit<br>Current   | V <sub>OUT</sub> = 1.65V (Note 1)                      | 80                   | 150 |         | mA    |

| I <sub>DD</sub> | Supply Current                    | No Load                                                |                      | 3.5 | 5       | mA    |

| $\Delta V_L$    | Load Regulation                   | $V_{IN} = 0.3 - 3 V_{DC}$ $I_{SOURCE} = 13 \text{ mA}$ |                      |     | -10     | mV    |

|                 |                                   | I <sub>SINK</sub> = 13 mA                              |                      |     | + 10    | mV    |

| V <sub>IH</sub> | A/B Switch Logic<br>Voltage, High | Select A                                               | 2                    |     |         | v     |

| V <sub>IL</sub> | A/B Switch Logic<br>Voltage, Low  | Select B                                               |                      |     | 0.8     | v     |

| IIH             | A/B Switch Logic<br>Current, High |                                                        |                      |     | 1.5     | μΑ    |

| IIL             | A/B Switch Logic<br>Current, Low  |                                                        |                      |     | 1       | μΑ    |

| A <sub>V</sub>  | Voltage Gain                      |                                                        | 0.985                |     |         | V/V   |

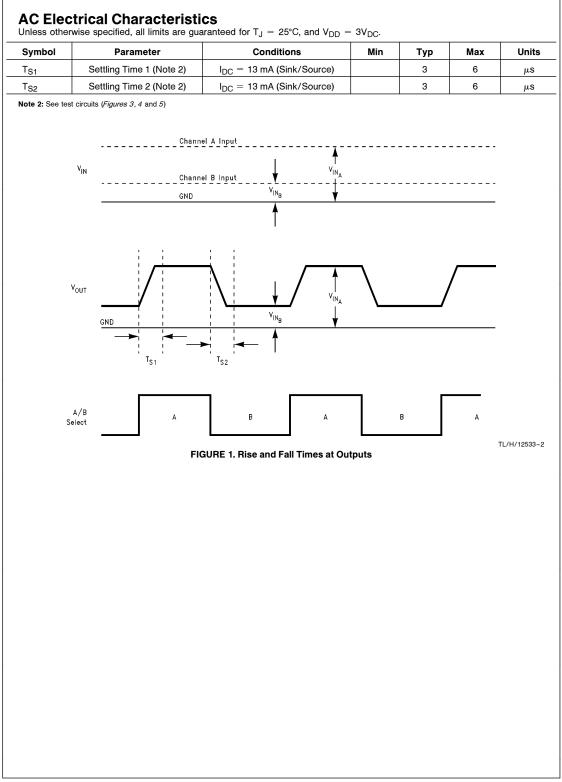

Note 1: See Test Circuit (Figure 2)

| Symbol          | Parameter                         | Conditions                                          | Min                   | Тур | Max     | Units |

|-----------------|-----------------------------------|-----------------------------------------------------|-----------------------|-----|---------|-------|

| V <sub>DD</sub> | Supply Voltage                    |                                                     | 4.5                   | 5   | 5.5     | V     |

| V <sub>OS</sub> | Offset Voltage                    | $R_S = 10k$                                         |                       |     | 20      | mV    |

| I <sub>B</sub>  | Input Bias Current                |                                                     |                       |     | 1500    | nA    |

| V <sub>OL</sub> | Output Voltage, Low               | Amp A8 and A9<br>$I_{SINK} = 20 \text{ mA}$         |                       |     | GND+0.2 | V     |

| V <sub>OL</sub> | Output Voltage, Low               | Amp A1–A7<br>I <sub>SINK</sub> = 20 mA              |                       |     | GND+1.0 | V     |

| V <sub>OH</sub> | Output Voltage, High              | Amp A1 and A2<br>I <sub>SOURCE</sub> = 20 mA        | V <sub>DD</sub> -0.2  |     |         | V     |

| V <sub>OH</sub> | Output Voltage, High              | Amp A3-A9<br>I <sub>SOURCE</sub> = 20 mA            | V <sub>DD</sub> - 1.0 |     |         | V     |

| I <sub>SC</sub> | Output Short Circuit<br>Current   | V <sub>OUT</sub> = 1.65V (Note 1)                   | 120                   | 200 |         | mA    |

| I <sub>DD</sub> | Supply Current                    | No Load                                             |                       | 4.5 | 6       | mA    |

| $\Delta V_L$    | Load Regulation                   | $V_{IN} = 0.5 - 4.5 V_{DC}$<br>$I_{SOURCE} = 20 mA$ |                       |     | -10     | mV    |

|                 |                                   | I <sub>SINK</sub> = 20 mA                           |                       |     | + 10    | mV    |

| V <sub>IH</sub> | A/B Switch Logic<br>Voltage, High | Select A                                            | 2                     |     |         | V     |

| V <sub>IL</sub> | A/B Switch Logic<br>Voltage, Low  | Select B                                            |                       |     | 0.8     | V     |

| IIH             | A/B Switch Logic<br>Current, High |                                                     |                       |     | 1.5     | μA    |

| IIL             | A/B Switch Logic<br>Current, Low  |                                                     |                       |     | 1       | μΑ    |

| A <sub>V</sub>  | Voltage Gain                      |                                                     | 0.985                 |     |         | V/V   |

|                 |                                   |                                                     |                       |     |         |       |

|                 |                                   |                                                     |                       |     |         |       |

|                 |                                   |                                                     |                       |     |         |       |

|                 |                                   |                                                     |                       |     |         |       |

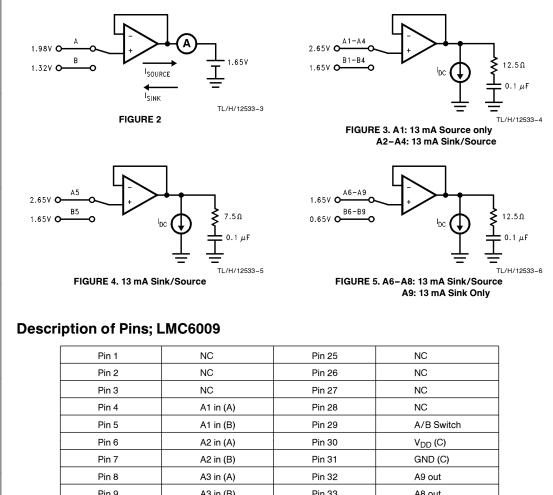

| 1115   | /(1 lil (D) | 1 11 25 | 70 D OWIteri        |  |

|--------|-------------|---------|---------------------|--|

| Pin 6  | A2 in (A)   | Pin 30  | V <sub>DD</sub> (C) |  |

| Pin 7  | A2 in (B)   | Pin 31  | GND (C)             |  |

| Pin 8  | A3 in (A)   | Pin 32  | A9 out              |  |

| Pin 9  | A3 in (B)   | Pin 33  | A8 out              |  |

| Pin 10 | A4 in (A)   | Pin 34  | A7 out              |  |

| Pin 11 | A4 in (B)   | Pin 35  | A6 out              |  |

| Pin 12 | A5 in (A)   | Pin 36  | A5 out              |  |

| Pin 13 | A5 in (B)   | Pin 37  | GND (B)             |  |

| Pin 14 | A6 in (A)   | Pin 38  | V <sub>DD</sub> (B) |  |

| Pin 15 | A6 in (B)   | Pin 39  | A4 out              |  |

| Pin 16 | A7 in (A)   | Pin 40  | A3 out              |  |

| Pin 17 | A7 in (B)   | Pin 41  | A2 out              |  |

| Pin 18 | A8 in (A)   | Pin 42  | A1 out              |  |

| Pin 19 | A8 in (B)   | Pin 43  | GND (A)             |  |

| Pin 20 | A9 in (A)   | Pin 44  | V <sub>DD</sub> (A) |  |

| Pin 21 | A9 in (B)   | Pin 45  | NC                  |  |

| Pin 22 | NC          | Pin 46  | NC                  |  |

| Pin 23 | NC          | Pin 47  | NC                  |  |

| Pin 24 | NC          | Pin 48  | NC                  |  |

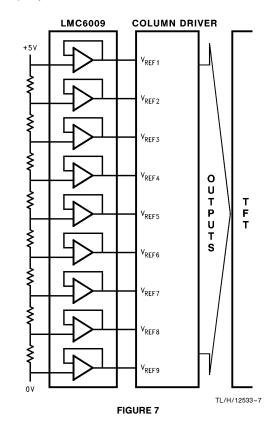

#### Applications

The LMC6009 is useful for buffering the nine reference voltages for gamma correction in a TFT-LCD as shown in *Figure 7*. The A/B channel inputs allow the user to alternate two sets of gamma references to compensate for asymmetrical Gamma characteristic during Row Inversion. The LMC6009 eliminates the need for nine external switches or an 18-to-9 multiplexer.

Since the buffers in the LMC6009 draw extremely low bias current (1.5  $\mu$ A max), large resistance values can be used in the reference voltage string. This allows the power dissipation in the gamma reference circuit to be minimized. The nine buffers are guaranteed to deliver 80 mA to the load, allowing the pixel voltages of the TFT-LCD to settle very quickly.

**Example:** Below is a calculation of pixel charge time (for a black to black transition) in a VGA display operating at a vertical refresh rate of 60 Hz, with a panel capacitance of 50 pF per sub-pixel:

A full black to black transition represents the maximum charging time for the panel, since it requires that the panel capacitance be driven by a 4V swing from node V<sub>REF1</sub> (*Figure 7*).

Total capacitive load presented to the LMC6009 is

$C_L = 50 \text{ pF} \times 3 \times 640 = 96 \text{ nF}$

Output current of the LMC6009 is:

$I_{SC} = 80 \text{ mA}$

Hence, slew time  $t_{SLEW}$  = (96 nF  $\times$  4V)/80 mA

The total line time for a VGA system is approximately 34  $\mu s.$ Therefore, the LMC6009 easily meets the drive requirements for the application. The input resistance seen between the V<sub>REFn</sub> and V<sub>REF(n+1)</sub> inputs, (where n = 0 thru 8) of the Column Driver (*Figure 7*) also draw current from the LMC6009. Thus, the actual current available for charging the panel capacitance is:

$lpx = 80 \text{ mA} - (V_{VREF1} - V_{VREF2})/R_{CD}$  where

$V_{V REFn} = Voltage at node V_{REFn}$ ,

$V_{VREF(n+1)} = Voltage at node V_{REF(n+1)}$ , and  $R_{CD} = Column driver input resistance between$

VREFn and VREF(n+1)

Since the LMC6009 is capable of sourcing 80 mA, the pixel charging time is primarily limited only by the length of the  $R_{CD}.\ C_L$  time constant. To implement a high quality display, column drivers that allow the shortest possible time constant (lower values of  $R_{CD}$ ) are desirable. However, lower values of  $R_{CD}$  result in increased system quiescent power dissipation. It is therefore important to optimize system performance by carefully considering speed vs power tradeoffs.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications