### LM2638

## Motherboard Power Supply Solution with a 5-Bit **Programmable Switching Controller and Two Linear Regulator Controllers**

### **General Description**

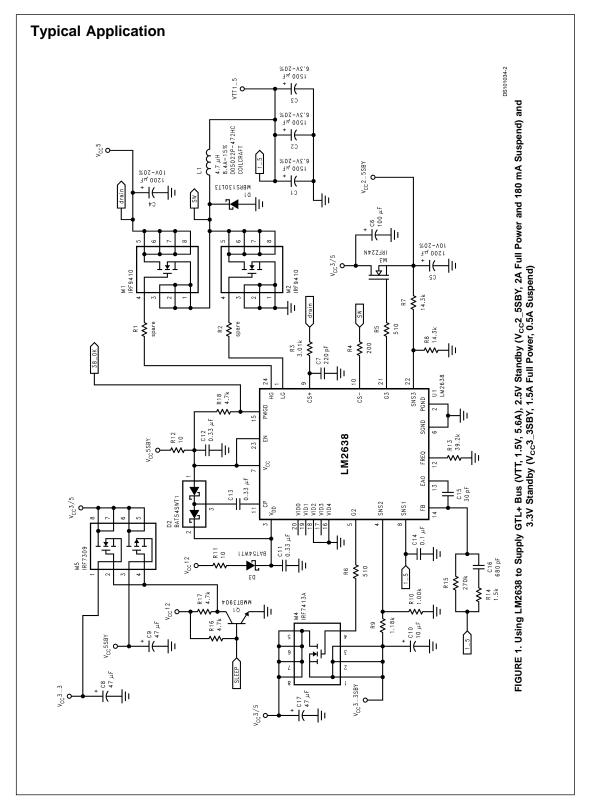

The LM2638 provides a comprehensive embedded power supply solution for motherboards hosting high performance MPUs such as Pentium™ II, M II™, K6™-2 and other similar high performance MPUs. The LM2638 incorporates a 5-bit programmable, synchronous buck switching controller and two high-speed linear regulator controllers in a 24-pin SO package. The switching controller supplies the MPU core. The linear regulator controllers supply the GTL+ bus and the clock or graphics chip core. A charge pump pin provides the necessary voltage to power the linear sections when 12V is shut off during system standby such as STR mode.

Switching Section — The switching regulator controller features an Intel-compatible, 5-bit programmable output voltage, over-current and over-voltage protection, a power good signal, and a logic-controlled output enable. There are two user-selectable over-current protection methods. One provides accurate over-current protection with the use of an external sense resistor. The other saves cost by taking advantage of the  $r_{\text{DS\_ON}}$  of the high-side FET. When there is an over voltage, the controller turns off the high side FET and turns on the low side.

Dynamic positioning of the switcher output voltage reduces the number of output capacitors and can be easily realized using the same sense resistor as the over-current protection.

Linear Section — The two linear regulator controllers feature wide control bandwidth, N-FET and NPN transistor driving capability and an adjustable output. The wide control bandwidth makes meeting the GTL+ bus transient response requirement an easy job. In minimum configuration, the two controllers default to 1.5V and 1.25V respectively.

Both linear controllers have under voltage protection.

#### **Features**

- Provides 3 regulated voltages

- Power Good flag and output enable

- Charge pump pin Switching Section

- Synchronous rectification

- 5-bit DAC programmable down to 1.3V

- Typical ±1% DAC tolerance

- Switching frequency: 50 kHz to 1 MHz

- Two levels of over-voltage protection

- Two methods of over-current protection ■ Adaptive non-overlapping FET gate drives

- Soft start without external capacitor

- Linear Section

- N-FET and NPN drive capability

- Ultra fast response speed

- Under voltage latch-off at 0.63V

- Pre-set output voltages: 1.5V and 1.25V

#### **Applications**

- Embedded power supplies for motherboards

- Triple DC/DC power supplies

- Programmable high current DC/DC power supply

M IITM is a trademark of Cyrix Corporation a wholly owned subsidiary of National Semiconductor Corporation. entium™ is a trademark of Intel Corporation. 6™ is a trademark of Advanced Micro Devices, Inc.

# Pin Configuration

#### 24-Lead SOIC

Top View Order Number LM2638M See NS Package Number M24B

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$V_{CC}$  7V  $V_{DD}$  17V

Junction Temperature 150°C

Power Dissipation (Note 2) 1.6W

Storage Temperature  $$-65^{\circ}\text{C}$$  to +150  $^{\circ}\text{C}$  ESD Susceptibility \$3\$ kV Soldering Time, Temperature (10 sec.)  $$300^{\circ}\text{C}$$

## **Operating Ratings** (Note 1)

$V_{CC}$  4.75V to 5.25V Junction Temperature Range 0°C to +125°C

**Electrical Characteristics**  $V_{CC}$  = 5V,  $V_{DD}$  = 12V unless otherwise specified. Typicals and limits appearing in plain type apply for  $T_A$  =  $T_J$  = +25°C. Limits appearing in **boldface** type apply over the 0°C to +70°C range.

| Symbol               | Parameter                                    | Conditions                                    | Min            | Тур   | Max    | Units           |  |

|----------------------|----------------------------------------------|-----------------------------------------------|----------------|-------|--------|-----------------|--|

| I <sub>EN</sub>      | EN Pin Internal Pull-up Current              |                                               | 60             | 90    | 140    | μA              |  |

| I <sub>cc</sub>      | Operating V <sub>CC</sub> Current            | EN = 5V, VID = 10111                          |                | 6     | 7.5    | mA              |  |

| I <sub>Q_VCC</sub>   | V <sub>CC</sub> Shutdown Current             | EN = 0V, VID Pins Floating                    |                | 1.5 3 |        | mA              |  |

| I <sub>Q_VDD</sub>   | V <sub>DD</sub> Shutdown Current             | EN = 0V, VID Pins Floating                    |                | 4     |        | μA              |  |

| R <sub>DS CP</sub>   | CP Pin Resistance                            | High Side FET                                 |                | 100   |        | Ω               |  |

|                      |                                              | Low Side FET                                  |                | 10    |        |                 |  |

| SWITCHING            | SECTION                                      |                                               |                |       |        |                 |  |

| V <sub>DACOUT</sub>  | 5-Bit DAC Output Voltage                     | (Note 3)                                      | <i>N</i> –1.5% | N     | N+1.5% | V               |  |

| I <sub>VID</sub>     | VID Pins Internal Pull-up<br>Current         |                                               | 60             | 90    | 140    | μA              |  |

| f <sub>osc</sub>     | Oscillator Frequency                         | RT = 100 kΩ                                   | 204            | 245   | 286    | kHz             |  |

|                      |                                              | RT = 25 kΩ                                    |                | 1000  |        |                 |  |

| D <sub>MAX</sub>     | Maximum Duty Cycle                           |                                               |                | 100   |        | %               |  |

| D <sub>MIN</sub>     | Minimum Duty Cycle                           |                                               |                | 0     |        | %               |  |

| R <sub>SNS1</sub>    | SNS1 Pin Resistance to Ground                |                                               | 8.5            | 10    | 13     | kΩ              |  |

| R <sub>DS_SRC</sub>  | Gate Driver Resistance When Sourcing Current |                                               |                | 6     |        | Ω               |  |

| R <sub>DS_SINK</sub> | Gate Driver Resistance When Sinking Current  |                                               |                | 1.5   |        | Ω               |  |

| V <sub>CC_TH1</sub>  | V <sub>CC</sub> Power-On-Reset<br>Threshold  |                                               |                | 4.0   | 4.3    | V               |  |

| V <sub>CC_TH2</sub>  | V <sub>CC</sub> Shutdown Threshold           |                                               | 3.0            | 3.6   |        | V               |  |

| V <sub>DAC_IH</sub>  | DAC Input High Voltage                       |                                               | 3.5            |       |        | V               |  |

| V <sub>DAC_IL</sub>  | DAC Input Low Voltage                        |                                               |                |       | 1.3    | V               |  |

| GA                   | Error Amplifier DC Gain                      |                                               |                | 76    |        | dB              |  |

| BW <sub>EA</sub>     | Error Amplifier Unity Gain Bandwidth         |                                               |                | 5     |        | MHz             |  |

| $V_{RAMP\_L}$        | Ramp Signal Valley Voltage                   |                                               |                | 1.25  |        | V               |  |

| V <sub>RAMP_H</sub>  | Ramp Signal Peak Voltage                     |                                               |                | 3.25  |        | V               |  |

| t <sub>SS</sub>      | Soft Start Time                              |                                               |                | 4096  |        | Clock<br>Cycles |  |

| D <sub>STEP_SS</sub> | Duty Cycle Step Change during<br>Soft Start  |                                               |                | 12.5  |        | %               |  |

| t <sub>PWGD</sub>    | PWGD Response Time                           | SNS1 Rises from 0V to Rated<br>Output Voltage | 2              | 8.4   | 15     | μs              |  |

| t <sub>PWBAD</sub>   | PWGD Response Time                           | SNS1 Falls from Rated Output<br>Voltage to 0V | 2              | 3.4   | 10     | μs              |  |

**Electrical Characteristics**  $V_{CC} = 5V$ ,  $V_{DD} = 12V$  unless otherwise specified. Typicals and limits appearing in plain type apply for  $T_A = T_J = +25^{\circ}C$ . Limits appearing in **boldface** type apply over the 0°C to +70°C range. (Continued)

| Symbol               | Parameter Conditions                                       |                                                                     | Min   | Тур  | Max   | Units |

|----------------------|------------------------------------------------------------|---------------------------------------------------------------------|-------|------|-------|-------|

| SWITCHING            | SECTION                                                    |                                                                     |       |      | •     | •     |

| $V_{PWGD\_HI}$       | PWGD High Trip Point                                       | % Above Rated Output Voltage When Output Voltage↑                   |       | 11.5 | 13    |       |

|                      |                                                            | % Above Rated Output Voltage<br>When Output Voltage↓ (Note<br>4)    | 5     | 7    | 9     | %     |

| $V_{PWGD\_LO}$       | PWGD Low Trip Point                                        | % Below Rated Output Voltage<br>When Output Voltage↑                |       | 2.6  | 6     |       |

|                      |                                                            | % Below Rated Output Voltage<br>When Output Voltage↓ (Note<br>4)    | 6     | 9.5  | 13    | %     |

| V <sub>OVP_TRP</sub> | Over-Voltage Trip Point                                    | % SNS1 Above Rated Output                                           | 15    | 25   | 35    | %     |

| I <sub>cs+</sub>     | CS+ Pin Sink Current                                       | CS+ = 5V, CS- = 4.8V                                                | 126   | 185  | 244   | μA    |

| V <sub>OCP</sub>     | Over-Current Trip Point (CS+ and CS- Differential Voltage) | CS+ = 2V, CS- Drops from 2V                                         | 41    | 55   | 69    | mV    |

| 1.5V LDO C           | ONTROLLER SECTION                                          |                                                                     |       |      |       |       |

| V <sub>SNS2</sub>    | SNS2 Voltage                                               | $V_{DD}$ = 12V, $V_{CC}$ = 4.75V to 5.25V, $I_{G2}$ = 0 mA to 20 mA | 1.463 | 1.5  | 1.538 | V     |

| R <sub>OUT2</sub>    | Output Resistance                                          |                                                                     |       | 200  |       | Ω     |

| I <sub>SNS2</sub>    | SNS2 Pin Bias Current                                      | When Regulating                                                     |       | 21   |       | μΑ    |

| V <sub>PWGD_HI</sub> | PWGD High Trip Point                                       | (Note 4)                                                            |       | 0.63 |       | V     |

| $V_{PWGD\_LO}$       | PWGD Low Trip Point                                        | (Note 4)                                                            |       | 0.44 |       | V     |

| 1.25V LDO            | CONTROLLER SECTION                                         |                                                                     |       |      |       |       |

| V <sub>SNS3</sub>    | SNS3 Voltage                                               | $V_{DD}$ = 12V, $V_{CC}$ = 4.75V to 5.25V, $I_{G3}$ = 0 mA to 20 mA | 1.219 | 1.25 | 1.281 | V     |

| R <sub>OUT3</sub>    | Output Resistance                                          |                                                                     |       | 200  |       | Ω     |

| I <sub>SNS3</sub>    | SNS3 Pin Bias Current                                      | When Regulating                                                     |       | 0    |       | μA    |

| V <sub>PWGD_HI</sub> | PWGD High Trip Point                                       | (Note 4)                                                            |       | 0.63 |       | V     |

| V <sub>PWGD_LO</sub> | PWGD Low Trip Point                                        | (Note 4)                                                            |       | 0.44 |       | V     |

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating ratings are conditions under which the device operates correctly. Operating Ratings do not imply guaranteed performance limits.

Note 2: Maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{JMAX}$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any ambient temperature is calculated using:  $P_{MAX} = (T_{JMAX} - T_A)P_{0JA}$ . The junction-to-ambient thermal resistance,  $\theta_{JA}$ , for LM2638 is 78°C/W. For a  $T_{JMAX}$  of 150°C and  $T_A$  of 25°C, the maximum allowable power dissipation is 1.6W. Note 3: The letter **N** stands for the typical output voltages appearing in *italic boldface* type in *Table 1*.

Note 4: The output level of the PWGD pin is a logic AND of the power good function of the switching section, the 1.5V section and the 1.25V section.

www.national.com

**Electrical Characteristics**  $V_{CC}$  = 5V,  $V_{DD}$  = 12V unless otherwise specified. Typicals and limits appearing in plain type apply for  $T_A$  =  $T_J$  = +25°C. Limits appearing in **boldface** type apply over the 0°C to +70°C range. (Continued)

$\begin{tabular}{ll} \textbf{TABLE 1. 5-Bit DAC Output Voltage Table} \\ (V_{CC} = 5V, \, V_{DD} = 12V \, \pm 5\%, \, T_A = 25^{\circ}C, \, Test \, Mode) \end{tabular}$

| Symbol              | Parameter                                         | Conditions     | Typical    | Units |

|---------------------|---------------------------------------------------|----------------|------------|-------|

| V <sub>DACOUT</sub> | 5-Bit DAC Output Voltages for Different VID Codes | VID4:0 = 01111 | 1.30       | V     |

|                     |                                                   | VID4:0 = 01110 | 1.35       |       |

|                     |                                                   | VID4:0 = 01101 | 1.40       |       |

|                     |                                                   | VID4:0 = 01100 | 1.45       |       |

|                     |                                                   | VID4:0 = 01011 | 1.50       |       |

|                     |                                                   | VID4:0 = 01010 | 1.55       |       |

|                     |                                                   | VID4:0 = 01001 | 1.60       |       |

|                     |                                                   | VID4:0 = 01000 | 1.65       |       |

|                     |                                                   | VID4:0 = 00111 | 1.70       |       |

|                     |                                                   | VID4:0 = 00110 | 1.75       |       |

|                     |                                                   | VID4:0 = 00101 | 1.80       |       |

|                     |                                                   | VID4:0 = 00100 | 1.85       |       |

|                     |                                                   | VID4:0 = 00011 | 1.90       |       |

|                     |                                                   | VID4:0 = 00010 | 1.95       |       |

|                     |                                                   | VID4:0 = 00001 | 2.00       |       |

|                     |                                                   | VID4:0 = 00000 | 2.05       |       |

|                     |                                                   | VID4:0 = 11111 | (shutdown) |       |

|                     |                                                   | VID4:0 = 11110 | 2.1        |       |

|                     |                                                   | VID4:0 = 11101 | 2.2        |       |

|                     |                                                   | VID4:0 = 11100 | 2.3        |       |

|                     |                                                   | VID4:0 = 11011 | 2.4        |       |

|                     |                                                   | VID4:0 = 11010 | 2.5        |       |

|                     |                                                   | VID4:0 = 11001 | 2.6        |       |

|                     |                                                   | VID4:0 = 11000 | 2.7        |       |

|                     |                                                   | VID4:0 = 10111 | 2.8        |       |

|                     |                                                   | VID4:0 = 10110 | 2.9        |       |

|                     |                                                   | VID4:0 = 10101 | 3.0        |       |

|                     |                                                   | VID4:0 = 10100 | 3.1        |       |

|                     |                                                   | VID4:0 = 10011 | 3.2        |       |

|                     |                                                   | VID4:0 = 10010 | 3.3        |       |

|                     |                                                   | VID4:0 = 10001 | 3.4        |       |

|                     |                                                   | VID4:0 = 10000 | 3.5        |       |

| in | Pin Name        | Pin Function                                                                                          |  |

|----|-----------------|-------------------------------------------------------------------------------------------------------|--|

| 1  | LG              | Low side N-FET gate driver output.                                                                    |  |

| 2  | PGND            | Ground for the two FET drivers of the switching section.                                              |  |

| 3  | V <sub>DD</sub> | Supply for the FET gate drivers. Usually tied to +12V.                                                |  |

| 4  | SNS2            | Feedback pin for the 1.5V linear regulator.                                                           |  |

| 5  | G2              | Gate drive output for the external N-MOS of the fast 1.5V linear regulator.                           |  |

| 6  | SGND            | Ground for internal signal circuitry and system ground reference.                                     |  |

| 7  | V <sub>cc</sub> | Supply voltage. Usually +5V.                                                                          |  |

| 8  | SNS1            | Output voltage monitor input for the switching regulator.                                             |  |

| 9  | CS+             | Switching regulator current sense input, positive node.                                               |  |

| 10 | CS-             | Switching regulator current sense input, negative node.                                               |  |

| 11 | СР              | Charge pump. Output is a square wave with 50% duty cycle. Amplitude is close to $V_{\rm CC}$ voltage. |  |

| 12 | FREQ            | Switching frequency adjustment pin. An external resistor is needed to set the desired frequency.      |  |

| 13 | EAO             | Output of the error amplifier. Used for compensating the switching regulator.                         |  |

| 14 | FB              | Inverting input of the error amplifier. Used for compensating the switching regulator.                |  |

| 15 | PWGD            | Open collector Power Good signal.                                                                     |  |

| 16 | VID4            | 5-Bit DAC input, MSB.                                                                                 |  |

| 17 | VID3            | 5-Bit DAC input.                                                                                      |  |

| 18 | VID2            | 5-Bit DAC input.                                                                                      |  |

| 19 | VID1            | 5-Bit DAC input.                                                                                      |  |

| 20 | VID0            | 5-Bit DAC input, LSB.                                                                                 |  |

| 21 | G3              | Gate drive pin for the external N-MOS of the 1.25V linear regulator.                                  |  |

| 22 | SNS3            | Feedback pin for the 1.25V linear regulator.                                                          |  |

| 23 | EN              | Output Enable. A logic low shuts the whole chip down.                                                 |  |

| 24 | HG              | High side N-FET gate driver output.                                                                   |  |

www.national.com 6

## Physical Dimensions inches (millimeters) unless otherwise noted LEAD NO 1 IDENTIFICATION -C-9 Н Н 12 **♦** 0.010 M A C S B $0.1043 \\ \underline{0.0926} \\ 2.65 \\ 2.35$ TYP ALL LEADS SEATING PLANE 8° MAX TYP-ALL LEADS TYP ALL LEADS M24B (REV F) 24-Lead Small Outline Package Order Number LM2638M NS Package Number M24B

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 1 80-530 85 86 Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-532 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconducto Asia Pacific Customer Response Group Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507