# LM1971 *Overture* TM Audio Attenuator Series Digitally Controlled 62 dB **Audio Attenuator with/Mute**

## **General Description**

The LM1971 is a digitally controlled single channel audio attenuator fabricated on a CMOS process. Attenuation is variable in 1 dB steps from 0 dB to -62 dB. A mute function disconnects the input from the output, providing over 100 dB of attenuation.

The performance of the device is exhibited by its ability to change attenuation levels without audible clicks or pops. In addition, the LM1971 features a low Total Harmonic Distortion (THD) of 0.0008%, and a Dynamic Range of 115 dB, making it suitable for digital audio needs. The LM1971 is available in both 8-pin plastic DIP or SO packages.

The LM1971 is controlled by a TTL/CMOS compatible 3-wire serial digital interface. The active low LOAD line enables the data input registers while the CLOCK line provides system timing. Its DATA pin receives serial data on the rising edge of each CLOCK pulse, allowing the desired attenuation setting to be selected.

# **Key Specifications**

■ Total harmonic distortion 0.0008% (typ)

■ Frequency response > 200 kHz (-3 dB) (typ)

■ Attenuation range (excluding mute) 62 dB (typ)

115 dB (typ) ■ Dvnamic range

Mute attenuation 102 dB (typ)

#### **Features**

- 3-wire serial interface

- Mute function

- Click and pop free attenuation changes

- 8-pin plastic DIP and SO packages available

## **Applications**

- Communication systems

- Cellular Phones and Pagers

- Personal computer audio control

- Electronic music (MIDI)

- Sound reinforcement systems

- Audio mixing automation

TL/H/12353-1

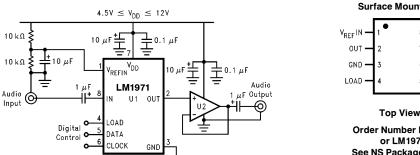

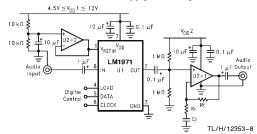

# **Typical Application**

# **Connection Diagram**

FIGURE 1. Typical Audio Attenuator Application Circuit

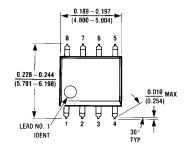

**Dual-In-Line Plastic or Surface Mount Package**

Order Number LM1971M or LM1971N See NS Package Number M08A or N08E

Overture™ is a trademark of National Semiconductor Corporation.

## **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage, V<sub>DD</sub> 15V

Voltage at any pin (GND -0.2V) to (V<sub>DD</sub> +0.2V)

ESD Susceptibility (Note 4) 3000V

Soldering Information

N Package (10s) 260°C

M Package

Vapor Phase (60s) 215°C

Infrared (15s) 220°C

Power Dissipation (Note 3) \$150 mW Junction Temperature  $150 ^{\circ} \text{C}$  Storage Temperature  $-65 ^{\circ} \text{C}$  to  $+150 ^{\circ} \text{C}$

## Operating Ratings (Notes 1, 2)

Temperature Range

$T_{MIN} \le T_A \le T_{MAX}$   $-20^{\circ}C \le T_A \le +85^{\circ}C$

Thermal Resistance

M08A Package, θ<sub>JA</sub> 167°C/W N08E Package, θ<sub>JA</sub> 102°C/W Supply Voltage 4.5V to 12V

**Electrical Characteristics** (Notes 1, 2) The following specifications apply for  $V_{DD}=\pm 12V$  ( $V_{REF}IN=\pm 6V$ ),  $V_{IN}=5.5\ V_{pk}$ , and  $f=1\ kHz$ , unless otherwise specified. Limits apply for  $T_A=25^{\circ}C$ . Digital inputs are TTL and CMOS compatible.

| Symbol            | Parameter                    | Conditions                                                                                             | LM1971                                  |                                         | Units                                                    |

|-------------------|------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------|

|                   |                              |                                                                                                        | Typical<br>(Note 5)                     | Limit<br>(Note 6)                       | (Limits)                                                 |

| I <sub>S</sub>    | Supply Current               | Digital Inputs Tied to 6V                                                                              | 1.8                                     | 3                                       | mA (max)                                                 |

| THD               | Total Harmonic Distortion    | V <sub>IN</sub> = 0.5 V <sub>pk</sub> @ 0 dB Attenuation                                               | 0.0008                                  | 0.003                                   | % (max)                                                  |

| e <sub>IN</sub>   | Noise                        | Input is AC Grounded @ -12 dB Attenuation A-Weighted (Note 7)                                          | 4.0                                     |                                         | μV                                                       |

| DR                | Dynamic Range                | Referenced to Full Scale $= +6 V_{pk}$                                                                 | 115                                     |                                         | dB                                                       |

| A <sub>M</sub>    | Mute Attenuation             |                                                                                                        | 102                                     | 96                                      | dB (min)                                                 |

|                   | Attenuation Step Size Error  | 0 dB to -62 dB                                                                                         | 0.009                                   | 0.2                                     | dB (max)                                                 |

|                   | Absolute Attenuation         | Attenuation @ 0 dB Attenuation @ -20 dB Attenuation @ -40 dB Attenuation @ -60 dB Attenuation @ -62 dB | 0.1<br>-20.3<br>-40.5<br>-60.6<br>-62.6 | 0.5<br>-19.0<br>-38.0<br>-57.0<br>-59.0 | dB (min)<br>dB (min)<br>dB (min)<br>dB (min)<br>dB (min) |

| I <sub>LEAK</sub> | Analog Input Leakage Current | Input is AC Grounded                                                                                   | 5.8                                     | 100                                     | nA (max)                                                 |

|                   | Frequency Response           | 20 Hz-100 kHz                                                                                          | ±0.1                                    |                                         | dB                                                       |

| R <sub>IN</sub>   | AC Input Impedance           | $Pin 8, V_{IN} = 1.0 V_{pk}, f = 1 kHz$                                                                | 40                                      | 20<br>60                                | $k\Omega$ (min) $k\Omega$ (max)                          |

| I <sub>IN</sub>   | Input Current                | @ Pins 4, 5, 6 @ 0V < V <sub>IN</sub> < 5V                                                             | 1.0                                     | 100                                     | nA (max)                                                 |

| f <sub>CLK</sub>  | Clock Frequency              |                                                                                                        | 3                                       | 2                                       | MHz (max)                                                |

| V <sub>IH</sub>   | High-Level Input Voltage     | @ Pins 4, 5, 6                                                                                         |                                         | 2.0                                     | V (min)                                                  |

| V <sub>IL</sub>   | Low-Level Input Voltage      | @ Pins 4, 5, 6                                                                                         |                                         | 0.8                                     | V (max)                                                  |

Note 1: All voltages are measured with respect to the GND pin (pin 3), unless otherwise specified.

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_D = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For the LM1971N and LM1971M,  $T_{JMAX} = +150^{\circ}\text{C}$ , and the typical junction-to-ambient thermal resistance,  $\theta_{JA}$ , when board mounted is 102° C/W and 167° C/W, respectively.

Note 4: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 5: Typicals are measured at 25°C and represent the parametric norm.

Note 6: Limits are guarantees that all parts are tested in production to meet the stated values.

Note 7: Due to production test limitations, there is no limit for the Noise test. Please refer to the noise measurements in the Typical Performance Characteristics section.

## **Pin Description**

$\textbf{V}_{\textbf{REF}}\textbf{IN}$  (1): The  $\textbf{V}_{\textbf{REF}}\textbf{IN}$  pin provides the reference for the analog input signal. This pin should be biased at half of the supply voltage,  $\textbf{V}_{\text{DD}}$ , as shown in Figures 1 and 6.

**OUT (2):** The attenuated analog output signal comes from this pin.

**GND** (3): The GND pin references the digital input signals and is the lower voltage reference for the IC. Typically this pin would be labeled " $V_{SS}$ " but the ground reference for the digital logic input control is tied to this same point. With a higher pin-count there would generally be separate pins for these functions;  $V_{SS}$  and Logic Ground. It is intended that the LM1971 always be operated using a single voltage supply configuration, for which pin 3 (GND) should always be at system ground. If a bipolar or split-supply configuration are desired, level shifting circuitry is needed for the digital logic control pins as they would be referenced through pin 3 which would be at the negative supply. It is highly recommended, however, that the LM1971 be used in a unipolar or single-supply configuration.

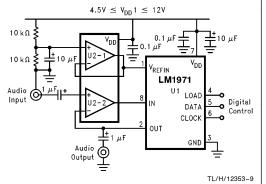

### Connection Diagram (Continued)

TL/H/12353-2

**LOAD (4):** The LOAD input accepts a TTL or CMOS level signal. This is the enable pin of the device, allowing data to be clocked in while this input is low (0V). The GND pin is the reference for this signal.

**DATA (5):** The DATA input accepts a TTL or CMOS level signal. This pin is used to accept serial data from a microcontroller that will be latched and decoded to change the channel's attenuation level. The GND pin is the reference for this signal.

**CLOCK (6):** The CLOCK input accepts a TTL or CMOS level signal. The clock input is used to load data into the internal shift register on the rising edge of the input clock waveform. The GND pin is the reference for this signal.

$\mathbf{V}_{\mathbf{DD}}$  (7): The positive voltage supply should be placed to this pin.

IN (8): The analog input signal should be placed to this pin.

## **Application Information**

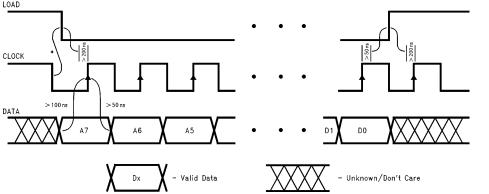

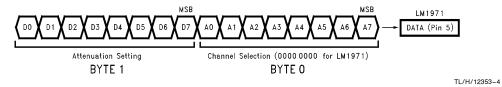

### SERIAL DATA FORMAT

The LM1971 uses a 3-wire serial communication format that is easily controlled by a microcontroller. The timing for the 3-wire set, comprised of DATA, CLOCK, and LOAD is shown in *Figure 2*. As depicted in *Figure 2*, the LOAD line is to go low at least 150 ns before the rising edge of the first clock pulse and is to remain low throughout the transmission of the 16 data bits. The serial data is composed of an 8-bit address, which must always be set to 0000 0000 to select the single audio channel, and 8 bits for attenuation setting. For both address data and attenuation setting data, the MSB is sent first with the address data preceding the attenuation data. Please refer to *Figure 3* to confirm the serial data format transfer process.

Table I shows the various Address and Data byte values for different attenuation settings. Note that Address bytes other than 0000 0000 are ignored.

#### $\mu$ POT SYSTEM ARCHITECTURE

The  $\mu$ Pot's digital interface is essentially a shift register where serial data is shifted in, latched, and then decoded. Once new data is shifted in, the LOAD line goes high, latching in the new data. The data is then decoded and the appropriate switch is activated to set the desired attenuation level. This process is continued each and every time an attenuation change is made. When the uPot is powered up, it is placed into the Mute mode.

#### $\mu$ POT DIGITAL COMPATIBILITY

The  $\mu$ Pot's digital interface section is compatible with TTL or CMOS logic. The shift register inputs act upon a threshold of two diode drops above the ground level (Pin 3) or approximately 1.4V.

**TABLE I. Attenuator Register Set Description**

| Address Register (Byte 0) |                  |  |  |  |

|---------------------------|------------------|--|--|--|

| MSB LSB<br>A7-A0          |                  |  |  |  |

| 0000 0000                 | Channel 1        |  |  |  |

| 0000 0001                 | Ignored          |  |  |  |

| 0000 0010                 | Ignored          |  |  |  |

| Data Register (Byte 1)    |                  |  |  |  |

| Contents                  | Attenuation (dB) |  |  |  |

| MSB LSB<br>D7-D0          |                  |  |  |  |

| 0000 0000                 | 0.0              |  |  |  |

| 0000 0001                 | 1.0              |  |  |  |

| 0000 0010                 | 2.0              |  |  |  |

| 0000 0011                 | 3.0              |  |  |  |

|                           | ::               |  |  |  |

| 0001 0000                 | 16.0             |  |  |  |

| 0001 0001                 | 17.0             |  |  |  |

| 0001 0010                 | 18.0             |  |  |  |

| 0001 0011                 | 19.0             |  |  |  |

|                           | ::               |  |  |  |

| 0011 1101                 | 61.0             |  |  |  |

| 0011 1110                 | 62.0             |  |  |  |

| 0011 1111                 | 96 (Mute)        |  |  |  |

| 0100 0000                 | 96 (Mute)        |  |  |  |

| ::::                      | ::               |  |  |  |

| 1111 1110                 | 96 (Mute)        |  |  |  |

| 1111 1111                 | 96 (Mute)        |  |  |  |

# **Application Information (Continued)**

TL/H/12353-3

\*Note: Load and clock falling edges can be coincident, however, the clock falling edge cannot be delayed more than 20 ns from the falling edge of load. It is preferrable that the falling edge of clock occurs before the falling edge of load.

#### FIGURE 2. Timing Diagram

FIGURE 3. Serial Data Format Transfer Process

## **Application Information (Continued)**

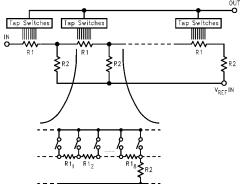

# $\mu$ POT LADDER ARCHITECTURE

The  $\mu Pot$  contains a chain of R1/R2 resistor dividers in a ladder form, as shown in Figure 4. Each R1 is actually a series of 8 resistors, with a CMOS switch that taps into the resistor chain according to the attenuation level chosen. For any given attenuation setting, there is only one CMOS switch closed (no paralleling of ladders). The input impedance therefore remains constant, while the output impedance changes as the attenuation level changes. It is important to note that the architecture is a series of resistor dividers, and not a straight, tapped resistor, so the  $\mu Pot$  is not a variable resistor; it is a variable voltage divider.

TL/H/12353-5 FIGURE 4. Resistor Ladder Architecture

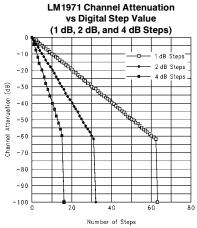

#### ATTENUATION STEP SCHEME

The fundamental attenuation step scheme for the LM1971 is shown in *Figure 5*. It is also possible to obtain any integer value attenuation step through programming, in addition to the 2 dB and 4 dB steps shown in *Figure 5*. All higher attenuation step schemes can have clickless and popless performance. Although it is possible to "skip" attenuation points by not sending all of the data, clickless and popless performance will suffer. It is highly recommended that all of the data points should be sent for each attenuation level. This insures flawless operation and performance when making steps larger than 1 dB.

TL/H/12353-6 FIGURE 5. LM1971 Attenuation Step Scheme

#### INPUT IMPEDANCE

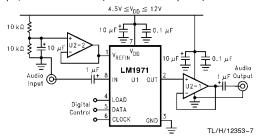

The input impedance of a  $\mu Pot$  is constant at a nominal 40 k $\Omega.$  Since the LM1971 is a single-supply operating device, it is necessary to have both input and output coupling caps as shown in Figure 1. To ensure full low-frequency response, a 1  $\mu F$  coupling cap should be used.

#### **OUTPUT IMPEDANCE**

The output impedance of a  $\mu$ Pot varies typically between 25 k $\Omega$  and 35 k $\Omega$  and changes nonlinearly with step changes. Since a  $\mu$ Pot is made up of a resistor ladder network with logarithmic attenuation, the output impedance is nonlinear. Due to this configuration, a  $\mu$ Pot cannot be considered as a linear potentiometer; it is a logarithmic attenuator.

The linearity of a  $\mu Pot$  cannot be measured directly without a buffer because the input impedance of most measurement systems is not high enough to provide the required accuracy. The lower impedance of the measurement system would load down the output and an incorrect reading would result. To prevent loading, a JFET input op amp should be used as the buffer/amplifier.

#### **OUTPUT BUFFERING**

There are two performance issues to be aware of that are related to a  $\mu Pot$ 's output stage. The first concern is to prevent audible clicks with attenuation changes, while the second is to prevent loading and subsequent linearity errors. The output stage of a  $\mu Pot$  needs to be buffered with a low input bias current op amp to keep DC shifts inaudible. Additionally, the output of  $\mu Pot$  needs to see a high impedance to keep linearity errors low.

Attenuation level changes cause changes in the output impedance of a µPot. Output impedance changes in the presence of a large input bias current for a buffer/amplifier will cause a DC shift to occur. Neglecting amplifier gains and speaker sensitivities, the audibility of a DC shift is dependent upon the output impedance change times the required input bias current. As an example, a 5 k $\Omega$  impedance change times a 1  $\mu$ A bias current results in a 5 mV DC shift; a level that is barely audible without any music material in the system. An op amp with a bias current of 200 pA for the same 5 k $\Omega$  change results in an inaudible 1  $\mu$ V DC shift. Since the worst case output impedance changes are on the order of several  $k\Omega$ , a bias current much less than 1  $\mu$ A is required for highest performance. In order to further quantify DC shifts, please refer to the Output Impedance vs Attenuation graph in the Typical Performance Characteristics section and relate worst case impedance changes to the selected buffer/amplifier input bias current.

Without the use of a high input impedance ( $> 1~M\Omega$ ) op amp for the buffer/amplifier, loading will occur that causes linearity errors in the signal. To insure the highest level of performance, a JFET or CMOS input high input impedance op amp is required.

### **Application Information (Continued)**

One common application that requires gain at the output of a  $\mu Pot$  is input signal volume control. Depending upon the input source material, the LM1971 provides a means of controlling the input signal level. With a supply voltage range of 4.5V to 12V, the LM1971 has the ability of controlling fairly inconsistent input source signal levels. Using an op amp with gain at the  $\mu Pot$ 's output, as shown in Figure~7, will also allow the system dynamic range to be increased. JFET op amps like the LF351 and the LF411 are well suited for this application. If active half-supply buffering is also desired, dual op amps like the LF353 and the LF412 could be used. For low voltage supply applications, op amps like the CMOS LMC6041 are preferred. This part has a supply operating range from 4.5V–15.5V and also comes in a surface mount package.

#### $\mu$ POT HALF-SUPPLY REFERENCING

The LM1971 operates off of a single supply, with half-supply biasing supplied at the  $V_{\mbox{\footnotesize{\rm REFIN}}}$  terminal (Pin 1). The easiest and most cost effective method of providing this half-supply is a simple resistor divider and bypass capacitor network shown in  $\it Figure~1$ . The capacitor not only stabilizes the half-supply node by "holding" the voltage nearly constant, but also decouples high frequency signals on the supply to ground. Signal feedthrough, power supply ripple and fluctuations that are not properly filtered could cause the performance of the LM1971 to be degraded.

A more stable half-supply node can be obtained by actively buffering the resistor divider network with a voltage follower as shown in Figure~6. Supply fluctuations are then isolated by the high input impedance/low output impedance mismatch associated with effective filtering. Since the LM1971 is a single channel device, using a dual JFET input op amp is optimum for both output buffering and half-supply biasing. A 10  $\mu F$  capacitor or larger is recommended for better half-supply stabilization. For added rejection of higher frequency power supply fluctuations, a smaller capacitor (0.01  $\mu F$  –0.1  $\mu F$ ) could be added in parallel to the 10  $\mu F$  capacitor.

#### FIGURE 6. Higher Performance Active Half-Supply Buffering

FIGURE 7. Active Reference with Active Gain Buffering

#### LOGARITHMIC GAIN AMPLIFIER

The  $\mu$ Pot is capable of being used in the feedback loop of an op amp to create a gain controlled amplifier as shown in Figure 8. In this configuration the attenuation levels from Table I become gain levels with the largest possible gain value being 62 dB. For most applications, 62 dB of gain will cause signal clipping to occur. However, this can be controlled through programming. It is important to note that when in mute mode the input is disconnected from the output, thus placing the amplifier in open-loop gain state. In this mode, the amplifier will behave as a comparator. Care should be taken with the programming and design of this type of circuit. To provide the best overall performance, a high input impedance, low input bias current op amp should be used

FIGURE 8. Logarithmic Gain Amplifier Circuit

#### **MUTE FUNCTION**

A major feature of the LM1971 is its ability to mute the input signal to an attenuation level of 102 dB. This is accomplished internally by physically disconnecting the output from the input while also grounding the output pin through approximately  $2 \, \mathrm{k}\Omega$ .

The mute function is obtained during power-up of the device or by sending any binary data of 0011 1111 and above serially to the device. The device may be placed into mute at any time during operation, allowing the designer to make the mute command accessible to the end-user.

#### DC INPUTS

Although the  $\mu$ Pot was designed to be used as an attenuator for signals within the audio spectrum, it is also capable of tracking and attenuating an input DC voltage. The device will track voltages to either supply rail.

One point to remember about DC tracking is that with a buffer at the output of the  $\mu Pot$ , the resolution of DC tracking will depend upon the gain configuration of that output buffer and its supply voltage. Also, the output buffer's supply voltage does not have to be the same as the  $\mu Pot$ 's supply voltage. Giving the buffer some gain can provide more resolution when tracking small DC voltages.

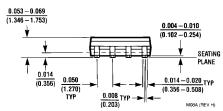

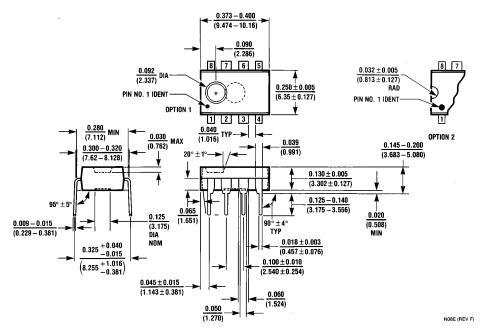

# Physical Dimensions inches (millimeters) unless otherwise noted

Order Number LM1971M 8-Lead (0.150" Wide) Molded Small Outline Package, JEDEC NS Package Number M08A

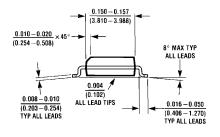

# Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

Order Number LM1971N 8-Lead (0.300" Wide) Molded Dual-In-Line Package NS Package Number N08E

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

http://www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Fax: +49 (0) 180-530 so so Email: europe.support@nsc.com Deutsch Tel: +49 (0) 180-530 85 85 English Tel: +49 (0) 180-532 78 32 Français Tel: +49 (0) 180-532 95 58 Italiano Tel: +49 (0) 180-534 16 80

National Semiconductor Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon

Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2308

Fax: 81-043-299-2408