# DS90C387/DS90CF388 +3.3V LVDS 24-Bit Dual Pixel Flat Panel Display (FPD) Link—SVGA to UXGA

#### **General Description**

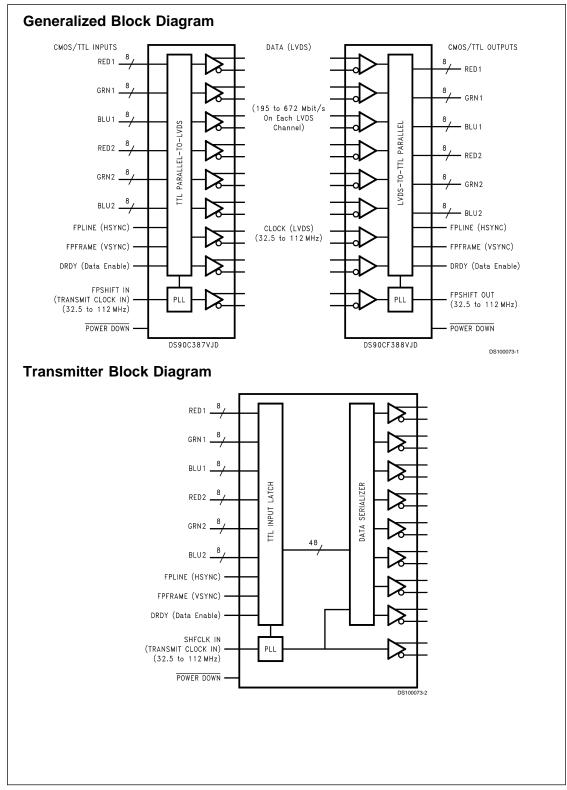

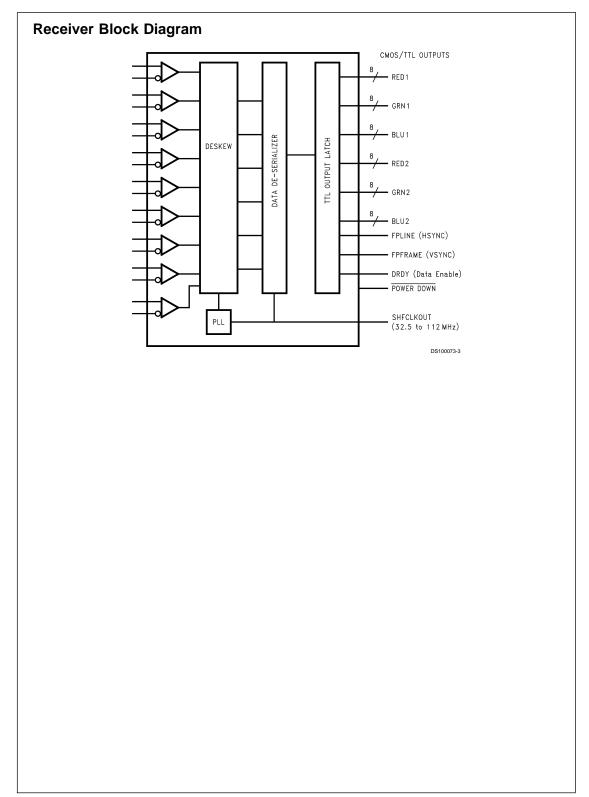

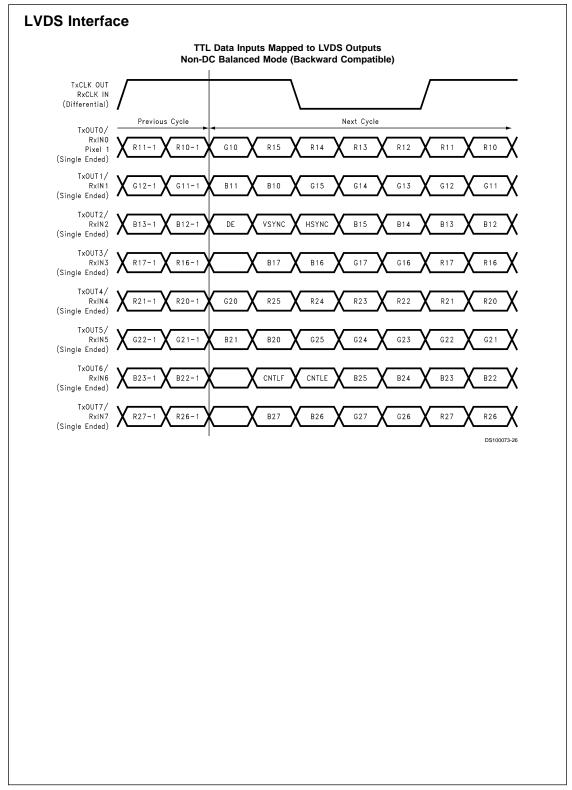

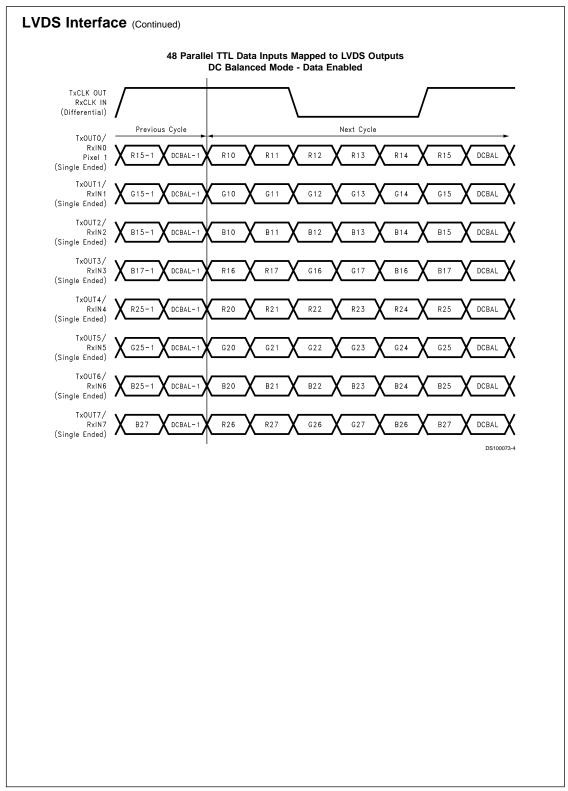

The DS90C387/DS90CF388 transmitter/receiver pair is designed to support dual pixel data transmission between Host and Flat Panel Display up to UXGA resolutions. The transmitter converts 48 bits of CMOS/TTL data into 8 LVDS (Low Voltage Differential Signalling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a ninth LVDS link. Every cycle of the transmit clock 48 bits of RGB input data are sampled and transmitted. The receiver converts the LVDS data streams back into 48 bits of CMOS/TTL data. Control bits (FPLINE, FPFRAME and DRDY) are transmitted over 3 LVDS lines during the blanking interval. At a transmit clock frequency of 112 MHz, 48 bits of RGB data are transmitted at an effective rate of 672 Mbps per LVDS data channel. Using a 112 MHz clock, the data throughput is 672 Megabytes (5.38 Gbits) per second. The transmitter may also provide a single pixel interface to the graphic controller, accepting clock speeds up to 170MHz. Data is split into 'even' and 'odd' pixels for transmission across the LVDS interface and at the receiver outputs.

National Semiconductor

The transmitter is designed to reject cycle-to-cycle jitter which may be seen at the transmitter input clock. Very low cycle-to-cycle jitter is passed on to the transmitter outputs. This significantly reduces the impact of jitter provided by the input clock source, and improves the accuracy of data sampling. Data sampling is further enhanced by automatically calibrated data sampling strobes at the receiver inputs. Timing and control signals are sent during blanking intervals to guarantee correct reception of these critical signals.

The DS90C387/8 chipset is designed to support both notebook and monitor applications. The cable deskew circuitry, pre-emphasis and encoded dc balance support the requirements of a longer cable interface at high speeds.

The transmitter is offered with programmable edge data strobes for convenient interface with a variety of graphics controllers. The transmitter can be programmed for rising edge strobe or falling edge strobe through a dedicated pin. A rising edge transmitter will inter-operate with a falling edge receiver without any translation logic. The chipset is an ideal means to solve EMI and cable size problems associated with wide, high speed TTL interfaces.

#### Features

- 32.5 MHz to 112 MHz input clock supports single pixel XGA and SXGA, dual pixel UXGA

- Dual pixel architecture supports interface to GUI and timing controller; optional single pixel transmitter inputs support single pixel GUI interface

- Automatically calibrated receiver sampling strobes

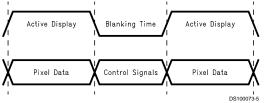

- Timing and control signals transmitted during blanking interval for improved reliability

- EMI reduction circuitry

- Pre-emphasis, deskew and dc balance coding support

- longer cable drive (5 meters) for monitor applications

- Flow-through pinout

- 50% receiver output clock duty cycle for lower EMI and easy timing controller interface

- Stopped RxCLKOUT" indicator pin

- Transmitter rejects cycle-to-cycle jitter

- Programmable transmitter data and control strobe select (Rising or Falling edge strobe)

- Backward compatible configuration select

- Transmitter provides optional second LVDS clock for backward compatibility

- Support for two additional user defined control signals

- Single +3.3V supply

- Up to 5.38 Gbits/sec bandwidth

- UDS signaling reduces cable size

- Compatible with TIA/EIA-644 LVDS standard

- Designed on a non-proprietary CMOS process for easy integration

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

## LVDS Interface (Continued)

Control Signals Transmitted During Blanking

### Control Signals Transmitted During Blanking

|                |                 |          | 0 0                      |

|----------------|-----------------|----------|--------------------------|

| Control Signal | Signal<br>Level | Channel  | Pattern                  |

| DE             | HIGH            | TxCLKOUT | 1111000<br>or<br>1110000 |

|                | LOW             |          | 1111100<br>or<br>1100000 |

| HSYNC          | HIGH            | τχουτο   | 1100000<br>or<br>1111100 |

|                | LOW             |          | 1110000<br>or<br>1111000 |

| VSYNC          | нідн            | TXOUT1   | 1100000<br>or<br>1111100 |

|                | LOW             |          | 1110000<br>or<br>1111000 |

| CNTLF          | HIGH            | TXOUT4   | 1100000<br>or<br>1111100 |

|                | LOW             |          | 1110000<br>or<br>1111000 |

| CNTLE          | нідн            | TXOUT5   | 1100000<br>or<br>1111100 |

|                | LOW             |          | 1110000<br>or<br>1111000 |

|                | -               | •        | DS100073-9               |

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> )     | -0.3V to +4V                      |

|---------------------------------------|-----------------------------------|

| CMOS/TTL Input Voltage                | -0.3V to (V <sub>CC</sub> + 0.3V) |

| CMOS/TTL Output<br>Voltage            | -0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Receiver Input<br>Voltage        | -0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Driver Output<br>Voltage         | -0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Output Short Circuit<br>Duration | Continuous                        |

| Junction Temperature                  | +150°C                            |

| Storage Temperature                   | –65°C to +150°C                   |

| Lead Temperature                      |                                   |

| (Soldering, 4 sec.)                   | +260°C                            |

| Maximum Package Power Diss            | ipation Capacity @ 25°C           |

| 100 TQFP Package:                 |       |      |        |                  |

|-----------------------------------|-------|------|--------|------------------|

| DS90C387                          |       |      |        | TBD              |

| DS90CF388                         |       |      |        | TBD              |

| Package Derating:                 |       |      |        |                  |

| DS90C387                          |       | TBI  | O mW/℃ | C above<br>+25°C |

| DS90CF388                         |       | TBE  | O mW/° | C above<br>+25°C |

| Recommended (<br>Conditions       | Opera | ting |        |                  |

|                                   | Min   | Nom  | Max    | Units            |

| Supply Voltage (V <sub>CC</sub> ) | 3.0   | 3.3  | 3.6    | V                |

| Supply voltage (v <sub>CC</sub> ) | 3.0 | 3.3 | 3.0 | v          |  |

|-----------------------------------|-----|-----|-----|------------|--|

| Operating Free Air                |     |     |     |            |  |

| Temperature (T <sub>A)</sub>      | -10 | +25 | +70 | °C         |  |

| Receiver Input Range              | C   | )   | 2.4 | V          |  |

| Supply Noise Voltage ( $V_{CC}$ ) |     |     | 100 | $mV_{p-p}$ |  |

#### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol          | Parameter                                                        | Conditions                                                            |                                 | Min  | Тур   | Max             | Unit |

|-----------------|------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------|------|-------|-----------------|------|

| CMOS/TT         | L DC SPECIFICATIONS                                              | 1                                                                     |                                 |      |       |                 |      |

| VIH             | High Level Input Voltage                                         |                                                                       |                                 | 2.0  |       | V <sub>cc</sub> | V    |

| VIL             | Low Level Input Voltage                                          |                                                                       |                                 | GND  |       | 0.8             | V    |

| V <sub>он</sub> | High Level Output Voltage                                        | I <sub>OH</sub> = -0.4 mA                                             |                                 | TBD  | TBD   |                 | V    |

|                 |                                                                  | I <sub>OH</sub> = -2mA                                                |                                 | TBD  | TBD   |                 | V    |

| V <sub>OL</sub> | Low Level Output Voltage                                         | I <sub>OL</sub> = 2 mA                                                |                                 |      | 0.1   | 0.3             | V    |

| V <sub>CL</sub> | Input Clamp Voltage                                              | I <sub>CL</sub> = -18 mA                                              |                                 |      | -0.79 | -1.5            | V    |

| I <sub>IN</sub> | Input Current                                                    | $V_{IN} = 0.4V$ , 2.5V or $V_{CC}$                                    |                                 |      | +1.8  | +10             | μA   |

|                 |                                                                  | V <sub>IN</sub> = GND                                                 |                                 | -10  | 0     |                 | μA   |

| l <sub>os</sub> | Output Short Circuit Current                                     | V <sub>OUT</sub> = 0V                                                 |                                 |      |       | -120            | mA   |

| LVDS DR         | IVER DC SPECIFICATIONS                                           | 1                                                                     |                                 |      |       |                 |      |

| V <sub>OD</sub> | Differential Output Voltage                                      | $R_{L} = 100\Omega$                                                   |                                 | 250  | 345   | 450             | m\   |

| $\Delta V_{OD}$ | Change in V <sub>OD</sub> between<br>Complimentary Output States |                                                                       |                                 |      | 35    | m∖              |      |

| V <sub>os</sub> | Offset Voltage                                                   |                                                                       | 1.125                           | 1.25 | 1.375 | V               |      |

| $\Delta V_{os}$ | Change in V <sub>os</sub> between<br>Complimentary Output States |                                                                       |                                 |      |       | 35              | m∖   |

| los             | Output Short Circuit Current                                     | $V_{OUT} = 0V, R_L = 100\Omega$                                       |                                 | -3.5 | -5    | mA              |      |

| loz             | Output TRI-STATE® Current                                        | $\overline{Powerdown} = 0V, V_{OUT} = 0V \text{ or } V_{CC}$          |                                 |      | ±1    | ±10             | μA   |

| LVDS RE         | CEIVER DC SPECIFICATIONS                                         | 1                                                                     |                                 |      |       |                 |      |

| V <sub>TH</sub> | Differential Input High<br>Threshold                             | V <sub>CM</sub> = +1.2V                                               |                                 |      |       | +100            | m∖   |

| V <sub>TL</sub> | Differential Input Low<br>Threshold                              |                                                                       |                                 | -100 |       |                 | m\   |

| I <sub>IN</sub> | Input Current                                                    | V <sub>IN</sub> = +2.4V, V <sub>CC</sub> = 3.6V                       | $V_{IN} = +2.4V, V_{CC} = 3.6V$ |      |       | ±10             | μA   |

|                 |                                                                  | $V_{IN} = 0V, V_{CC} = 3.6V$                                          |                                 |      |       | ±10             | μA   |

| TRANSM          | TTER SUPPLY CURRENT                                              |                                                                       |                                 |      |       |                 |      |

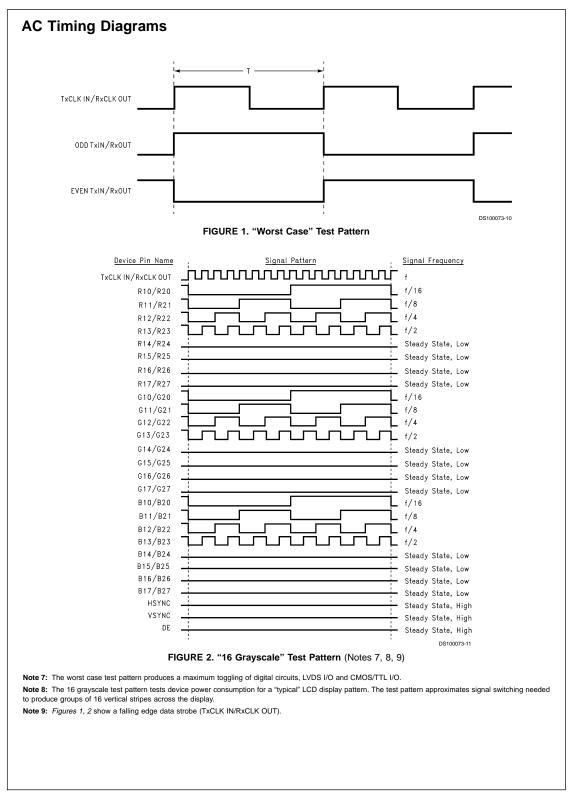

| ICCTW           | Transmitter Supply Current                                       | rrent $R_{L} = 100\Omega, C_{L} = 5 \text{ pF}, f = 32.5 \text{ MHz}$ |                                 |      | TBD   | TBD             | mA   |

|                 | Worst Case                                                       | Worst Case Pattern                                                    | f = 65 MHz                      |      | TBD   | TBD             | mA   |

|                 |                                                                  | (Figures 1, 3)                                                        | f = 112 MHz                     |      | TBD   | TBD             | m/   |

### Electrical Characteristics (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified. Conditions Min Мах Units Symbol Parameter Тур TRANSMITTER SUPPLY CURRENT ICCTG  $R_{L} = 100\Omega, C_{L} = 5 \text{ pF},$ TBD TBD Transmitter Supply Current f = 32.5 MHz mΑ 16 Grayscale 16 Grayscale Pattern TBD f = 65 MHz TBD mΑ (Figures 2, 3) f = 112 MHz TBD TBD mΑ ICCTZ Transmitter Supply Current Powerdown = Low TBD 150 μA Power Down Driver Outputs in TRI-STATE under Powerdown Mode RECEIVER SUPPLY CURRENT ICCRW **Receiver Supply Current**  $C_{L} = 8 \text{ pF},$ f = 32.5 MHz TBD TBD mΑ Worst Case Pattern Worst Case f = 65 MHz TBD TBD mΑ (Figures 1, 4) f = 112 MHz TBD TBD mΑ ICCRG Receiver Support Current  $C_L = 8 \text{ pF},$ f = 32.5 MHz TBD TBD mΑ 16 Grayscale 16 Grayscale Pattern f = 65 MHz TBD TBD mΑ (Figures 2, 4) f = 112 MHz TBD TBD mΑ ICCRZ **Receiver Supply Current**  $\overline{Powerdown} = Low$ TBD 150 μA Power Down Receiver Outputs stay low during Power down mode.

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

Note 2: Typical values are given for V\_{CC} = 3.3V and T  $_{A}$  = +25  $^{\circ}C.$

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except V<sub>OD</sub> and  $\Delta$ V<sub>OD</sub>).

| Symbol | Parameter Min                                                                   |                            |             | Typ M      |       | ax        | Units    |

|--------|---------------------------------------------------------------------------------|----------------------------|-------------|------------|-------|-----------|----------|

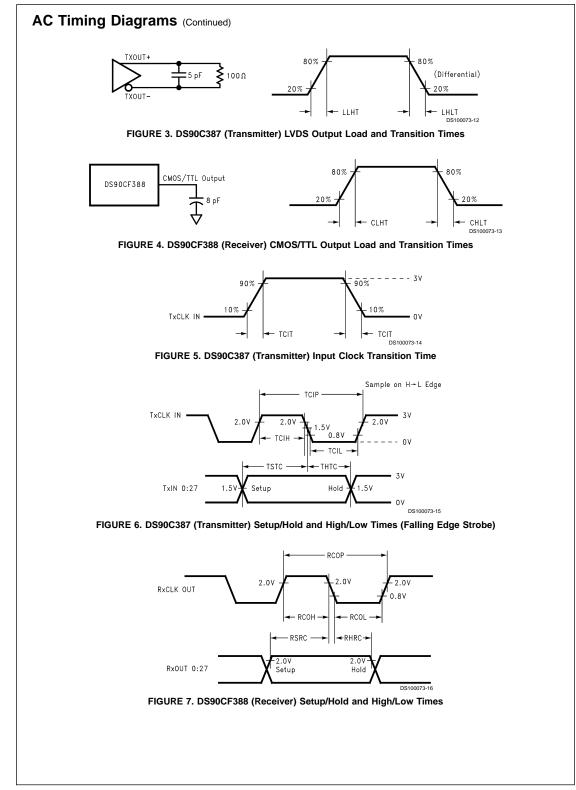

| тсіт   | TxCLK IN Transition Time (Figure 5)                                             |                            |             |            | TE    | 3D        | ns       |

| TCIP   | TxCLK IN Period (Figure 6)                                                      |                            |             | T 30       |       | .77       | ns       |

| TCIH   | TxCLK in High Time (Figure 6)                                                   |                            | 0.35T       | 0.5T 0.6   |       | 5T        | ns       |

| TCIL   | TxCLK in Low Time ( <i>Figure 6</i> ) 0.35T                                     |                            | 0.5T        | 0.5T 0.65T |       | ns        |          |

|        | nitter Switching Character                                                      |                            | therwise sp | ecified.   |       |           |          |

| Symbol | Parameter                                                                       |                            |             | Min        | Тур   | Max       | Unit     |

| LLHT   | LVDS Low-to-High Transition Time (Figur                                         | re 3)                      |             |            |       | TBD       | ns       |

| LHLT   | LVDS High-to-Low Transition Time (Figur                                         | re 3)                      |             |            |       | TBD       | ns       |

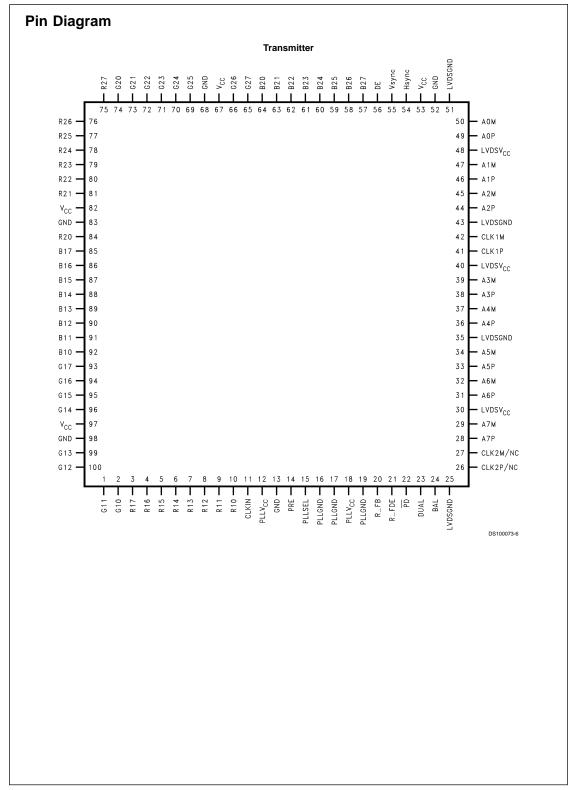

| TPPos0 | Transmitter Output Pulse<br>Position for Bit 0 ( <i>Figure 14</i> )<br>(Note 4) | f = 112 MHz                |             | -200       | 0     | +200      | ps       |

| TPPos1 | Transmitter Output Pulse<br>Position for Bit 1                                  |                            |             | 1.076      | 1.276 | 1.476     | ns       |

| TPPos2 | Transmitter Output Pulse<br>Position for Bit 2                                  |                            |             | 2.351      | 2.551 | 2.751     | ns       |

| TPPos3 | Transmitter Output Pulse<br>Position for Bit 3                                  |                            |             | 3.626      | 3.826 | 4.026     | ns       |

| TPPos4 | Transmitter Output Pulse<br>Position for Bit 4                                  |                            |             | 4.902      | 5.102 | 5.302     | ns       |

| TPPos5 | Transmitter Output Pulse<br>Position for Bit 5                                  | _                          |             | 6.178      | 6.378 | 6.578     | ns       |

| TPPos6 | Transmitter Output Pulse<br>Position for Bit 6                                  |                            |             | 7.453      | 7.653 | 7.853     | ns       |

| TSTC   | TxIN Setup to TxCLK IN (Figure 6)                                               |                            |             | 3.5        |       |           | ns       |

| THTC   | TxIN Hold to TxCLK IN (Figure 6)                                                |                            | -)          | 0.5        | 0     |           | ns       |

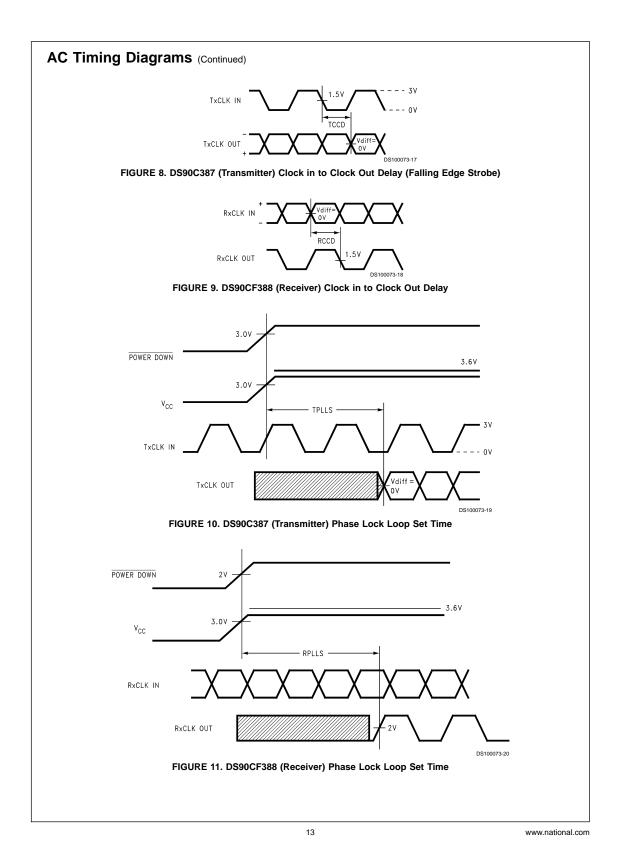

| TCCD   | TxCLK IN to TxCLK OUT Delay @ 25°C,                                             |                            | ire 8)      | TBD        | 3.7   | TBD       | ns       |

| TICC   | TxCLK IN to TxCLK OUT Delay (Figure &                                           |                            |             | TBD        | 3.7   | TBD       | ns       |

| TJCC   | Transmitter Jitter<br>Cycle-to-cycle (Figure TBD)                               | f = 112 MHz                |             |            | TBD   | TBD       | ps       |

|        |                                                                                 | f = 65 MHz<br>f = 32.5 MHz |             |            | TBD   | TBD       | ps       |

| TPLLS  | Transmitter Phase Lock Loop Set (Figure                                         |                            |             |            | TBD   | TBD<br>10 | ps<br>ms |

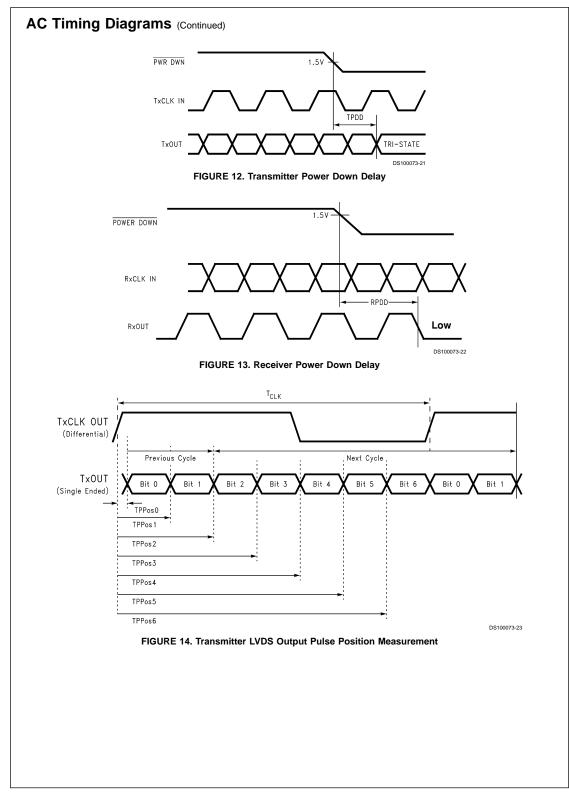

| TPDD   | Transmitter Powerdown Delay (Figure 12                                          |                            |             |            |       | 100       | ns       |

|        |                                                                                 |                            |             |            |       |           |          |

| Symbol | Parameter                                                                 |                                            | Min   | Тур   | Max   | Units |

|--------|---------------------------------------------------------------------------|--------------------------------------------|-------|-------|-------|-------|

| CLHT   | CMOS/TTL Low-to-High Transition Time                                      | (Figure 4)                                 |       |       | TBD   | ns    |

| CHLT   | CMOS/TTL High-to-Low Transition Time                                      | (Figure 4)                                 |       |       | TBD   | ns    |

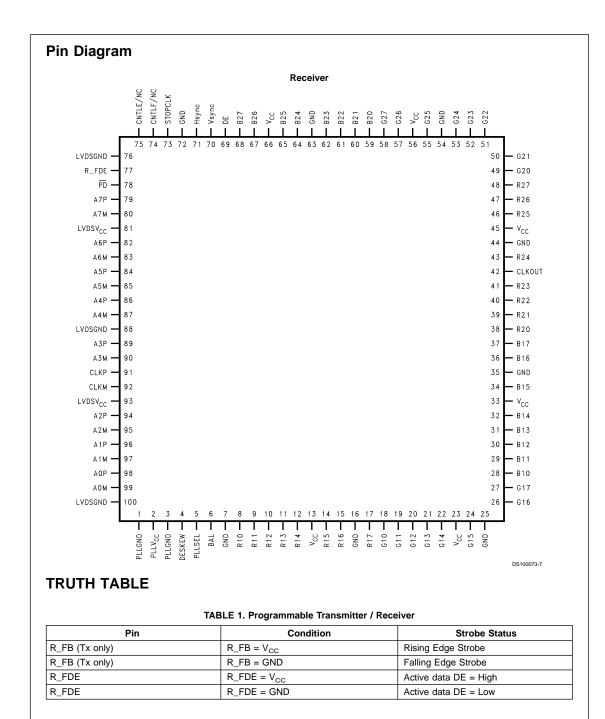

| RSPos0 | Receiver Input Strobe Position<br>for Bit 0 ( <i>Figure 15</i> ) (Note 4) | f = 112 MHz                                | 338   | 638   | 938   | ps    |

| RSPos1 | Receiver Input Strobe Position<br>for Bit 1                               |                                            | 1.613 | 1.913 | 2.213 | ns    |

| RSPos2 | Receiver Input Strobe Position<br>for Bit 2                               |                                            | 2.889 | 3.189 | 3.489 | ns    |

| RSPos3 | Receiver Input Strobe Position<br>for Bit 3                               |                                            | 4.164 | 4.464 | 4.764 | ns    |

| RSPos4 | Receiver Input Strobe Position<br>for Bit 4                               |                                            | 5.440 | 5.740 | 6.040 | ns    |

| RSPos5 | Receiver Input Strobe Position<br>for Bit 5                               |                                            | 6.715 | 7.015 | 7.315 | ns    |

| RSPos6 | Receiver Input Strobe Position<br>for Bit 6                               |                                            | 7.991 | 8.291 | 8.591 | ns    |

| RCOP   | RxCLK OUT Period (Figure 7)                                               |                                            | 8.928 | Т     | 30.77 | ns    |

| RCOH   | RxCLK OUT High Timef = 112 MHz( <i>Figure 7</i> )                         |                                            | TBD   |       |       | ns    |

| RCOL   | RxCLK OUT Low Time<br>( <i>Figure 7</i> )                                 | f = 112 MHz                                | TBD   |       |       | ns    |

| RSRC   | RxOUT Setup to RxCLK OUT<br>(Figure 7)                                    | f = 112 MHz                                | TBD   |       |       | ns    |

| RHRC   | RxOUT Hold to RxCLK OUT<br>( <i>Figure 7</i> )                            | f = 112 MHz                                | TBD   |       |       | ns    |

| RCCD   | RxCLK IN to RxCLK Out Delay @ 25°C,                                       | V <sub>CC</sub> = 3.3V ( <i>Figure 9</i> ) | TBD   |       | TBD   | ns    |

| RPLLS  | Receiver Phase Lock Loop Set (Figure 1                                    | 11)                                        |       |       | 10    | ms    |

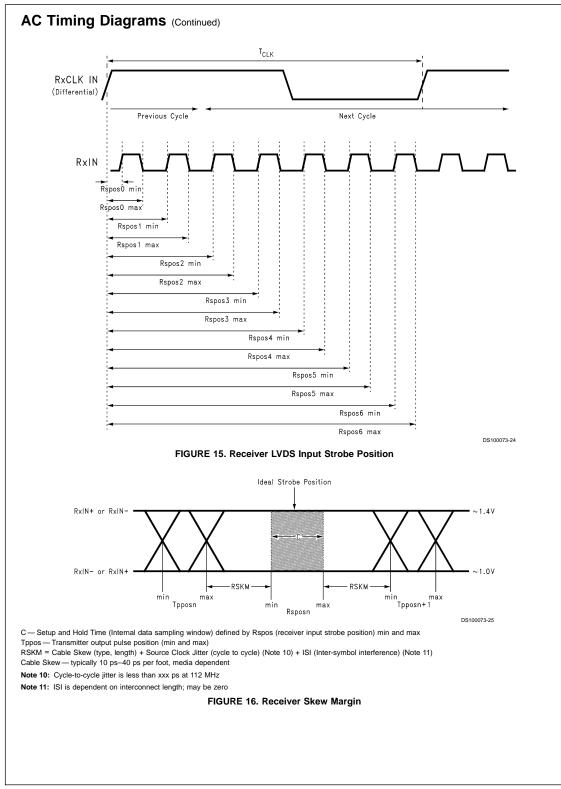

| RPDD   | Receiver Powerdown Delay (Figure 13)                                      |                                            |       |       | 1     | μs    |

| RSKM   | Receiver Skew Margin without<br>Deskew ( <i>Figure 16</i> ) (Note 5)      | f = 112 MHz                                | TBD   |       |       | ps    |

|        | Receiver Skew Margin with<br>Deskew ( <i>Figure 16</i> ) (Note 6)         |                                            | TBD   |       |       | ps    |

Note 5: Receiver Skew Margin is defined as the valid data sampling region at the receiver inputs. This margin takes into account transmitter output pulse positions (min and max) and the receiver input setup and hold time (internal data sampling window RSPOS). This margin allows for LVDS interconnect skew, intersymbol interference (both dependent on type/length of cable) and clock jitter.

$\mathsf{RSKM} \geq \mathsf{cable}$  skew (type, length) + source clock jitter (cycle to cycle).

Note 6: This limit is based on the capability of deskew circuitry. This margin allows for LVDS interconnect skew, intersymbol interference (both dependent on type/ length of cable) and clock jitter.

12

16

| Pin Name                           | I/O | No. | Description                                                                                                                                                                                                                                |  |  |  |

|------------------------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Rn, Gn, Bn,<br>DE, HSYNC,<br>VSYNC | I   | 51  | TTL level input. This includes: 16 Red, 16 Green, 16 Blue, and 3 control lines HSYNC, VSYNC, Data Enable.                                                                                                                                  |  |  |  |

| AnP                                | 0   | 8   | Positive LVDS differential data output.                                                                                                                                                                                                    |  |  |  |

| AnM                                | 0   | 8   | Negative LVDS differential data output.                                                                                                                                                                                                    |  |  |  |

| CLKIN                              | I   | 1   | TTL level clock input.                                                                                                                                                                                                                     |  |  |  |

| R_FB                               | I   | 1   | Programmable data strobe select. Rising data strobe edge selected when input is high. (Note 12).                                                                                                                                           |  |  |  |

| R_FDE                              | I   | 1   | Programmable control (DE) strobe select. Data active when DE = High when input is high. (Note 12).                                                                                                                                         |  |  |  |

| CLK1P                              | 0   | 1   | Positive LVDS differential clock output.                                                                                                                                                                                                   |  |  |  |

| CLK1M                              | 0   | 1   | Negative LVDS differential clock output.                                                                                                                                                                                                   |  |  |  |

| PWR DOWN                           | I   | 1   | TTL level input. Assertion (low input) tri-states the outputs, ensuring low current at power down. (Note 12).                                                                                                                              |  |  |  |

| PLLSEL                             | I   | 1   | PLL range select. External resistor network required (See Figure 17).<br>Auto-range active when input is high.                                                                                                                             |  |  |  |

| BAL                                | I   | 1   | Mode select for dc balanced (new) or non-dc balanced (backward compatible) interface. DC balance is active when input is high. (Note 12).                                                                                                  |  |  |  |

| PRE                                | I   | 1   | Pre-emphasis "on/off" select. Pre-emphasis is active when input is tied to $V_{\rm CC}$ through external pull-up resistor.                                                                                                                 |  |  |  |

| DUAL                               | 1   | 1   | Three-mode select for dual pixel, single pixel, or single pixel input to dual pixel output operation. Single pixel mode (only LVDS channels A0 thru A3 active) for power savings. Dual mode is active when input is high. <i>Figure 17</i> |  |  |  |

| V <sub>cc</sub>                    | I   | 4   | Power supply pins for TTL inputs.                                                                                                                                                                                                          |  |  |  |

| GND                                | I   | 5   | Ground pins for TTL inputs.                                                                                                                                                                                                                |  |  |  |

| PLL V <sub>CC</sub>                | I   | 2   | Power supply pin for PLL.                                                                                                                                                                                                                  |  |  |  |

| PLL GND                            | I   | 3   | Ground pins for PLL.                                                                                                                                                                                                                       |  |  |  |

| LVDS V <sub>CC</sub>               | I   | 2   | Power supply pin for LVDS outputs.                                                                                                                                                                                                         |  |  |  |

| LVDS GND                           | I   | 4   | Ground pins for LVDS outputs.                                                                                                                                                                                                              |  |  |  |

| CLK2P NC                           |     | 1   | Additional positive LVDS differential clock output. Identical to CLK1P. No<br>connect if not used.                                                                                                                                         |  |  |  |

| CLK2M NC                           |     | 1   | Additional negative LVDS differential clock output. Identical to CLK1PM. No<br>connect if not used.                                                                                                                                        |  |  |  |

Note 12: Inputs default to "low" when left open due to internal pull-down resistor.

| Pin Name                           | I/O | No. | Description                                                                                                                               |

|------------------------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| AnP                                | I   | 8   | Positive LVDS differential data inputs                                                                                                    |

| AnM                                | I   | 8   | Negative LVDS differential data inputs.                                                                                                   |

| Rn, Gn, Bn,<br>DE, HSYNC,<br>√SYNC | 0   | 51  | TTL level data outputs. This includes: 16 Red, 16 Green, 16 Blue, and 3 control lines — HSYNC, VSYNC, Data Enable.                        |

| RxCLK INP                          | I   | 1   | Positive LVDS differential clock input.                                                                                                   |

| RxCLK INM                          | I   | 1   | Negative LVDS differential clock input.                                                                                                   |

| RXCLK OUT                          | 0   | 1   | TTL level clock output. The falling edge acts as data strobe.                                                                             |

| R_FDE                              | I   | 1   | Programmable control (DE) strobe select.                                                                                                  |

| PLLSEL                             | I   | 1   | PLL range select. External resistor network required (See Figure 17).<br>Auto-range active when input is high.                            |

| BALANCED                           | I   | 1   | Mode select for dc balanced (new) or non-dc balanced (backward compatible) interface. DC balance is active when input is high. (Note 12). |

| DSSEL                              | I   | 1   | Deskew and oversampling "on/off" select. Deskew is active when input is<br>high.                                                          |

| PWR DOWN                           | I   | 1   | TTL level input. When asserted (low input) the receiver outputs are low.                                                                  |

| STOPCLK                            | 0   | 1   | Indicates receiver clock signal is not present.                                                                                           |

| V <sub>cc</sub>                    | I   | 6   | Power supply pins for TTL outputs.                                                                                                        |

| GND                                | I   | 8   | Ground pins for TTL outputs.                                                                                                              |

| PLL V <sub>CC</sub>                | I   | 1   | Power supply for PLL.                                                                                                                     |

| PLL GND                            | I   | 2   | Ground pin for PLL.                                                                                                                       |

| VDS V <sub>cc</sub>                | I   | 2   | Power supply pin for LVDS inputs.                                                                                                         |

| LVDS GND                           | I   | 3   | Ground pins for LVDS inputs.                                                                                                              |

| NC                                 |     | 2   | No Connect for compatibility with TI receiver.                                                                                            |

FIGURE 17. Resistor Network for Control Pin Inputs

#### **Applications Information**

The transmitter provides a second LVDS output clock. Both LVDS clocks will be identical. This feature supports backward compatibility with the previous generation of devices - the second clock allows the transmitter to interface to panels using a 'dual pixel' configuration of two receivers.

The 387/388 will also support the transmission of two additional customer defined control signals which are active during blanking while VSYNC is low. The additional control signals, referred to as CNTLE and CNTLF, should be multiplexed with data signals and provided to the transmitter inputs. Inputs B26 and B27 are designated for this purpose. When operating in 'non-balanced' mode, controls are transmitted on LVDS channels A4 and A5 during the blanking interval. Refer to Table (Control Signals Transmitted During Blanking) for details. These signals may be active only during blanking while VSYNC is low. Control signal levels are latched and held in the last valid state upon entering the data enabled phase. These control signals are available as TTL outputs of the receiver.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications