±25 mV

$\pm\,5V$

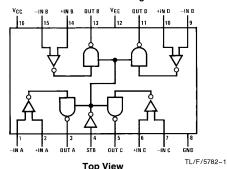

# DS1652/DS3650/DS3652 **Quad Differential Line Receivers**

#### **General Description**

The DS3650 and DS1652/DS3652 are TTL compatible quad high speed circuits intended primarily for line receiver applications. Switching speeds have been enhanced over conventional line receivers by the use of Schottky technology, and TRI-STATE® strobing is incorporated offering a high impedance output state for bussed organizations.

The DS3650 has active pull-up outputs and offers a TRI-STATE strobe, while the DS1652/DS3652 offers open collector outputs providing implied "AND" operation.

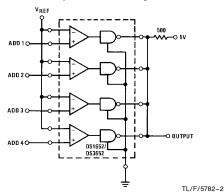

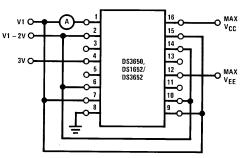

The DS1652/DS3652 can be used for address decoding as illustrated below. All outputs of the DS1652/DS3652 are tied together through a common resistor to 5V. In this con-

figuration, the DS1652/DS3652 provides the "AND" function. All addresses have to be true before the output will go high. This scheme eliminates the need for an "AND" gate and enhances speed throughput for address decoding.

#### **Features**

- High speed

- TTL compatible

- Input sensitivity

- TRI-STATE outputs for high speed busses

- Standard supply voltages

■ Pin and function compatible with MC3450 and MC3452

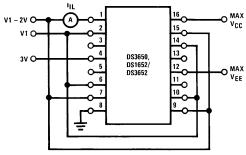

#### **Connection Diagram**

#### **Dual-In-Line Package**

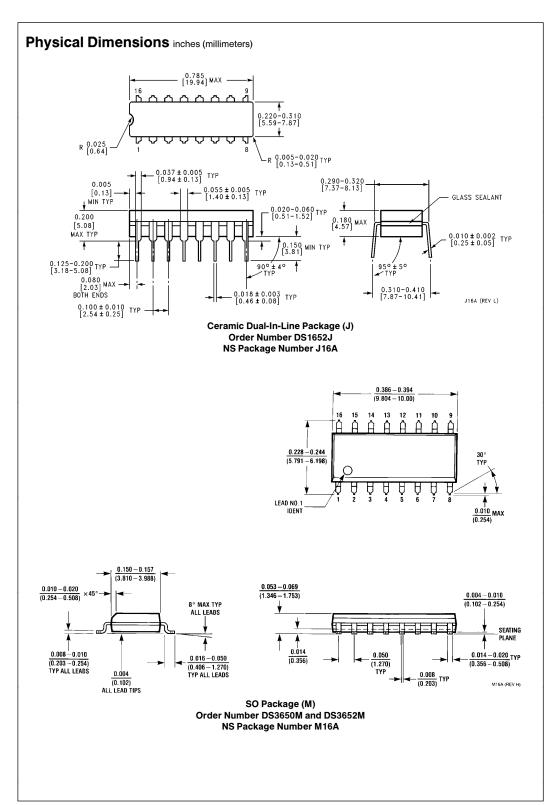

Order Number DS3650M, DS3652M or DS3650N See NS Package Number M16A or N16A For Complete Military 883 Specifications, see RETS Data Sheet.

Order Number DS1652J See NS Package Number J16A

#### **Truth Table**

|                                                      |        | Output |                   |  |  |

|------------------------------------------------------|--------|--------|-------------------|--|--|

| Input                                                | Strobe | DS3650 | DS1652/<br>DS3652 |  |  |

| $V_D \ge 25 \text{ mV}$                              | L      | Н      | Open              |  |  |

|                                                      | Н      | Open   | Open              |  |  |

| $-25 \text{ mV} \le V_{\text{ID}} \le 25 \text{ mV}$ | L      | Х      | Х                 |  |  |

|                                                      | Н      | Open   | Open              |  |  |

| $V_{ID} \leq -25 \text{ mV}$                         | L      | L      | L                 |  |  |

|                                                      | н      | Open   | Open              |  |  |

$\mathsf{L} = \mathsf{Low}\;\mathsf{Logic}\;\mathsf{State}\quad\mathsf{Open} = \mathsf{TRI}\text{-}\mathsf{STATE}$

H = High Logic State X = Indeterminate State TRI-STATE® is a registered trademark of National Semiconductor Corporation.

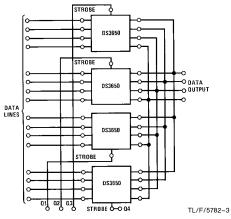

## **Typical Applications**

#### Implied "AND" Gating

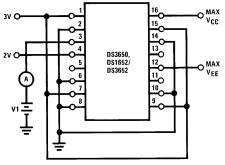

#### Wired "OR" Data Selecting Using TRI-STATE Logic

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Power Supply Voltages

| rower supply voltages                          |                                                 |

|------------------------------------------------|-------------------------------------------------|

| $V_{CC}$                                       | +7.0 V <sub>DC</sub>                            |

| $V_{EE}$                                       | $-7.0 V_{DC}$                                   |

| Differential-Mode Input Signal Voltage         |                                                 |

| Range, V <sub>IDR</sub>                        | $\pm6.0~V_{DC}$                                 |

| Common-Mode Input Voltage Range, VIC           | $\pm 5.0  V_{DC}$                               |

| Strobe Input Voltage, VI(S)                    | 5.5 V <sub>DC</sub>                             |

| Storage Temperature Range                      | $-65^{\circ}\text{C}$ to $+150^{\circ}\text{C}$ |

| Lead Temperature (Soldering, 4 seconds         | s) 260°C                                        |

| Maximum Power Dissipation* at 25°C             |                                                 |

| Cavity Package                                 | 1509 mW                                         |

| Molded DIP Package                             | 1476 mW                                         |

| SO Package                                     | 1051 mW                                         |

| *Derate cavity package 10.1 mW/°C above 25°C;  | derate molded DIP pack-                         |

| age 11.8 mW/°C above 25°C; derate SO package 8 | 3.41 mW/°C above 25°C.                          |

|                                                |                                                 |

| Operating Conditions                  |       |       |          |  |  |  |  |  |

|---------------------------------------|-------|-------|----------|--|--|--|--|--|

|                                       | Min   | Max   | Units    |  |  |  |  |  |

| Supply Voltage, V <sub>CC</sub>       |       |       |          |  |  |  |  |  |

| DS1652                                | 4.5   | 5.5   | $V_{DC}$ |  |  |  |  |  |

| DS3650, DS3652                        | 4.75  | 5.25  | $V_{DC}$ |  |  |  |  |  |

| Supply Voltage, V <sub>EE</sub>       |       |       |          |  |  |  |  |  |

| DS1652                                | -4.5  | -5.5  | $V_{DC}$ |  |  |  |  |  |

| DS3650, DS3652                        | -4.75 | -5.25 | $V_{DC}$ |  |  |  |  |  |

| Operating Temperature, T <sub>A</sub> |       |       |          |  |  |  |  |  |

| DS1652                                | -55   | +125  | °C       |  |  |  |  |  |

| DS3650, DS3652                        | 0     | +70   | °C       |  |  |  |  |  |

| Output Load Current, IOL              |       | 16    | mA       |  |  |  |  |  |

| Differential-Mode Input               |       |       |          |  |  |  |  |  |

| Voltage Range, V <sub>IDR</sub>       | -5.0  | +5.0  | $V_{DC}$ |  |  |  |  |  |

| Common-Mode Input                     |       |       |          |  |  |  |  |  |

| Voltage Range, V <sub>ICR</sub>       | -3.0  | +3.0  | $V_{DC}$ |  |  |  |  |  |

| Input Voltage Range                   |       |       |          |  |  |  |  |  |

| Input to GND, VIR                     | -5.0  | +3.0  | $V_{DC}$ |  |  |  |  |  |

### **Electrical Characteristics**

(V\_{CC} = 5.0 V\_{DC}, V\_{EE} = -5.0 V\_{DC}, Min  $\leq$   $T_{A} \leq$  Max, unless otherwise noted) (Notes 2 and 3)

| Symbol             | Parameter                                                                                 | Cond                                                                                                                               | Conditions                                   |     |  | Max   | Units |

|--------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----|--|-------|-------|

| V <sub>IS</sub>    | Input Sensitivity, (Note 5) (Common-Mode Voltage Range = $-3V \le V_{\text{IN}} \le 3V$ ) | $\begin{aligned} & \text{Min} \leq \text{V}_{CC} \leq \text{Max} \\ & \text{Min} \geq \text{V}_{EE} \geq \text{Max} \end{aligned}$ |                                              |     |  | ±25.0 | mV    |

| I <sub>IH(I)</sub> | High Level Input Current to Receiver Input                                                | (Figure 5)                                                                                                                         |                                              |     |  | 75    | μΑ    |

| I <sub>IL(I)</sub> | Low Level Input Current to<br>Receiver Input                                              | (Figure 6)                                                                                                                         |                                              |     |  | -10   | μΑ    |

| I <sub>IH(S)</sub> | High Level Input Current to<br>Strobe Input                                               | (Figure 3)                                                                                                                         | V <sub>IH(S)</sub> = 2.4V,<br>DS1652         |     |  | 100   | μΑ    |

|                    |                                                                                           |                                                                                                                                    | V <sub>IH(S)</sub> = 2.4V,<br>DS3650, DS3652 |     |  | 40    | μΑ    |

|                    |                                                                                           |                                                                                                                                    | $V_{IH(S)} = V_{CC}$                         |     |  | 1     | mA    |

| I <sub>IL(S)</sub> | Low Level Input Current to<br>Strobe Input                                                |                                                                                                                                    | $V_{IH(S)} = 0.4V$                           |     |  | -1.6  | mA    |

| V <sub>OH</sub>    | High Level Output Voltage                                                                 | (Figure 1)                                                                                                                         | DS3650                                       | 2.4 |  |       | V     |

| I <sub>CEX</sub>   | High Level Output Leakage Current                                                         | (Figure 1)                                                                                                                         | DS1652, DS3652                               |     |  | 250   | μΑ    |

| V <sub>OL</sub>    | Low Level Output Voltage                                                                  | (Figure 1)                                                                                                                         | DS3650, DS3652                               |     |  | 0.45  | v     |

|                    |                                                                                           |                                                                                                                                    | DS1652                                       |     |  | 0.50  | , v   |

| los                | Short-Circuit Output Current (Note 4)                                                     | (Figure 4)                                                                                                                         | DS3650                                       | -18 |  | -70   | mA    |

| loff               | Output Disable Leakage Current                                                            | (Figure 7)                                                                                                                         | DS3650                                       |     |  | 40    | μΑ    |

#### **Electrical Characteristics**

(V<sub>CC</sub> = 5.0 V<sub>DC</sub>, V<sub>EE</sub> = -5.0 V<sub>DC</sub>, Min  $\leq$  T<sub>A</sub>  $\leq$  Max, unless otherwise noted) (Notes 2 and 3) (Continued)

| Symbol | Parameter                                            | Conditions |  | Min | Тур | Max | Units |

|--------|------------------------------------------------------|------------|--|-----|-----|-----|-------|

| Іссн   | High Logic Level Supply Current from V <sub>CC</sub> | (Figure 2) |  |     | 45  | 60  | mA    |

| IEEH   | High Logic Level Supply Current from V <sub>EE</sub> | (Figure 2) |  |     | -17 | -30 | mA    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified, min/max limits apply across the 0°C to +70°C range for the DS3650, DS3652 and the -55°C to +125°C range for the DS1652. All typical values are for T<sub>A</sub> = 25°C, V<sub>CC</sub> = 5V and V<sub>EE</sub> = -5V.

Note 3: All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted. All values shown as max or min on absolute value basis.

Note 4: Only one output at a time should be shorted.

Note 5: A parameter which is of primary concern when designing with line receivers is, what is the minimum differential input voltage required as the receiver input terminals to guarantee a given output logic state. This parameter is commonly referred to as threshold voltage. It is well known that design considerations of threshold voltage are plagued by input offset currents, bias currents, network source resistances, and voltage gain. As a design convenience, the DS1652 and the DS3650, DS3652 are specified to a parameter called input sensitivity (V<sub>IS</sub>). This parameter takes into consideration input offset currents and bias currents and guarantees a minimum input differential voltage to cause a given output logic state with respect to a maximum source impedance of 2000 at each input.

### **Switching Characteristics** ( $V_{CC} = 5 V_{DC}$ , $V_{EE} = -5 V_{DC}$ , $T_A = 25 ^{\circ}C$ unless otherwise noted)

| Symbol              | Parameter                                                     | Co          | Conditions    |  | Тур | Max | Units |

|---------------------|---------------------------------------------------------------|-------------|---------------|--|-----|-----|-------|

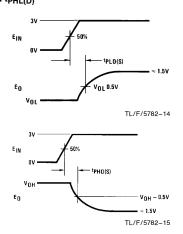

| t <sub>PHL(D)</sub> | High-to-Low Logic Level Propagation                           |             | DS3650        |  | 21  | 25  | ns    |

|                     | Delay Time (Differential Inputs)                              | (Figure 8)  | DS1652/DS3652 |  | 20  | 25  | ns    |

| t <sub>PLH(D)</sub> | Low-to-High Logic Level Propagation                           | (riguro o)  | DS3650        |  | 20  | 25  | ns    |

|                     | Delay Time (Differential Inputs)                              |             | DS1652/DS3652 |  | 22  | 25  | ns    |

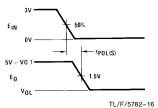

| t <sub>POH(S)</sub> | TRI-STATE to High Logic Level Propagation Delay Time (Strobe) |             | DS3650        |  | 16  | 21  | ns    |

| t <sub>PHO(S)</sub> | High Logic Level to TRI-STATE Propagation Delay Time (Strobe) | (Figure 9)  | DS3650        |  | 7   | 18  | ns    |

| t <sub>POL(S)</sub> | TRI-STATE to Low Logic Level Propagation Delay Time (Strobe)  | (Figure 9)  | DS3650        |  | 19  | 27  | ns    |

| t <sub>PLO(S)</sub> | Low Logic Level to TRI-STATE Propagation Delay Time (Strobe)  |             | DS3650        |  | 14  | 29  | ns    |

| t <sub>PHL(S)</sub> | High-to-Low Logic Level Propagation Delay Time (Strobe)       | (Figure 10) | DS1652/DS3652 |  | 16  | 25  | ns    |

| t <sub>PLH(S)</sub> | Low-to-High Logic Level Propagation<br>Delay Time (Strobe)    | ( iguic 10) | DS1652/DS3652 |  | 13  | 25  | ns    |

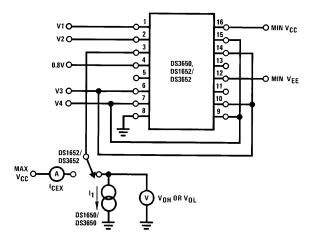

### **Electrical Characteristic Test Circuits**

TL/F/5782-4

|                  | V                                                                                                                                  | 1                 | V                | 2                 | ,            | /3                | V4           |                   |                    |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-------------------|--------------|-------------------|--------------|-------------------|--------------------|--|

|                  | DS3650                                                                                                                             | DS1652/<br>DS3652 | DS3650           | DS1652/<br>DS3652 | DS3650       | DS1652/<br>DS3652 | DS3650       | DS1652/<br>DS3652 | l <sub>1</sub>     |  |

| V <sub>OH</sub>  | +2.975V<br>-3.0V                                                                                                                   |                   | +3.0V<br>-2.975V |                   | +3.0V<br>GND |                   | GND<br>-3.0V |                   | −0.4 mA<br>−0.4 mA |  |

| I <sub>CEX</sub> |                                                                                                                                    | +2.975V<br>-3.0V  |                  | +3.0V<br>-2.975V  |              | +3.0V<br>GND      |              | GND<br>-3.0V      |                    |  |

| V <sub>OL</sub>  | +3.0V<br>-2.975V                                                                                                                   | +3.0V<br>-2.975V  | +2.975V<br>-3.0V | +2.975V<br>-3.0V  | GND<br>-3.0V | GND<br>-3.0V      | +3.0V<br>GND | +3.0V<br>GND      | + 16 mA<br>+ 16 mA |  |

| Channe           | Channel A shown under test. Other channels are tested similarly.  FIGURE 1. I <sub>CEX</sub> , V <sub>OH</sub> and V <sub>OL</sub> |                   |                  |                   |              |                   |              |                   |                    |  |

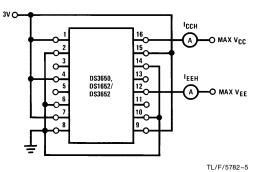

FIGURE 2.  $I_{\mbox{\footnotesize CCH}}$  and  $I_{\mbox{\footnotesize EEH}}$

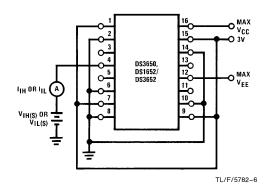

FIGURE 3.  $I_{\mbox{\scriptsize IH(S)}}$  and  $I_{\mbox{\scriptsize IL(S)}}$

### **Electrical Characteristic Test Circuits (Continued)**

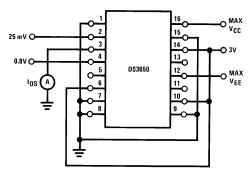

TL/F/5782-7

**Note:** Channel A shown under test, other channels are tested similiarly. Only one output shorted at a time.

FIGURE 4. I<sub>OS</sub>

TL/F/5782-9

Note: Channel A(-) shown under test, other channels are tested similarly. Devices are tested with V1 from 3V to  $-3\mathrm{V}.$

FIGURE 6. I<sub>IL</sub>

TL/F/5782-8

Note: Channel A(-) shown under test, other channels are tested similarly. Devices are tested with V1 from 3V to -3V.

FIGURE 5. I<sub>IH</sub>

TL/F/5782-10

Note: Output of Channel A shown under test, other outputs are tested similarly for V1  $\,=\,$  0.4V and 2.4V.

FIGURE 7. I<sub>OFF</sub>

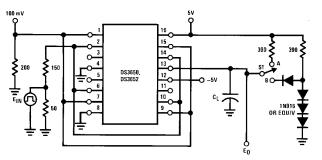

## **AC Test Circuits and Switching Time Waveforms**

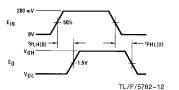

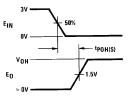

Note: E<sub>IN</sub> waveform characteristics: : EIN waveform characteristics:  $t_{LH}$  and  $t_{THL} \le 10$  ns measured 10% to 90% PRR = 1 MHz Duty Cycle = 50%

TL/F/5782-11

Note: Output of Channel B shown under test, other channels are tested similarly.

S1 at "A" for DS1652/DS3652 S1 at "B" for DS1650/DS3650  $C_L=15\ pF$  total for DS1652/DS3652

$C_L = 50 \text{ pF total for DS1650/DS3650}$

FIGURE 8. Receiver Propagation Dealy t<sub>PLH(D)</sub> and t<sub>PHL(D)</sub>

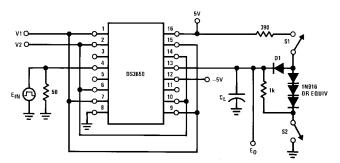

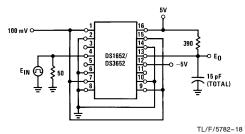

TL/F/5782-13

Note: Output of Channel B shown under test, other channels are tested similiarly.

|                     | V1     | V2     | S1     | S2     | CL    |

|---------------------|--------|--------|--------|--------|-------|

| t <sub>PLO(S)</sub> | 100 mV | GND    | Closed | Closed | 15 pF |

| t <sub>POL(S)</sub> | 100 mV | GND    | Closed | Open   | 50 pF |

| t <sub>PHO(S)</sub> | GND    | 100 mV | Closed | Closed | 15 pF |

| t <sub>POH(S)</sub> | GND    | 100 mV | Open   | Closed | 50 pF |

$\mathbf{C}_{\mathsf{L}}$  includes jig and probe capacitance.

$E_{IN}$  waveform characteristics:  $t_{TLH}$  and  $t_{THL} \leq$  10 ns measured 10% to 90%

PRR = 1 MHz

Duty Cycle = 50%

TL/F/5782-17

FIGURE 9. Strobe Propagation Delay  $t_{PLO(S)}, t_{POL(S)}, t_{PHO(S)}$  and  $t_{POH(S)}$

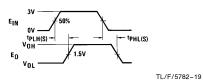

# AC Test Circuits and Switching Time Waveforms (Continued)

Note:  $E_{IN}$  waveform characteristics:  $t_{TLH}$  and  $t_{THL} \le 10$  ns measured 10% and 90% PRR = 1 MHz Duty Cycle = 500 ns

**Note:** Output of Channel B shown under test, other channels are tested similarly.

FIGURE 10. Strobe Propagation Delay  $t_{\mbox{\scriptsize PLH}(\mbox{\scriptsize S})}$  and  $t_{\mbox{\scriptsize PHL}(\mbox{\scriptsize S})}$

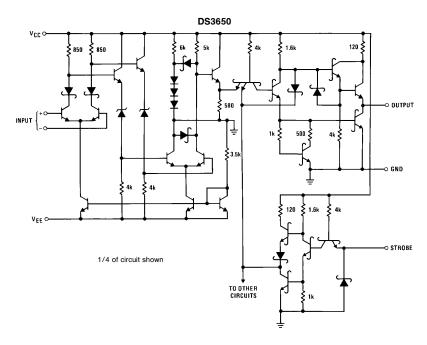

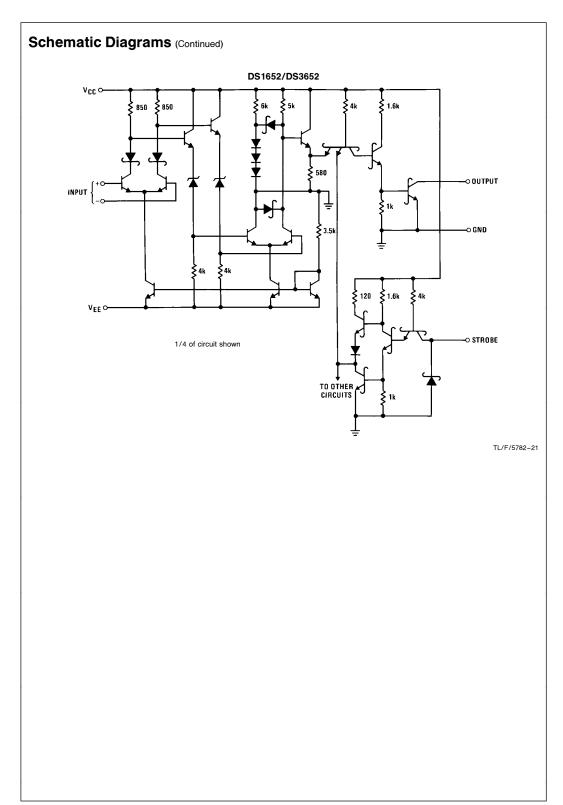

# **Schematic Diagrams**

TL/F/5782-20

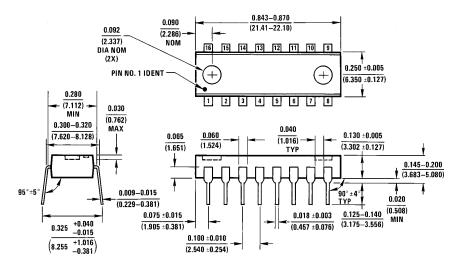

### Physical Dimensions inches (millimeters) (Continued)

Molded Dual-In-Line Package (N) Order Number DS3650N NS Package Number N16A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

N16A (REV E)

**National Semiconductor** National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

http://www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Fax: +49 (0) 180-530 so so Email: europe.support@nsc.com Deutsch Tel: +49 (0) 180-530 85 85 English Tel: +49 (0) 180-532 78 32 Français Tel: +49 (0) 180-532 95 58 Italiano Tel: +49 (0) 180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon

Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2308

Fax: 81-043-299-2408