# Comlinear CLC522 Wideband Variable-Gain Amplifier

### **General Description**

The CLC522 variable gain amplifier (VGA) is a dc-coupled, twoquadrant multiplier with differential voltage inputs and a singleended voltage output. Two input buffers and an output operational amplifer are integrated with the multiplier core to make the CLC522 a complete VGA system that does not require external buffering.

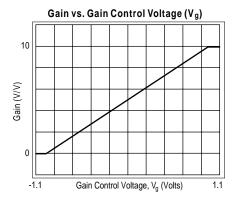

The CLC522 provides the flexibility of externally setting the maximum gain with only two external resistors. Greater than 40dB gain control is easily achieved through a single high impedance voltage input. The CLC522 provides a linear (in Volts per Volt) relationship between the amplifier's gain and the gain-control input voltage.

The CLC522's maximum gain may be set anywhere over a nominal range of 2V/V to 100V/V. The gain control input then provides attenuation from the maximum setting. For example, set for a maximum gain of 100V/V, the CLC522 will provide a 100V/V to 1V/V gain control range by sweeping the gain control input voltage from +1 to -0.98V.

Set at a maximum gain of 10V/V, the CLC522 provides a 165MHz signal channel bandwidth and a 165MHz gain control bandwidth. Gain nonlinearity over a 40dB gain range is 0.5% and gain accuracy at  $A_{Vmax} = 10V/V$  is typically ±0.3%.

### Features

- 330MHz signal bandwidth: A<sub>vmax</sub> = 2

- 165MHz gain-control bandwidth

- 0.3° to 60MHz linear phase deviation

- 0.04% (-68dB) signal-channel non-linearity

- >40dB gain-adjustment range

- Differential or single-end voltage inputs

- Single-ended voltage output

### Applications

- Variable attenuators

- Pulse amplitude equalizers

- HF modulators

- Automatic gain control & leveling loops

- Video production switching

- Differential line receivers

- Voltage controlled filters

| PARAMETERS                          | CONDITIONS                              | TYP   | MIN      | I/MAX RATIN | IGS        | UNITS                       | NOTE |

|-------------------------------------|-----------------------------------------|-------|----------|-------------|------------|-----------------------------|------|

| AmbientTemperature                  | AJE,AJP                                 | +25   | +25      | 0 to +70    | -40 to +85 | °C                          | 1    |

| REQUENCY DOMAIN RESPON              | SE                                      |       |          |             |            |                             |      |

| -3dB bandwidth                      | $V_{out} < 0.5 V_{pp}$                  | 165   | 120      | 115         | 110        | MHz                         | 3    |

|                                     | $V_{out} < 5.0 V_{pp}$                  | 150   | 100      | 95          | 90         | MHz                         |      |

| gain control bandwidth              | $V_{out} < 0.5 V_{pp}$                  | 165   | 120      | 115         | 110        | MHz                         | 4    |

| gain flatness                       | $V_{out} < 0.5 V_{pp}$                  |       |          |             |            |                             |      |

| peaking                             | DC to 30MHz                             | 0     | 0.1      | 0.1         | 0.1        | dB                          | 3    |

| rolloff                             | DC to 30MHz                             | 0.05  | 0.25     | 0.25        | 0.4        | dB                          | 3    |

|                                     |                                         |       |          |             | -          |                             | 3    |

| linear phase deviation              | DC to 60MHz<br>30MHz                    | 0.3   | 1.0      | 1.1<br>- 57 | 1.2        |                             | 25   |

| feedthrough                         | 30IVIEZ                                 | - 62  | - 57     | - 57        | -57        | dB                          | 3,5  |

| TIME DOMAIN RESPONSE                |                                         |       |          |             |            |                             |      |

| rise and fall time                  | 0.5V step                               | 2.2   | 2.9      | 3.0         | 3.2        | ns                          |      |

|                                     | 5.0V step                               | 3.0   | 5.0      | 5.0         | 5.0        | ns                          |      |

| settling time                       | 2.0V step to 0.1%                       | 12    | 18       | 18          | 18         | ns                          |      |

| overshoot                           | 0.5V step                               | 2     | 15       | 15          | 15         | %                           |      |

| slew rate                           | 4.0V step                               | 2000  | 1400     | 1400        | 1400       | V/µs                        |      |

| DISTORTION AND NOISE RESPO          | ONSE                                    |       |          |             |            |                             |      |

| 2 <sup>nd</sup> harmonic distortion | 2V <sub>pp</sub> , 20MHz                | - 50  | - 44     | - 44        | -44        | dBc                         | 3    |

| 3 <sup>rd</sup> harmonic distortion | 2V <sub>pp</sub> , 20MHz                | - 65  | - 58     | - 56        | -54        | dBc                         | 3    |

| equivalent input noise              | 1 to 200MHz                             | 5.8   | 6.2      | 6.5         | 6.8        | nV/√Hz                      | Ŭ    |

| noise floor                         | 1 to 200MHz                             | - 152 | - 150    | - 149       | - 149      | dBm <sub>1Hz</sub>          |      |

|                                     |                                         | - 102 | - 150    | - 143       | - 143      |                             |      |

|                                     | V · · · · · · · · · · · · · · · · · · · |       | 0.1      | 0.1         | 0.1        | %                           |      |

| signal channel nonlinearity (SGNL)  |                                         | 0.04  | 0.1      | 0.1         | 0.1        |                             | 2    |

| gain control nonlinearity (GCNL)    | full range                              | 0.5   | 2.0      | 2.2         | 3.0        | %                           | 2    |

| gain error (GACCU)                  | A <sub>Vmax</sub> =+10                  | ± 0.0 | ± 0.5    | ± 0.5       | ± 1.0      | dB                          | 2    |

| V <sub>g</sub> high                 |                                         | + 990 | + 990±60 | + 990±60    | + 990±60   | mV                          |      |

| low                                 |                                         | - 975 | - 975±80 | - 975±80    | - 975±80   | mV                          |      |

| STATIC DC PERFORMANCE               |                                         |       |          |             |            |                             |      |

| V <sub>in</sub> voltage range       | common mode                             | ± 2.2 | ± 1.2    | ± 1.2       | ± 1.4      | V                           |      |

| bias current                        |                                         | 9     | 21       | 26          | 45         | μA                          | 2    |

| average drift                       |                                         | 65    |          | 175         | 275        | ∏nA/°C                      |      |

| offset current                      |                                         | 0.2   | 2.0      | 3.0         | 4.0        | μA                          |      |

| average drift                       |                                         | 5     |          | 30          | 40         | ∏ nA/°C                     |      |

| resistance                          |                                         | 1500  | 650      | 450         | 175        | kΩ                          |      |

| capacitance                         |                                         | 1.0   | 2.0      | 2.0         | 2.0        | pF                          |      |

|                                     |                                         |       |          | 47          |            | H ·                         |      |

| V <sub>g</sub> bias current         |                                         | 15    | 38       |             | 82         | l∣μA<br>I∣nA/°C             |      |

| average drift                       |                                         | 125   |          | 300         | 600        |                             |      |

| resistance                          |                                         | 100   | 38       | 30          | 15         | kΩ                          |      |

| capacitance                         |                                         | 1.0   | 2.0      | 2.0         | 2.0        | pF                          |      |

| output voltage range                | R <sub>L</sub> = ∞                      | ± 4.0 | ± 3.7    | ± 3.6       | ± 3.5      | v                           |      |

| current                             |                                         | ± 70  | ± 47     | ± 40        | ± 25       | mA                          |      |

| offset voltage                      | A <sub>Vmax</sub> =+10                  | 25    | 85       | 95          | 120        | mV                          | 2    |

| average drift                       |                                         | 100   |          | 350         | 400        | μV/°C                       |      |

| resistance                          |                                         | 0.1   | 0.2      | 0.3         | 0.6        | $  _{\Omega}^{\mu,\mu,\nu}$ |      |

|                                     |                                         | 1.8   | 1.37     |             |            |                             |      |

| IRgmax                              | output roferrad                         |       |          | 1.26        | 1.15       | mA                          |      |

| power supply sensitivity            | output referred                         | 10    | 40       | 40          | 40         | mV/V                        | 3    |

| common-mode rejection ratio         | input referred                          | 70    | 59       | 59          | 59         | dB                          | _    |

| supply current                      | R <sub>L</sub> = ∞                      | 46    | 61       | 62          | 63         | mA                          | 2    |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

## Absolute Maximum Ratings

| supply voltage                      | ±7V              |

|-------------------------------------|------------------|

| short circuit current               | 96mA             |

| common-mode input voltage           | ±V <sub>cc</sub> |

| maximum junction temperature        | +200°C           |

| storagetemperature                  | -65°C to+150°C   |

| lead temperature (soldering 10 sec) | +300°C           |

|                                     |                  |

### Notes

1) AJE (SOIC) is tested/guaranteed with  $R_f=866\Omega$  and  $R_g=165\Omega$ .

2) J-level, spec is 100% tested at +25°C, sample tested at +85°C.

- L-level, spec is 100% wafer probed at 25°C. 3) J-level, spec is sample tested at 25°C.

4) Tested with  $V_{in}$  = 0.2V and  $V_g$  < 0.5V\_{pp}. 5) Feedtrough is tested at maximum attenuation (i.e  $V_g = -1.1V$ )

### **Ordering Information**

| Model                       | Temperature Range | Description                |  |  |  |

|-----------------------------|-------------------|----------------------------|--|--|--|

| CLC522AJP                   | -40°C to +85°C    | 14-pin PDIP                |  |  |  |

| CLC522AJE                   | -40°C to +85°C    | 14-pin SOIC                |  |  |  |

| CLC522ALC                   | -40°C to +85°C    | dice                       |  |  |  |

| CLC522A8D                   | -55°C to +125°C   | 14-pin CerDIP, MIL-STD-883 |  |  |  |

| CLC522AMC                   | -55°C to +125°C   | dice, MIL-STD-883          |  |  |  |

| CLC522A8L-2                 | -55°C to +125°C   | 20pin LCC, MIL-STD-883     |  |  |  |

| DESC SMD number: 5962-93259 |                   |                            |  |  |  |

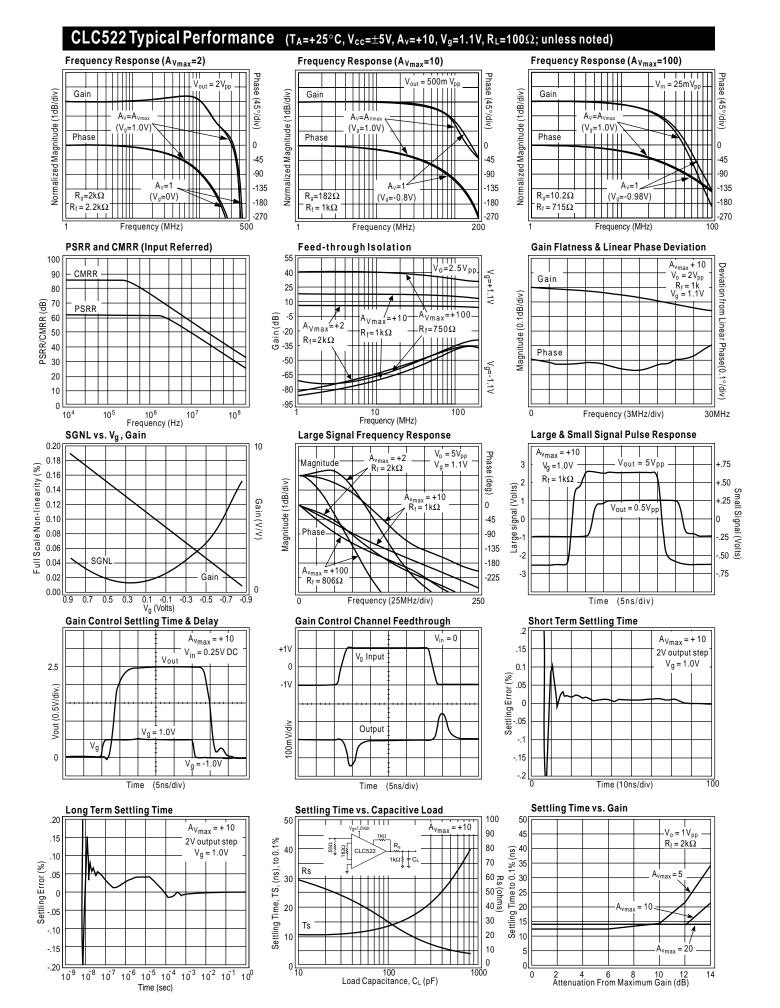

#### CLC522 Typical Performance ( $T_{A}$ =+25°C, $V_{cc}$ =±5V, $A_{v}$ =+10, $V_{g}$ =1.1V, $R_{L}$ =100 $\Omega$ ; unless noted) **Differential Gain and Phase** Input Referred Voltage Noise vs Avmax **Differential Gain and Phase** 100 .25 .10 10 25 4.43 MHz 4.43 MHz $A_{vmax} = +10$ Gain Positive Sync Phase, $V_g = 0.0V$ $V_{g} = 1.0V$ .20 DifferentialPhase (n .15 10 DifferentialPhase Negative Sync .20 .08 $A_{vmax} = +2$ Voltage Noise (nV/√Hz) (%) Differential Gain (%) ... 01 5: 90'ain 90'ain Phase Negative Sync Phase Phase, Vg = 1.0V Differential ( Positive Sync Gain, $V_g = 1.0V$ e (degrees) 02 (degrees) Gain Positive Sync .05 .02 Gain, Vg èoov 0 0 0 30 40 10 20 50 60 70 80 90 0 100 Number of 150Ω Loads Number of 150 Loads Maximum Gain Setting, AVmax (V/V) 2nd Harmonic Distortion vs. Pout 3rd Harmonic Distortion vs. Pout -1dB Compression at Maximum Gain 20 -35 -35 Output R 50MHz 19 -40 -40 Limited 1kΩ 50Ω Po 182Ω 522 $R_f = 1.4 k\Omega$ 18 -45 -45 50Ω (dBm) 50MHz 20Ω Distortion Level (dBc) Distortion Level (dBc) 17 -50 -50 50Ω 20MHz -1dB Compression 12 12 13 13 -55 -55 20MHz Input -60 -60 Limited 10MHz -65 омн $R_{f} = 9000$ -65 5MHz Vg 1.1V Rf -70 -70 50Ω 50Ω 50Ω 182Ω 1kΩ 50Ω P₀ 522 12 -75 -75 522 50Ω ≸ 50Ω ≹ 5MHz 20Ω 20Ω -80 -80 11 50Ω -85 -85 10 10 -2 10 6 8 Frequency (MHz) 100 -4 0 2 6 8 -4 2 4 0 Output Power (Pout, dBm) Output Power (Pout, dBm) Application Discussion

#### Theory of Operation

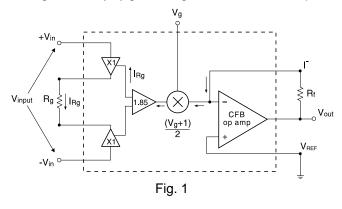

The CLC522 is a linear wideband variable-gain amplifier as illustrated in Fig 1. A voltage input signal may be applied differentially between the two inputs  $(+V_{in}, -V_{in})$ , or single-endedly by grounding one of the unused inputs.

The CLC522 input buffers convert the input voltage to a current ( $I_{Rg}$ ) that is a function of the differential input voltage ( $V_{input} =+V_{in} - -V_{in}$ ) and the value of the gainsetting resistor ( $R_g$ ). This current ( $I_{Rg}$ ) is then mirrored to a gain stage with a current gain of 1.85. The voltage-controlled two-quadrant multiplier attenuates this current which is then converted to a voltage via the output amplifier. This output amplifier is a current-feedback op amp configured as a transimpedance amplifier. It's transimpedance gain is the feedback resistor ( $R_f$ ). The input signal, output, and gain control are all voltages. The output voltage can easily be calculated as seen in Eq. 1.

$$V_{out} = I_{R_g} * 1.85 * \left(\frac{V_g + 1}{2}\right) * R_f$$

Eq. 1

/. .

ince

$$I_{R_g} = \frac{V_{input}}{R_g}$$

s

$$A_{v} = 1.85* \frac{R_{f}}{R_{g}} * \left(\frac{V_{g} + 1}{2}\right)$$

Eq. 2

The gain of the CLC522 is therefore a function of three external variables;  $R_g$ ,  $R_f$  and  $V_g$  as expressed in Eq. 2. The gain-control voltage ( $V_g$ ) has a ideal input range of  $-1V \le V_g \le +1V$ . At  $V_g = +1V$ , the gain of the CLC522 is at its maximum as expressed in Eq. 3.

$$A_{V_{max}} = 1.85 \frac{R_{f}}{R_{g}}$$

Eq. 3

Notice also that Eq. 3 holds for both differential and single-ended operation.

#### Choosing R<sub>f</sub> and R<sub>g</sub>

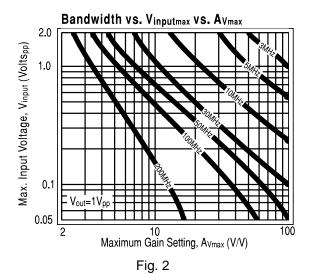

$R_g$  is calculated from Eq.4.  $V_{input_{max}}$  is the maximum peak

$$R_{g} = \frac{V_{input_{max}}}{I_{R_{g_{max}}}}$$

Eq. 4

input voltage (V<sub>pk</sub>) determined by the application.  $I_{Rg_{max}}$  is the maximum allowable current through  $R_g$  and is typically 1.8mA. Once  $A_{V_{max}}$  is determined from the minimum input and desired output voltages,  $R_f$  is then determined using Eq. 5. These values of  $R_f$  and  $R_g$  are

$$R_{f} = \frac{1}{1.85} * R_{g} * A_{V_{max}}$$

Eq. 5

the minimum possible values that meet the input voltage and maximum gain constraints. Scaling the resistor values will decrease bandwidth and improve stability.

http://www.national.com

Fig. 2 illustrates the resulting CLC522 bandwidths as a function of the maximum and minimum input voltages when  $V_{out}$  is held constant at  $1V_{pp}$ .

#### **Adjusting Offsets**

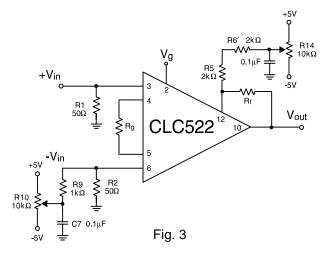

Treating the offsets introduced by the input and output stages of the CLC522 is easily accomplished with a two step process. The offset voltage of the output stage is treated by first applying -1.1 Volts on V<sub>a</sub>, which effectively

isolates the input stage and multiplier core from the output stage. As illustrated in Fig. 3, the trim pot located at R14 on the CLC522 Evaluation Board should then be adjusted in order to null the offset voltage seen at the CLC522's output (pin 10). Once this is accomplished, the offset errors introduced by the input stage and multiplier core can then be treated. The second step requires the absence of an input signal and matched source impedances on the two input pins in order to cancel the bias current errors. This done then +1.1Volts should be applied to V<sub>q</sub> and the trim pot located at R10 adjusted in order to null the offset voltage seen at the CLC522's output. If a more limited gain range is anticipated, the above adjustments should be made at these operating points.

#### Gain Errors

The CLC522's gain equation as theoretically expressed in Eq. 2 must include the device's error terms in order to yield the actual gain equation. Each of the gain error terms are specified in the Electrical Characteristics table and are defined below and illustrated in Fig. 4.

Combining these error terms with Eq. 2 gives the "gain envelope" equation and is expressed in Eq. 7. From the Electrical Characteristics table, the nominal endpoint values of V<sub>g</sub> are:  $V_{g_{high}}$  =+990mV and  $V_{g_{low}}$  = -975mV.

$$A_{V} = A_{Vmax} \begin{pmatrix} \frac{10^{\frac{\pm GACCU}{20}} \left(V_{g} - V_{g_{low}} \pm \Delta V_{g_{low}}\right)}{\left(V_{g_{high}} \pm \Delta V_{g_{high}} - V_{g_{low}} \pm \Delta V_{g_{low}}\right)} \pm \left(1 - V_{g}^{2}\right) GCNL \\ Eq. 7 \end{pmatrix}$$

#### Signal-Channel Nonlinearity

Signal-channel nonlinearity, SGNL, also known as integral endpoint linearity, measures the non-linearity of an amplifier's voltage transfer function. The CLC522's SGNL, as it is specified in the Electrical Characteristics table, is measured while the gain is set at its maximum (i.e.  $V_{g}$ =+1.1V). The Typical Performance Characteristics plot labled "SGNL & Gain vs Vg" illustrates the CLC522's SGNL as Vg is swept through its full range. As can be seen in this plot, when the gain as reduced from  $A_{V_{max}}$ , SGNL improves to < 0.02%(-74dB) at V<sub>a</sub>=0 and then degrades somewhat at the lowest gains.

#### Noise

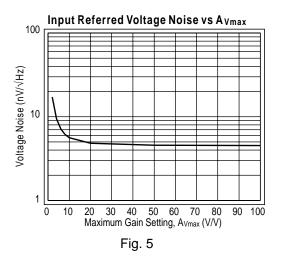

Fig. 5 describes the CLC522's input-refered spot noise density as a function of  $A_{Vmax}$ . The plot includes all the noise contributing terms. At  $A_{Vmax} = 10V/V$ , the CLC522 has a typical input-referred spot noise density (eni) of 5.8nV/ $\sqrt{Hz}$ . The input RMS voltage noise can be determined from the following single-pole model:

$$V_{RMS} = e_{in} * \sqrt{1.57*(-3dB bandwidth)}$$

Eq. 8

Further discussion and plots of noise and the noise model is provided in Application Note OA-23. Comlinear also provides SPICE models that model internal noise and other parameters for a typical part.

#### **Circuit Layout Considerations**

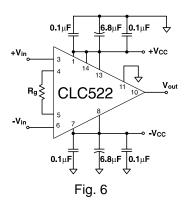

Please refer to the CLC522 Evaluation Board Literature for precise layout guidelines. Good high-frequency operation requires all of the de-coupling capcitors shown in Fig. 6 to be placed as close as possible to the power

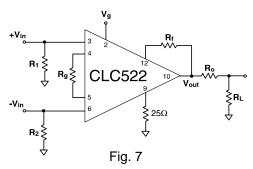

supply pins in order to insure a proper high-frequency low-impedance bypass. Adequate ground plane and lowinductive power returns are also required of the layout. Minimizing the parasitic capacitances atpins 3, 4, 5, 6, 9,

10 and 12 as shown in Fig. 7 will assure best high frequency performance. Vref (pin 9) to ground should include a small resistor value of 25 ohms or greater to buffer the internal voltage follower. The parasitic inductance of component leads or traces to pins 4, 5 and 9 should also be kept to a minimum. Parasitic or load capacitance,  $C_L$ , on the output (pin 10) degrades phase margin and can lead to frequency response peaking or circuit oscillation. This should be treated with a small series resistor between output (pin 10) and  $C_L$  (see the plot "Settling Time vs. Capacitive Load" for a recommended series resistance).

Component parasitics also influence high frequency results, therefore it is recommended to use metal film resistors such as RN55D or leadless components such as surface mount devices. High profile sockets are not recommended. If socketing is necessary, it is recommended to use low impedance flush mount connector jacks such as Cambion (P/N 450-2598).

#### **Application Circuits**

#### **Four-Quadrant Multiplier**

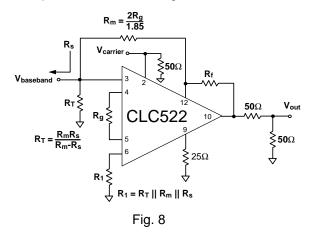

Applications requiring multiplication, squaring or other non-linear functions can be implemented with four-quadrant multipliers. The CLC522 implements a four-quadrant multiplier as illustrated in figure 8.

#### Frequency Shaping

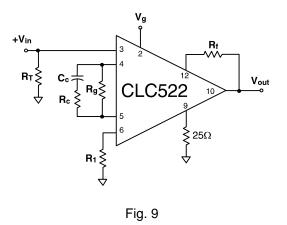

Frequency shaping and bandwidth extension of the CLC522 can be accomplished using parallel networks connected across the  $R_g$  ports. The network shown in the Fig. 9 schematic will effectively extend the CLC522's bandwidth.

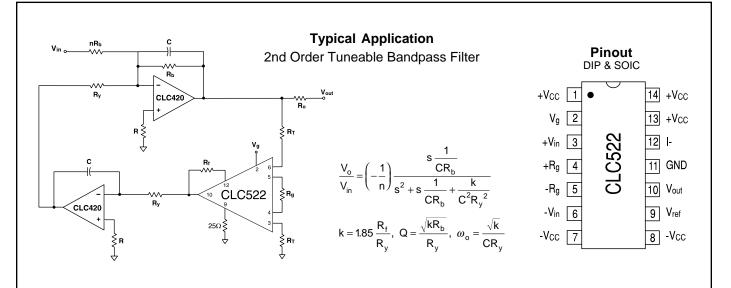

#### 2nd Order Tuneable Bandpass Filter

The CLC522 Variable-Gain Amplifier placed into feedback loops provide signal processing functions such as 2nd order tuneable bandpass filters. The center frequency of the 2nd order bandpass illustrated on the front page is adjusted through the use of the CLC522's gaincontrol voltage,  $V_g$ . The integrators implemented with two CLC420s, provide the coefficients for the transfer function. This page intentionally left blank.

### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block Ocean Centre, 5 Canton Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.