# ADC12041 12-Bit Plus Sign 216 kHz Sampling **Analog-to-Digital Converter**

## **General Description**

Operating from a single 5V power supply the ADC12041 is a 12 bit + sign, parallel I/O, self-calibrating, sampling analogto-digital converter (ADC). The maximum sampling rate is 216 kHz. On request, the ADC goes through a self-calibration process that adjusts linearity, zero and full-scale errors.

The ADC12041 can be configured to work with many popular microprocessors/microcontrollers including National's HPC family, Intel386 and 8051, TMS320C25, Motorola MC68HC11/16, Hitachi 64180 and Analog Devices ADSP21xx.

For complementary voltage references see the LM4040, LM4041 or LM9140.

## **Key Specifications** (f<sub>CLK</sub> = 12 MHz)

- 12-bits + sign 3.6  $\mu$ s, max

- 13-bit conversion time ■ 13-bit throughput rate

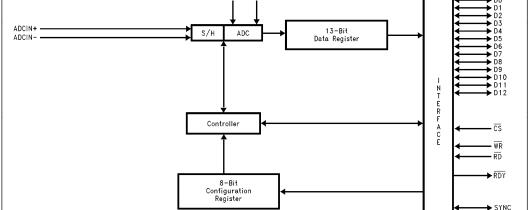

**Block Diagram**

- 216 ksamples/s, min  $\pm\,$ 1 LSB, max

- Integral Linearity Error (ILE)

■ Single supply

$+5V \pm 10\%$

■ V<sub>IN</sub> range

GND to V<sub>A</sub>+

■ Power consumption:

Normal operation Stand-by mode

33 mW, max 75  $\mu$ w, max

### **Features**

- Fully differential analog input

- Programmable acquisition times and user-controllable throughput rates

- Programmable data bus width (8/13 bits)

- Built-in Sample-and-Hold

- Programmable auto-calibration and auto-zero cycles

- Low power standby mode

- No missing codes

## **Applications**

- Medical instrumentation

- Process control systems

- Test equipment

- Data logging

- Inertial guidance

V<sub>REF</sub> V<sub>REF</sub><sup>+</sup>

WMODE

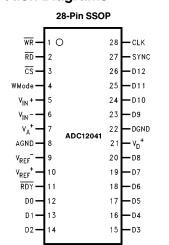

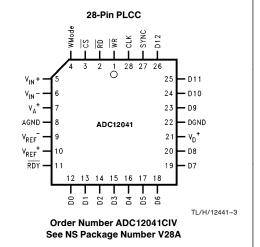

## **Connection Diagrams**

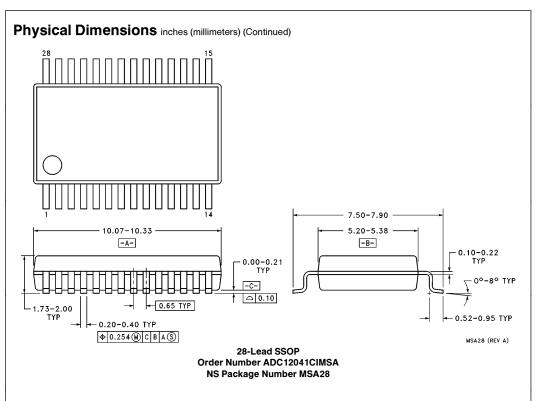

Order Number ADC12041CIMSA See NS Package Number MSA28

# **Ordering Information**

|               | NS<br>Package<br>Number |

|---------------|-------------------------|

| ADC12041CIV   | V28A                    |

| ADC12041CIMSA | MSA28, SSOP             |

## **Absolute Maximum Ratings**

(Notes 1 and 2)  $\begin{aligned} &\text{Supply Voltage (V}_A{}^+ \text{ and V}_D{}^+) & & 6.0V \\ &\text{Voltage at all Inputs} & & -0.3V \text{ to V}^+ + 0.3V \end{aligned}$

$\begin{array}{ll} |\mathsf{V_A} + - \mathsf{V_D}^+| & 300 \text{ mV} \\ |\mathsf{AGND} - \mathsf{DGND}| & 300 \text{ mV} \\ |\mathsf{Input Current at Any Pin (Note 3)} & \pm 30 \text{ mA} \\ |\mathsf{Package Input Current (Note 3)} & \pm 120 \text{ mA} \\ \end{array}$

Power Dissipation (Note 4)

at  $T_A = 25^{\circ}\text{C}$  500 mW Storage Temperature  $-65^{\circ}\text{C to} + 150^{\circ}\text{C}$

Lead Temperature SSOP Package

Vapor Phase (60 sec.)

210°C

Infared (15 sec.)

220°C

V Package, Infared (15 sec.)

300°C

ESD Susceptibility (Note 5)

3.0 kV

## Operating Ratings (Notes 1 and 2)

Temperature Range

$(T_{min} \le T_A \le T_{max})$   $-40^{\circ}C \le T_A \le 85^{\circ}C$

Supply Voltage

$\begin{array}{lll} & \text{VA}^+, \text{VD}^+ & \text{4.5V to 5.5V} \\ |\text{VA}^+ - \text{VD}^+| & & \text{5100 mV} \\ |\text{AGND} - \text{DGND}| & & \text{5100 mV} \\ |\text{VIN} \text{ Voltage Range at all Inputs} & & \text{GND} \leq \text{VIN}^+ \leq \text{VA}^+ \end{array}$

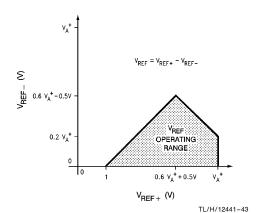

$V_{REF}^+$  Input Voltage  $V_{REF}^+ \le V_{A}^+$  $V_{REF}^-$  Input Voltage  $0 \le V_{REF}^- \le V_{REF}^+ - 1V$

$V_{REF}^{+} - V_{REF}^{-}$   $1V \le V_{REF} \le V_{A}^{+}$

$V_{REF}$  Common Mode 0.1  $V_A^+ \le V_{REFCM} \le 0.6 V_A^+$

**Converter DC Characteristics** The following specifications apply to the ADC12041 for  $V_A^+ = V_D^+ = 5V$ ,  $V_{REF}^+ = 4.096V$ ,  $V_{REF}^- = 0.0V$ , 12-bit + sign conversion mode,  $f_{CLK} = 12.0$  MHz,  $R_S = 25\Omega$ , source impedance for  $V_{REF}^+$  and  $V_{REF}^- \le 1\Omega$ , fully differential input with fixed 2.048V common-mode voltage ( $V_{INCM}$ ), and minimum acquisition time, unless otherwise specified. **Boldface limits apply for T\_A = T\_J = T\_{MIN} to T\_{MAX};** all other limits  $T_A = T_J = 25^{\circ}C$

| Symbol | Parameter                                         | Conditions                                                                                                     | Typical<br>(Note 10) | Limits<br>(Note 11)     | Units<br>(Limit) |

|--------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------|-------------------------|------------------|

|        | Resolution with No Missing Codes                  | After Auto-Cal                                                                                                 |                      | 13                      | Bits (max)       |

| ILE    | Positive and Negative Integral<br>Linearity Error | After Auto-Cal<br>(Notes 12 and 17)                                                                            | ±0.6                 | ± 1                     | LSB (max)        |

| DNL    | Differential Non-Linearity                        | After Auto-Cal                                                                                                 |                      | ± 1                     | LSB (max)        |

|        | Zero Error                                        | After Auto-Cal (Notes 13 and 17)  V <sub>INCM</sub> = 5.0V  V <sub>INCM</sub> = 2.048V  V <sub>INCM</sub> = 0V |                      | ± 5.5<br>± 2.0<br>± 5.5 | LSB (max)        |

|        | Positive Full-Scale Error                         | After Auto-Cal (Notes 12 and 17)                                                                               | ±1.0                 | ± 2.5                   | LSB (max)        |

|        | Negative Full-Scale Error                         | After Auto-Cal (Notes 12 and 17)                                                                               | ±1.0                 | ± 2.5                   | LSB (max)        |

|        | DC Common Mode Error                              | After Auto-Cal (Note 14)                                                                                       | ±2                   | ± 5.5                   | LSB (max)        |

| TUE    | Total Unadjusted Error                            | After Auto-Cal (Note 18)                                                                                       | ±1                   |                         | LSB              |

**Power Supply Characteristics** The following specifications apply to the ADC12041 for  $V_A^+ = V_D^+ = 5V$ ,  $V_{REF}^+ = 4.096V$ ,  $V_{REF}^- = 0.0V$ , 12-bit + sign conversion mode,  $f_{CLK} = 12.0$  MHz,  $R_S = 25\Omega$ , source impedance for  $V_{REF}^+$  and  $V_{REF}^- = 1\Omega$ , fully differential input with fixed 2.048V common-mode voltage, and minimum acquisition time, unless otherwise specified. **Boldface limits apply for T\_A = T\_J = T\_{MIN} to T\_{MAX};** all other limits  $T_A = T_J = 25^{\circ}C$

| Symbol           | Parameter                               | Conditions                                        | Typical<br>(Note 10) | Limits<br>(Note 11) | Unit<br>(Limit) |

|------------------|-----------------------------------------|---------------------------------------------------|----------------------|---------------------|-----------------|

| PSS              | Power Supply Sensitivity                | $V_D^+ = V_A^+ = 5.0V \pm 10\%$                   |                      |                     |                 |

|                  | Zero Error                              | $V_{REF}^{+} = 4.096V$                            | ±0.1                 |                     | LSB             |

|                  | Full-Scale Error                        | $V_{REF}^- = 0V$                                  | ±0.5                 |                     | LSB             |

|                  | Linearity Error                         |                                                   | ±0.1                 |                     | LSB             |

| I <sub>D</sub> + | V <sub>D</sub> + Digital Supply Current | Start Command (Performing a conversion) with SYNC |                      |                     |                 |

|                  |                                         | configured as an input and driven with a 214 kHz  |                      |                     |                 |

|                  |                                         | signal. Bus width set to 13.                      |                      |                     |                 |

|                  |                                         | f <sub>CLK</sub> = 12.0 MHz, Reset Mode           | 850                  |                     | μΑ              |

|                  |                                         | f <sub>CLK</sub> = 12.0 MHz, Conversion           | 2.45                 | 2.6                 | mA (max)        |

| I <sub>A</sub> + | V <sub>A</sub> + Analog Supply Current  | Start Command (Performing a conversion) with SYNC |                      |                     |                 |

|                  |                                         | configured as an input and driven with a 214 kHz  |                      |                     |                 |

|                  |                                         | signal. Bus width set to 13.                      |                      |                     |                 |

|                  |                                         | f <sub>CLK</sub> = 12.0 MHz, Reset Mode           | 2.3                  |                     | mA              |

|                  |                                         | f <sub>CLK</sub> = 12.0 MHz, Conversion           | 2.3                  | 4.0                 | mA (max)        |

| I <sub>ST</sub>  | Standby Supply Current                  | Standby Mode                                      |                      |                     |                 |

|                  | $(I_D^+ + I_A^+)$                       | f <sub>CLK</sub> = Stopped                        | 5                    | 15                  | μΑ (max)        |

|                  |                                         | $f_{CLK} = 12.0 \text{ MHz}$                      | 100                  | 120                 | μA (max)        |

**Analog Input Characteristics** The following specifications apply to the ADC12041 for  $V_A^+ = V_D^+ = 5V$ ,  $V_{REF}^+ = 4.096V$ ,  $V_{REF}^- = 0.0V$ , 12-Bit + sign conversion mode,  $f_{CLK} = 12.0$  MHz,  $R_S = 25\Omega$ , source impedance for  $V_{REF}^+$  and  $V_{REF}^+ \le 1\Omega$ , fully differential input with fixed 2.048V common-mode voltage, and minimum acquisition time, unless otherwise specified. **Boldface limits apply for T**<sub>A</sub> = **T**<sub>J</sub> = **T**<sub>MIN</sub> **to T**<sub>MAX</sub>; **all other limits T**<sub>A</sub> = **T**<sub>J</sub> = **25**°C

| Symbol          | Parameter                                                 | Conditions                                                        | Typical<br>(Note 10) | Limits<br>(Note 11) | Unit<br>(Limit) |

|-----------------|-----------------------------------------------------------|-------------------------------------------------------------------|----------------------|---------------------|-----------------|

| I <sub>IN</sub> | ${ m V_{IN}}^+$ and ${ m V_{IN}}^-$ Input Leakage Current | $V_{IN}^{+} = 5V$<br>$V_{IN}^{-} = 0V$                            | 0.05<br>0.05         | 2.0                 | μA (max)        |

| R <sub>ON</sub> | ADC Input On Resistance                                   | $V_{\rm IN} = 2.5 {\rm V}$ Refer to section titled INPUT CURRENT. | 1000                 |                     | Ω               |

| CVIN            | ADC Input Capacitance                                     |                                                                   | 10                   |                     | pF              |

**Reference Inputs** The following specifications apply to the ADC12041 for  $V_A{}^+ = V_D{}^+ = 5V$ ,  $V_{REF}{}^+ = 4.096V$ ,  $V_{REF}{}^- = 0.0V$ , 12-bit + sign conversion mode,  $f_{CLK} = 12.0$  MHz,  $R_S = 25\Omega$ , source impedance for  $V_{REF}{}^+$  and  $V_{REF}{}^- \le 1\Omega$ , fully differential input with fixed 2.048V common-mode voltage, and minimum acquisition time, unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A = T_J = 25^{\circ}C$

| Symbol           | Parameter                   | Conditions                                                                                                                 | Typical<br>(Note 10) | Limits<br>(Note 11) | Unit<br>(Limit) |

|------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|-----------------|

| I <sub>REF</sub> | Reference Input Current     | V <sub>REF</sub> <sup>+</sup> 4.096V, V <sub>REF</sub> <sup>-</sup> = 0V<br>Analog Input Signal: 1 kHz<br>(Note 20) 80 kHz | 145<br>136           |                     | μΑ<br>μΑ        |

| C <sub>REF</sub> | Reference Input Capacitance |                                                                                                                            | 85                   |                     | pF              |

Digital Logic Input/Output Characteristics The following specifications apply to the ADC12041 for  $V_A^+ = V_D^+ = 5V$ ,  $V_{REF}^+ = 4.096V$ ,  $V_{REF}^- = 0.0V$ , 12-bit + sign conversion mode,  $f_{CLK}^- = 12.0$  MHz,  $f_{RS}^- = 25\Omega$ , source impedance for  $f_{REF}^+ = 12.0$  MHz,  $f_{RS}^- = 12.0$

| Symbol          | Parameter                                                      | Conditions                                            | Typical<br>(Note 10) | Limits<br>(Note 11) | Unit<br>(Limit) |

|-----------------|----------------------------------------------------------------|-------------------------------------------------------|----------------------|---------------------|-----------------|

| V <sub>IH</sub> | Logic High Input Voltage                                       | $V_A^+ = V_D^+ = 5.5V$                                |                      | 2.2                 | V (min)         |

| V <sub>IL</sub> | Logic Low Input Voltage                                        | $V_A^+ = V_D^+ = 4.5V$                                |                      | 0.8                 | V (max)         |

| I <sub>IH</sub> | Logic High Input Current V <sub>IN</sub> = 5V 0.035 <b>2.0</b> |                                                       | μΑ (max)             |                     |                 |

| I <sub>IL</sub> | Logic Low Input Current                                        | $V_{IN} = 0V$                                         | -0.035               | -2.0                | μA (max)        |

| V <sub>OH</sub> | Logic High Output Voltage                                      | $V_A^+ = V_D^+ = 4.5V$<br>$I_{OUT} = -1.6 \text{ mA}$ | 2.4                  | 2.4                 | V (min)         |

| V <sub>OL</sub> | Logic Low Output Voltage                                       | $V_A^+ = V_D^+ = 4.5V$<br>$I_{OUT} = 1.6 \text{ mA}$  | 0.4                  | 0.4                 | V (max)         |

| loff            | TRI-STATE Output Leakage Current                               | $V_{OUT} = 0V$ $V_{OUT} = 5V$                         | ± 2.0                |                     | μΑ (max)        |

| C <sub>IN</sub> | D12-D0 Input Capacitance                                       |                                                       | 10                   |                     | pF              |

**Converter AC Characteristics** The following specifications apply to the ADC12041 for  $V_S^+ = V_D^+ = 5V$ ,  $V_{REF}^+ = 4.096V$ ,  $V_{REF}^- = 0.0V$ , 12-bit + sign conversion mode,  $f_{CLK} = 12.0$  MHz,  $F_S = 25\Omega$ , source impedance for  $V_{REF}^+$  and  $V_{REF}^- \le 1\Omega$ , fully differential input with fixed 2.048V common-mode voltage, and minimum acquisition time, unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A = T_J = 25^{\circ}C$

| Symbol           | Parameter             | Conditions          | Typical<br>(Note 10) | Limits<br>(Note 11) | Unit<br>(Limit) |

|------------------|-----------------------|---------------------|----------------------|---------------------|-----------------|

| $t_Z$            | Auto Zero Time        |                     | 78                   | 78 clks + 120 ns    | clks (max)      |

| t <sub>CAL</sub> | Full Calibration Time |                     | 4946                 | 4946 clks + 120 ns  | clks (max)      |

|                  | CLK Duty Cycle        |                     | 50                   |                     | %               |

|                  |                       |                     |                      | 40                  | % (min)         |

|                  |                       |                     |                      | 60                  | % (max)         |

| tconv            | Conversion Time       | Sync-Out Mode       | 44                   | 44                  | clks (max)      |

| tAcqSYNCOUT      | Acquisition Time      | Minimum for 13 Bits | 9                    | 9 clks + 120 ns     | clks (max)      |

|                  | (Programmable)        | Maximum for 13 Bits | 79                   | 79 clks + 120 ns    | clks (max)      |

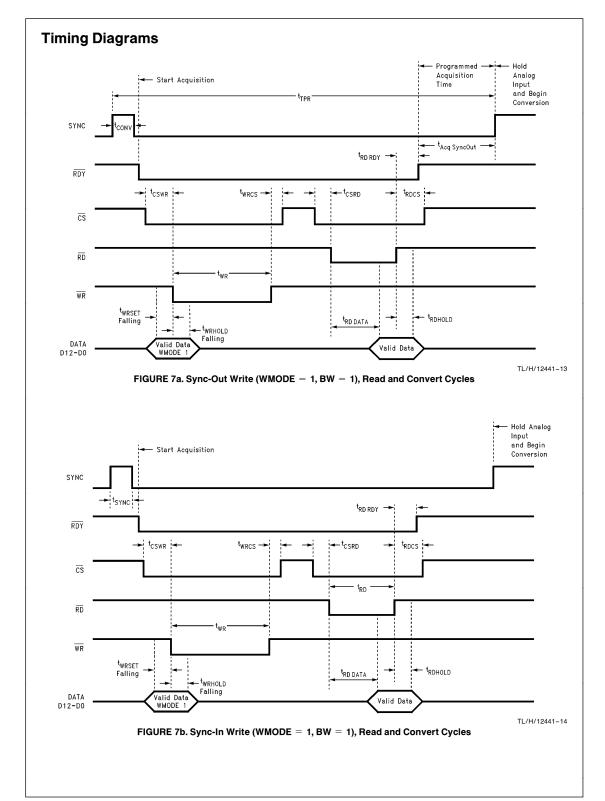

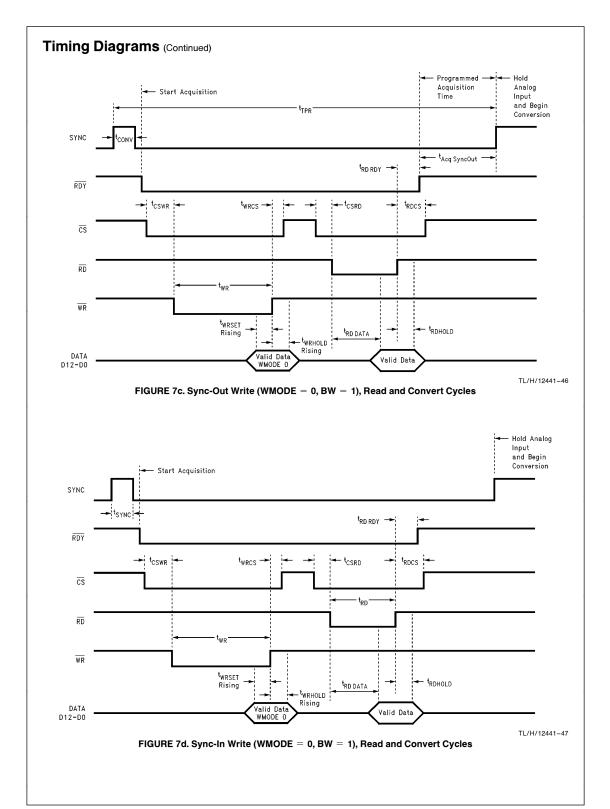

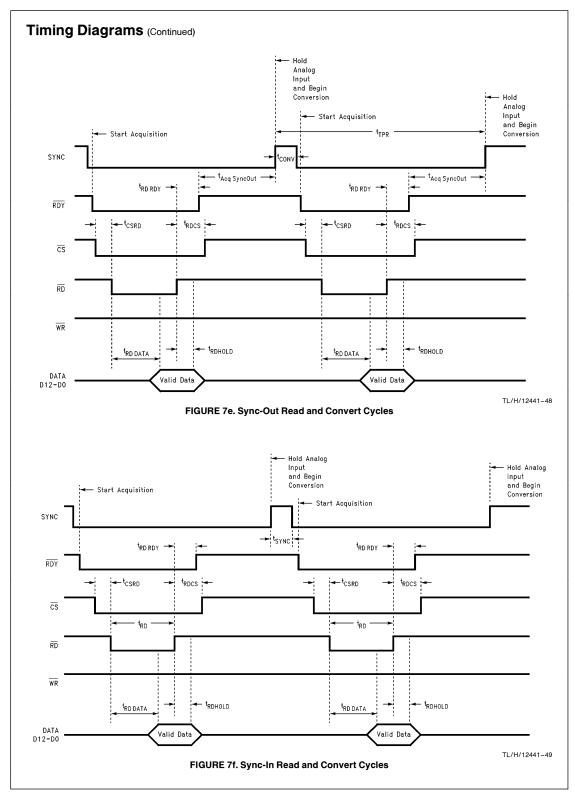

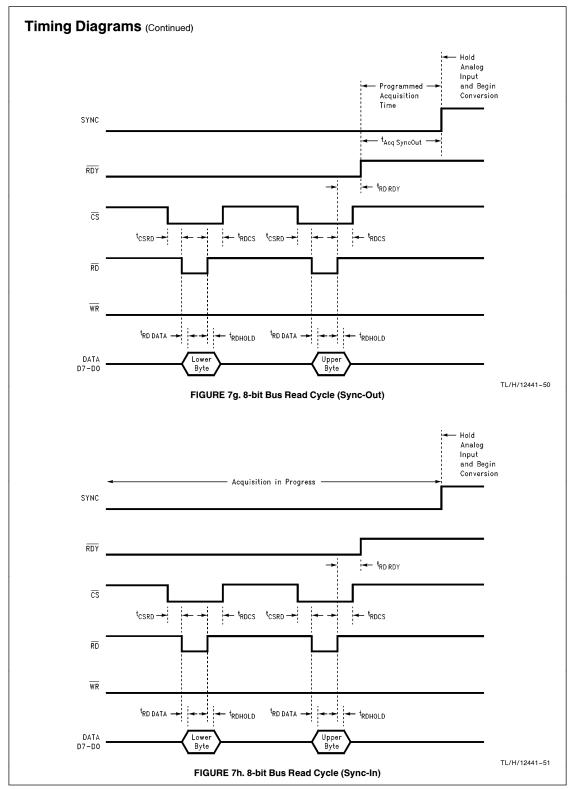

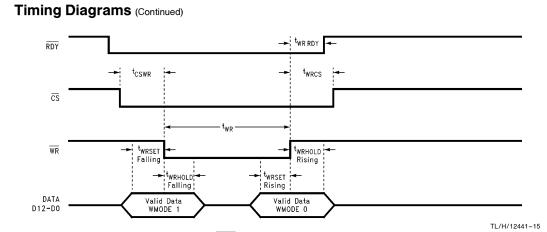

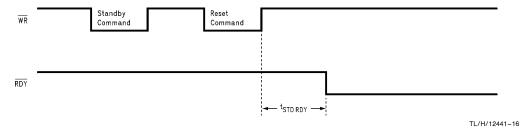

| Symbol<br>(Figure 7) | Parameter                                   | Conditions                                                             | Typical<br>(Note 10) | Limits<br>(Note 11) | Unit<br>(Limit) |

|----------------------|---------------------------------------------|------------------------------------------------------------------------|----------------------|---------------------|-----------------|

| t <sub>TPR</sub>     | Throughput Rate                             | Sync-Out Mode (SYNC Bit = "0") 9 Clock Cycles of Acquisition Time      | 222                  |                     | kHz             |

| t <sub>CSWR</sub>    | Falling Edge of CS<br>to Falling Edge of WR |                                                                        | 0                    |                     | ns              |

| t <sub>WRCS</sub>    | Active Edge of WR to Rising Edge of CS      |                                                                        | 0                    |                     | ns              |

| $t_{WR}$             | WR Pulse Width                              |                                                                        | 20                   | 30                  | ns (min)        |

| twRSETFalling        | Write Setup Time                            | WMODE = "1"                                                            |                      | 20                  | ns (min)        |

| twRHOLDFalling       | Write Hold Time                             | WMODE = "1"                                                            |                      | 5                   | ns (min)        |

| twRSETRising         | Write Setup Time                            | WMODE = "0"                                                            |                      | 20                  | ns (min)        |

| twRHOLDRising        | Write Hold Time                             | WMODE = "0"                                                            |                      | 5                   | ns (min)        |

| t <sub>CSRD</sub>    | Falling Edge of CS to Falling Edge of RD    |                                                                        | 0                    |                     | ns              |

| t <sub>RDCS</sub>    | Rising Edge of RD to Rising Edge of CS      |                                                                        | 0                    |                     | ns              |

| t <sub>RDDATA</sub>  | Falling Edge of RD to Valid Data            | 8-Bit Mode (BW Bit = "0")                                              | 40                   | 58                  | ns (max)        |

| t <sub>RDDATA</sub>  | Falling Edge of RD to Valid Data            | 13-Bit Mode (BW Bit = "1")                                             | 26                   | 44                  | ns (max)        |

| t <sub>RDHOLD</sub>  | Read Hold Time                              |                                                                        | 23                   | 32                  | ns (max)        |

| t <sub>RDRDY</sub>   | Rising Edge of RD to Rising Edge of RDY     |                                                                        | 24                   | 38                  | ns (max)        |

| t <sub>WRRDY</sub>   | Active Edge of WR to Rising Edge of RDY     | WMODE = "1"                                                            | 37                   | 60                  | ns (max)        |

| <sup>t</sup> STDRDY  | Active Edge of WR to Falling Edge of RDY    | WMODE = "0". Writing the RESET Command into the Configuration Register | 1.4                  | 2.5                 | ms (max)        |

| t <sub>SYNC</sub>    | Minimum SYNC Pulse Width                    |                                                                        | 5                    | 10                  | ns (min)        |

## **Notes on Specifications**

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supply rails  $(V_{IN} \le GND \text{ or } V_{IN} \ge (V_A^+ \text{ or } V_D^+))$ , the current at that pin should be limited to 30 mA. The 120 mA maximum package input current limits the number of pins that can safely exceed the power supplies with an input current of 30 mA to four.

Note 4: The maximum power dissipation must he derated at elevated temperatures and is dictated by  $T_{Jmax}$ . (maximum junction temperature),  $\theta_{JA}$  (package junction to ambient thermal resistance), and  $T_A$  (ambient temperature). The maximum allowable power dissipation at any temperature is  $P_{Dmax} = (T_{Jmax} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For this device,  $T_{Jmax} = 150^{\circ}C$ , and the typical thermal resistance ( $\theta_{JA}$ ) of the ADC12041 in the V package, when board mounted, is 55°C/W, and in the SSOP package, when board mounted, is 130°C/W.

Note 5: Human body model, 100 pF discharged through 1.5  $\Omega k$  resistor.

### **Notes on Specifications** (Continued)

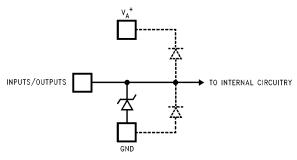

Note 6: Each input is protected by a nominal 6.5V breakdown voltage zener diode to GND, as shown below, input voltage magnitude up to 5V above V<sub>A</sub><sup>+</sup> or 5V below GND will not damage the ADC12041. There are parasitic diodes that exist between the inputs and the power supply rails and errors in the A/D conversion can occur if these diodes are forward biased by more than 50 mV. As an example, if V<sub>A</sub><sup>+</sup> is 4.50 V<sub>DC</sub>, full-scale input voltage must be 4.55 V<sub>DC</sub> to ensure accurate conversions.

TL/H/12441-4

Note 7:  $V_A^+$  and  $V_D^+$  must be connected together to the same power supply voltage and bypassed with separate capacitors at each  $V^+$  pin to assure conversion/comparison accuracy. Refer to the Power Supply Considerations section for a detailed discussion.

Note 8: Accuracy is guaranteed when operating at  $f_{CLK} = 12$  MHz.

Note 9: With the test condition for  $V_{REF}^+ - V_{REF}^-$ ) given as  $\pm$  4.096V, the 12-bit LSB is 1.000 mV.

Note 10: Typicals are at  $T_A = 25^{\circ}C$  and represent most likely parametric norm.

Note 11: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

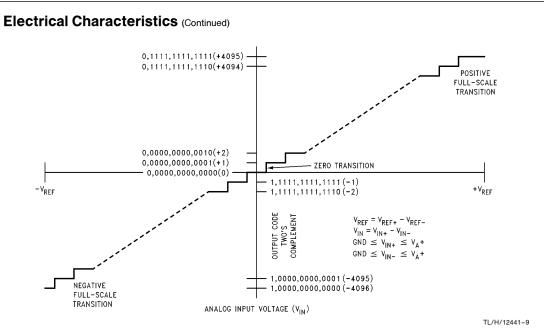

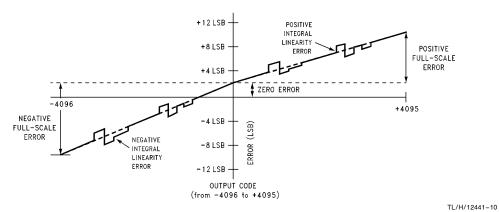

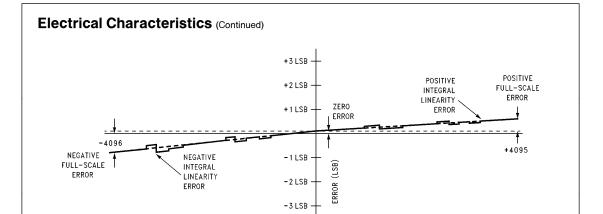

Note 12: Positive integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive full-scale and zero. For negative integral linearity error, the straight line passes through negative full-scale and zero.

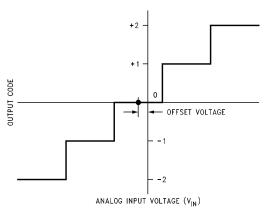

Note 13: Zero error is a measure of the deviation from the mid-scale voltage (a code of zero), expressed in LSB. It is the average value of the code transitions between -1 to 0 and 0 to + 1 (see Figure 6).

Note 14: The DC common-mode error is measured with both inputs shorted together and driven from 0V to 5V. The measured value is referred to the resulting output value when the inputs are driven with a 2.5V input.

Note 15: Power Supply Sensitivity is measured after an Auto-Zero and Auto Calibration cycle has been completed with  $V_A^+$  and  $V_D^+$  at the specified extremes.

Note 16:  $V_{REFCM}$  (Reference Voltage Common Mode Range) is defined as  $\left(\frac{V_{REF}{}^{+} + V_{REF}{}^{-}}{2}\right)$

Note 17: The ADC12041's self-calibration technique ensures linearity and offset errors as specified, but noise inherent in the self-calibration process will result in a repeatability uncertainty of ±0.20 LSB.

Note 18: Total Unadjusted Error (TUE) includes offset, full scale linearity and MUX errors.

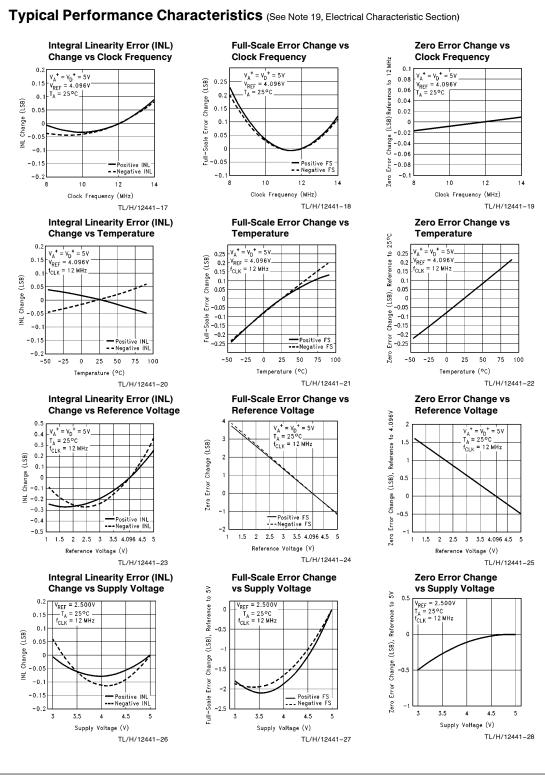

Note 19: The ADC12041 parts used to gather the information for these curves were auto-calibrated prior to taking the measurements at each test condition. The auto-calibration cycle cancels any first order drifts due to test conditions. However, each measurement has a repeatability uncertainty error of 0.2 LSB. See Note 17

Note 20: This is a DC average current drawn by the reference input with a full-scale sinewave input. The ADC12041 is continuously converting with a throughput rate of 206 kHz.

Note 21: These typical curves were measured during continuous conversions with a positive half-scale DC input. A 240 ns  $\overline{\text{RD}}$  pulse was applied 25 ns after the  $\overline{\text{RDY}}$  signal went low. The data bus lines were loaded with 2 HC family CMOS inputs (C<sub>L</sub>  $\sim$  20 pF).

Note 22: Any other values placed in the command field are meaningless. However, if a code of 101 or 110 is placed in the command field and the  $\overline{\text{CS}}$ ,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  go low at the same time, the ADC12041 will enter a test mode. These test modes are only to be used by the manufacturer of this device. A hardware power-off and power-on reset must be done to get out of these test modes.

FIGURE 5a. Transfer Characteristic

FIGURE 5b. Simplified Error vs Output Code without Auto-Calibration or Auto-Zero Cycles

FIGURE 5c. Simplified Error vs Output Code after Auto-Calibration Cycle

OUTPUT CODE (from -4096 to +4095)

TL/H/12441-11

FIGURE 6. Offset or Zero Error Voltage (Note 13)

FIGURE 7i. Write Signal Negates  $\overline{RDY}$  (Writing the Standby, Auto-Cal or Auto-Zero Command)

FIGURE 7j. Standby and Reset Timing (13-Bit Data Bus Width)

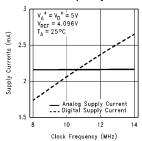

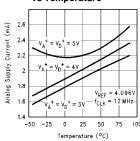

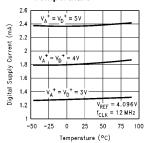

## Typical Performance Characteristics (See Note 21, Electrical Characteristic Section) (Continued)

## Supply Current vs Clock Frequency

TL/H/12441-29

#### Reference Current vs Clock Frequency

TL/H/12441-30

# Analog Supply Current vs Temperature

TL/H/12441-31

## Digital Supply Current vs Temperature

**Typical Performance Characteristics** (Continued) The curves were obtained under the following conditions.  $R_S = 50\Omega$ ,  $T_A = 25^{\circ}C$ ,  $V_A{}^{+} = V_D{}^{+} = 5V$ ,  $V_{REF} = 4.096V$ ,  $f_{CLK} = 12$  MHz, and the sampling rate  $f_S = 215$  kHz unless otherwise stated.

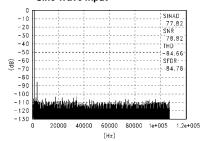

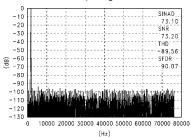

#### Full Scale Differential 1,099 Hz Sine Wave Input

TL/H/12441-33

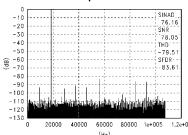

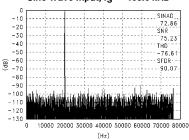

## Full Scale Differential 18,677 Hz Sine Wave Input

TL/H/12441-34

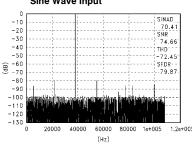

#### Full Scale Differential 38,452 Hz Sine Wave Input

TL/H/12441-35

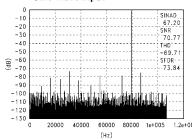

### Full Scale Differential 79,468 Hz Sine Wave Input

TL/H/12441-36

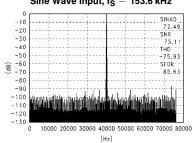

#### Half Scale Differential 1 kHz Sine Wave Input, f<sub>S</sub> = 153.6 kHz

TL/H/12441-37

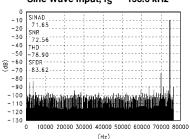

# Half Scale Differential 20 kHz Sine Wave Input, $f_S = 153.6 \text{ kHz}$

TL/H/12441-38

# Half Scale Differential 40 kHz Sine Wave Input, $f_S = 153.6 \text{ kHz}$

TL/H/12441-39

#### Half Scale Differential 75 kHz Sine Wave Input, f<sub>S</sub> = 153.6 kHz

| PLCC and<br>SSOP Pkg.<br>Pin Number | Pin<br>Name                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5<br>6                              | V <sub>IN</sub> +<br>V <sub>IN</sub> - | The analog ADC inputs. $V_{IN}+$ is the non-inverting (positive) input and $V_{IN}-$ is the inverting (negative) input into the ADC.                                                                                                                                                                                                                                                                                                    |  |  |  |

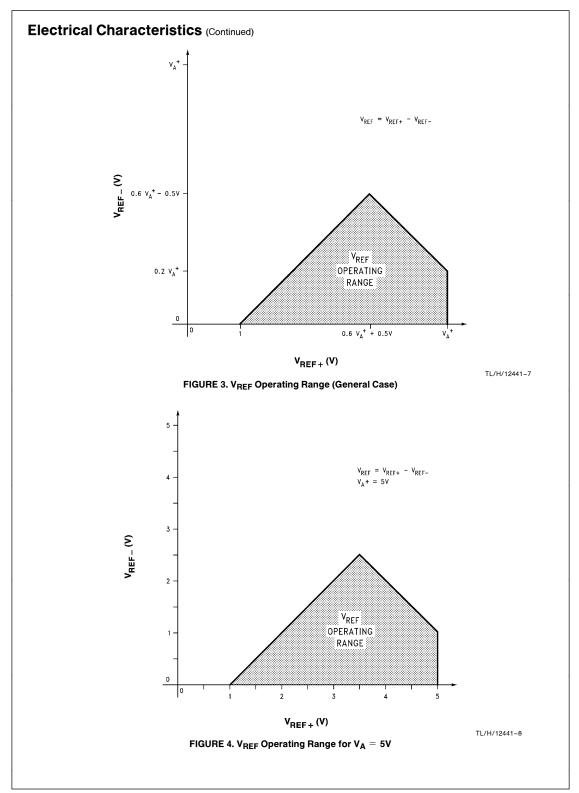

| 10                                  | V <sub>REF</sub> +                     | Positive reference input. The operating voltage range for this input is $1V \le V_{REF}^+ \le V_A^+$ (see <i>Figures 3</i> and 4). This pin should be bypassed to AGND at least with a parallel combination of a 10 $\mu$ F and a 0.1 $\mu$ F (ceramic) capacitor. The capacitors should be placed as close to the part as possible.                                                                                                    |  |  |  |

| 9                                   | V <sub>REF</sub> -                     | Negative reference input. The operating voltage range for this input is $0V \le V_{REF}^- \le V_{REF}^+ - 1$ (see Figures 3 and 4). This pin should be bypassed to AGND at least with a parallel combination of a 10 $\mu$ F and a 0.1 $\mu$ F (ceramic) capacitor. The capacitors should be placed as close to the part as possible.                                                                                                   |  |  |  |

| 4                                   | WMODE                                  | he logic state of this pin at power-up determines which edge of the write signal ( $\overline{WR}$ ) will latch in data om the data bus. If tied low, the ADC12041 will latch in data on the rising edge of the $\overline{WR}$ signal. If tied is a logic high, data will be latched in on the falling edge of the $\overline{WR}$ signal. The state of this pin should of the changed after power-up.                                 |  |  |  |

| 27                                  | SYNC                                   | he SYNC pin can be programmed as an <b>input</b> or an <b>output</b> . The Configuration register's bit b4 controls be function of this pin. When programmed as an input pin ( $b4 = 1$ ), a rising edge on this pin causes the DC's sample-and-hold to hold the analog input signal and begin conversion. When programmed as an atput pin ( $b4 = 0$ ), the SYNC pin goes high when a conversion begins and returns low when impleted. |  |  |  |

| 12-20<br>23-26                      | D0-D8<br>D9-D12                        | bit Data bus of the ADC12041. D12 is the most significant bit and D0 is the least significant. The BW(bus width) bit of the Configuration register (b3) selects between an 8-bit or 13-bit data bus width. When the BW bit is cleared (BW = 0), D7-D0 are active and D12-D8 are always in TRI-STATE®. When the BW bit is set (BW = 1), D12-D0 are active.                                                                               |  |  |  |

| 28                                  | CLK                                    | The clock input pin used to drive the ADC12041. The operating range is 0.05 MHz to 12 MHz.                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 1                                   | WR                                     | WR is the active low WRITE control input pin. A logic low on this pin and the CS will enable the input buffers of the data pins D12–D0. The signal at this pin is used by the ADC12041 to latch in data on D12–D0. The sense of the WMODE pin at power-up will determine which edge of the WR signal the ADC12041 will latch in data. See WMODE pin description.                                                                        |  |  |  |

| 2                                   | RD                                     | $\overline{\text{RD}}$ is the active low read control input pin. A logic low on this pin and $\overline{\text{CS}}$ will enable the active output buffers to drive the data bus.                                                                                                                                                                                                                                                        |  |  |  |

| 3                                   | <u>CS</u>                              | $\overline{\text{CS}}$ is the active low Chip Select input pin. Used in conjunction with the $\overline{\text{WR}}$ and $\overline{\text{RD}}$ signals to control the active data bus input/output buffers of the data bus.                                                                                                                                                                                                             |  |  |  |

| 11                                  | RDY                                    | RDY is an active low output pin. The signal at this pin indicates when a requested function has begun or ended. Refer to section <b>Functional Description</b> and the digital timing diagrams for more detail.                                                                                                                                                                                                                         |  |  |  |

| 7                                   | V <sub>A</sub> <sup>+</sup>            | Analog supply input pin. The device operating supply voltage range is $\pm 5V \pm 10\%$ . Accuracy is guaranteed only if the $V_A^+$ and $V_D^+$ are connected to the same potential. This pin should be bypassed to AGND with a parallel combination of a 10 $\mu$ F and a 0.1 $\mu$ F (ceramic) capacitor. The capacitors should be placed as close to the supply pins of the part as possible.                                       |  |  |  |

| 8                                   | AGND                                   | Analog ground pin. This is the device's analog supply ground connection. It should be connected through a low resistance and low inductance ground return to the system power supply.                                                                                                                                                                                                                                                   |  |  |  |

| 21                                  | V <sub>D</sub> +                       | Digital supply input pins. The device operating supply voltage range is $+5V \pm 10\%$ . Accuracy is guaranteed only if the $V_A^+$ and $V_D^+$ are connected to the same potential. This pin should be bypassed to DGND with a parallel combination of a 10 $\mu$ F and a 0.1 $\mu$ F (ceramic) capacitor. The capacitors should be placed as close to the supply pins of the part as possible.                                        |  |  |  |

| 22                                  | DGND                                   | Digital ground pin. This is the device's digital supply ground connection. It should be connected through a low resistance and low inductance ground return to the system power supply.                                                                                                                                                                                                                                                 |  |  |  |

| 28-Pin SSOP                         |                                        | Wind   1                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

## **Register Bit Description**

#### **CONFIGURATION REGISTER (Write Only)**

This is an 8-bit write-only register that is used to program the functionality of the ADC12041. All data written to the ADC12041 will always go to this register only. The contents of this register cannot be read.

ISB

LSB

| b <sub>7</sub>   | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

|------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| COMMAND<br>FIELD |                |                | SYNC           | BW             | SE             | ACC            | TIME           |

Power on State: 10 Hex

$b_1-b_0$ : The ACQ TIME bits select one of four possible acquistion times in the SYNC-OUT mode ( $b_4=0$ ). (Refer to **Selectable Acquisition Time** section, page 22).

| b <sub>1</sub> | b <sub>0</sub> | Clocks |

|----------------|----------------|--------|

| 0              | 0              | 9      |

| 0              | 1              | 15     |

| 1              | 0              | 47     |

| 1              | 1              | 79     |

**b<sub>2</sub>:** When the Single-Ended bit (SE bit) is set, conversion results will be limited to positive values only and any negative conversion results will appear as a code of zero in the Data register. The SE bit is cleared at **power-up**.

$\mathbf{b_3}$ : This is the Bus Width (BW) bit. When this bit is cleared the ADC12041 is configured to interface with an 8-bit data bus; data pins  $D_7 - D_0$  are active and pins  $D_{12} - D_9$  are in TRI-STATE. When the BW bit is set, the ADC12041 is configured to interface with a 16-bit data bus and data pins  $D_{12} - D_0$  are all active. The BW bit is cleared at **power-up**.

**b**<sub>4</sub>: The SYNC bit. When the SYNC bit is set, the SYNC pin is programmed as an input and the converter is in synchronous mode. In this mode a rising edge on the SYNC pin causes the ADC to hold the input signal and begin a conversion. When b<sub>8</sub> is cleared, the SYNC pin is programmed as an output and the converter is in an asynchronous mode. In this mode the signal at the SYNC pin indicates the status of the converter. The SYNC pin is high when a conversion is taking place. The SYNC bit is set at **power-up**.

b<sub>7</sub>-b<sub>5</sub>: The command field. These bits select the mode of operation of the ADC12041. Power-up value is 000. (See Note 22)

| b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | Command                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|----------------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0              | 0              | 0              | Standby command. This puts the ADC in a low power consumption mode.                                                                                                                                                                                                                                                                                   |  |  |  |

| 0              | 0              | 1              | Ful-Cal command. This will cause the ADC to perform a self-calibrating cycle that will correct linearity and zero errors.                                                                                                                                                                                                                             |  |  |  |

| 0              | 1              | 0              | Auto-zero command. This will cause the ADC to perform an auto-zero cycle that corrects offset errors.                                                                                                                                                                                                                                                 |  |  |  |

| 0              | 1              | 1              | Reset command. This puts the ADC in an idle mode.                                                                                                                                                                                                                                                                                                     |  |  |  |

| 1              | 0              | 0              | Start command. This will put the converter in a start mode, preparing it to perform a conversion. If in asynchronous mode (b <sub>4</sub> = "0"), conversions will immediately begin after the programmed acquisition time has ended. In synchronous mode (b <sub>4</sub> = "1"), conversions will begin after a rising edge appears on the SYNC pin. |  |  |  |

#### DATA REGISTER (Read Only)

This is a 13-bit read only register that holds the 12-bit + sign conversion result in two's complement form. All reads performed from the ADC12041 will place the contents of this register on the data bus. When reading the data register in 8-bit mode, the sign bit is extended.

MSB

LSB

| b <sub>12</sub> | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |  |

|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|

| sign            |                 |                 |                |                | (              | Convers        | ion Data       | 1              |                |                |                |                |  |

Power on State: 0000Hex

$\textbf{b}_{11}\textbf{-}\textbf{b}_0\textbf{:} \ b_{11} \ \text{is the most significant bit and } b_0 \ \text{is the least significant bit of the conversion result.}$

b<sub>12</sub>: This bit contains the sign of the conversion result. 0 for positive results and 1 for negative.

## **Functional Description**

The ADC12041 is programmed through a digital interface that supports an 8-bit or 16-bit data bus. The digital interface consists of a 13-bit data input/output bus  $(D_{12}-D_0),$  digital control signals and two internal registers: a write only 8-bit Configuration register and a read only 13-bit Data register.

The Configuration register programs the functionality of the ADC12041. The 8 bits of the Configuration register are divided into 5 fields. Each field controls a specific function of the ADC12041: the acquisition time, synchronous or asynchronous conversions, mode of operation and the data bus size

## **Features and Operating Modes**

#### **SELECTABLE BUS WIDTH**

The ADC12041 can be programmed to interface with an 8-bit or 16-bit data bus. The BW bit (b<sub>3</sub>) in the Configuration register controls the bus size. The bus width is set to 8 bits (D<sub>7</sub>–D<sub>0</sub> are active and D<sub>12</sub>–D<sub>8</sub> are in TRI-STATE) if the BW bit is cleared or 13 bits (D<sub>12</sub>–D<sub>0</sub> are active) if the BW bit is set. At power-up the default bus width is 8 bits (BW = 0).

In 8-bit mode the Configuration register is accessed with a single write. When reading the ADC in 8-bit mode, the first read cycle places the lower byte of the Data register on the data bus followed by the upper byte during the next read cycle.

In 13-bit mode all bits of the Data register and Configuration register are accessible with a single read or write cycle. Since the bus width of the ADC12041 defaults to 8 bits after power-up, the first action when 13-bit mode is desired must be to set the bus width to 13 bits.

#### WMODE

The WMODE pin is used to determine the active edge of the write pulse. The state of this pin determines which edge of the  $\overline{WR}$  signal will cause the ADC to latch in data. This is processor dependent. If the processor has valid data on the bus during the falling edge of the  $\overline{WR}$  signal, the WMODE pin must be tied to  $V_D^+$ . This will cause the ADC to latch the data on the falling edge of the  $\overline{WR}$  signal. If data is valid on the rising edge of the  $\overline{WR}$  signal, the WMODE pin must be tied to DGND causing the ADC to latch in the data on the rising edge of the  $\overline{WR}$  signal.

#### **ANALOG INPUTS**

The ADCIN+ and ADCIN- are the fully differential non-inverting (positive) and inverting (negative) inputs into the analog-to-digital converter (ADC) of the ADC12041.

#### STANDBY MODE

The ADC12041 has a low power consumption mode (75  $\mu$ W @ 5V). This mode is entered when a Standby command is written in the command field of the Configuration register. The  $\overline{\text{RDY}}$  ouput pin is high when the ADC12041 is in the Standby mode. Any command other than the Standby command written to the Configuration register will get the ADC12041 out of the Standby mode. The  $\overline{\text{RDY}}$  pin will immediately switch to a logic "0" when the ADC12041 is out of the standby mode. The ADC12041 defaults to the Standby mode following a hardware power-up.

#### SYNC/ASYNC MODE

The ADC12041 may be programmed to operate in synchronous (SYNC-IN) or asynchronous (SYNC-OUT) mode. To enter synchronous mode, the SYNC bit in the Configuration register must be set. The ADC12041 is in synchronous mode after a hardware power-up. In this mode, the SYNC pin is programmed as an input and conversions are synchronized to the rising edges of the signal applied at the SYNC pin. Acquisition time can also be controlled by the SYNC signal when in synchronous mode. Refer to the syncin timing diagrams. When the SYNC bit is cleared, the ADC is in asynchronous mode and the SYNC pin is programmed as an output. In asynchronous mode, the signal at the SYNC pin indicates the status of the converter. This pin is high when the converter is performing a conversion. Refer to the sync-out timing diagrams.

#### **SELECTABLE ACQUISITION TIME**

The ADC12041's internal sample/hold circuitry samples an input voltage by connecting the input to an internal sampling capacitor (approximately 70 pF) through an effective resistance equal to the "On" resistance of the analog switch at the input to the sample/hold circuit (2500 $\Omega$  typical) and the effective output resistance of the source. For conversion results to be accurate, the period during which the sampling capacitor is connected to the source (the "acquisition time") must be long enough to charge the capacitor to within a small fraction of an LSB of the input voltage. An acquisition time of 750 ns is sufficient when the external source resistance is less than 1  $k\Omega$  and any active or reactive source circuitry settles to 12 bits in less than 500 ns. When source resistance or source settling time increase beyond these limits, the acquisition time must also be increased to preserve precision.

In asynchronous (SYNC-OUT) mode, the acquisition time is controlled by an internal counter. The minimum acquisition period is 9 clock cycles, which corresponds to the nominal value of 750 ns when the clock frequency is 12 MHz. Bits  $b_0$  and  $b_1$  of the Configuration Register are used to select the acquisition time from among four possible values (9, 15, 47, or 79 clock cycles). Since acquisition time in the asynchronous mode is based on counting clock cycles, it is also inversely proportional to clock frequency:

$$T_{ACQ}$$

( $\mu$ s) =  $\frac{\text{number of clock cycles}}{f_{CLK}$  (MHz)

Note that the actual acquisition time will be longer than  $T_{ACQ}$  because acquisition begins either when the multiplexer channel is changed or when  $\overline{RDY}$  goes low, if the multiplexer channel is not changed. After a read is performed,  $\overline{RDY}$  goes high, which starts the  $T_{ACQ}$  counter (see Figure 7).

In synchronous (SYNC-IN) mode, bits  $b_0$  and  $b_1$  are ignored, and the acquisition time depends on the sync signal applied to the SYNC pin. The acquisition period begins on the falling edge of  $\overline{\text{RDY}},$  which occurs at the end of the previous conversion (or at the end of an autozero or autocalibration procedure. The acquisition period ends when SYNC goes high.

To estimate the acquisition time necessary for accurate conversions when the source resistance is greater than 1  $k\Omega,$  use the following expression:

$$T_{ACQMIN}\left(\mu s\right) = \frac{0.75\left(R_S + R_{S/H}\right)}{1~k\Omega + R_{S/H}} = \frac{0.75\left(R_S + 2500\right)}{3500}$$

where  $R_S$  is the source resistance, and  $R_{S/H}$  is the sample/hold "On" resistance.

## Features and Operating Modes (Continued)

If the settling time of the source is greater than 500 ns, the acquisition time should be about 300 ns longer than the settling time for a "well-behaved", smooth settling characteristic

#### **FULL CALIBRATION CYCLE**

A full calibration cycle compensates for the ADC's linearity and offset errors. The converter's DC specifications are guaranteed only after a full calibration has been performed. A full calibration cycle is initated by writing a Ful-Cal command to the ADC12041. During a full calibration, the offset error is measured eight times, averaged and a correction coefficient is created. The offset correction coefficient is stored in an internal offset correction register.

The overall linearity correction is achieved by correcting the internal DAC's capacitor mismatches. Each capacitor is compared eight times against all remaining smaller value capacitors. The errors are averaged out and correction coefficients are created.

Once the converter has been calibrated, an arithmetic logic unit (ALU) uses the offset and linearity correction coefficients to reduce the conversion offset and linearity errors to within guaranteed limits.

#### **AUTO-ZERO CYCLE**

During an auto-zero cycle, the offset is measured only once and a correction coefficient is created and stored in an internal offset register. An auto-zero cycle is initiated by writing an Auto-Zero command to the ADC12041.

#### **DIGITAL INTERFACE**

The digital control signals are  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$  and  $\overline{RDY}$ . Specific timing relationships are associated with the interaction of these signals. Refer to the Digital Timing Diagrams section for detailed timing specifications. The active low RDY signal indicates when a certain event begins and ends. It is recommended that the ADC12041 should only be accessed when the RDY signal is low. It is in this state that the ADC12041 is ready to accept a new command. This will minimize the effect of noise generated by a switching data bus on the ADC. The only exception to this is when the ADC12041 is in the standby mode at which time the RDY is high. The ADC12041 is in the standby mode at power up or when a STANDBY command is issued. A Ful-Cal, Auto-Zero, Reset or Start command will get the ADC12041 out of the standby mode. This may be observed by monitoring the status of the RDY signal. The RDY signal will go low when the ADC12041 leaves the standby mode.

The following describes the state of the digital control signals for each programmed event in both 8-bit and 13-bit mode.  $\overline{\text{RDY}}$  should be low before each command is issued except for the case when the device is in standby mode.

## **FUL-CAL OR AUTO-ZERO COMMAND**

*8-bit mode:* A Ful-Cal or Auto-Zero command must be issued and the BW bit (b<sub>3</sub>) cleared. The active edge of the write pulse on the  $\overline{WR}$  pin will force the  $\overline{RDY}$  signal high. At this time the converter begins executing a full calibration or auto-zero cycle. The  $\overline{RDY}$  signal will automatically go low when the full calibration or auto-zero cycle is done.

13-bit mode: A Ful-Cal or Auto-Zero command must be issued and the BW bit (b<sub>3</sub>) set. The active edge of the write pulse on the  $\overline{WR}$  pin will force the  $\overline{RDY}$  signal high. At this time the converter begins executing a full calibration or auto-zero cycle. The  $\overline{RDY}$  signal will automatically go low when the full calibration or auto-zero cycle is done.

#### STARTING A CONVERSION: START COMMAND

In order to completely describe the events associated with the Start command, both the SYNC-OUT and SYNC-IN modes must be considered.

#### SYNC-OUT/Asynchronous

8-bit mode: A write to the ADC12041 should set the acquisition time, clear the BW and SYNC bit and select the START command in the Configuration register. In order to initiate a conversion, two reads must be performed from the ADC12041. The rising edge of the second read pulse will force the RDY pin high and begin the programmed acquisition time selected by bits b<sub>1</sub> and b<sub>0</sub> of the Configuration register. The SYNC pin will go high indicating that a conversion sequence has begun following the end of the acquisition period. The RDY and SYNC signal will fall low when the conversion is done. At this time new information, such as a new acquisition time and operational command can be written into the Configuration register or it can remain unchanged. Assuming that the START command is in the Configuration register, the previous conversion can be read. The first read places the lower byte of the conversion result contained in the Data register on the data bus. The second read will place the upper byte of the conversion result stored in the Data register on the data bus. The rising edge on the second read pulse will begin another conversion sequence and raise the RDY and SYNC signals appropriately. 13-bit mode: The acquisition time should be set, the BW bit set, the SYNC bit cleared and the START command issued with a write to the ADC12041. In order to initiate a conversion, a single read must be performed from the ADC12041. The rising edge of the read signal will force the RDY signal high and begin the programmed acquisition time selected by bits  $b_1$  and  $b_0$  of the configuration register. The SYNC pin  $\,$ will go high indicating that a conversion sequence has begun following the end of the acquisition period. The RDY and SYNC signal will fall low when the conversion is done. At this time new information, such as a new acquisition time and operational command can be written into the Configuration register or it can remain unchanged. With the START command in the Configuration register, a read from the ADC12041 will place the entire 13-bit conversion result stored in the data register on the data bus. The rising edge of the read pulse will immediately force the  $\overline{\mbox{RDY}}$  output high and begin the programmed acquisition time selected by bits b<sub>1</sub> and b<sub>0</sub> of the configuration register. The SYNC will then go high at the end of the programmed acquisition time.

## Features and Operating Modes (Continued)

SYNC-IN/Synchronous

For the SYNC-IN case, it is assumed that a series of SYNC pulses at the desired sampling rate are applied at the SYNC pin of the ADC12041.

8-bit mode: A write to the ADC12041 should set the SYNC bit, write the START command and clear the BW bit. The programmed acquisition time in bits  $b_1$  and  $b_0$  is a don't care condition in the SYNC-IN mode.

A rising edge on the SYNC pin or the second rising edge of two consecutive reads from the ADC12041 will force the RDY signal high. It is recommended that the action of reading from the ADC12041 (not the rising edge of the SYNC signal) be used to raise the RDY signal. This will ensure that the conversion result is read during the acquisition period of the next conversion cycle, eliminating a read from the ADC12041 while it is performing a conversion. Noise generated by accessing the ADC12041 while it is converting may degrade the conversion result. In the SYNC-IN mode, only the rising edge of the SYNC signal will begin a conversion cycle. The rising edge of the SYNC also ends the acquisition period. The acquisition period begins after the falling edge of the RDY signal. The input is sampled until the rising edge of the SYNC pulse, at which time the signal will be held and conversion begins. The RDY signal will go low when the conversion is done and a new operational command may be written into the Configuration register at this time, if needed. Two consecutive read cycles are required to retrieve the entire 13-bit conversion result from the ADC12041's Data register. The first read will place the lower byte of the conversion result contained in the Data register on the data bus. The second read will place the upper byte of the conversion result stored in the Data register on the data bus. With the START command in the configuration register, the rising edge of the second read pulse will raise the RDY signal high and begin a conversion cycle following a rising edge on the SYNC pin.

13-bit mode: The SYNC bit and the BW bit should be set and the START command issued with a write to the ADC12041. A rising edge on the SYNC pin or on the RD pin will force the RDY signal high. It is recommended that the action of reading from the ADC12041 (not the rising edge of the SYNC signal) be used to raise the  $\overline{\text{RDY}}$  signal. This will ensure that the conversion result is read during the acquisition period of the next conversion cycle, eliminating a read from the ADC12041 while it is performing a conversion. Noise generated by accessing the ADC12041 while it is converting may degrade the conversion result. In the SYNC-IN mode, only the rising edge of the SYNC signal will begin a conversion cycle. The RDY signal will go low when the conversion cycle is done. The acquisition time is controlled by the SYNC signal. The acquisition period begins after the falling edge of the RDY signal. The input is sampled until the rising edge of the SYNC pulse, at which time the signal will be held and conversion begins. The RDY signal will go low when the conversion is done and a new operational command may be written into the Configuration register at this time, if needed. With the START command in the Configuration register, a read from the ADC12041 will place the entire conversion result stored in the Data register on the data bus and the rising edge of the read pulse will force the RDY signal high.

#### STANDBY COMMAND

$\ensuremath{\textit{8-bit}}$  mode: A write to the ADC12041 should clear the BW bit and issue the Standby command.

13-bit mode: A write to the ADC12041 should set the BW bit and issue the Standby command.

#### RESET

The RESET command places the ADC12041 into a ready state and forces the  $\overline{\text{RDY}}$  signal low. The RESET command can be used to interrupt the ADC12041 while it is performing a conversion, full-calibration or auto-zero cycle. It can also be used to get the ADC12041 out of the standby mode.

## **Analog Application Information**

### REFERENCE VOLTAGE

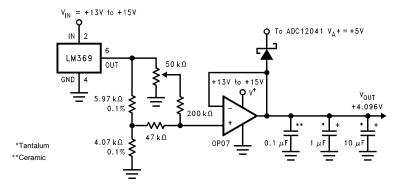

The ADC12041 has two reference inputs,  $V_{REF}^{+}$  and  $V_{REF}^{-}$ . They define the zero to full-scale range of the analog input signals over which 4095 positive and 4096 negative codes exist. The reference inputs can be connected to span the entire supply voltage range ( $V_{REF}^{-} = AGND$ ,  $V_{REF}^{+} = V_{A}^{+}$ ) or they can be connected to different voltages when other input spans are required. The reference inputs of the ADC12041 have transient capacitive switching currents. The voltage sources driving  $V_{REF}^{+}$  and  $V_{REF}^{-}$  must have very low output impedence and noise and must be adequately bypassed. The circuit in *Figure 8* is an example of a very stable reference source.

The ADC12041 can be used in either ratiometric or absolute reference applications. In ratiometric systems, the analog input voltage is proportional to the voltage used for the ADC's reference voltage. This technique relaxes the system reference requirements because the analog input voltage moves with the ADC's reference. The system power supply can be used as the reference voltage by connecting the  $V_{\rm REF}{}^+$  pin to  $V_{\rm A}{}^+$  and the  $V_{\rm REF}{}^-$  pin to AGND. For absolute accuracy, where the analog input voltage varies between very specific voltage limits, a time and temperature stable voltage source can be connected to the reference inputs. Typically, the reference voltage's magnitude will require an initial adjustment to null reference voltage induced full-scale errors.

The reference voltage inputs are not fully differential. The ADC12041 will not generate correct conversions if  $V_{REF}^+-V_{REF}^-$  is below 1V. *Figure 9* shows the allowable relationship between  $V_{REF}^+$  and  $V_{REF}^-$ .

FIGURE 9. V<sub>REF</sub> Operating Range

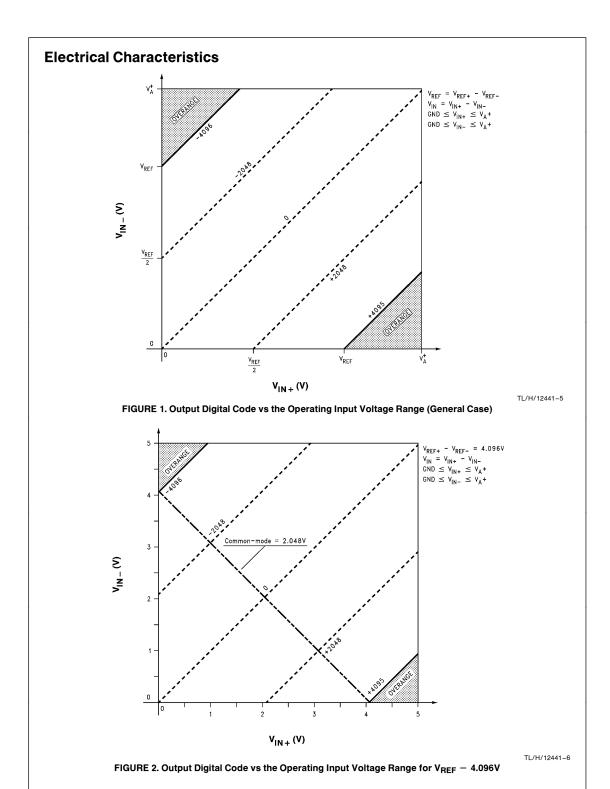

# OUTPUT DIGITAL CODE VERSUS ANALOG INPUT VOLTAGE

The ADC12041's fully differential 12-bit  $+\ \, {\rm sign}\ \, {\rm ADC}\ \, {\rm generates}\ \, {\rm a}\ \, {\rm two}$ 's complement output that is found by using the equation shown below:

Output code =

$$\frac{(V_{IN}^{+} - V_{IN}^{-}) (4096)}{(V_{REF}^{+} - V_{REF}^{-})}$$

Round off the result to the nearest integer value between -

FIGURE 8. Low Drift Extremely Stable Reference Circuit

| Part Number         | Output Voltage<br>Tolerance | Temperature<br>Coefficient |  |  |

|---------------------|-----------------------------|----------------------------|--|--|

| LM4041CI-Adj        | ±0.5%                       | ±100ppm/°C                 |  |  |

| LM4040AI-4.1        | ±0.1%                       | ±100ppm/°C                 |  |  |

| LM9140BYZ-4.1       | ±0.5%                       | ±25ppm/°C                  |  |  |

| LM368Y-5.0          | ±0.1%                       | ±20ppm/°C                  |  |  |

| Circuit of Figure 8 | Adjustable                  | ±2ppm/°C                   |  |  |

## **Analog Application Information (Continued)**

#### INPUT CURRENT

At the start of the acquisition window ( $t_{AcqSYNOUT}$ ) a charging current (due to capacitive switching) flows through the analog input pins (ADCIN+ and ADCIN-). The peak value of this input current will depend on the amplitude and frequency of the input voltage applied, the source impedance and the ADCIN+ and ADCIN- input switch ON resistance of 2500 $\Omega$ .

For low impedance voltage sources (1000  $\leq \Omega$  for 12 MHz operation), the input charging current will decay to a value that will not introduce any conversion errors before the end of the default sample-and-hold (S/H) acquisition time (9 clock cycles). For higher source impedances (1000  $\geq \Omega$  for 12 MHz operation), the S/H acquisition time should be increased to allow the charging current to settle within specified limits. In asynchronous mode, the acquisition time may be increased to 15, 47 or 79 clock cycles. If different acquisition times are needed, the synchronous mode can be used to fully control the acquisition time.

#### **INPUT BYPASS CAPACITANCE**

External capacitors (0.01  $\mu$ F–0.1  $\mu$ F) can be connected between the ADCIN+ and ADCIN- analog input pins and the analog ground to filter any noise caused by inductive pickup associated with long leads.

#### POWER SUPPLY CONSIDERATIONS

Decoupling and bypassing the power supply on a high resolution ADC is an important design task. Noise spikes on the  $V_A{}^+$  (analog supply) or  $V_D{}^+$  (digital supply) can cause conversion errors. The analog comparator used in the ADC will respond to power supply noise and will make erroneous conversion decisions. The ADC is especially sensitive to power supply spikes that occur during the auto-zero or linearity calibration cycles.

The ADC12041 is designed to operate from a single +5V power supply. The separate supply and ground pins for the analog and digital portions of the circuit allow separate external bypassing. To minimize power supply noise and ripple, adequate bypass capacitors should be placed directly between power supply pins and their associated grounds. Both supply pins should be connected to the same supply source. In systems with separate analog and digital supplies, the ADC should be powered from the analog supply. At least a 10  $\mu F$  tantalum electrolytic capacitor in parallel with a 0.1  $\mu\text{F}$  monolithic ceramic capacitor is recommended for bypassing each power supply. The key consideration for these capacitors is to have low series resistance and inductance. The capacitors should be placed as close as physically possible to the supply and ground pins with the smaller capacitor closer to the device. The capacitors also should have the shortest possible leads in order to minimize series lead inductance. Surface mount chip capacitors are optimal in this respect and should be used when possible.

When the power supply regulator is not local on the board, adequate bypassing (a high value electrolytic capacitor) should be placed at the power entry point. The value of the capacitor depends on the total supply current of the circuits

on the PC board. All supply currents should be supplied by the capacitor instead of being drawn from the external supply lines, while the external supply charges the capacitor at a steady rate.

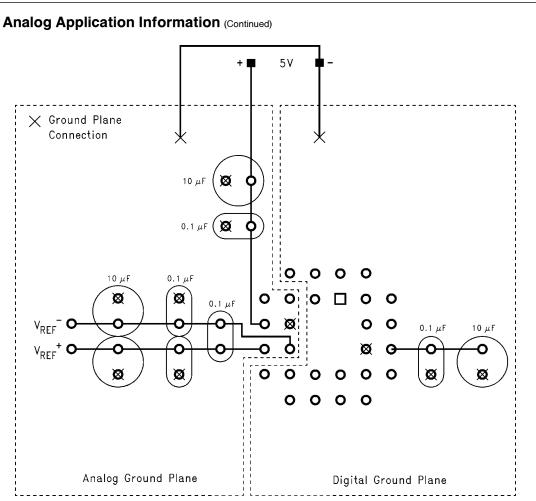

The ADC has two  $V_D^+$  and DGND pins. It is recommended to use a 0.1  $\mu F$  plus a 10  $\mu F$  capacitor between pin 21( $V_D^+$ ) and 22 (DGND) the SSOP and PLCC package. The layout diagram in *Figure 10* shows the recommended placement for the supply bypass capacitors.

# PC BOARD LAYOUT AND GROUNDING CONSIDERATIONS

To get the best possible performance from the ADC12041, the printed circuit boards should have separate analog and digital ground planes. The reason for using two ground planes is to prevent digital and analog ground currents from sharing the same path until they reach a very low impedance power supply point. This will prevent noisy digital switching currents from being injected into the analog ground.

Figure 10 illustrates a favorable layout for ground planes, power supply and reference input bypass capacitors. It shows a layout using a 28-pin PLCC socket and through-hole assembly. A similar approach should be used for the SSOP package.

The analog ground plane should encompass the area under the analog pins and any other analog components such as the reference circuit, input amplifiers, signal conditioning circuits, and analog signal traces.

The digital ground plane should encompass the area under the digital circuits and the digital input/output pins of the ADC12041. Having a continuous digital ground plane under the data and clock traces is very important. This reduces the overshoot/undershoot and high frequency ringing on these lines that can be capacitively coupled to analog circuitry sections through stray capacitances.

The AGND and DGND in the ADC12041 are not internally connected together. They should be connected together on the PC board right at the chip. This will provide the shortest return path for the signals being exchanged between the internal analog and digital sections of the ADC.

It is also a good design practice to have power plane layers in the PC board. This will improve the supply bypassing (an effective distributed capacitance between power and ground plane layers) and voltage drops on the supply lines. However, power planes are not as essential as ground planes are for satisfactory performance. If power planes are used, they should be separated into two planes and the area and connections should follow the same guidelines as mentioned for the ground planes. Each power plane should be laid out over its associated ground planes, avoiding any overlap between power and ground planes of different types. When the power planes are not used, it is recommended to use separate supply traces for the V<sub>A</sub><sup>+</sup> and  $\ensuremath{\text{V}_{\text{D}}}^{+}$  pins from a low impedance supply point (the regulator output or the power entry point to the PC board). This will help ensure that the noisy digital supply does not corrupt the analog supply.

FIGURE 10. Top View of Printed Circuit Board for a 28-Pin PLCC ADC12041

TL/H/12441-45

When measuring AC input signals, any crosstalk between analog input lines and the reference lines (ADCIN $\pm$ ,  $V_{\text{REF}}^{\pm}$ ) should be minimized. Crosstalk is minimized by reducing any stray capacitance between the lines. This can be done by increasing the clearance between traces, keeping the traces as short as possible, shielding traces from each other by placing them on different sides of the AGND plane, or running AGND traces between them.

Figure 10 also shows the reference input bypass capacitors. Here the reference inputs are considered to be differential. The performance improves by having a 0.1  $\mu$ F capacitor

between the V<sub>REF</sub><sup>+</sup> and V<sub>REF</sub><sup>-</sup>, and by bypassing in a manner similar to that described for the supply pins. When a single ended reference is used, V<sub>REF</sub><sup>-</sup> is connected to AGND and only two capacitors are used between V<sub>REF</sub><sup>+</sup> and V<sub>REF</sub><sup>-</sup> (0.1  $\mu\text{F}$  + 10  $\mu\text{F}$ ). It is recommended to directly connect the AGND side of these capacitors to the V<sub>REF</sub><sup>-</sup> instead of connecting V<sub>REF</sub><sup>-</sup> and the ground sides of the capacitors separately to the ground planes. This provides a significantly lower-impedance connection when using surface mount technology.

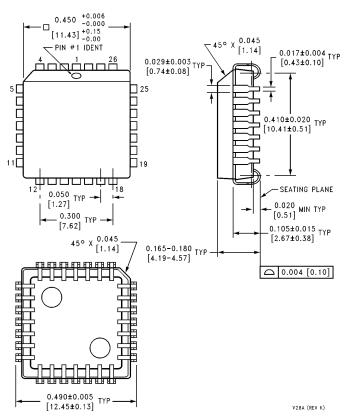

## Physical Dimensions inches (millimeters)

28-Lead Molded Plastic Leaded Chip Carrier Order Number ADC12041CIV NS Package Number V28A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Europe

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 180-530 85 85

English Tel: +49 (0) 180-532 78 82

Français Tel: +49 (0) 180-532 93 58

Italiano Tel: +49 (0) 180-542 416 80

**National Semiconductor** National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd.

Tel: 81-043-299-2308

Fax: 81-043-299-2408