# National Semiconductor

### 54FCT574 Octal D-Type Flip-Flop with TRI-STATE<sup>®</sup> Outputs

#### **General Description**

The 'FCT574 is an octal flip-flop with a buffered common Clock (CP) and a buffered common Output Enable ( $\overline{OE}$ ). The information presented to the D inputs is stored in the flip-flops on the LOW-to-HIGH Clock (CP) transition.

The device is functionally identical to the 'FCT374 except for the pinouts.

- Useful as input or output port for microprocessors

- Functionally identical to 'FCT374

- TRI-STATE outputs for bus-oriented applications

- Output sink capability of 32 mA, source capability of 12 mA

- TTL input and output level compatible

- CMOS power consumption

- Standard Microcircuit Drawing (SMD) 5962-8951301

#### **Features**

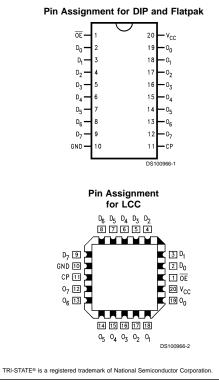

Inputs and outputs on opposite sides of package allowing easy interface with microprocessors

#### **Ordering Code**

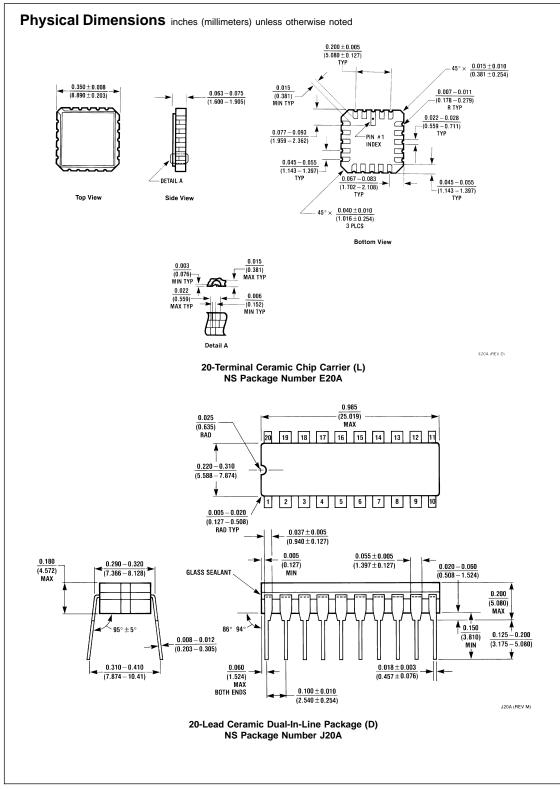

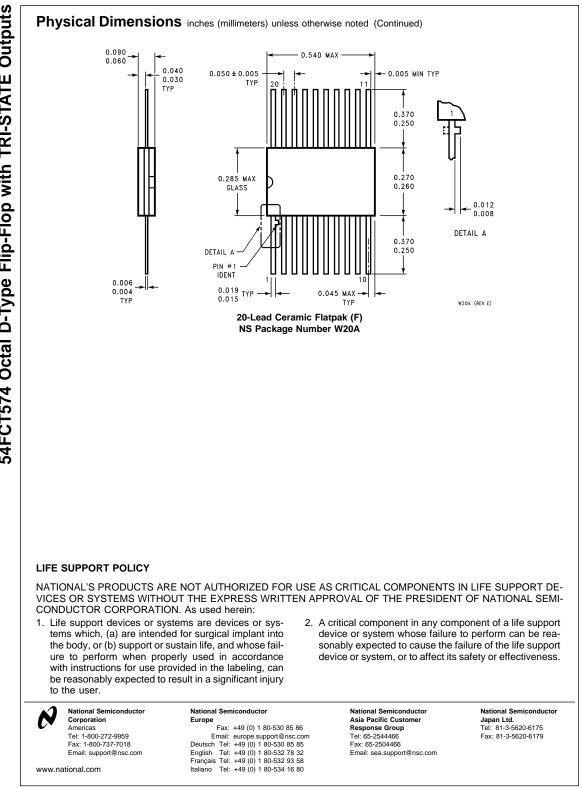

| Military Package Number |      | Package Description                           |  |

|-------------------------|------|-----------------------------------------------|--|

| 54FCT574DMQB            | J20A | 20-Lead Ceramic Dual-In-Line                  |  |

| 54FCT574FMQB            | W20A | 20-Lead Cerpack                               |  |

| 54FCT574LMQB            | E20A | 20-Lead Ceramic Leadless Chip Carrier, Type C |  |

### **Connection Diagrams**

#### Pin Descriptions

| Pin Description                |                         |

|--------------------------------|-------------------------|

| Names                          |                         |

| D <sub>0</sub> -D <sub>7</sub> | Data Inputs             |

| CP                             | Clock Pulse Input       |

|                                | (Active Rising Edge)    |

| OE                             | TRI-STATE Output Enable |

|                                | Input (Active LOW)      |

| 0 <sub>0</sub> -0 <sub>7</sub> | TRI-STATE Outputs       |

54FCT574 Octal D-Type Flip-Flop with TRI-STATE Outputs

© 1998 National Semiconductor Corporation DS100966

#### **Functional Description**

•

The 'FCT574 consists of eight edge-triggered flip-flops with individual D-type inputs and TRI-STATE true outputs. The buffered clock and buffered Output Enable are common to all flip-flops. The eight flip-flops will store the state of their individual D inputs that meet the setup and hold times requirements on the LOW-to-HIGH Clock (CP) transition. With the Output Enable  $(\overline{OE})$  LOW, the contents of the eight flip-flops are available at the outputs. When  $\overline{OE}$  is HIGH, the outputs are in a high impedance state. Operation of the  $\overline{\text{OE}}$  input does not affect the state of the flip-flops.

#### **Function Table**

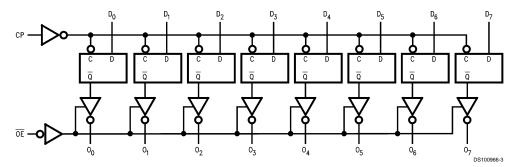

Logic Diagram

|   | Inputs |        | Internal | Outputs | Function |      |

|---|--------|--------|----------|---------|----------|------|

| C | DE     | СР     | D        | Q       | 0        |      |

|   | Н      | H or L | L        | NC      | Z        | Hold |

| Inputs |        | Internal | Outputs | Function |                   |

|--------|--------|----------|---------|----------|-------------------|

| OE     | СР     | D        | Q       | 0        |                   |

| н      | H or L | Н        | NC      | Z        | Hold              |

| н      | Ν      | L        | L       | Z        | Load              |

| н      | Ν      | н        | н       | Z        | Load              |

| L      | Ν      | L        | L       | L        | Data Available    |

| L      | Ν      | н        | н       | н        | Data Available    |

| L      | H or L | L        | NC      | NC       | No Change in Data |

| L      | H or L | н        | NC      | NC       | No Change in Data |

H = HIGH Voltage Level L = LOW Voltage Level

X = Immaterial Z = High Impedance N = LOW-to-HIGH Transition NC = No Change

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

#### Absolute Maximum Ratings (Note 1)

.

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Storage Temperature                             | −65°C to +150°C               |

|-------------------------------------------------|-------------------------------|

| Ambient Temperature under Bias                  | –55°C to +125°C               |

| Junction Temperature under Bias                 |                               |

| Ceramic                                         | –55°C to +175°C               |

| V <sub>CC</sub> Pin Potential to Ground Pin     | -0.5V to +7.0V                |

| Input Voltage (Note 2)                          | -0.5V to +7.0V                |

| Input Current (Note 2)                          | -30 mA to +5.0 mA             |

| Voltage Applied to Any Output in                |                               |

| the Disabled or Power-Off State                 | -0.5V to 5.5V                 |

| in the HIGH State                               | –0.5V to V <sub>CC</sub>      |

| Current Applied to Output<br>in LOW State (Max) | twice the rated $I_{OL}$ (mA) |

**DC Electrical Characteristics**

DC Latchup Source Current Over Voltage Latchup (I/O)

# Recommended Operating Conditions

| Free Air Ambient Temperature                                                                                               |                 |

|----------------------------------------------------------------------------------------------------------------------------|-----------------|

| Military                                                                                                                   | –55°C to +125°C |

| Supply Voltage                                                                                                             |                 |

| Military                                                                                                                   | +4.5V to +5.5V  |

| Note 1: Absolute maximum ratings are value<br>be damaged or have its useful life impaired. F<br>conditions is not implied. |                 |

–500 mA

10V

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

#### Symbol Parameter FCT574 Units $V_{cc}$ Conditions Min Max $V_{IH}$ Input HIGH Voltage 2.0 V Recognized HIGH Signal VIL Input LOW Voltage 0.8 V Recognized LOW Signal $I_{IN} = -18 \text{ mA}$ $V_{CD}$ Input Clamp Diode Voltage -1.2 V Min Output HIGH 54FCT V Min $I_{OH} = -300 \ \mu A$ V<sub>OH</sub> 4.3 Voltage 54FCT V $I_{OH} = -12 \text{ mA}$ 2.4 Min Min $I_{OL} = 300 \ \mu A$ 54FCT V Vol 0.2 Output LOW Voltage 54FCT $I_{OL} = 32mA$ 0.5 V Min V<sub>IN</sub> = 2.7V (Note 3) Input HIGH Current 5 μA Max $I_{\rm H}$ $V_{IN} = V_{CC}$ 5 μA $V_{IN} = 0.5V$ (Note 3) $I_{\rm IL}$ Input LOW Current -5 Max $V_{IN} = 0.0V$ -5 $V_{OUT} = 2.7V; \overline{OE} = 2.0V$ Output Leakage Current 0 – 5.5V I<sub>OZH</sub> 10 μΑ $V_{OUT} = 0.5V; \overline{OE} = 2.0V$ Output Leakage Current -10 μA 0 – 5.5V I<sub>OZL</sub> Output Short-Circuit Current -60 mΑ Max $V_{OUT} = 0.0V$ los $V_{IN} = 0.2V$ or $V_{IN} = 5.3V$ , $f_I =$ Power Supply Current 1.5 mΑ Max Iccq 0MHz Power Supply Current 2.0 mΑ Max $V_{IN} = 3.4V$ $\Delta I_{CC}$ $V_{I} = V_{CC} - 2.1V$ or $V_{IN} = GND$ , $f_{CP}$ Additional 6.0 mΑ Max I<sub>CCT</sub> = 10MHz, Outputs open, $\overline{OE}$ = I<sub>CC</sub>/Input GND, one bit toggling at $f_1 = 5MHz$ , 50% duty cycle $V_{I} = 5.3V \text{ or } V_{CC} = 0.2V, f_{CP} =$ 5.5 mΑ Max 10MHz, Outputs open, $\overline{OE} = GND$ , one bit toggling at $f_I = 5MHz, 50\%$ duty cycle Outputs Open, $\overline{OE}$ = GND, One bit Dynamic I<sub>CC</sub> No Load 0.40 mA/ Max ICCD MHz toggling, 50% duty cycle, $V_{IN}$ = 5.3V or V<sub>IN</sub> = 0.2V

Note 3: Guaranteed, but not tested.

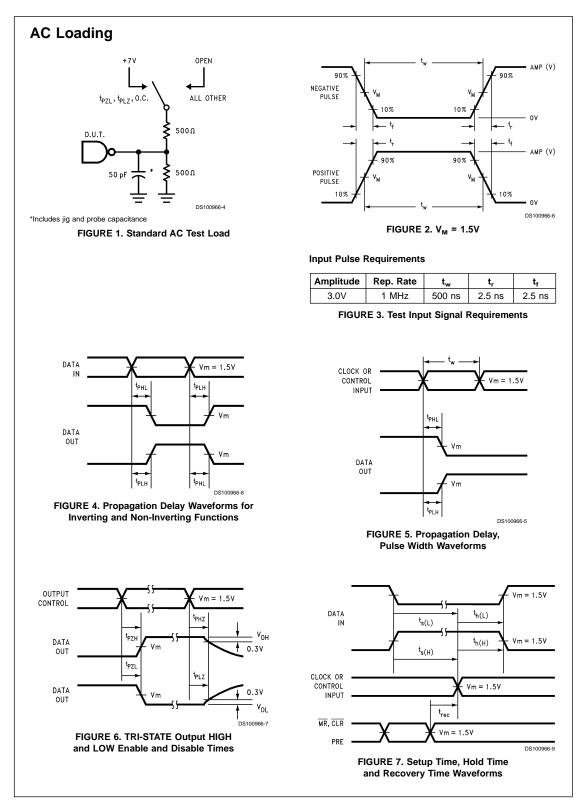

|                  |                      | 54F                                    | СТ    |     | Fig.     |

|------------------|----------------------|----------------------------------------|-------|-----|----------|

| Symbol           | Parameter            | $T_A = -55^{\circ}C$<br>$V_{CC} = 4.5$ | Units | No. |          |

|                  |                      | C <sub>L</sub> = 50 pF                 |       |     |          |

|                  |                      | Min                                    | Max   | 1   |          |

| t <sub>PLH</sub> | Propagation Delay    | 2.0                                    | 11.0  | ns  | Figure 4 |

| t <sub>PHL</sub> | CP to O <sub>n</sub> | 2.0                                    | 11.0  |     |          |

| t <sub>PZH</sub> | Output Enable Time   | 1.5                                    | 14.0  | ns  | Figure 6 |

| t <sub>PZL</sub> |                      | 1.5                                    | 14.0  |     |          |

| t <sub>PHZ</sub> | Output Disable Time  | 1.5                                    | 8.0   | ns  | Figure 6 |

| t <sub>PLZ</sub> |                      | 1.5                                    | 8.0   |     |          |

# AC Operating Requirements

| Symbol             | Parameter                   | $T_{A} = -55^{\circ}$ $V_{CC} = 4.5$ | $54FCT$ $T_{A} = -55^{\circ}C \text{ to } +125^{\circ}C$ $V_{CC} = 4.5V \text{ to } 5.5V$ $C_{L} = 50 \text{ pF}$ |    | Fig.<br>No. |

|--------------------|-----------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|----|-------------|

|                    |                             | Min                                  | Max                                                                                                               |    |             |

| t <sub>s</sub> (H) | Setup Time, HIGH            | 3.5                                  |                                                                                                                   | ns | Figure 7    |

| t <sub>s</sub> (L) | or LOW D <sub>n</sub> to CP | 3.5                                  |                                                                                                                   |    |             |

| t <sub>h</sub> (H) | Hold Time, HIGH             | 2.0                                  |                                                                                                                   | ns | Figure 7    |

| t <sub>h</sub> (L) | or LOW D <sub>n</sub> to CP | 2.0                                  |                                                                                                                   |    |             |

| t <sub>w</sub> (H) | Pulse Width, CP,            | 7.0                                  |                                                                                                                   | ns | Figure 5    |

| t <sub>w</sub> (L) | HIGH or LOW                 | 7.0                                  |                                                                                                                   |    |             |

## Capacitance

.

| Symbol                    | Parameter          | Тур | Units | Conditions<br>T <sub>A</sub> = 25°C |

|---------------------------|--------------------|-----|-------|-------------------------------------|

| C <sub>IN</sub>           | Input Capacitance  | 5.0 | pF    | $V_{CC} = 0V$                       |

| C <sub>OUT</sub> (Note 4) | Output Capacitance | 9.0 | pF    | $V_{CC} = 5.0V$                     |

Note 4: C<sub>OUT</sub> is measured at frequency f = 1 MHz, per MIL-STD-883B, Method 3012.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.