IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 42 NO. 6, DECEMBER 1995

1823

## Ion Induced Charge Collection and SEU Sensitivity of Emitter Coupled Logic (ECL) Devices

R. Koga, W.R. Crain, S.J. Hansel, K.B. Crawford, J.F. Kirshman, S.D. Pinkerton, S.H. Penzin, S.C. Moss, and M. Maher\*

The Aerospace Corporation, El Segundo CA 90009

\* National Semiconductor, South Portland ME 04106

#### Abstract

This paper presents single event upset (SEU) and latchup test results for selected Emitter Coupled Logic (ECL) microcircuits, including several types of low capacity SRAMs and other memory devices. The high speed of ECL memory devices makes them attractive for use in space applications. However, the emitter coupled transistor design increases susceptibility to radiation induced functional errors, especially SEU, because the transistors are not saturated, unlike the transistors in a CMOS device. Charge collection at the sensitive nodes in ECL memory elements differs accordingly. These differences are responsible, in part, for the heightened SEU vulnerability of ECL memory devices relative to their CMOS counterparts.

#### Introduction

Emitter Coupled Logic (ECL) devices have been used in numerous electronic systems in the past twenty or more years [1-3]. Because the gate delay (on the order of 1 ns) is significantly shorter for ECL devices than for devices from the CMOS or TTL logic families, ECL microcircuits are often utilized in the so-called "front end" of electronic systems, where input signals need to be processed rapidly. ECL memory devices are also used in computer cache memory systems, again because of their high speed.

The high speed of ECL microcircuits makes them attractive to space system engineers. However, before their continued use in critical space applications can be fully endorsed, a more thorough characterization is needed of the susceptibility of these devices to single event effects, such as single event upset (SEU) and single event latchup (SEL).

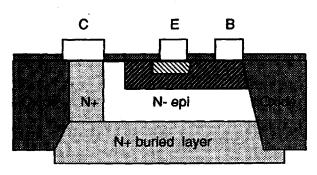

P substrate

Fig. 1. Schematic of ECL Transistor Structure

Because the coupled transistors in an ECL memory cell remain in a non-saturated state continuously, the charge collection characteristics and SEU susceptibility of these devices differs from those fabricated in CMOS or TTL technology. For example, in ECL devices prompt charge collection at the sensitive nodes appears to be more important than drift charge collection in causing upset.

In the following, we present SEU and latchup results relevant to the use of ECL devices in space, and discuss the implications of these findings for our current understanding of upset mechanisms in this family of devices.

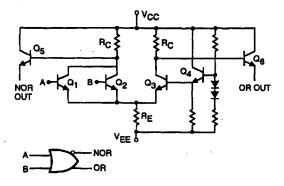

Fig. 2. ECL OR/NOR Gate

### ECL Devices.

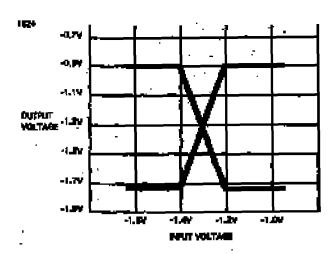

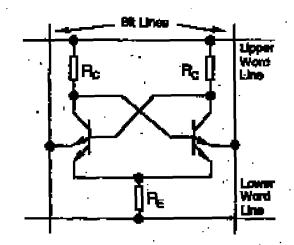

The transistors (see Fig. 1) in an ECL gate are not fully saturated, unlike the transistors in devices from other logic families, such as TTL and CMOS. The output of an ECL gate (e.g., see Fig. 2) exhibits minimum high levels and maximum low levels of about -1V and -1.6V, respectively. The typical relationship between the input and output logic levels is shown in Fig. 3. About 1 ns (or less) is required for transition from one logical state to another. Thus, an overall operational speed of several gigahertz can be achieved by logic systems that utilize devices fabricated in mature ECL technology.

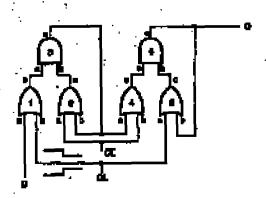

High speed memory elements can be developed using combinations of ECL "AND" and "OR" gates. For example, Fig. 4 shows a master-slave flip-flop constructed from six ECL gates. ECL technology has also been used to fabricate fast SRAMs. Each SRAM cell consists of two matching active transistors, as shown in Fig. 5. Unlike the collectors of the Q2 and Q3 transistors in the circuit for a logic gate (see Fig. 2), the collectors in ECL SRAM cells are tied to the bases of the opposite transistors (Fig. 5), forming bistable

0018-9499/95\$04.00 © 1995 IEEE

Fig. 3. Typical BCL Transfer Chemosedates

logic elements, Recense meliter translater in extensive, a stable state consists of one translator (the "eat" inscribing a much larger cornect than the other (eletinoph hoth are forward larged). The logic pointing is changed if the other translator carries a higher translator in changed if the other translator carries a higher translator. The complementary precesses of requiring from and weighing to the call on both accomplished transplato his literal vector amplifies while the call in long read, and to a set of driven while the call in long read, and to a set of driven while the call in long read, and to a set

The periodes in the memory call are placed adjacent to the translation in cater to make the geometry and the capacitation between various layers, such as the boundary between the collector and the home [4]. In these to-collect, "isophrape" devices, it is possible to achieve a sphereometric transition of the memory state.

Possesse the employing of the experiences in ECL submicircula are forward binard, and therefore transitions from legic "high" to "low" and view squar take piace very first, power consumption (bursts, host generation) tooks to be greater for ECL submoducing than for those fainfusted to other technologies, such as TTL or CMOS, The capacity of ECL SHAMS (up to test of thousands of address longitions) furnished tooks to be markler than that of SHAMs from other legic families.

Fig. 4. Proctional Logic of Mining-Shaw D Prip-Prop

Pic. 5. Translation in Methody Physical of BCL SEAM.

Table 1 shows the BCL devices selected for hardistics, with beavy icon and partials (as described in the following matters). The 100331 Sig-Stops and the 100341 shift replace belong to National Sensionalizator's F100K300 methodagy family, and layer a flatters aim of about 2.5 p.m. The thickness of the spilinger is an the cuber of 1 micross (see Fig. 2). The Microsola layer is an the cuber of 1 micross (see Fig. 2). The Microsola line deliver belongs to the FCL MK technology flowing and has a sensemble layer flatters sink. Because this device type does not involvemently elements, it was tasted for intelline only. The Cypsus Sensionalizator, Refine, and MBC SEAles, show the tasted 1K 2.4 supporty configurations, making comparisons of SEU page-path-bity sensemble chapter.

Table 1. Original SCI. Test Deliber.

| Davice Type | Mt.  | Russian          | - Date Oods |

|-------------|------|------------------|-------------|

| 100881      | N/SG | Manus Chies D RF | 9720        |

| 190841      | MBC  | Shift Register   | 9250        |

| MC10H115    | MOT  | Line Receiver    | 6930        |

| CY100E474   | CYP  | BPANA (4K x 4)   | 9010        |

| MENHORAA    | ۴W   | SRAM (1K proj    | 6602        |

| µPB10474    | NEO  | 59444 (1K ± 4)   | 6721 -      |

# Single Event Effects Totting and Obstructions

The test techniques utilized in the present study of RCL devices an similar to those typically used to but released which fabricated in other technologies, with two exceptions. First, because ECL devices nonnears a rather large current and therefore the device temperature rises thereby, especially in a vacuum controperate, the temperature of the jest devices tracia to be controlled; both thermoelectric and water could apparatusts were used for this purpose. Second, ECL legic levels (-1.0 volts for "high" and -1.6 volts for "how") need to be translated to either ChEDS or TTL levels in order to sate

1825

Fig. 6. SEU Test Results for NSC 100331 D Flip-Flop

standard laboratory equipment. SEU testing of ECL devices has seldom been performed in the past, mainly because of these two difficulties [5].

The test devices for the present study (see Table 1) were irradiated at the Lawrence Berkeley Laboratory 88-inch cyclotron facility using the following ion beams: xenon (603 MeV), krypton (380 MeV), copper (290 MeV), argon (180 MeV), neon (90 MeV), nitrogen (67 MeV), and protons (35 and 55 MeV). The corresponding linear energy transfer (LET) values for the non-hydrogen beams were: 63, 41, 30, 15, 5.6, and 3 MeV/(mg/cm<sup>2</sup>).

A brief description of the testing procedure follows (detailed information on beam delivery and data collection techniques can be found in [6,7]). While running the test, the single event upset rate was kept between 1 and 3 events per second. This made the dead time caused by resetting the device under test (DUT) negligible compared to the total test time. After a sufficient number of errors had been recorded, the test was stopped and the total fluence of particles and total number of errors were recorded. The device error probability or cross-section,  $\sigma$ , was then calculated from the expression:

$$\sigma = \frac{N \sec(\theta)}{F}$$

where N and F are the number of errors and beam fluence, respectively, and  $\theta$  is the incident angle of the beam, measured with respect to the chip-surface normal. (The cross-section provides an index of gross susceptibility to SEU.) During the SEU tests, the DUT power supply current was closely monitored to detect any occurrence of latchup.

When the incident ion is very energetic and the sensitive region is a very thin, flat volume (resembling a pancake), the charge deposited varies with  $\sec(\theta)$  for a wide range of incident angles. In this case, the effective LET is [L  $\sec(\theta)$ ], where L is the LET of the incident ion. However, for many microcircuits, and ECL devices in particular, the geometry of the sensitive region cannot be assumed to be flat. Therefore, only small incident angles were utilized in the present study.

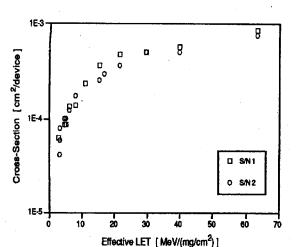

SEU test results for the National Semiconductor 100331 and 100341 flip-flop devices are shown in Figs. 6 and 7,

Fig. 7. SEU Test Results for NSC 100341 Shift Register

respectively. The 100331 contains three flip-flops in a single package, whereas the 100341 consists of eight flip-flops, organized as an 8-bit shift register. The SEU cross-sections shown in Figs. 6 and 7 are aggregate measures of the SEU susceptibility of all the flip-flops in a single package (either three or eight, respectively).

As illustrated in Figs. 6 and 7, the cross-section curves for 100331 and 100341 differ in overall shape, although the saturation values are similar (just under 10<sup>-3</sup>). For 100331 the cross-section values increase gradually with LET, whereas for 100341 a sharp "knee" is observed at about 4 MeV/(mg/cm<sup>2</sup>). The gradual slope of the curves for 100331 suggests that the memory elements in this device have different critical charges for SEU; in contrast, the charge thresholds for the memory elements in 100341 appear to be nearly uniform. This disparity may be due to the use of master-slave flip-flops in 100331 but not in 100341 (in a master-slave flip-flop, the master and slave can have different critical charges [8]).

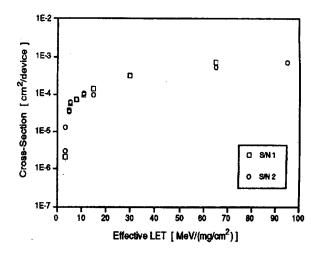

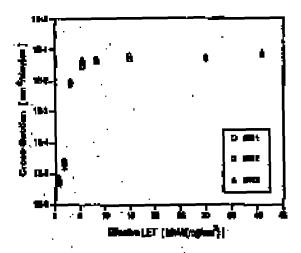

Figures 8 through 10 show the heavy ion SEU test results for the NEC μPB10474, Fujitsu MBM10474A, and Cypress Semiconductor CY100E474 1K x 4 SRAMs, respectively. MBM10474A was also tested for proton induced SEU using 35 and 55 MeV protons, as shown in Fig. 11.

The cross-section curves for both  $\mu PB10474$  (Fig. 8) and MBM10474A (Fig. 9) display a relatively sharp "knee" below an effective LET of about 3 MeV/(mg/cm<sup>2</sup>), which suggests that the critical charge for SEU is similar for most memory elements in these devices. In contrast, for CY100E474 (Fig. 10) the cross-section gradually increases, suggesting non-uniformity in the charge thresholds of the memory elements. (This could be due to the memory elements having different sizes or geometries; however, this possibility was not investigated here.)

The LET thresholds of the  $\mu PB10474$  and MBM10474A SRAMs, but not the CY100E474, are lower than those of typical commercial CMOS and NMOS RAMs (e.g., see [9,10]). Overall, the saturation cross-sections for ECL SRAMs appear to be comparable to those of many CMOS SRAMs, although  $\sigma_{sat}$  is highly variable in both technologies.

1874

Fig. 8. SHU Tool Rombs the NBC pPH10474 SRAM

Rg. 9. SHU Test Regula for Politics MEMBOCIAA STRAIN

Pig. 10. SHU Test Results for Cypters CY900B474 SHAM

No. 11. Protes 200 Test Regits for MBM16474A SRAM

The name of the upon was constant in detail; and is sugmentable box for MBM10474A. The polarity of the bit spaces approved to be executely sublaced: 47%  $0 \rightarrow 1$  around all 3%  $1 \rightarrow 0$  count, at above in Table 3 (that obtained with Er inner. The should of a polarity effect inflicate first the translation in the manuary elements (see Fig. 5) here very similar according than [11].

Single ion induced or little-bit space have been reported for SRANIs thirdented to other testinologies (9,12,13). In the present investigation (again taking MBhitle474A, as an example), the frequency and distribution of multiple-bit spaces was analyzed by irradiating the set devices with Er. Co. Ar. No, and N kins normal to the chip surface, and seconting the market of memory order space by each ion order. The percentage of scalingle various single bit space is above in Table 3. Nortes that no many date two bits were speet by any

Table 2. Upont Rt Potents for MERIOGIAA

| Rune         | Upoets | Uports    |     |       |

|--------------|--------|-----------|-----|-------|

|              | 884    | 0-11      | 1-0 | Total |

| <del>-</del> | · 1    | <b>46</b> | 45  | 107   |

| ż            | 1      | 45        | 68  | 109   |

|              | . 2    | 58        | 44  | 100   |

| 4            | 2      | 40        | 61  | 101   |

| ø ·          | 3      | 80        | 51  | 101   |

| 4            | 9      | 42        | 160 | 102   |

|              |        | 47%       | 65% | in!   |

ion, and those upset bits appeared to be physically adjacent. Furthermore, for multiple-bit upsets, the two upset bits belonged to different logical words — that is, there were no single-word multiple-bit upsets [13]. No "stuck bits" were observed either (in some CMOS and NMOS SRAMs a sizable number of bits become stuck during ion irradiation in either logical "0" or logical "1" [14]).

Table 3. Multiple-Bit Upsets for MBM10474A

| lon | % of Upsets Caused by Single Ion Hit |        |          |  |

|-----|--------------------------------------|--------|----------|--|

|     | 1 bit                                | 2 bits | > 2 bits |  |

| Kr  | 80                                   | 20     | 0        |  |

| Cu  | 78                                   | 22     | 0        |  |

| Ar  | 80                                   | 20     | 0        |  |

| Ne  | 98                                   | 2      | 0        |  |

| N   | 100                                  | 0      | 0        |  |

The Motorola MC10H115 line receiver was tested for latchup only. Neither this device nor any of the aforementioned devices latched-up during testing. The calculated upper limit of the latchup cross-section is thus about 1 x 10-7 cm<sup>2</sup>.

## Discussion: SEU Mechanisms

The mechanisms responsible for SEU in bistable ECL memory elements are described below. The high SEU susceptibility (i.e., low SEU thresholds) of ECL devices in comparison to CMOS and NMOS devices stems, in part, from the large base-to-collector current amplification factor  $(\beta)$  and low capacitance of the transistors; a small voltage swing can easily alter the bistable elements in these devices.

As shown in Fig. 5, each ECL cell is constructed from two similar transistors. The vulnerable nodes are located at the bases of the transistors, as well as at the collector of the "off" transistor. Because the transistors are not in the saturated state while biased at a low voltage ( $V_{CE} = \sim 1V$ ), the depletion regions are thin. The large base-to-collector current amplification factor of the transistors ( $\beta = \sim 120$ ) greatly magnifies relatively small charges ( $\sim 9$  fC in the thin sensitive regions) at the collector of the "off" transistor, causing an alteration of the logic state of the other (coupled) transistor. Because ECL circuits have a very small parasitic capacitance by design, there is no significant time delay. The combined change in the states of the transistors alters the logical state of the memory bit, resulting in SEU.

This model is supported by additional experiments in which an MBM10474A memory cell was exposed to a pulsed laser beam. (A description of the use of laser beams in SEU research can be found in [15].) Because the spot size of the laser beam is on the order of one micron, it was possible to expose one section of the cell at a time. Results indicate that the "off" transistor was 5 times more sensitive than its counterpart (sensitivity is measured by the laser power required to induce upset). That is, the memory cell could be upset by exposing

the "on" transistor at 5 times the energy required to cause upset at the "off" transistor. This further supports the observation that charge collection at the base of the "on" transistor can lead to memory upset.

Thick SiO<sub>2</sub> surrounds the silicon island that makes up a transistor (see Fig. 1). Within a transistor, the collector occupies the entire lateral area and the base occupies about two-thirds of this area. The sensitive region is therefore a very large portion of the entire area. The large cross-section of ECL devices arises from the fact that the sensitive regions occupy a large fraction of the transistor.

For devices fabricated in CMOS and other technologies diffusion charge collection can affect sensitive regions at a distance from the ion impact site as the column of charge expands to a wider area, thereby resulting in multiple-bit upsets potentially involving several bits at a time. However, as shown in Table 3, only single and double bit errors were observed for the MBM10474A SRAM, which suggests that diffusion charge collection is relatively ineffective at producing SEU in this device type; instead, it appears that prompt charge collection is the primary cause of upset.

The sensitive regions of the 100331 and 100341 flip-flop devices are located at various transistors within the gates (see Fig. 4). Some transistors, such as Q4 in Fig. 2, are more sensitive than others due to their relationships with other transistors in the microcircuit.

Table 4 shows the cross-section per bit for the test devices, obtained by dividing the saturation cross-section by the total number of bits. The geometrical area of a transistor base for the 100341 shift register is approximately  $140\,\mu^2$ . Therefore, the cross-section for a single memory element is about 7 times as large as the sensitive area of a single transistor.

Table 4. Sensitivity of ECL Memory Elements

| Device Type        | Cross-Section per Bit (μ <sup>2</sup> ) |  |

|--------------------|-----------------------------------------|--|

| CY100E474 SRAM     | 370                                     |  |

| MBM10474 SRAM      | 730                                     |  |

| μPB10474 SRAM      | 2100                                    |  |

| 100341 Shift Reg.  | 1000                                    |  |

| 100331 D Flip-Flop | 2670                                    |  |

The high resistivity p-substrate is located below the buried layer. Regardless of the resistivity, no p-n-p-n parasitic SCR circuits are activated because the p-substrate is tied to the negative supply voltage; this, possibly, is also the reason that all the test devices were immune to latchup.

### Conclusion

The present study has demonstrated that ECL devices are very vulnerable to SEU. ECL SRAMs display a lower LET threshold (~3 MeV/(mg/cm²)) than most comparable CMOS devices. The ECL devices appear to be sensitive to prompt charge collection only, which limits effective charge collection

فكار

to a much region map the top impact site; they are transfers less encopylish to contrible-bit opens than many communish. CMDS RAMS, Norm of the test devices hatched-up.

The above scinits represent only a preliminary study of BCL devices, diffriend excepts is required to most theoretisty of this family of devices. Because their devices have been (and will constant to be) used in space afactronics systems, is in committed to determine the probable spect rate of each device, to understand the machiners, of SEU, and to excess effective SEU originally probable (and to excess effective).

## Arimowiodements

We would like to thank our Acceptant collecture V.T. Hunt, B.M. Johnson, M. Lalie, and R.L. Walter for providing sectoded scaletone, and the smill of the LBL 98-inch cyclosese facility for beam delivery.

### Beforenen

- Minker, R.H., W.E. Owens, and P.W.J. Verhalbank, "Rully Compressed Farker-Coupled Logic: Minkesting the Deprotects of Conventional ECL," <u>IEEE J. Solid.</u> <u>Step Circuits</u>, <u>3C-8</u>, 362-367, 1973.

- Giock, H. and V. Burber, "An HCL 1908-Compatible 1624 x 4 Bit RAM with 15 or Access Time," IEEE L. Sciid-State Caralle, SC-14, 190-134, 1979.

- Bragt, R., W. Pertsch, and H.V. Wench, "A Fligh-Speed BCL 108E Compatible 64 x 4 Bit BAM with 6 as Access Time," IEEE J. Solid-State Chemics, 20:-13, 306-310, 1988.

- Dhaka, V.A., J.E. Minechingho, and W.K. Owens, "Subminespected Relater-coupled Logic Gate Circuit Using Inspirate II," <u>IKER Internal of Solid State Circuits</u>, <u>8C-8</u>, 363-372, 1973.

- Shoge, M., E. John, M. Gimgow, M. Prespensate, B. Smith, and R. Koga, "Stagle Breat Upper at Gigabasta Prespensates," IHRR Trans. Nucl. Sci., 41, 2252-2253, 1994.

- Kopa, R., W.A. Kolastocki, and S. Immusto, "Heavy Ion. Induced Upiets in Secriconductor Devices," <u>INSE Trans.</u> <u>Nucl. Sci., NS-32</u>, 159-162, 1983.

- Roga, R. and S.D. Finkenter, "Advantage of the I.Bl. 38-inch Cycletron for SEP Studies," <u>Proc. European</u>

Conference on Radiculus and in Effects of Devices and

Section (RADICS 91), 586-590, 1991.

- Kolasionki, W.A., E. Koga, and D.L. Chrustin, "Heavy lea Enduced Single Event Upsets in a Dipolar Logic Device," <u>IEEE Toms. Nucl. Sci.</u>, <u>NS-30</u>, 4470-4474, 1983.

- Kopa, R., W.B. Caste, K.B. Crawford, D.D. Lee, S.D. Holmston, B.K. YI., and R. Chitry, "On the Suitability of Non-hundred High Density SPAMs for Space Applications," IEEE Trans. Nucl. Sci., 34, 1367-1513, 1991.

- [f] Malles, R.G., E.P. Kay, and R. Kogs, "SHJ Results from the Advanced Photovoltale and Electrosistes Experiments (APHX) Satellies," IEEE Torse, Nucl. Sci., 42, in press, 1995.

- Koga, R., J.F. Kinthasan, S.D. Pinkyrien, S.J. Hansel, K.B. Chawfool, and W.R. Curb, "Sometiphous Hamburing of Resistive Land SEAMS," Third Research Confession on Resistion and its Effects on Devices and Systems (EADSCS 97), in pages, 1993.

- Cabraril, T.L., D.L. Chang, J.L. West, P.R. Missest, and W.R. Wilson, "Managements of SEU Throubolds and Cross Sections at Fixed Incident Augins," IEEE Trans. Nact. Sci., 128-34, 1916-1921, 1967.

- Kegn, R., S.D. Perkeston, T.J. Liu, and K.B. Carachell, "Single-word Multiple-left Uppers in Static Rambon Actom Devices," <u>IEEE Trans. Phys. Sci.</u>, 48, 1941-1946, 1993.

- Privay, C., T. Carriero, J. Bremoter, and T.R. Cichero, "Connectatingtion of Single Rand Forces (SEE) in 1M-bit SRAMs from Single Ion," IEEE Trans. Nucl. Sci., 41, 2235-2239, 1994.

- Koga, R., S.D. Pinkorton, S.C. Most, D.C. Mayer, S. Lallamon(kyo, S.J. Hansel, K.B. Corwinel, and W.R. Cola, "Observation of Single Event Uponts in Analog Devices," IEEE Trans. Nucl. Sci., 40, 1838-1844/1993.