# Stability Analysis of Current Feedback Amplifiers

Rea Schmid

May 1995

#### Introduction

High frequency current-feedback amplifiers (CFA) are finding a wide acceptance in more complicated applications from dc to high bandwidths. Often the applications involve amplifying signals in simple resistive networks for which the data sheets provide adequate information to complete the task. Too often the CFA application involves amplifying signals that have a complex load or parasitic components at the external nodes that creates stability problems.

This application note covers the discussion of using Bode analysis to determine the gain and phase margin while including external parameters. It discusses how to determine the input buffer gain and its effect on the closed-loop gain. A more appropriate mathematical model is developed for a clearer understanding of the poles and zeros of the CFA amplifier. Finally a summary of how parasitic components influence the frequency and time domain response.

## **Stability Review**

Bode analysis is one of the more useful methods for determining stability for an amplifier. When an engineer selects a unity gain stable voltage-feedback amplifier, the internal compensation of the amplifier is transparent to the end user of the amplifier. If the VFA is connected to a complex load and it alters the phase margin then often the part will oscillate or peak the Adding external compensation frequency response. networks with capacitors and resistors will generally stabilize the amplifier. Of course, this is done at the expense of additional components and cost. With a CFA amplifier, stabilization is accomplished by adjusting the feedback resistor. Thus one component, the feedback resistor, controls the phase and gain margin of the amplifier. The most practical way to determine stability of current-feedback amplifier is by Bode plots generated from computer simulations.

## **Review of Bode Analysis**

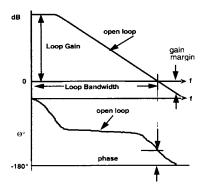

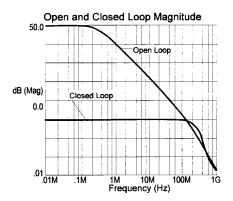

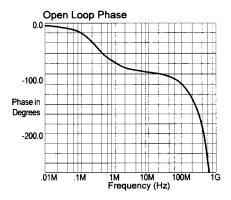

Bode analysis is the easiest predictor for determining amplifier stability. The measurement is based upon creating an open-loop magnitude and phase plot to arrive at the closed-loop stability, indicators of gain and phase margin. The phase margin is derived by finding the intersection of the closed-loop unity gain frequency response curve to the open-loop response curve as shown in Figure 1. At this frequency the phase is read from the phase plot. This value is subtracted from 180° to arrive at the desired phase margin. Similarly the frequency at 180° is used to determine the gain margin in the magnitude plot shown in Figure 1. A recommended phase margin is at least 60° with gain margin of 12dB.

Figure 1: Bode Analysis

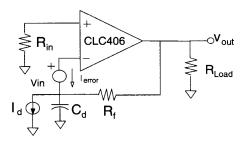

## A Better Model

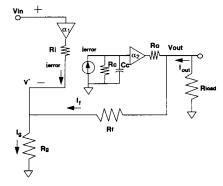

A practical voltage follower has output resistance which creates a need for a more comprehensive model. That model is developed in Figure 2 and allows us to mathematically model the effects of critical parameters. For example, if an application consists of amplifying continuous waveforms, then this model allows us to determine gain-accuracy, stability, impedances, frequency response and output swing for a particular load requirement.

Figure 2 Practical Model

## **Mathematical Justification**

Our first task is to derive a transfer function by nodal analysis for an infinite load condition.

$$\begin{split} I_{error} &= I_g - I_f \\ I_{error} &= \frac{V^-}{R_g} - \frac{V_{out} - V^-}{R_f} \\ V_{out} &= I_{error} (\alpha_2 \cdot Z(s)) - I_f \cdot R_o \\ V^- &= \alpha_1 \cdot V_{in} - I_{error} \cdot Ri \end{split}$$

Equation 1

After combining and eliminating the terms V and Ierror in Equation 1, a transfer function is derived by dividing Vout by Vin as seen in Equation 2.

$$\frac{V_{out}}{V_{in}} = \frac{\alpha_{1} \cdot A_{v} \left(1 + \frac{R_{o}}{A_{v} \cdot \alpha_{2} \cdot Z(s)}\right)}{R_{f} + R_{i} \cdot A_{v} + R_{o} \left(1 + \frac{R_{i}}{R_{g}}\right)}$$

$$1 + \cdots + \frac{R_{f}}{\alpha_{2} \cdot Z(s)}$$

$$A_{v} = 1 + \frac{R_{f}}{R_{g}}$$

# **Equation 2**

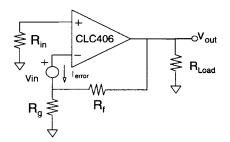

The Z(s) in Equation 2 is the open-loop transimpedance gain and its value is derived by dividing the output voltage Vout by the current through Vin, shown in the schematic of Figure 3. The terms " $\alpha_1$  and  $\alpha_2$ " are the buffer gains while Ro is the open loop output resistance.

Although this equation has many variables, most of the terms are reduced by the open-loop response Z(s). The gain bandwidth independance for CFA is still true when Z(s) approaches infinity and the gain Av remains small. The denominator term, "Ri" is multiplied by closed-loop gain Av, and is small with a range of 16 to  $490\Omega$  for current feedback amplifiers. For a CLC406 Ri is  $60\Omega$ . The series output resistance Ro in the denominator is scaled by the ratio of the Ri and gain setting resistor Rg. While the Ro in the numerator is divided by the gain Av,  $\alpha_2$ , and Z(s). Typically, the open-loop Ro will vary from 5 to 25 ohms.

The closed-loop output resistance approaches zero at dc, and is a function of the open-loop Z(s) frequency response. This is an important point when matching an output impedance by a back matching resistor. Typically back matching consists of placing a resistor that matches the characteristic impedance of a coaxial cable or specific devices input impedance, such as 50 ohms.

The denominator term:

$$\frac{\alpha_2 \cdot Z(s)}{R_f + R_i \cdot A_v + R_o \left(1 + \frac{R_i}{R_g}\right)}$$

is referred to as the loop gain, and its closed-loop bandwidth is determined by denominator:

$$R_f + R_i \cdot A_v + R_o \left( 1 + \frac{R_i}{R_g} \right)$$

As you increase gain Av, you need to decrease Rf to maintain the largest possible -3dB bandwidth. Manufacturers of CFA amplifiers specify a gain of 1 or 2 at a recommended Rf in the data sheet. For large gain changes the designer can select a value that best fits the desired new closed-loop gain Av. This maximizes the bandwidth and maintains the same stability based upon maintaining the same ratio used to select the original Rf in the datasheet. For small changes in gain, using the recommended Rf while changing the gain by Rg is acceptable unless stability becomes an issue.

As Rf decreases, a fundamental limit is reached by the approximate parallel combination of Rload and Rf. At this new load, the output voltage limit is set by the output current capability or the maximum output voltage swing into a no load condition. An alternative is to increase Rload or increase Rf. A bandwidth reduction in the ratio of the open-loop to closed-loop will result. This ratio decrease results in secondary effects such as a decrease in distortion, noise, gain accuracy, etc. Therefore, small changes are acceptable and large ratio changes are not recommended.

Figure 3: Simulation Method

## **Open Loop Transimpedance Plot**

At first it may seem strange to determine Z(s) by placing the voltage source in the inverting node of Figure 3. But this simplifies the simulation steps and has advantages for deriving the stability plot for investigating loads at the output pin.

The circuit in Figure 3 simulates the open-loop transimpedance response Plot 1, while looking at 2 conditions:

- 1. Infinite load.

- 2.  $100\Omega$  load.

This plot helps explain the accuracy of our spice model and its effects for a practical application. Later this transimpedance gain Z(s) is normalized to an open-loop magnitude function.

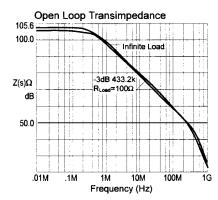

Plot 1: Open Loop Transimpedance

The open loop transimpedance gain Plot 1 has axis in dB ohms versus frequency, and shows an approximate

$$\label{eq:zero} \text{first order roll off function} \quad Z(s) = \frac{R_c}{sR_cC_c+1} \quad \text{that}$$

includes secondary poles at the higher frequencies. To derive the value of Rc you take the inverse log of the axis:

$$10^{Z(s)/20}$$

at low frequencies while the 3dB bandwidth gives Cc by the following:

$$\frac{1}{2\pi R_c f_{-3dB}}$$

Equation 3:

$$T(s) = \frac{Z(s) \cdot A_v}{R_f + R_i \cdot A_v}$$

where Z(s) is:

$$\frac{V_{out}}{I(V_{in})}$$

and I is the current in Vin.

If we plot this transfer function for a CLC406 at an Av=1 with an Rf=768 $\Omega$  and Rg= $\infty$ , the magnitude and phase information is shown in Plot 2 and 3. The output Ro term is ignored since Ri is low. The gain and phase margin is now available for determining the stability of our CLC406 Current Feedback Amplifier.

With Plot 2, you find the unity gain crossover frequency point. This frequency point determines the phase of the amplifier on Plot 3 and it is subtracted from a 180° to derive the Phase Margin. The value at zero dB is at a frequency of 108MHz and infers a phase margin of 62°. The gain margin is measured from the -180° phase point and is the difference between the open-loop gain

intersection and the 0dB gain line in Plot 2, which is approximately 12dB. From control theory, these values are the indicators for optimum amplifier performance, although many designers will set the phase margin to 45° and 9dB of gain margin. This results in 3dB of frequency peaking or in the time domain signal preshoot and undershoot. Yet, we will still have a difference in the unity gain -3dB frequency response of 220MHz in simulation versus 200MHz in an actual part. The explanation for the difference will be explained later.

Plot 2: Open and Closed Loop Magnitude

Plot 3: Open Loop Phase

# Including Z(s)

The transfer function derived in Equation 2 has little meaning when looking at the poles and zeros for the amplifier without including transimpedance gain Z(s). At first let's substitute the first order pole of Z(s) into Equation 2. After some mathematical manipulation we discover a pole plus a zero as shown in Equation 3. This is not intuitively obvious until you think about the amplifier's independent and dependent source and the inclusion of Ro to produce this zero.

$$\frac{V_{out}}{V_{in}} = \frac{\alpha_1 \cdot A_v \left(1 + \frac{R_o}{A_v \cdot R_c}\right)}{1 + \frac{R_t}{R_c}} \cdot \frac{1 + s \left(\frac{R_o \cdot C_c}{A_v}\right)}{1 + s \left(R_t \|R_c \cdot C_c\right)}$$

**Equation 3**

Where the term:

$$R_t \cong R_f + A_v \cdot R_i + \left(1 + \frac{R_i}{R_g}\right) \cdot R_o'$$

$s = j\omega$ , and  $\omega = 2\pi f$ .

At s=0 the open-loop Rc reduces the terms in Equation 3 to the gain Av times  $a_{_{\! 1}}$ . The zero in the numerator is an order of magnitude higher than the pole in denominator, while the pole has a new value of Rt times Cc where Rc >> Rt. Yet, we have not considered the effects of "Parasites" and their influences upon the stability of the amplifier.

## **External Parasites and Complex Loads**

Connecting multiple circuits that have complex values (capacitance or inductance) at the nodes often results in stability issues for all types of amplifiers. Recall the bandwidth of the CLC406 model indicated its -3dB bandwidth to be higher than the measured unity-gain frequency. This increase bandwidth is largely the result of parasitic components of the package and evaluation board layout. This adds additional zeros and poles to the equation that peaks the frequency response. Adding complex loads to various pins of our model causes stability questions that are probably more easily answered through simulation analysis rather than mathematical analysis.

If a capacitance is in parallel with the load resistance, a decrease in phase margin will result. Capacitance in parallel with Rg decreases the loop gain, while capacitance in parallel with Rf increases the loop gain. All of these effects are seen in simulations for an amplifier.

A common designed circuit is a transimpedance amplifier. The circuit in Figure 4 shows replacing the Rg resistor with the equivalent photo-diode capacitance to simulate closed-loop stability for the CFA. Using the earilier spice simulation method to generate a Bode plot that determines the stability of the design. Adding an independent current source in parallel with the diode capacitance provides a method to simulate the transimpedance gain versus frequency.

Figure 4: Photo Diode Analysis

## Summary

Models are available from Comlinear Corporation for modeling many of the important parameters for high speed op amps. Application note OA-18 "Simulation SPICE Models For Comlinear's Op Amps", details the schematics and parameters that are modeled. Ask for Comlinear's latest spice model diskette.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup> R. Schmid, "Technique targets board parasites.", EDN April 14, 1994 page 147.

This page intentionally left blank.

## **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

## Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## National Semiconductor Corporation 1111 West Bardin Road

Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

#### National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 E-mail: europe.support@nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58

Italiano Tel: (+49) 0-180-534 16 80

# National Semiconductor Hong Kong Ltd.

13th Floor, Straight Block Ocean Centre, 5 Canton Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600

Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.