## **Current Feedback Amplifier Loop Gain Analysis and Performance Enhancement**

Michael Steffes

January 1993

With the introduction of commercially available amplifiers using the current feedback topology by Comlinear Corporation in the early 1980s, previously unattainable gains and bandwidths in a DC coupled amplifier became easily available to any design engineer. The basic achievement realized by the current feedback topology is to de-couple the signal gain from the loop gain part of the overall transfer function. Commonly available voltage feedback amplifiers offer a signal gain expression that appears identically in the loop gain expression, yielding a tight coupling between the desired gain and the resulting bandwidth. This historically has led to the gain-bandwidth product idea for voltage feedback amplifiers. The current feedback topology transcends this limitation to offer a signal bandwidth that is largely independent of gain. This application note develops the current feedback transfer function with an eye towards manipulating the loop gain.

### **Current Feedback Amplifier Transfer Function Development**

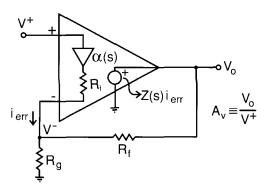

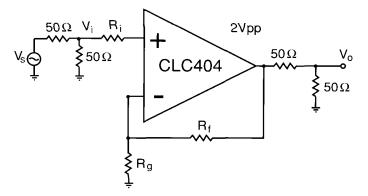

The equivalent amplifier circuit of Figure 1 will be used to develop the non-inverting transfer function for the current feedback topology. The current feedback topology is also perfectly suitable for inverting mode operation, especially inverting summing applications. The non-inverting transfer function will be developed, in preference to the inverting, since the inverting transfer function development is a subset of the non-inverting.

Figure 1: Current Feedback Amplifier Internal Elements

The amplifier's non-inverting input presents a high impedance to the input voltage,  $V^+$ , so as to not load the driving source. Any voltage appearing at the input node is passed through an open loop, unity gain, buffer that has a frequency dependent gain,  $\alpha(s)$ .  $\alpha(s)$  is very neatly equal to 1 at DC (typically .996 or higher, but always < 1.00) and typically has a -3dB point beyond 500 MHz. The output of the buffer ideally presents a  $0\Omega$  output impedance at the inverting input,  $V^-$ . It actually shows a frequency dependent impedance,  $Z_i$ , that is relatively low at DC and increases inductively at high frequencies. For this development, we will only consider that  $Z_i$  is a small valued resistive impedance,  $R_i$ .

The intent of the buffer is to simultaneously force the inverting node voltage to follow the non-inverting input voltage while also providing a low impedance path for an error current to flow. Any small signal error current flowing in the inverting node,  $i_{err}$ , is passed through the buffer to a high transimpedance gain stage and on to the output pin as a voltage. This transimpedance gain, Z(s), senses  $i_{err}$  and generates an output voltage proportional to it. Z(s) has a very high DC value, a dominant low frequency pole, and higher order poles. When the loop is closed, the action of the feedback loop is to drive  $i_{err}$  to zero much like a voltage feedback amplifier will drive the delta voltage across its inputs to zero. Z(s) ideally transforms the error current into a zero ohm output impedance voltage source.

Figure 2 steps through the transfer function development including the effect of  $R_{\rm i}$ . This analysis neglects the impact of a finite output impedance from Z(s) to the output, output loading interactions with that output impedance, and the effect of stray capacitance shunting  $R_{\rm a}$ .

Start by summing currents at the V<sup>-</sup>node of Figure 1

$$i_{err} + \frac{V_0 - V^-}{R_f} = \frac{V^-}{R_g}$$

Eq. 1

We also know that,

$$V^- = \alpha$$

(s)  $V^+ - i_{err} R_i$

and,  $i_{err} Z_{(s)} = V_o$  then,  $i_{err} = \frac{V_o}{Z_{(s)}}$

Multiply equation 1 through by  $R_f$  and isolate V

$$R_f i_{err} + V_o = V^- \left(1 + \frac{R_f}{R_g}\right)$$

Now substitute in for ierr and V from above

$$\frac{R_{f} V_{o}}{Z_{(s)}} + V_{o} = \left(\alpha(s) V^{+} - \frac{V_{o} R_{i}}{Z_{(s)}}\right) \left(1 + \frac{R_{f}}{R_{g}}\right)$$

Gather  $V_o$  terms and solve for  $V_o / V^+$

$$\frac{V_{o}}{V^{+}} = \frac{\alpha(s) \left(1 + \frac{R_{f}}{R_{g}}\right)}{1 + \frac{R_{f} + R_{i} (1 + R_{f}/R_{g})}{Z_{(s)}}}$$

Eq. 2

Figure 2. Current Feedback Amplifier Transfer Function

It is instructive to consider the separate parts of Equation 2 separately.

$\alpha(s)$  —> Frequency dependent buffer gain. Normally considered = 1

$1+R_{_{\rm I}}/$   $R_{_{\rm S}}$  —> Desired signal gain. Identical to voltage feedback non-inverting amplifier gain.

$$\frac{R_f + R_i \left(1 + \frac{R_f}{R_g}\right)}{Z_{(s)}} = \frac{1}{\text{Loop Gain}}$$

Hence, Loop Gain (LG) =

$$\frac{Z_{(s)}}{R_f + R_i \left(1 + \frac{R_f}{R_g}\right)}$$

Eq. 3

The loop gain expression is of particular interest here. If Z(s), the forward transimpedance, is much greater than  $R_1 + R_2(1+R_2/R_3)$ , the feedback transimpedance, (as it is at low frequencies) then this term goes to zero leaving just the numerator terms for the low frequency transfer function. As frequency increases, Z(s) rolls off to eventually equal the feedback transimpedance expression. Beyond this point, at higher frequencies, this term increases in value rolling off the overall closed loop response.

The key thing to note is that the elements external to the amplifier that determine the loop gain, and hence the closed loop frequency response, do not exactly equal the desired signal gain expression in the transfer function numerator. The desired signal gain expression has been de-coupled from the feedback expression in the loop gain.

If the inverting input impedance were zero, the loop gain would depend externally only on the feedback resistor value. Even with small R, the feedback resistor dominantly sets the loop gain and every current feedback amplifier has a recommended R, for which Z(s) has been optimized. As the desired signal gain becomes very high, the R(1+R/R2) term in the feedback transimpedance can come to dominate, pushing the amplifier back into a gain bandwidth type operation.

#### **Understanding the Loop Gain**

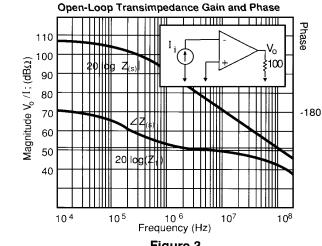

It is very useful, and commonly done for voltage feedback amplifiers, to look at the loop gain graphically. Figure 3 shows this for the CLC400, a low gain part offering DC to 200MHz performance. What has been graphed is 20\*log(IZ(s)I), the forward transimpedance gain, along with its phase, and 20 log(Zt). This Z, is the feedback transimpedance,  $R_i + R_i(1 + R_i/R_a)$ , and where it crosses the forward transimpedance curve is the frequency at which the loop gain has dropped to 1. Note that the forward transimpedance phase starts out with a 180° phase shift, indicating a signal inversion through the part, and could have plotted as continuing to 360° or, as shown, going to zero. Using these axis allows a direct reading of the phase margin at unity gain crossover.

As with any negative feedback amplifier, the key determinant of the closed loop frequency response is the phase margin at unity gain crossover. If the phase has shifted completely around to 360°, or dropped to zero on the axis used above when the loop gain has decreased to 1, unity gain crossover - (where the 20 log(Z) line intersects the 20  $\log(/Z(s)/)$  curve), the denominator in the closed loop expression will become (1-1), or infinity (For the axis used above, the closed loop expression

(Eq.2) would have a 1-1/LG in the denominator. The form developed as Equation 2 accounted for the inversion with the sign convention for  $i_{err}$  and  $V_{a}$ ).

Figure 3

It is critical for stable amplifier operation to maintain adequate phase margin at the unity gain crossover frequency. The feedback transimpedance that is plotted in Figure 3 is R,+R(1+R,/R<sub>a</sub>) evaluated at the specifications setup point for the CLC400. This yields:

$$\begin{array}{ll} R_f = 250\Omega & \text{then} \\ A_v \equiv 1 + \frac{R_f}{R_g} = 2 & Z_t = 250\Omega + 50\Omega \ (2) = 350\Omega \\ Z_i \simeq 50\Omega & \text{20 log } (350\Omega) = 50.9 \ dB \end{array}$$

Looking at the unity gain crossover near 100MHz, we see somewhere in the neighborhood of a 60° phase margin. This is Comlinear's targeted phase margin at the gain and R, used to specify any particular current feedback part. This phase margin, for simple 2 pole Z(s), yields a maximally flat Butterworth filter shape for the closed loop amplifier response (Q=.707). Note that the design targets reasonable flatness over a wide range of process tolerances and temperatures. This typically yields a nominal part that is somewhat overcompensated (phase margin > 60°) at room temperature.

Note that the closed loop bandwidth will only equal the open loop unity gain crossover frequency for 90° phase margins (single pole forward gain response). As the open loop phase margin decreases from 90°, with the impact of higher frequency poles in the forward transimpedance gain, the closed loop poles move off the negative real axis (in the s-plane) peaking the response up and extending the bandwidth. The actual bandwidth achieved by Comlinear's amplifiers is considerably beyond the unity gain crossover frequency due to these open loop phase effects.

#### Controlling the Loop Gain

One of the key insights provided by the loop gain plot is what happens when Z, is changed. Decreasing Z, (dropping the horizontal line of  $20 \log(Z_1)$ ), will extend the unity gain crossover frequency but will sacrifice phase margin. This is commonly seen in current feedback amplifiers when an erroneously low R, value is used yielding an extremely peaked frequency response. In fact a very reliable oscillator can be generated with any current feedback amplifier by using R,=0 in a unity gain configuration. Conversely, increasing Z. (raising the horizontal line of 20  $log(Z_i)$  will drop the unity gain crossover frequency and increase phase margin. Increasing R, is in fact a very effective means of overcompensating a current feedback amplifier. Increasing R, will decrease the closed loop bandwidth and/or decrease peaking in the frequency response.

# Computing $\mathbf{Z}_t$ for the design point used in setting the specifications for any particular current feedback part indicates an optimum targeted feedback transimpedance under any condition.

In design, the internal Z(s) has been set up to yield a maximally flat closed loop response with the gain and Rf used to develop the performance specifications. If we then try to hold the same feedback transimpedance under different gain conditions, an option not possible with voltage feedback topologies, this optimum unity gain crossover for the open loop response can be maintained.

If we designate this optimum feedback transimpedance as  $Z_i^{\star}$ ,

we would like to hold  $R_1+R_1(1+R/R_g)=Z_1^*$  (where  $R_1$  and  $1+R_1/R_g$  are those values shown at the top of the parts performance specifications.)

Substituting  $A_v=1+R_v/R_g$ , we get,  $R_v=Z_v^*-R_vA_v$  Eq. 4 (where  $R_v$  is a new value to be used at a gain other than the design point.)

This is a design equation for holding optimum unity gain crossover. Having computed R, to hold  $Z_t = Z_t^*$  $R_a = R/(A_t - 1)$  Eq.5

#### The Benefits of Controlling Z

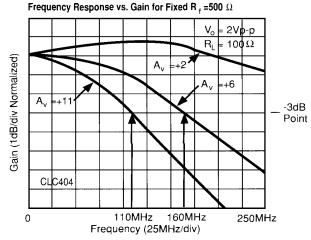

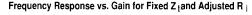

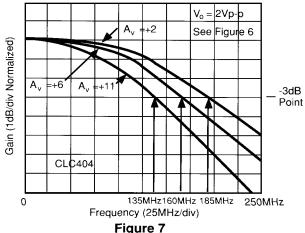

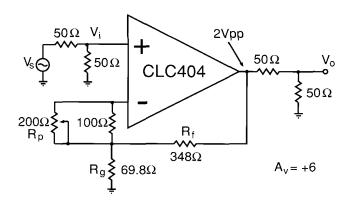

As an example of adjusting  $R_i$  to hold a constant  $Z_i$  as the desired signal gain is changed, consider a CLC404 at gains of +2, +6 and +11. Figure 4 shows test results over these gains for a fixed  $R_i$ - very similar to how the CLC404 data sheet plots were generated.

Using the CLC404 design and specifications points (see Appendix I)

$A_{v} = +6$

$R_f = 500 \Omega$

$R = 30 \Omega$

$Z_{i}^{*} = 500 + 30^{*}6 = 680 \Omega$

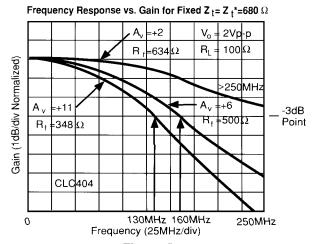

Figure 5 shows the same part operated with  $R_{\rm p}$  adjusted as indicated by Equation 4.  $R_{\rm g}$  in both cases is set using Equation 5.

Figure 4

Figure 5

The results of Figure 5 vs. Figure 4 show that adjusting R, does indeed hold a more constant frequency response over gain than a simple fixed R,. The low gain response has flattened out while the high gain response has been extended.

The remaining variability in frequency response can be attributed to 2nd order effects that have not yet been considered. As described in Application Note OA-15, parasitic capacitance shunting the gain setting resistor,  $R_{\rm g}$ , will introduce a response zero for non-inverting gain operation. This zero location can be easily located by substituting  $R_{\rm g}IIC_{\rm g}$  into the numerator part of the transfer function, Equation 2. This yields a zero at  $1/(R_{\rm f}IIR_{\rm g})C_{\rm g}$  in radians. This effect would not be observed in inverting mode operation yielding a much more consistent response over gains, especially with  $R_{\rm f}$  adjusted as shown above.

If we assume equal parasitic capacitances on the two inputs, we can cancel this zero by introducing a series impedance into the non-inverting input that equals  $R_{\rm l} I R_{\rm g}$ . Figure 6 shows the test circuit and table of values used

to test this for the same CLC404 used above. Note that we must include the equivalent source impedance of the source matching and termination resistors in setting the series resistor into the non-inverting node, (25  $\Omega$  here). Note that the table shows actual standard values used, rather than the exact calculated values.

$$R_f = 680 - A_v(30)$$

$R_g = R_f/(A_v - 1)$

$R_i = (R_f || R_g) - 25\Omega$

$A_v || R_f || R_g || R_i$

$+2 || 634 || 634 || 287 ||$

A<sub>v</sub> R<sub>f</sub> R<sub>g</sub> R<sub>i</sub> +2 634 634 287 +6 500 100 56.2 +11 348 34 6

Figure 6

Figure 7 shows the measured frequency responses under the conditions tabulated in Figure 6.

Clearly, adding R<sub>i</sub> has brought the low gain response to be much more consistent with the higher gains. Little effect was observed by adding R<sub>i</sub> at gains of 6 and 11. Generally, adding R<sub>i</sub> is particularly effective at flattening out the frequency response for higher gain parts, which are designed using high value of feedback resistors, when they are operated at lower gains.

An alternative to adding  $R_i$  is simply to continue to increase  $R_i$  until the loop gain is overcompensated enough to cancel the zero. This is increasingly ineffective as the resistor values get larger but was developed empirically for the CLC414 and CLC415 quad amplifiers (Refer to those data sheets for details). An alternative approach with those parts would be to adjust  $R_i$  using the data from Appendix I and then add an R as described above.

Note that Equation 3 will predict negative R, values as the desired gain exceeds Z,\*/R,. From a loop gain standpoint, this is exactly correct. However, additional concerns (particularly distortion and output current limits) will come in to limit the applicable range of gains for Equation 3. Generally, the total loading on the amplifiers should not be allowed to drop below 65 ohms. This is the actual load in parallel with R,+R, for the non-inverting configuration. For a 100 ohm load, this limits the minimum  $R_i + R_a$  to about 200  $\Omega$ . Lower values can be used if R, is greater. For inverting mode, which has exactly the same loop gain expression as non-inverting, R, alone appears in parallel with R, as an additional load. This would limit R, to a minimum of 200  $\Omega$  in inverting mode operation. This does not, of course, limit the amplifier's maximum gain. When a minimum R, has been reached, R<sub>a</sub> can continue to decrease, yielding higher gains, with a gain bandwidth characteristic eventually developing as the  $R_i$  (1+ $R_i/R_g$ ) part of  $Z_i$  comes to dominate.

#### **Special Considerations for Variable Supply Current**

The inverting input impedance,  $R_i$ , is essentially the output impedance of parallel/series combinations of emitter followers for most Comlinear amplifiers. Thus,  $R_i$  is some fraction or integer multiple of  $V_t/I_c$ , where  $V_t=kT/q$  and  $I_c$  is the bias current in those transistors. For lower power parts, and parts with adjustable supply currents,  $R_i$  can get very large, as  $I_c$  decreases quickly putting the parts into a gain bandwidth type operation. Appendix I shows the nominal design point  $I_c$ , along with a room temperature  $R_i$ , and, for the adjustable supply current,  $I_{cc}$ . Anything that adjusts the total quiescent supply current from its nominal design point, changing power supply voltages, using the bias adjust pins on some parts, etc., will scale the  $I_c$  listed in Appendix I in direct proportion to  $I_{cc}$ .

#### **Additional Loop Gain Control Applications**

Recognizing that the inverting input impedance provides an opportunity to adjust the loop gain, without having any impact on the signal gain, we can add a resistor inside the loop that can act as an independent frequency response compensation element. This is very useful if a fine control over the frequency response shape is desired.

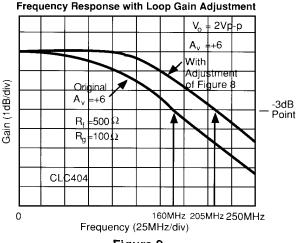

Using the same CLC404 used in the earlier tests (a part that is nominally overcompensated as shown by the rolloff at its gain of +6 condition in Figure 4), the circuit of Figure 8 shows an adjustment technique for the frequency response. Since we are intentionally adding  $R_i$  to the feedback transimpedance expression,  $Z_i$ , it is recommended to approximately set  $R_i$  to yield  $Z_i^{\star}$  when the

adjustment to R<sub>i</sub> is at midrange. This will yield a lower R<sub>i</sub> as shown in Figure 8. Figure 9 shows the original gain of +6 response of Figure 4, along with the response achieved with the circuit of Figure 8 with R adjusted to yielded maximally flat frequency response. This circuit shows a ± .1dB gain flatness to beyond 100 MHz.

Figure 8: Adjustable Frequency Response

Figure 9

In inverting applications there is oftentimes a conflict between the required gain setting resistors from an input impedance and signal gain standpoint, and what the amplifier would like to see from a loop gain phase margin standpoint. In a similar fashion to voltage feedback, in this case, an additional resistor to ground on the inverting input can be used to tune the loop gain independently of the inverting signal gain requirements. The drawback of this, is that, like voltage feedback, this increases the noise gain for the non-inverting input voltage noise.

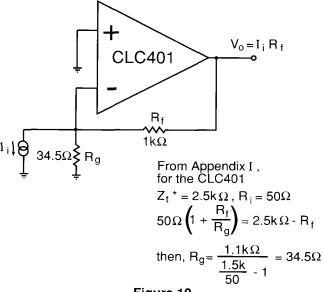

Figure 10 shows an example of a transimpedance application using a CLC401 with a 1k $\Omega$  feedback resistor. In this case, the value of the feedback resistor is set by the desired signal gain, while R<sub>a</sub> is used to satisfy the loop gain phase margin by setting the feedback transimpedance to  $Z^* = 2.5k$ .

Figure 10

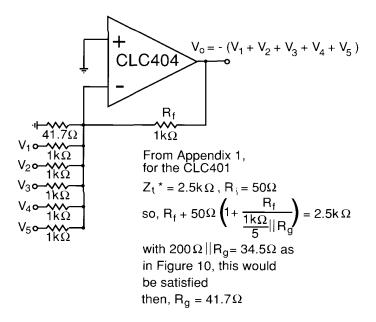

Similarly, in an inverting summing application, once the desired gain and input impedance conditions are set, the loop gain can be independently controlled through the use of an additional resistor to ground on the inverting input. Figure 11 shows an example of this using the CLC401 summing 5 channels, at a gain of -1 for each channel, using 1k  $\Omega$  input resistors.

Figure 11: Loop Gain Adjusted in inverting **Summing Application**

#### Conclusions

The current feedback topology has allowed us to de-couple the signal gain from the loop gain expressions. This provides ample opportunity for independent control of both the signal gains and the frequency response by using only resistive elements. A thorough understanding of the loop gain mechanisms provides the designer with a flexibility unavailable to the voltage feedback op amp.

#### Appendix I

The data tabulated here provide the necessary information to hold a constant feedback transimpedance over a wide range of closed loop signals gains for the current feedback amplifiers available from Comlinear at the time of this application note's publication. The data is broken into a set for the monolithic amplifiers, which generally have a higher  $\mathbf{R}_{i}$  due to their lower quiescent bias current, and a set of data for the hybrid amplifier products.

The table entries show

- A<sub>v</sub> -> Non-inverting voltage gain used to set device specs.

- R<sub>f</sub> -> Feedback resistor value used to set the device specs.

- 3. R<sub>i</sub> -> Nominal inverting input impedance

These 3 items are used to compute the optimum feedback transimpedance for the particular part. This is given by

$$Z_{,*}^* = R_{,} + RA_{,}$$

This information is used to compute a more optimum R, as the desired closed loop gain moves away from the design point A,.

It is important to note that, given any feedback R, and any closed loop non-inverting signal gain, a feedback transimpedance can be computed using the equation for  $Z_1 = R_1 + R_1 A_2$ .  $Z_1^*$  is the optimum value for open loop

phase margin and closed loop response flatness found by evaluating the expression at the specific R<sub>i</sub> and gain used in designing and specifying the part.

Ic -> Approximate collector current for the emmitter followers seen looking into the inverting input. The inverting inputs do not necessarily present an integer number of series/parallel emmitter followers. The approximate scale factors can be computed by solving for n in the following expression.

$R_i = n V_i / I_c$  with  $V_t = kT/q$  (=26mV at room temperature)

$I_c/I_{cc}$  -> ratio of inverting input stage bias current to the total device quiescent current. With n determined from above, the adjusted value for  $R_i$  may be determined for a part that is being operated at a different quiescent current than is normally specified.

The data presented here represent a good approximation to the device characteristics. Several second order effects have been neglected for the sake of simplicity.

The CLC505, an adjustable supply current op amp, was optimized at 9mA supply current. No attempt was made in this table, or in the data sheet, to reset the optimum R, as the supply current is decreased. At very low supply currents, the CLC505's inverting input impedance dominates the feedback transimpedance expression. To compensate for this with a reduced R, as has been suggested in this document, would require such low values as to excessively load the limited output drive current available. The CLC505 at 1mA supply current shows a gain bandwidth product performance due to the dominance of R in the loop gain equation.

Table 1

Comlinear Monolithic, Current Feedback, Amplifier Optimum Feedback Transimpedance and Operating Point Information

|        | Design Point Information |                                     |               |                             | Operating Currents  |                                 |                                                          |

|--------|--------------------------|-------------------------------------|---------------|-----------------------------|---------------------|---------------------------------|----------------------------------------------------------|

| Part # | A <sub>v</sub>           | $\mathbf{R}_{f}\left(\Omega\right)$ | $R_i(\Omega)$ | <b>Z</b> <sub>t</sub> * (Ω) | I <sub>c</sub> (mA) | I <sub>c</sub> /I <sub>cc</sub> | Comments                                                 |

| CLC400 | + 2                      | 250                                 | 40            | 330                         | .67                 | .045                            |                                                          |

| CLC401 | + 20                     | 1500                                | 50            | 2500                        | .52                 | .035                            |                                                          |

| CLC402 | + 2                      | 250                                 | 16            | 282                         | .82                 | .055                            |                                                          |

| CLC404 | + 6                      | 500                                 | 30            | 680                         | .87                 | .080                            |                                                          |

| CLC406 | + 6                      | 500                                 | 60            | 860                         | .43                 | .09                             |                                                          |

| CLC409 | + 2                      | 250                                 | 25            | 300                         | 1.05                | .08                             |                                                          |

| CLC410 | + 2                      | 250                                 | 35            | 320                         | .74                 | .05                             | disable left<br>open                                     |

| CLC411 | + 2                      | 301                                 | 50            | 400                         | .52                 | .05                             | disable left<br>open                                     |

| CLC414 | + 6                      | 500                                 | 250           | 2000                        | .105                | .05                             | each amplifier<br>of quad                                |

| CLC415 | + 6                      | 500                                 | 60            | 860                         | .43                 | .09                             | each amplifier<br>of quad                                |

| CLC430 | + 2                      | 750                                 | 60            | 870                         | .43                 | .04                             | disable left<br>open                                     |

| CLC500 | + 2                      | 250                                 | 32            | 314                         | .82                 | .05                             |                                                          |

| CLC501 | + 20                     | 1500                                | 30            | 2100                        | .86                 | .05                             | see note 3                                               |

| CLC502 | + 2                      | 250                                 | 16            | 282                         | .82                 | .05                             |                                                          |

| CLC505 | + 6                      | 1000                                | 50            | 1300                        | .52                 | .06                             | $I_{cc} = 9.0 \text{ mA}$<br>$R_p = 33 \text{ k}\Omega$  |

| CLC505 | + 6                      | 1000                                | 150           | 1900                        | .175                | .06                             | $I_{cc} = 3.3 \text{ mA}$<br>$R_p = 100 \text{ k}\Omega$ |

| CLC505 | + 6                      | 1000                                | 490           | 3950                        | .053                | .06                             | $I_{cc}$ = 1.0 mA<br>$R_p$ = 300 k $\Omega$              |

#### **Notes**

- 1. Power supplies at  $\pm$  5V

- 2. 25°C temperature assumed; yields kT/q = .026V

- 3. CLC501 specification point at  $A_v = +32$ ,  $R_f = 1500\Omega$  Design point, however is at  $A_v = +20$ ,  $R_f = 1500\Omega$

Table 2

Comlinear Hybrid, Current Feedback, Amplifier Optimum Feedback Transimpedance and Operating Point Information

|         | Design Point Information |               |                           |                                          | Operating Currents  |                                 |                                               |

|---------|--------------------------|---------------|---------------------------|------------------------------------------|---------------------|---------------------------------|-----------------------------------------------|

| Part #  | A <sub>v</sub>           | $R_f(\Omega)$ | <b>R</b> <sub>i</sub> (Ω) | $\mathbf{Z_{t}^{*}}\left( \Omega\right)$ | I <sub>c</sub> (mA) | I <sub>c</sub> /I <sub>cc</sub> | Comments                                      |

| CLC103  | 20                       | 1500          | 8.5                       | 1670                                     | 1.57                | .054                            | fixed internal<br>R <sub>f</sub> . See note 3 |

| CLC203  | 20                       | 1500          | 11.8                      | 1736                                     | 2.21                | .072                            | fixed internal<br>R <sub>f</sub> . See note 3 |

| CLC200  | 20                       | 2000          | 8.5                       | 2170                                     | 1.54                | .053                            | see note 4                                    |

| CLC201  | 20                       | 2000          | 17                        | 2340                                     | 1.54                | .053                            | see note 4                                    |

| CLC205  | 20                       | 2000          | 23Ω                       | 2460                                     | .74                 | .037                            | see note 5                                    |

| CLC206  | 20                       | 2000          | 15Ω                       | 2300                                     | 1.10                | .038                            | see note 5                                    |

| CLC207  | 20                       | 2000          | 23Ω                       | 2460                                     | 74                  | .030                            | see note 5                                    |

| CLC220  | 20                       | 1500          | 8.5                       | 1670                                     | 1.54                | .053                            | see note 4                                    |

| CLC221  | 20                       | 1500          | 17                        | 1840                                     | 1.54                | .053                            | see note 4                                    |

| CLC231  | 2                        | 250           | 15                        | 280                                      | 1.78                | .093                            |                                               |

| CLC232  | 2                        | 250           | 15                        | 280                                      | 1.78                | .071                            |                                               |

| CLC300A | 20                       | 1500          | 7.5                       | 1650                                     | 1.73                | .070                            | see note 4                                    |

#### **Notes**

1. Power supplies at ±15V

2. 25°C temperature assumed; yields kT/q=.026V

3. CLC103 & CLC203 have fixed internal R<sub>f</sub>. Cannot, therefore increase the R<sub>f</sub> value or insert additional R<sub>i</sub> for loop gain control.

4. These parts include an optional internal feedback resistor that may or may not be used in applying the part. Not using this internal  $R_f$  allows adjusting the  $R_f$  over gain and/or inserting additional  $R_i$ .

5. CLC205, CLC206, & CLC207 use a small shunting capacitance across the internal  $R_f$  to extend the bandwidth. Using a standard RN55D external  $R_f$ , with lower shunt capacitance, will require a larger nominal design point value for  $Z_t^*$  to hold optimum loop gain. At  $A_v=+20$ , an external  $R_f=2.74~\mathrm{k}\Omega$  yields the desired  $Z_t$ .

This page intentionally left blank.

This page intentionally left blank.

http://www.national.com 10

This page intentionally left blank.

#### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### National Semiconductor Corporation 1111 West Bardin Road

Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

#### National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 E-mail: europe.support@nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58

Italiano Tel: (+49) 0-180-534 16 80

13th Floor, Straight Block Ocean Centre, 5 Canton Road Tsimshatsui, Kowloon

**National Semiconductor**

Hong Kong Ltd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600

Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.