# Software Engineer's Guide to the System Interface of the DP83266 MACSI Device

# AN-964

# A Software Engineer's Guide to the System Interface of the DP83266 MACSI™ Device

National Semiconductor Application Note 964 Robert Macomber August 1994

# 1.0 INTRODUCTION

This document describes features and mechanisms of the System Interface portion of National's DP83200 FDDI chipset that are important for software designers to know about. The information presented corresponds to the DP83256A BSI-2TM Device. However, this information also applies to the System Interface portion of the DP83266 MACSI Device as well as the DP83256 BSITM Device. Throughout this document we use the generic term System Interface (SI) to refer to all three of these devices.

The goal of this document is to reduce your learning curve (and implementation time) as a software designer using the SI by clearly describing how the SI operates and suggesting methods of interacting with the chip. Since the SI can be used in many different system environments (e.g., direct bus connection, local memory) an effort has been made to make the discussion as general as possible. This document includes:

- An overview of the System Interface (SI)

- A description of the data structures used to transmit and receive FDDI frames

- · A complete tutorial on the SI queues

- A description of the steps involved with sending and receiving FDDI frames

- An examination of various software design issues (i.e., memory mgmt., performance)

- An overview of some low-level SI operations

- · A description of the steps involved with initializing the SI

- A description of the exception conditions and ideas for handling them

This document should be read in conjunction with the appropriate device datasheet; though it should be possible to get a good understanding of the chip using this document alone. An example of SI interface routines, the BSI Device Primitives, is also available from National Semiconductor. These example routines are free of charge. Please contact your local Sales Engineer for more information.

# 2.0 AN INTRODUCTION TO THE SYSTEM INTERFACE (SI)

This section of the document presents a basic overview of the System Interface portion of the FDDI chipset, discusses the design philosophy of the SI and offers a survey of features that are important for software designers to know about

# 2.1 Overview of the System Interface (SI)

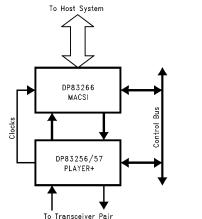

The SI architecture provides a high-level, high-performance system interface for National Semiconductor Corporation's DP83200 FDDI (Fiber Distributed Data Interface) chip set. It provides a simple, powerful interface for sending and receiving frames on FDDI networks. It includes features important to software designers who are implementing high performance interfaces to FDDI networks. *Figure 2-1* shows the MACSI Device (which integrates both the SI functions and the BMACTM functions) as well as the PLAYER+TM Physical Layer Controller.

TL/F/12304-1

# FIGURE 2-1. FDDI Chip Set Block Diagram

The basic operation of the SI is straight forward. It receives and sends FDDI frames. More specifically, it transfers FDDI frames received from the BMAC Device into buffers previously defined by the host and generates status information that describes where the received frames have been placed in memory. It also transfers FDDI frames from buffers supplied by the host to the BMAC Device and generates status information about the frame transmission. At the center of this activity is a set of circular queues located in memory that is shared by the host and the SI. With these memory resident queues, the SI and host engage in classic consumer/producer relationships. In particular:

The host produces transmit requests and consumes transmission status information

MACSI™, BSI-2™, BSI™, BMAC™, PLAYER+™ and SONIC™ are trademarks of National Semiconductor Corporation

- The host produces buffers that will hold received frames and consumes received frames

- The SI consumes empty receive buffers and produces received frames

- The SI consumes transmit requests and produces transmission status information

The host software controls the operation of the SI by manipulating:

- directly accessible registers (called Control Bus Registers)

- registers that are internal to the SI and accessed indirectly by the host (called Pointer RAM and Limit RAM Registers)

- a memory resident mailbox (used to load and store some internal registers)

- several queue related data structures that reside in memory accessible by both the host processor and the SI.

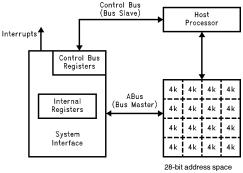

See Figure 2-2 for an illustration of where these registers and data structures exist. It should be noted that some memory must be mutually accessible by both the host processor and the SI. The host accesses memory directly, (though at the hardware level, the host and SI may arbitrate for memory bandwidth). It does not use the FDDI chip set to reach this memory (as is done with some other FDDI chip sets).

memory (contains queues, mailbox and frame data)

TL/F/12304-2

FIGURE 2-2. SI Device, Host Processor and Memory Relationships

# 2.2 Design Philosophy of the SI

The architecture of the SI differs from many analogous Ethernet chips (including National Semiconductor's own SONIC™ Device). Why is this so? FDDI and Ethernet are very different types of networks. FDDI is an order of magnitude faster than Ethernet. The way that stations arbitrate for network bandwidth is completely different, albeit much more equitable in FDDI. FDDI's maximum frame size is roughly three times bigger than Ethernet. FDDI requires that each station engage in a rather complicated set of protocols for network connection and operation (collectively called FDDI Station Management or SMT), which greatly increase the robustness of the network at the cost of more network software/firmware. FDDI supports different classes of frames that are intended for different entities within a station (SMT, MAC, LLC, etc.). The SI was designed to meet these chall

lenges of FDDI and provide features that facilitate the design of robust, high performance network products. Because FDDI is more demanding than Ethernet, different tradeoffs were made.

The design of the SI was driven by many goals. The three most important goals were 1) performance, 2) robustness and 3) FDDI specific functionality.

- Performance, FDDI is ten times faster than Ethernet (100 Megabits per second). Things happen much more quickly and happen much more often than with Ethernet. Also, due to the way that network bandwidth is distributed among stations, traffic on an FDDI network can be very "bursty", so that a station can experience periods of very intense network activity. Frames can arrive with very little idle time between each frame. To handle this type of traffic the SI is capable of simultaneously producing received frame status for one frame while processing the next incoming frame. The system interface is capable of generating and receiving frames at full FDDI bandwidth. The SI also has mechanisms in place to minimize the volume of status information that the host needs to process and make the best use of available memory bandwidth. The data structures were designed to be efficient for both the host and SI (i.e., minimize fetches). The concept of minimizing the volume of status information is also manifested in an interrupt batching scheme, where a single interrupt is generated after multiple frames have been received. Interrupt batching is very important when dealing with FDDI speeds. For example, a series of 100 byte frames can arrive only 8 to 10 microseconds apart.

- Robustness. The FDDI protocols have a lot of inherent reliability features (e.g., dynamic reconfiguration and monitoring of link quality). This emphasis on robustness is also pervasive throughout the entire DP83200 FDDI chip set. The SI was designed to be consistently reliable and operate deterministically. The data structures and queuing mechanisms, in particular, were designed to be extremely robust. For example, all queues are unidirectional with clearly defined producers and consumers; which makes the debugging of queue logic quite straightforward.

- · FDDI Specific Functionality. To make FDDI work well, there are a number of features that should be available. For example, there are several different types of frames that may each need to be handled by different software or hardware agents (i.e., SMT frames, synchronous frames, restricted dialogs, LLC Frames of different priorities, etc.). The system interface needs to help the network driver(s) multiplex and de-multiplex this frame traffic. Also, FDDI requires that stations limit the amount of bandwidth consumed under certain circumstances (e.g., synchronous frames) and control the capture and issuance of different kinds of tokens (e.g., for restricted dialogs). National's FDDI chip set also provides features that take advantage of the fact that each station "strips" the frames that it transmits. The host may receive status information that includes information gathered after the frame has traversed the ring and is being stripped from the FDDI network. For example, it is possible to determine if the receiving station has "dropped" a frame; perhaps due to congestion.

### 2.3 SI Features

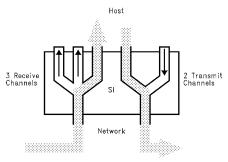

The SI supports two independent Transmit Channels and three independent Receive Channels. Concurrently queued transmit requests are serviced on a priority basis and incoming FDDI frames are sorted to one of three Receive Channels (Receive Channel 0 is dedicated to SMT usage). Channels allow frames to be sent and received by different pieces of software or they can be used to help software meet performance goals by sorting incoming frames onto different Receive Channels based upon the frame class. In addition, there is an option for splitting frames where the headers are placed in one buffer pool and the rest of the frames are, optionally, placed into another buffer pool. See Figure 2-3 for an illustration of the SI Channels.

TI /F/12304-3

### FIGURE 2-3. SI Channels

A skip filter is available on Receive Channel 0 that causes the SI to automatically discard duplicate MAC frames. During FDDI ring initialization thousands of duplicate MAC frames (Claim and/or Beacon) can be circulating on the network. When the skip filter is enabled the first instance of the frame is received while redundant frames are ignored. Thus the station can examine the MAC frames used in ring initialization without the penalty of having to perform unnecessary frame processing.

The data structures used in frame transmission and reception map nicely to data structures frequently used with layered protocols. The SI is capable of doing "gather reads" when processing transmit requests and a limited form of "scatter writes" when receiving frames from the network. On systems where the SI is attached to system memory it may be possible to avoid copying frame data by configuring the SI to read and write directly from system dependent data structures. For example, on systems where the protocol stack uses mbuf/mcluster data structures the SI may be configured to write frame data directly into mclusters (provided that the cluster size is 4 kb or larger).

The SI eliminates the need for network drivers to maintain a separate link layer transmit queue. (The SI datasheet uses OSI terminology where "Request" is equivalent to "Transmit" and "Indicate" is equivalent to "Receive". For the sake of readability the more conventional terms are used in this document.) Instead frame transmission requests from upper-level software can be directly appended to one of the SI's Transmit Channel Queues. Frames can be dynamically queued for transmission while the SI is concurrently sending

other frames from the same queue (without any race conditions). In addition, there are mechanisms available to provide link layer flow control. This is very important when sending FDDI synchronous frames, as each station must explicitly limit the amount of synchronous network bandwidth it uses at each token opportunity.

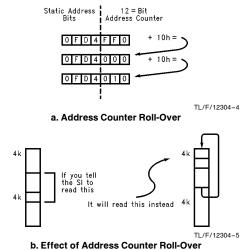

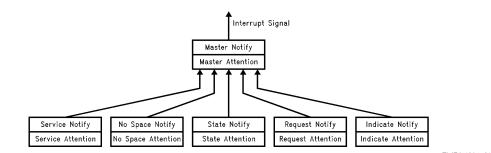

The MACSI and BSI-2 versions of the SI can be configured to automatically flip address bits when sending and receiving FDDI frames (the ordering of bits within each FDDI address octet is reversed from the IEEE canonical form used on Ethernet networks). This option can be enabled on some Channels and disabled on others; which is useful when SMT doesn't want the bits reversed and the "normal" LLC data path does want the bits reversed (actually this is the most common situation). This feature is not available on previous versions of the BSI Device. The SI is page oriented. It logically divides memory into 4 kb pages. This notion permeates the internal design of the SI. As a general rule, the host must not supply data to the SI that crosses a 4 kb page boundary. (Frame data larger than 4k can be described to the SI as multiple independent chunks of memory that happen to be contiguous. This concept is more fully explained in Section 4 "Sending a Frame".) This is due to the way that the SI internally generates addresses. The SI has a 28-bit address space, but the internal address counter that the SI uses to step through memory is 12 bits wide. The upper 16 address bits remain static during memory accesses of a given piece of data (i.e., descriptor queues, frame data, arrays of descriptors, etc.). If the SI is instructed to read across a 4 kb boundary the 12 bit address counter will roll-over and the effective address will "wrap" back to the beginning of the 4 kb page. See Figure 2-4 for an illustration of address "wrapping". The SI presents interrupt status information in a hierarchical manner. This decreases the amount of time required to determine what event caused a given interrupt to occur.

FIGURE 2-4. Four kb Address Counter Roll-Over

The SI is a full-duplex device; meaning that it can simultaneously send and receive data. Full duplex operation is implemented throughout the DP83200 chip set. This feature, along with four available loopback paths in the MACSI and PLAYER+ devices, significantly increases the "testability" of a station's network interface. As a Power Up Self Test, the network interface software can test for good connectivity between the various DP83200 devices and proper operation of the entire chip set by sending and receiving frames across the four available internal loopback paths.

# **3.0 DATA STRUCTURES**

This section covers the data structures shared between the host and the SI. As these data structures are all, in some fashion, related to the SI queues, the discussion will start with an overview of the SI queues, followed by an exposition of the various data structures and then finish up with a thorough tutorial about the SI queues. A full understanding of the operation of these queues is absolutely crucial for any software engineer who is developing software that will interface with the SI.

### 3.1 Introduction to the SI Queues

The SI queues are the primary interface for communication between the host and the SI. The host uses the queues to produce frames for transmission (and consume transmit status information) and consume frames that have been received from the network (and produce empty receive buffers). All SI queues are unidirectional; meaning that the SI either consumes descriptors from a given queue or it produces descriptors for a given queue.

The SI operates independently and asynchronously from the host processor. Many of the older network interface devices use a "batch oriented" approach when transmitting frames. In this scheme a limited number of frames are placed in a staging area, a "Go" command is issued and the host waits for all of the frames to be sent before attempting any further frame transmission. This method of operation sometimes requires that the network interface software provide a link layer queue to hold transmit requests that arrive when the hardware is busy. In contrast the SI is designed to dynamically accept transmit requests at any time (i.e., like a FIFO). The host doesn't have to "spoon feed" frames to the SI.

A crude analogy can be made between network interface hardware (i.e., the SI) and ovens for baking bread. A "batch oriented" oven holds a limited number of loaves for a fixed period of time, while a "continuous process" oven is constantly moving loaves through the heated area. A "continuous process" oven, of the same internal capacity, can bake many more loaves of bread than a "batch oriented" oven over the same span of time. To complete the analogy, the SI may be thought of as a "continuous process" network interface device with the queues acting as "conveyor belts" that carry frames. The net result is that a station can transmit and receive more frames with less overhead. This is an important concept and one that should be exploited by software designers.

# Where do the SI queues exist?

The SI queues exist in memory that is shared between the host and the SI. The actual data of each queue does not reside within the SI, although it does internally retain a unique Queue Pointer for each queue.

# What types of queues does the SI support?

There are four kinds of queues. Each queue is defined by the type of descriptor used within it. Each queue type supports one and only one kind of descriptor.

- Request Descriptor (REQ) queues contain Request Descriptors (REQs). This type of queue is used by the host to queue frames for network transmission.

- Confirmation Descriptor (CNF) queues contain Confirmation Status Message Descriptors (CNFs). This type of queue is used by the host to obtain confirmation about previously queued (and sent) frames.

- Input Data Unit Descriptor (IDUD) queues contain Input Data Unit Descriptors (IDUDs). This type of queue is used by the host to find out about frames that have been received from the network.

- Pool Space Descriptor (PSP) queues contain Pool Space Descriptors (PSPs). This type of queue is used by the host to declare empty buffers where the SI may store incoming frames.

Each Channel has two queues associated with it. Transmit Channels have a REQ queue and a CNF queue. Receive Channels have an IDUD queue and a PSP queue. Figure 3-1 shows how descriptors flow between the host and the SI using these four types of queues.

Host

a. The SI consumes descriptors from the REQ queue, transmits the queued frames and reports back the status of the transmission(s) by producing CNF Descriptors on the CNF queue.

b. The SI consumes PSP Descriptors from the PSP queue (to determine where buffers are available for storing incoming frames), receives frames from the network into these buffers and reports the status of the received frames by producing IDUD Descriptors on the IDUD queue.

TL/F/12304-6

FIGURE 3-1. Flow of Descriptors between Host and SI

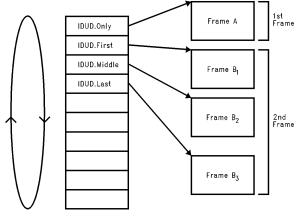

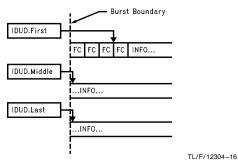

If the SI can do "gather reads" of frame data this implies that more than one descriptor may be required to completely describe a packet. How is this done?

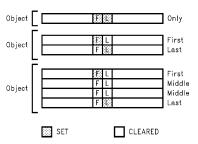

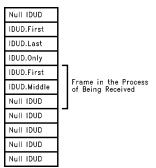

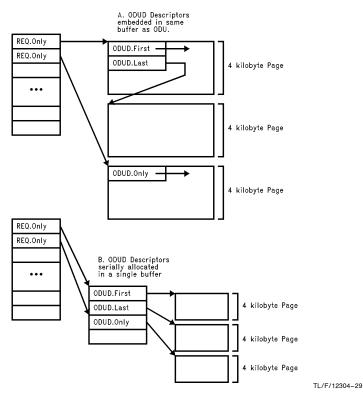

All SI descriptors can be bound together into "multi-descriptor objects". To achieve this grouping all SI descriptors have two bits defined: the "First" and "Last" bits. The first descriptor of an object must have the "First" bit set and, not

surprisingly, the last descriptor of an object must have the "Last" bit set. Any in-between descriptors are termed "Middle" and must have both the "First" and "Last" bits cleared. A descriptor with both the "First" and "Last" bits set is termed an "Only" and describes a complete object. See Figure 3-2 for a graphical representation of a few of the possible descriptor groupings using the First (F) and Last (L) hits

TL/F/12304-

# FIGURE 3-2. Sample Descriptor Groupings

This document uses the term "object" to denote one or more descriptors that logically belong together. Groups of REQ Descriptors are termed "Request Objects". Groups of IDUD Descriptors are termed "Indicate Objects". Groups of CNF Descriptors are termed "Confirmation Objects". Multi-descriptor PSP objects are not currently processed in groups, but rather on an individual basis. For future compati-

bility it is recommended that all PSP Descriptors be configured as PSP.Only (both First and Last bits set). The following sections on SI data structures supply concrete examples of how the First and Last bits are used.

# 3.2 Transmit Data Structures

### 3.2.1 An Overview of the Transmit Data Structures

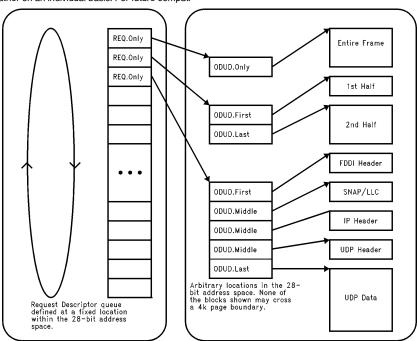

The SI has a three level transmit data structure. It consists of two levels of descriptors and buffers of frame data. The first level consists of Request Descriptors (REQ) that reside in a Request Descriptor queue. Each REQ Descriptor includes a frame count and an address pointer to the second level of the transmit data structure. The second level consists of an array of Output Data Unit Descriptors (ODUDs) that, in turn, each define the address and length of frame data buffers (called Output Data Units (ODUs) in the datasheet). The third level consists of buffers of frame data. See Figure 3-3 for an example of some single frame transmit data structures.

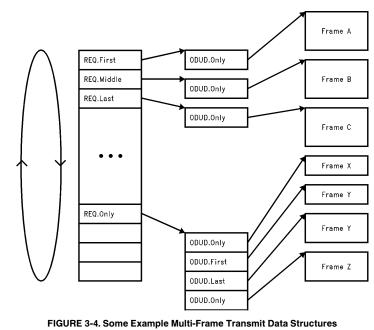

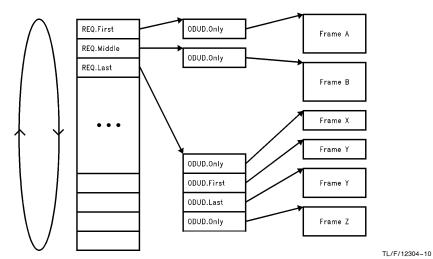

The three level transmit data structure employed by the SI offers a flexible vehicle for building multi-frame Request Objects. It supports applications that need to dynamically batch single frame transmit requests into multi-frame Request Objects as well as applications that need to queue a group of frames (i.e., a TCP window) in a single atomic operation. Building multi-frame Request Objects is important for performance reasons. See *Figures 3-4* and *3-5* for examples of some multi-frame transmit data structures.

FIGURE 3-3. Some Example Single Frame Transmit Data Structures

FIGURE 3-4. Some Example Multi-Frame Transmit Data Structures (Shows the Two Mechanisms for Building Multi-Frame Request Objects)

FIGURE 3-5. Some Example Multi-Frame Transmit Data Structures (Combines the Two Mechanisms for Building Multi-Frame Request Objects)

A Request Object consists of one or more REQ Descriptors grouped together using First and Last bits and all of the ODUDs and ODUs referenced by the REQ Descriptors. (During normal operation Request Objects should be limited to a maximum size of 255 frames.) The Request Object is the unit of consumption used by the SI when consuming transmit requests. The general flow control rule is that the SI processes one Request Object per Channel per service opportunity, thus the host may implement fine grained link layer flow control (at the network service opportunity level) by modulating the size of the Reguest Objects that it produces. If both of the two Transmit Channels each have at least one Request Object queued, then two Request Objects will be consumed upon the next service opportunity. (FDDI service opportunities are briefly described in the glossary at the end of this document.)

The SI automatically performs a series of consistency checks when consuming a Request Object. For example, if the SI consumes a REQ.First followed immediately by another REQ.First it will report a consistency failure and attempt to discard REQ Descriptors until a REQ Descriptor is found with the Last bit set.

Many Ethernet system interfaces, including National Semiconductor's SONIC Device, chain together descriptors into a linked list. The SI uses an array of ODUD Descriptors instead of a linked list. This was done to minimize the number of memory fetches needed to consume a transmit request (no "next descriptor" pointer to fetch). Plus, the use of First/Last bits allows the SI to perform consistency checks when processing a stream of ODUD Descriptors.

# 3.2.2 Transmit Frame Layout

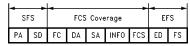

When the frame data buffers (ODUs) are concatenated they present an entire FDDI frame to the SI. What frame format does the SI expect to find inside these ODUs?

The FDDI MAC Standard (X3.139-1987) defines the format of an FDDI frame as shown in *Figure 3-6*.

TL/F/12304-11

| SFS | Start of Frame Sequence | INFO | Information           |

|-----|-------------------------|------|-----------------------|

| PA  | Preamble                | FCS  | Frame Check Sequence  |

| SD  | Starting Delimiter      | ED   | Ending Delimiter      |

| FC  | Frame Control           | FS   | Frame Status          |

| DA  | Destination Address     | EFS  | End of Frame Sequence |

| C 4 | O Add                   |      |                       |

FIGURE 3-6. FDDI Frame Format

The SI expects to be presented with FDDI frames structured with place holders for the Frame Control, Destination Address and Source Address fields. The INFO field may be zero or more bytes and the host may optionally supply its own FCS field. The start of the frame data (or any of the ODUs for that matter) need not be aligned in any special way (i.e., frame data can start on any byte boundary). None of the blocks of frame data may cross a 4 kb page boundary, though any single, contiguous block of frame data can be represented by multiple ODUDs. The frame must always include a place for the Frame Control, whether or not Frame Control Transparency is used. (Frame Control Transparency is useful for SMT usage, which routinely uses different FDDI Frame Control values. This mode is enabled via the Transmit Channel's Request Configuration Register (R0CR0 or R1CR0).) The frame must always include a place for the Source Address, whether or not Source Address Transparency is used. Source Address Transparency is useful in transparent bridging applications. This mode is enabled via the Transmit Channel's Request Configuration Register (R0CR0 or R1CR0) and is normally used with "Void Stripping" (also enabled via the Request Configuration Register).

A typical frame (long addresses and FCS automatically generated by the BMAC device) will have the format shown in *Figure 3-7*.

| FC  | DA     | SA | INFO |

|-----|--------|----|------|

| 0   | 1      | 7  | 13   |

| 4:- | h.ukaa |    |      |

Offset in bytes from the start of a frame

TL/F/12304-12

# FIGURE 3-7. Format of FDDI Frame within Output Data Units

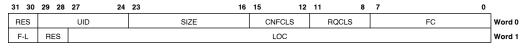

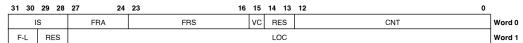

### 3.2.3 The Request Descriptor

Request Descriptors (REQ) exist on REQ queues and are produced by the host. They function as the root of the three-level transmit data structure. In addition to describing what FDDI frames to transmit, the REQ Descriptor describes how the FDDI frames should be transmitted and what type of transmit status information the SI should produce. REQ Descriptors can be grouped together into a multi-descriptor Request Object by using the First/Last bits found in all of the SI descriptors. See *Figure 3-8* for an illustration of the REQ Descriptor.

FIGURE 3-8. Request Descriptor (REQ)

The SI examines the UID, CNFCLS, RQCLS and FC fields when consuming the first REQ Descriptor in a Request Object (i.e., the First bit is set). These values are then used for all REQ Descriptors in the rest of the Request Object. The LOC (address of ODUD array) and SIZE (frame count) fields of all REQ Descriptors are always used by the SI. A brief explanation of each field follows. The databook should be examined for a full explanation of these fields.

- The UID, User Identification, field (6 bits) may be programmed by the host with any value. This value reappears in the transmit status information (CNF Descriptors) that correspond to the transmit request. This field can be used by the host to match up transmit requests with transmit status.

- The SIZE, frame count, field (8 bits) declares the number of frames described by the current REQ Descriptor; not the number of ODUDs. The SI counts ODUD Descriptors that have the Last bit set and compares this value with SIZE

- The CNFCLS, Confirmation Class, field (4 bits) declares the class of transmit status information that the SI should produce. This class describes three different kinds of status generating behavior, each represented by a bit, that can be combined in the following ways (the device datasheets includes a fourth bit, repeat frame (R) that is not related to transmit status generation). Many applications use a confirmation class of Tend to generate transmit status information solely for the purpose of transmit data memory reclamation. See Table 3-1.

**TABLE 3-1. CNFCLS Components**

| CNFCLS | End   | Intermediate | Full/Transmit | Description                                                                                                                                                                                                                                                                 |

|--------|-------|--------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NONE   | False | False        | Don't Care    | <b>NONE.</b> CNF Descriptors are <i>produced</i> only when a transmit exception occurs.                                                                                                                                                                                     |

| TEND   | True  | False        | False         | <b>TEND.</b> A single CNF Descriptor is <i>produced</i> for each <i>consumed</i> Request Object (NOT one for each REQ Descriptor). CNF Descriptors are <i>produced</i> at frame transmission time.                                                                          |

| TINT   | True  | True         | False         | TINT. The same as TEND, plus CNF Descriptors are <i>produced</i> at the end of each transmission (token) opportunity (provided that the Request Object spans more than one transmission opportunity).                                                                       |

| FEND   | True  | False        | True          | <b>FEND.</b> A single CNF Descriptor is <i>produced</i> for each <i>consumed</i> Request Object (NOT one for each REQ Descriptor). CNF Descriptors are <i>produced</i> at frame stripping time and populated with additional status information about the returning frames. |

| FINT   | True  | True         | True          | FINT. The same as FEND, plus CNF Descriptors are produced at the end of each transmission (token) opportunity (provided that the Request Object spans more than one transmission opportunity).                                                                              |

- The RQCLS, Request Class, field (4 bits) denotes how the BMAC device should behave when transmitting the frames of the Request Object. It describes the type of token (if any) that must be captured before sending the frames, how the frames should be sent (e.g., synchronous, asynchronous), the type of token (nonrestricted, restricted, none) that will be issued after sending the frames and whether or not the BMAC device should use the normal (asynchronous) rules for determining token usability in a restricted dialog. (Different criterion are used for asynchronous and synchronous frames when determining if a frame may be transmitted at a given token opportunity.) Restricted dialogs can be thought of as a supervisor (kernel) mode for access to an FDDI network. This capability is not currently used by FDDI Station Management (SMT). Logical Link Control (LLC) traffic would typically use a value of 1000 binary (Asyn) to denote that the BMAC device should capture a non-restricted token, send asynchronous frames in a manner that respects the integrity of the FDDI timed token protocol and issue a non-restricted token after frame transmission. The network driver should enforce the use of appropriate request classes (e.g., don't allow IP packets to go out with a RQCLS of "immediate").

- The FC, Frame Control, field (8 bits) can be used to optionally override, at network transmission time, the FDDI Frame Control value of the FDDI frames of the Request Object. This will be done if Frame Control Transparency has not been enabled in the Transmit Channel's Request Configuration Register (ROCR or R1CR).

- The F-L, First-Last, fields (2 bits) are used to define groupings of one or more descriptors.

- The LOC, Location, field (28 bits) holds the address of an array of ODUD Descriptors.

# What is the difference between "Full" and "Transmit" Confirmation?

Both "Full" and "Transmit" confirmation result in the generation of CNF Descriptors on the Transmit Channel's CNF queue. They differ in the time at which CNF Descriptors are produced and in the type of valid information contained in the CNF Descriptors.

Transmit confirmation is generated at frame transmit time and, therefore, includes only information that can be gathered when transmitting frames. The UID is always valid as is the Transmitted Frame Count (TFC) and the Request Status (RS). When using transmit confirmation the Frame Attributes (FRA), Frame Status (FRS), Confirmed Frame Count (CFC), and some bits of the Confirmation Status (CS) are invalid.

Full confirmation is generated at frame stripping time. The information that is valid under full confirmation is a super set of transmit confirmation (All of the fields of the CNF Descriptor are valid). While full confirmation does provide more information, the real power of this option is that it provides the ability to terminate wasteful transmissions.

When sending a large amount of data to another station (i.e., a TCP window) the receiving station may be receiving more frames than it can handle. In this case the sending station is wasting network bandwidth and system resources (e.g., bus bandwidth) by transmitting frames that will be "dropped". When using full confirmation the host may define certain conditions that will halt transmission and flush the remainder of the current Request Object. This is accomplished by configuring the Transmit Channel's Expected Frame Status Register (R0FSR or R1EFSR). For example, the host may specify that transmission will halt if the receiving station doesn't copy a frame or if a frame becomes corrupted on the network.

# What is the difference between End and Intermediate Confirmation?

The End confirmation classes, Transmit End (Tend) and Full End (Fend), cause the SI to produce a single CNF Descriptor for each Request Object.

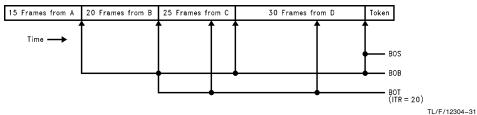

The Intermediate confirmation classes, Transmit Intermediate (Tint) and Full Intermediate (FINT) cause the SI to produce a CNF Descriptor for each service opportunity in which frames, of a given Request Object, have been sent. The confirmation count fields of the CNF Descriptors contain a cumulative, running count of what has been sent. For example, if a Request Object includes 20 frames which are actually transmitted in three service opportunities, then the SI will produce three CNF Descriptors perhaps with Transmitted Frame Count (TFC) values of 7, 14 and 20. The actual value depends upon the duration of each service opportunity.

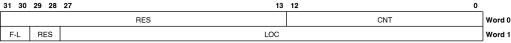

# 3.2.4 The Output Data Unit Descriptor

Output Data Unit Descriptors (ODUDs) are the middle level of the three-level transmit data structure. They do not exist in a queue, but rather in arrays placed at arbitrary locations within the 28-bit addressable memory range of the SI. Each ODUD defines the address and length of part of a frame (perhaps the entire frame) queued for transmission. Those ODUD Descriptors that refer to a given frame are grouped together via First and Last bits. See *Figure 3-9* for a picture of the ODUD. A brief explanation of each field follows. The databook should be examined for a full explanation of these fields.

FIGURE 3-9. Output Data Unit Descriptor (ODUD)

- The CNT, count, field (13 bits) tells the SI the length of a chunk of frame data referred to by the ODUD.

- The F-L, First-Last, fields (2 bits) are used to define groupings of one or more descriptors.

- The LOC, location, field (28 bits) holds the address of a chunk of frame data referred to by the ODUD (called an Output Data Unit (ODU)).

ODUD arrays may not cross 4 kb page boundaries. If the SI is "asked" to fetch ODUDs from an array that spans two 4k pages, the SI will "wrap" back to the beginning of the first page. This behavior can be exploited to implement a very simple memory management scheme for ODUDs. For example, the host software could maintain a 4 kb page of memory (aligned on a 4 kb page boundary) for ODUD arrays. The same type of logic used to acquire space on a REQ or PSP queue could be applied to managing such a block of ODUD memory.

# 3.2.5 The Confirmation Status Message Descriptor (CNF)

The SI produces transmit status information in the form of CNF Descriptors on a CNF Descriptor queue. The host can determine the success or failure of a transmit request by consuming CNF Descriptors from the queue. Some of the fields are not valid unless Full Confirmation is specified in the first REQ Descriptor of the Request Object See *Figure 3-10* for a picture of the CNF Descriptor. A brief explanation of each field follows. The databook should be examined for a full explanation of these fields.

- The RS, Request Status, field (4 bits) enumerates the status of the transmit request. This field is always valid.

- The FRA, Frame Attributes, field (4 bits) describes the terminating condition and address matching flags (Destination or Source Address equal to MAC address). These values are collected as the frame is stripped off of the ring. This field is only valid when Full Confirmation is used.

- The FRS, Frame Status, field (8 bits) contains the FDDI E, A, and C Indicators (Error Detected, Address Recognized and Frame Copied) and two flags that indicate if the FCS on the frame agrees with frame data and if the frame is well formed. These values are collected as the frame is stripped off of the ring. This field is only valid when Full Confirmation is used.

- The TFC, Transmitted Frame Count, field (8 bits) records the number of frames transmitted. This field is always valid. When using Tint or Fint confirmation the SI will produce a CNF Descriptor at the end of each service opportunity and this field will contain a running total of the number transmitted frames. This field is not accurate for Request Objects containing more than 255 frames.

- The CFC, Confirmed Frame Count, field (8 bits) records the number of frames confirmed. This count is based upon frames stripped off of the ring. This field is only valid when Full Confirmation is used. When using Tint or Fint confirmation the SI will produce a CNF Descriptor at the end of each service opportunity and this field will contain a running total of the number of confirmed frames. This field is not accurate for Request Objects containing more than 255 frames.

- The F-L, First-Last, fields (2 bits) are used to define groupings of one or more descriptors.

- The UID, User Identification, field (6 bits) matches the UID field programmed by the host in the first REQ Descriptor of the Request Object. The basic idea is that all CNF Descriptors produced by the SI include a tag that identifies which Request Object the status information is all about. The host can use the UID field to relate transmit status information to a given Request Object. Since this field is 6 bits wide, 26 (64) Request Objects can be uniquely paired with CNF Descriptors. Request objects may include multiple REQ Descriptors.

| 31 30 29 | 9 28 27 24 | 23 16 | 15 8 | 7 0 | _      |

|----------|------------|-------|------|-----|--------|

| RS       | FRA        | FRS   | TFC  | CFC | Word 0 |

| F-L      | UID        | FC    | CS   | RES | Word 1 |

FIGURE 3-10. Confirmation Status Message Descriptor (CNF)

- The FC, Frame Control, field (8 bits) contains the FDDI Frame Control value of the last confirmed frame. This field is valid only when using Full Confirmation (Fend, Fint)

- The CS, Confirmation Status, field (8 bits) contains several miscellaneous flags related to the confirmation process. Some of these bits relate only to Full Confirmation.

# 3.3 Receive Data Structures

# 3.3.1 Overview of Receive Data Structures

The SI uses a two level data structure to represent frames that have been received from the network. The receive data structure is extremely straightforward. The top level consists

of Input Data Unit Descriptors (IDUDs) organized as a queue and the bottom level consists of frame data that has been placed in memory by the Sl. See *Figure* 3-11 for a depiction of the receive data structure generated by the Sl. The format of the IDUD is a super set of the ODUD. This was done to allow FDDI-to-FDDI bridges to reuse IDUDs as ODUDs.

# 3.3.2 Received Frame Layout

Frames that are received from the network contain the FDDI Frame Control (FC), Destination Address (DA), Source Address (SA), the FDDI Info field (i.e., packet data) and the FDDI Frame Check Sequence (FCS, 4 bytes long). See *Figure 3-12* for an illustration of the received frame format.

FIGURE 3-11. Receive Data Structure

FC

DA

SA

INFO ...

FCS

0 1

7

13

→

Offset in Bytes

4 Bytes

Long

FIGURE 3-12. Received Frame Layout

TL/F/12304-13

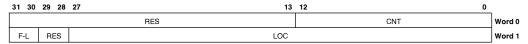

### 3.3.3 The Input Data Unit Descriptor (IDUD)

The SI produces IDUD Descriptors and the host consumes them. Each IDUD Descriptor refers to part of a frame (possibly an entire frame). IDUD Descriptors that describe a single frame are grouped together via First and Last bits. The last IDUD of an Indicate Object (one or more IDUD Descriptors grouped together to completely describe a received frame) contains status for the entire frame. See *Figure 3-13* for a picture of the Input Data Unit Descriptor. A brief explanation of the fields in the IDUD Descriptor follows. The databook should be examined for a full explanation of these fields.

- The IS, Indicate Status, field (4 bits) reports the status of the received frame. This field should be queried to determine if the received frame is suitable for processing.

- The FRA, Frame Attributes, field (4 bits) describes the terminating condition and address matching flags (Destination or Source Address equal to MAC address). This field should be queried to determine if the received frame is suitable for processing.

- The FRS, Frame Status, field (8 bits) contains the FDDI E, A, and C Indicators (Error Detected, Address Recognized and Frame Copied) and two flags that indicate if the FCS on the frame agrees with frame data and if the frame is well formed. This field should be queried to determine if the received frame is suitable for processing.

- The VC (Valid Copy) field (1 bit) records how the SI signaled the BMAC device with regard to copying the frame off of the network. If VC is false then the BMAC device will increment its Frames Not Copied counter.

- The CNT (Count) field (13 bits) holds the length of the part of the received frame data (Input Data Unit (IDU)) to which the IDUD refers.

- The F-L, First-Last, fields (2 bits) are used to define groupings of one or more descriptors.

- The LOC (Location) field (28 bits) holds the address of the part of the received frame data (IDU) to which the IDUD refers.

# 3.3.4 The Pool Space Descriptor (PSP)

For the SI to produce received frames it must be told where, in memory, the incoming frame data can be stored. To declare receive buffers the host must produce Pool Space Descriptors (PSP) for the SI to consume. See *Figure 3-14* for a picture of the PSP Descriptor.

The current implementation of the SI is heavily page oriented. It does not currently use the PSP's CNT field at all (it does not even fetch the first word of the PSP Descriptor). It uses the 28-bit address of the LOC field to define the start of a receive buffer and the next 4 kb page boundary as the end of a receive buffer. Also, the buffer memory defined by the LOC field must be aligned on a "burst boundary"; either 16 or 32 bytes. When dealing with frame data the SI accesses memory in "bursts" of bus usage. It acquires the bus and the reads or writes in 4 or 8 word (16 or 32 byte) chunks. The SI can be configured to use only 4 word bursts or both 4 and 8 word bursts.

FIGURE 3-13. Input Data Unit Descriptor (IDUD)

FIGURE 3-14. Pool Space Descriptor (PSP)

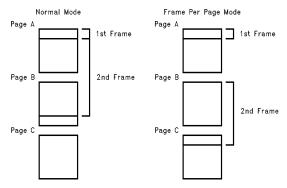

# How are received frames stored in memory? One frame per page? Multiple frames packed in a page?

The SI has two modes of operation that affect the way that incoming frames are stored: "normal" mode and "Frame per Page" mode (FPP). When Frame per Page mode is enabled the SI will only put one frame in a given page; though a single frame may split up into fragments that are stored in multiple pages (i.e., frames greater than the page size). When Frame per Page mode is not enabled the SI will pack as many frames as possible into each page. Currently Frame per Page mode affects all Receive Channels. See Figure 3-15 for a picture showing the difference between the two modes.

The SI writes frame data out in bursts of 4 or 8 words (16 or 32 bytes). When transferring a new frame to memory the SI always starts writing at a burst boundary. The first word is filled with four copies of the FDDI Frame Control and the

Destination Address starts with the second word. The LOC field of the first IDUD points to the last byte in the first word. This has the effect of starting the FDDI Info field with a 32-bit word alignment. This alignment is important (for performance reasons) for applications that want to avoid copying frame data as it allows the host to use native accesses (i.e., 16 and 32 bit integers) to parse the packet contents. When a frame is split across multiple pages the SI begins the next IDU on a burst boundary. Therefore, the bottom two bits of the IDUD.LOC field will either contain 3 or 0, but never 1 or 2 (this makes an IDUD with 0x00000001 or 0x00000002 in the LOC field a good candidate for marking an IDUD queue slot as a "null descriptor"). A "null descriptor" is a descriptor value that signifies that a queue slot is empty. This concept is presented more fully in the following discussion about SI queues. See Figure 3-16 for an illustration of IDU alignments.

FIGURE 3-15. SI Memory Storage Modes

FIGURE 3-16. IDU Alignments

### 3.4 The SI Queues in Depth

This area of the document focuses in on the operational details of the SI queues. Although there are four types of descriptor queues, when examining the operation of the queues we need only consider two basic types:

- queues for which the host produces descriptors and from which the SI consumes descriptors (REQ and PSP queues) and

- queues from which the host consumes descriptors and for which the SI produces descriptors (CNF and IDUD queues).

In the discussion that follows the REQ and PSP queues are treated as equivalent and the IDUD and CNF queues are treated as equivalent. The steps that the host performs to produce or consume descriptors is the same.

# How are the SI queues organized?

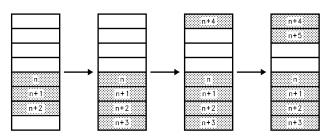

An SI queue is a 1 kb or 4 kb block of memory divided up into 8 byte (descriptor sized) gueue slots. The size of the queues is defined at SI initialization time and is specified via the Mode Register (SIMR0) Control Bus Register. A 1 kb queue has 128 queue slots and a 4 kb queue has 512 queue slots. This block of memory is reused in a circular fashion (i.e., like a ring buffer); such that as descriptors are being processed, the lowest addressed descriptor is considered to logically follow after the highest addressed descriptor. This behavior is termed a "queue wrap" in this document. The point at which the queue wrap occurs is fixed at either a 1 kb or 4 kb boundary. All of the active SI queues are the same size (either 1 kb or 4 kb). Also, since boundaries are used to define the "wrap point" all SI queues must be aligned on either 1 kb or 4 kb boundaries. See Figure 3-17 for illustrations of a queue before and after a queue wrap.

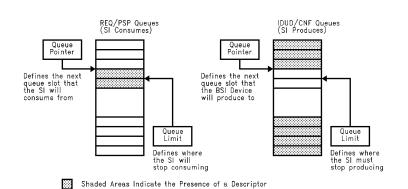

The SI uses two internal registers to represent the current progress of a queue: a Queue Pointer that indicates where the SI "is" in the queue and a Queue Limit that indicates how far the SI can advance. The consumption and production of descriptors is totally controlled via the Queue Pointer

and Queue Limit values. The SI does not use "ownership" bits. See *Figure 3-18* for an illustration of how Queue Pointers and Queue Limits are logically used in queues.

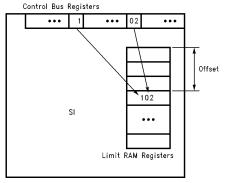

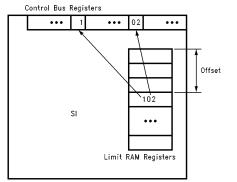

The SI maintains a 28-bit Queue Pointer (internal Pointer RAM Register) for each queue. This pointer indicates the next queue slot that the SI will access. Also, because all queues are aligned on 1 or 4 kb boundaries, the upper most bits in the pointer (16 bits for 1 kb queues or 14 bits for 4 kb queues) define the base location of the queue. The host must load the Queue Pointer during initialization to tell the SI where the queue is located. Thereafter it is totally maintained by the SI.

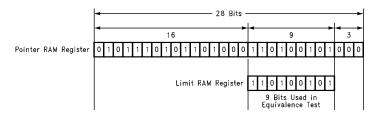

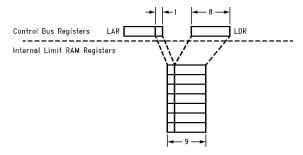

The SI uses a 9-bit Queue Limit (internal Limit RAM Register) for each queue. The Queue Limit defines which queue slots are available for either reading or writing by limiting how far the SI can advance in the queue. A Queue Limit value can be thought of as an offset from the base address of the queue in units of 8 byte descriptors. Queue limits are totally maintained by the host. The SI only looks at Queue Limit values to determine when to stop queue processing. Figure 3-19 shows how Pointer RAM Register and Limit RAM Register data types are related.

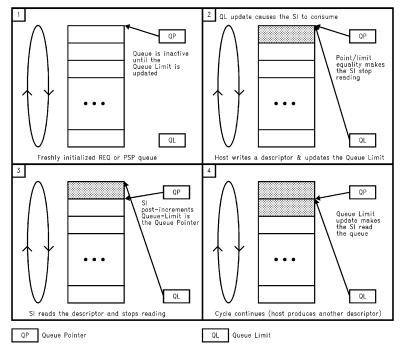

# How does the SI "know" when to examine the REQ and PSP queues for new descriptors to consume?

Rather than implementing a special "queue ready" command or making the system interface repeatedly check for the presence of a descriptor (i.e., an "ownership" bit), the designers of the SI incorporated special logic in the portion of the chip that deals with updates to Limit RAM Registers. The act of updating a REQ or PSP Queue Limit is detected and interpreted as a signal to begin consuming descriptors from the queue. Thus the host may simply queue descriptors without having to be concerned about whether the Channel is active or inactive. If the host is queuing a group of descriptors it may, for the sake of efficiency, update the queue's Queue Limit once for all of the descriptors. See Figure 3-20 for a depiction of the actions necessary to queue a single REQ or PSP Descriptor.

FIGURE 3-17. Queue Wrap at 1 kb or 4 kb Boundary (Snapshots of a Queue Over Time)

FIGURE 3-18. Queue Pointers and Queue Limits

TL/F/12304-18

TL/F/12304-19

FIGURE 3-19. Comparison of Pointer RAM and Limit RAM Registers (The Register Values Shown Are Considered to be Equivalent)

FIGURE 3-20. REQ or PSP Descriptor Queuing Example

# How does the SI "know" when to stop consuming REQ and PSP Descriptors?

As each descriptor is fetched the SI compares the Queue Pointer with the Queue Limit. When these two registers are equivalent the descriptor currently being fetched is consumed and queue processing is stopped and remains inactive until the Queue Limit is updated. If the Queue Limit is updated before the above mentioned equivalence is detected the SI will automatically continue consuming descriptors from the queue. This mechanism is very robust and allows the host to dynamically produce transmit requests without concern for race conditions between the host and SI.

# What causes the SI to produce descriptors on CNF and IDUD queues?

The CNF and IDUD queues are status queues. The SI produces CNF or IDUD Descriptors to report status information back to the host. CNF Descriptors are produced when a transmission request has completed or, optionally, a network transmission opportunity has ended before the entire Request Object has completed. (If a confirmation class of "none" is specified on a given Request Object then CNF Descriptors will only be produced when an error occurs while processing that Request Object.) IDUD Descriptors are produced every time a frame is received from the network. Multiple IDUD Descriptors are produced to describe a frame that is split across 4 kb pages.

How does the SI "know" when to stop producing CNF and IDUD Descriptors so that previously produced descriptors are not overwritten before the host has consumed them?

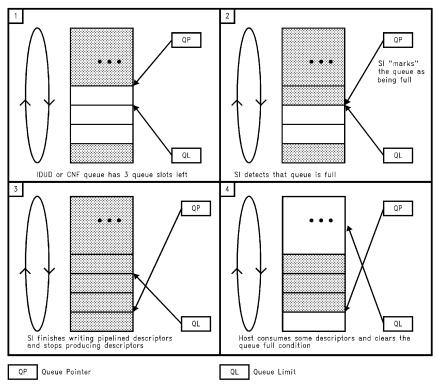

The SI compares the queue's Queue Pointer and Queue Limit after producing a CNF or IDUD Descriptor (the SI post-increments the Queue Pointer after producing a descriptor). When these two registers are found to be equivalent then the SI "marks" the queue as full, by asserting a bit in one of the directly accessible Control Bus Registers (No Space Attention Register (NSAR)), and stops Channel operation. The user may configure the SI to generate an interrupt when this bit is asserted. The Channel will remain stopped until the host has cleared the bit. This mechanism keeps the SI from overwriting previously produced descriptors before the host has consumed them. The host should update the queue's Queue Limit (to denote which queue slots may be overwritten) before clearing the bit.

Due to internal "pipelining" of descriptors within the SI, it is possible for two additional descriptors to be produced after pointer/limit equality has been detected. This behavior must be considered by the host when calculating Queue Limit values. The Queue Limit should be set such that it refers to the "next to the last" writable queue slot. Also, when responding to a full queue condition the host must ensure that the Queue Limit is set to be logically "ahead" of the Queue Pointer before clearing the bit that signals the queue full condition. See Figure 3-21 for an illustration of the queue full condition.

TL/F/12304-21

FIGURE 3-21. IDUD or CNF Queue Full Condition

# How does the host "know" when to start consuming IDUD or CNF Descriptors?

The host may either poll for new descriptors or respond to an interrupt signifying the arrival of a single or group of descriptors.

The SI can be configured to generate interrupts when producing a CNF Descriptor and when frames have been received (it can generate a single interrupt for a group of frames or an interrupt after each frame is received). The host may enable and disable specific interrupt causing attentions at any time.

The host may poll for new descriptors in two different ways. One way is for the host to repeatedly read the queue memory looking for a new descriptor to be written into memory. An alternate method is for the host to configure the SI to generate an attention, yet disable that specific attention from causing an actual interrupt. The host may then repeatedly read one of the directly accessible Control Bus Registers, waiting for the attention bit to become asserted.

# How does the host "know" when to stop consuming IDUD or CNF Descriptors? How does the host recognize an "End of Queue" condition?

There are two different methods of dealing with this issue. The most direct way for the host to determine which descriptors it should consume is to read the value of the queue's Queue Pointer. The Queue Pointer is maintained by the SI and defines the 28-bit address at which the next descriptor will be written; thus the host may consume IDUD or CNF Descriptors until reaching this point in memory. Since the Queue Pointer is maintained by the SI as an internal Pointer RAM Register the host must initiate an operation that causes the SI to write out the Queue Pointer into a predefined memory location (termed the mailbox). However, this operation competes with other SI functions for access to the SI's ABus interface.

Another method is for the host to populate each empty queue slot with a specially marked descriptor referred to as a "null descriptor". When processing the queue the host can recognize the "End of Queue" condition by detecting the presence of a "null descriptor". In most environments the "null descriptor" method will be fastest.

# What is a good bit pattern for denoting a "null descriptor"?

The value used to denote a null descriptor must be one that is impossible for the SI to produce and must be placed in the second word of the descriptor. Null descriptors are only needed for IDUD and CNF queues, since these are the kinds of queues that the host uses to consume descriptors. The SI writes descriptors out to memory using two distinct bus request/grant cycles, so the host should look for "nullness" in the second word (which is written out last). There is no single value that, in general, can be used for both IDUD and CNF queues. Some ideas follow.

The SI will never produce an IDUD Descriptor with a value of x'1' or x'2' in the least significant two bits of the LOC field. It will only produce IDUDs with a value of x'0' or x'3' for these two bits. It is recommended to use an IDUD with a LOC field value of x'000001' or x'000002' to denote a null

descriptor on an IDUD queue. If the system environment precludes the use of page 0 (e.g., that's where the system's interrupt vectors are located), then the act of testing for "nullness" may be made more efficient by using an IDUD with binary zeroes in the second word as the null descriptor; which may permit a "Branch Not Zero" instruction to be used.

The choice of a null descriptor for CNF queues is, unfortunately, dependent upon the way that the SI is programmed. Here are two suggestions.

- When consistently using a confirmation class of None, Tend or Fend the F-L field may be used. In particular, a descriptor with both First and Last bits cleared could be used to denote a null descriptor on a CNF queue.

- If using a confirmation class of Tint or Fint the UID field could be used. This requires that the host never create a Request Object using a particular UID value (i.e., zero) that is being used to denote a null descriptor on a CNF queue.

# The host produces REQ Descriptors when queuing a frame for transmission, but how does the host "know" when to produce a PSP Descriptor?

The host produces PSP Descriptors to declare where the SI can store incoming frames. So, the host should either attempt to maintain a certain number of receive buffers (by detecting when buffers are consumed by the SI) or respond to the attention bit (in one of the directly accessible Control Bus Registers) that signals the "Low Data Space" condition. This issue is discussed in greater detail in Section 7.1, Memory Issues.

# How can the host tell when it should stop producing REQ or PSP Descriptors (to avoid overwriting descriptors not yet consumed by the SI)? What is the "Queue Full" condition for REQ and PSP queues?

The SI queues are circular, so it makes sense that the host should consider a REQ or PSP queue full when producing one more descriptor would cause the SI to treat the queue as empty. The SI recognizes the queue as empty when it detects pointer/limit equality while consuming a descriptor, so the host should recognize the "Queue Full" condition when the queue's Queue Pointer is logically one descriptor "ahead" of the queue's Queue Limit. The host should test for the "Queue Full" condition before queuing an additional REQ Descriptor.

If, for some reason, the host also wants to be able to determine if a REQ or PSP queue is empty by comparing the Queue Pointer and Queue Limit values the above test for a full queue will make a test for an empty queue impossible. In this case the host should recognize the "Queue Full" condition when the queue's Queue Pointer is logically two descriptors "ahead" of the queue's Queue Limit and recognize an empty queue when the Queue Pointer is logically one descriptor "ahead" of the Queue Limit. This is a non-typical requirement, since there are more intuitive ways for the host to determine when a REQ Queue is empty.

# How does the host "know" which queue slot to access when either producing or consuming a descriptor?

The SI does not maintain pointers to tell the host where to read or write descriptors. The host must maintain these pointers by itself, but it is a simple task. When the SI is initialized the Queue Pointers are established with known values (typically the base address of the queue). The SI always advances sequentially in all queues; therefore the host should start with the initialized value and proceed sequentially from then on (taking care to handle queue wraps). Some example C macros for calculating the address of the next queue slot can be found in Figure 3-22.

The host needs to "know" the value of Queue Pointers to check for the "Queue Full" condition on REQ and PSP queues (to avoid overwriting descriptors before the SI consumes them). Does the host need to perform Pointer RAM Operations each time it produces a descriptor?

While directly reading Queue Pointers from the SI's internal Pointer RAM Registers is logically simple, it may be unacceptable (for performance reasons) for the host to frequently perform Pointer RAM Operations in a synchronous manner. (An alternate and efficient method is to asynchronously schedue Pointer RAM Operations and update the Software Queue Pointer when the read operation has completed.) In stead the host may infer the value of an SI's REQ or PSP Queue Pointer when consuming the complementary status queue. This requires that the host maintain a "Software Queue Pointer" (SQP) that is a lower bound approximation

of the true value of the "Hardware Queue Pointer" (HQP, located in a register internal to the SI). Note that this exercise is not necessary for Queue Limits, since these are totally maintained by the host. The Software Queue Pointer indicates how far the Queue Limit can be advanced before overwriting descriptors that the SI has not yet consumed.

To maintain a REQ Software Queue Pointer (SQP) by inference the host must:

- use a confirmation class other than none (Tend works quite well for this purpose)

- initialize the SQP and SI's Queue Pointer with the same value (at power-up time)

- increment the REQ.UID field value for each REQ.Only or REQ.First Descriptor

- consume CNF Descriptors and use the CNF.UID field to see which REQ Descriptors have been consumed by the SI, incrementing the REQ queue's SQP when scanning through the REQ queue for matching UID values. See Figure 3-23 for the pseudo-code of this step.

To maintain a PSP Software Queue Pointer (SQP) the host must

- initialize the SQP and HQP with the same value (at power-up time)

- when consuming IDUD Descriptors increment the SQP when a page change is seen in the IDUs (input data buffers). See Figure 3-24 for the pseudo-code of this step.

```

#define BSIQ_NEXT_1K(p) ((((p) + 8) & 0x3ff) | ((p) & 0x0ffffc00)) #define BSIQ_NEXT_4K(p) ((((p) + 8) & 0xfff) | ((p) & 0x0ffff000)) /* increment a Software Queue Pointer q_ptr is 32 bit variable */ q_ptr = BSIQ_NEXT_4K(q_ptr);

```

FIGURE 3-22. C Preprocessor Macros for Incrementing Queue Pointers

```

Get CNF Descriptor

WHILE CNF QUEUE NOT EMPTY

Get REQ Descriptor (at SQP location)

WHILE REQ.UID = CNF.UID

<reclaim transmit request memory>

increment REQ queue's SQP

Get next REQ Descriptor (at SQP location)

END WHILE

Get next CNF Descriptor

END WHILE

```

FIGURE 3-23. Maintaining a SQP for a REQ Queue

FIGURE 3-24. Maintaining a SQP for a PSP Queue

# 4.0 SENDING A FRAME

The steps for producing a frame for transmission are:

- 1. Make sure REQ queue isn't full

- 2. Build the ODU(s)

- 3. Build the ODU Descriptor(s)

- 4. Produce a REQ Descriptor

- 5. Update the REQ queue's Queue Limit

# 4.1 Make Sure REQ Queue Isn't Full

The host may produce transmit requests faster than the network can service them (i.e., a heavily loaded network), so the host must make sure that is doesn't overlay previously produced REQ Descriptors before the SI has consumed them (the SI queues are circular). This is accomplished by doing a comparison between the Queue Limit and Software Queue Pointer. See the discussion on SI queues in Section 3.4 for information on how to detect the queue full condition.

# 4.2 Build the ODU(s)

If the SI is directly attached to system memory this step may not be necessary, since the SI can directly access the same memory that the host uses for system dependent data structures (i.e., mbufs/mclusters). (It may still be necessary for the device driver to provide FDDI and/or LLC/SNAP encapsulation, which may be placed in an ODU that is separate from the rest of the frame data.) If the SI is not directly attached to system memory, then the host must allocate one or more buffers (none of which may span across a four kb page boundary) and populate the ODU(s) with frame data.

# 4.3 Build the ODU Descriptor(s)

Each frame data buffer (ODU) must be "described" to the SI with an ODU Descriptor (ODUD). The ODUDs must be placed contiguously (back to back) in memory within a 4 kb page. When dealing with system dependent data structures some care must be taken to avoid asking the SI to read across a 4 kb page boundary when fetching frame data. For example, if a particular host buffer does span across a 4 kb page boundary then two ODUDs must be used to describe that buffer. See *Figure 4-1* for picture of how to configure ODUDs to handle this situation.

FIGURE 4-1. Two ODUDs Needed for a Buffer that Crosses a 4k Page Boundary

# 4.4 Produce A REQ Descriptor

At this point there exists one or more buffers of frame data and an array of ODUD Descriptors that define the address and length of each buffer (termed ODUs in the datasheet).

A REQ Descriptor must be created on a REQ queue that defines the address and frame count of the ODUD array. This completes the three level data structure. If the REQ Descriptor is marked as REQ.First or REQ.Only the host must configure the REQ.UID, REQ.CNFCLS, REQ.RQCLS and REQ.FC fields.

# 4.5 Update the REQ Queue's Queue Limit

The SI will not consume REQ Descriptors beyond the queue slot defined by the queue's Queue Limit. (Queue limits are updated via Limit RAM Operations (LMOP). LMOPs are described in Section 6.0, "Low Level Operations".) So the host must update the Queue Limit to denote how far in the queue the SI will progress. If the queue is quiescent, the act of updating the Queue Limit, located in the SI's internal Limit RAM, will "wake up" the Channel and cause the SI to start consuming REQ Descriptors. If the SI is already actively consuming REQ Descriptors from the queue, the newly queued REQ Descriptor will be automatically consumed.

# 5.0 RECEIVING A FRAME

The steps for consuming a frame that has been received from the network are:

- Collect the IDUD Descriptors that describe the next received frame

- 2. Check status fields in the last IDUD of those collected

- 3. Process the frame data

- 4. Reclaim Pool Space (receive data buffers)

- 5. Update the IDUD queue's Queue Limit

# 5.1 Collect the IDUD Descriptors that Describe the Next Received Frame

As a first step it is necessary to gather up all of the IDUD Descriptors that describe the next frame. This is necessary as the SI only includes status information in IDUDs with the "Last" bit set (IDUD.Only and IDUD.Last). As a general rule the host software should be capable of dealing with up to three IDUDs per frame. The host software should plan on handling three IDUDs per frame; even when operating the SI in "Frame per Page" mode. If buffers smaller than 4 kb are used (i.e., PSP.LOC points to an offset within a 4 kb page), then more than three IDUDs may be produced for a single frame.

It is possible for the host to detect an "end of queue" while collecting IDUDs. This can happen when the SI is in the process of receiving a frame and the host is asynchronously examining the queue. The host may either consider the queue as currently empty or wait for the frame reception to complete (note that IDUDs are produced after the corresponding part of frame data has been copied to memory). If the host considers the queue as empty in this situation and interrupts are used to trigger received frame processing, then the host should clear the attention only at the beginning of the Interrupt Service Routine (ISR) code (so that the frame reception in progress will not be missed). See *Figure 5-1* for a snapshot of an IDUD queue displaying this transient condition.

TL/F/12304-23

FIGURE 5-1. Frame Reception in Progress

# 5.2 Check Status Fields in the Last IDUD of Those Collected

The host must decide if the frame should be processed or "dropped". There are several status items in the IDUD that provide all of the information required to make this decision. These status indicators are only valid in an IDUD Descriptor with the Last bit set (IDUD.Last or IDUD.Only). The host should always check the following indicators.

- Indicate Status (IDUD.IS). This field must be examined to check for errors that may occur during frame reception.

- Valid Frame Check Sequence (VFCS). As the frame is being received a CRC calculation is done. If the calculated value doesn't agree with the FCS field of the frame, this bit in the IDUD will be zero to indicate a problem.

- Valid Data Length (VDL). This bit will be zero if a length problem has been detected (basically an odd number of FDDI symbols (kind of like 4 bit nibbles)).

- Terminating Condition (TC). This two bit field reports how

the received frame ended. The host must verify that the

frame ended with an FDDI Ending Delimiter. If the sending station isn't stripping the frame properly or if there is a

lot of noise on one of the links in the ring the frame may

be partially stripped. This fact is only recorded in this field

(just checking the IDUD.IS field isn't enough).

# 5.3 Process the Frame Data

Clearly this step is very system dependent. On some systems this may only involve the creation of a few mbufs and a scheduling of the protocol stack processing. On others the frame may need to be actively copied into different data structures.

# 5.4 Reclaim Pool Space (receive data buffers)

Again this is a fairly system dependent step. One thing is true in all cases, though; the host can be sure that the SI has finished using a receive buffer when an IDUD is consumed that refers to a new buffer. (Assuming that the host is processing the IDUD queue in a sequential manner.) The process of determining when the host has finished using a receive buffer is system dependent. Many systems use a mechanism in which frames are passed to upper level protocols and may be relinquished in an arbitrary order. Section 7.4, Reclaiming Receive Buffer Memory, presents a mechanism that deals with this situation by using buffer reference counts.

### 5.5 Update the IDUD Queue's Queue Limit

The SI will consider an IDUD queue as full when queue pointer/limit equality is detected. Therefore, the host should update the Queue Limit (in the SI's internal Limit RAM) to grant additional status space (i.e., queue slots) to the SI. This need not be done for each frame (it can be done as infrequently as almost once per queue wrap). For performance reasons, it is advantageous to delay this operation until many frames have been consumed by the host. An example of delaying Queue Limit updates can be found in the nf\_ret\_idud() routine of the SI Primitives. National Semiconductor makes the source code to these example routines available to National's FDDI customers.

### 6.0 LOW LEVEL OPERATIONS

At the lowest, most primitive level the host must be able to perform read and write operations to the SI's Control Bus Registers and memory that is accessible by both the host and the SI. These operations are highly system dependent. For example, the Control Bus Registers might be memory mapped in one implementation and reached via some form of programmed I/O in another system.

At the next higher level (where the host software has control) there are several low level operations.

- Pointer RAM Operations (PTOP)

- Limit RAM Operations (LMOP)

- · Mailbox definition

- · Reading the SI's silicon revision number

- Updating Conditional Control Bus Registers

- Updating "Stop Mode Only" Control Bus Registers

# 6.1 Pointer RAM Operations (PTOP)

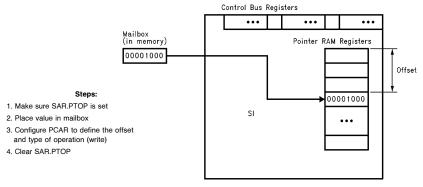

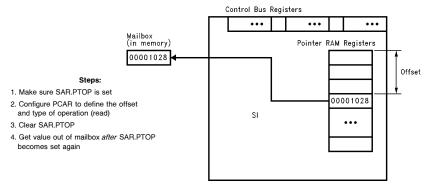

All Queue Pointers are maintained by the SI in Pointer RAM Registers that are internal to the chip. These registers are not directly accessible via the SI's Control Bus. Instead the host performs a Pointer RAM Operation (PTOP) to load or store one of the Pointer RAM Registers. The SI uses a special memory location (a 32-bit word termed the mailbox) to load and store 28-bit Pointer RAM Registers. The SI reads the mailbox when loading a Pointer RAM Register and writes to the mailbox when storing a Pointer RAM Register. The steps required to perform a PTOP are:

- make sure that the SAR.PTOP bit is asserted (SI able to do a PTOP)

- 2. if loading a register from memory, put the new value in the mailbox

- configure the Pointer Control and Address Register (PCAR) (defines load/store and which Pointer RAM Register)

- 4. clear the PTOP bit in the Service Attention Register (SAR.PTOP) (causes the SI to do the PTOP)

- 5. if storing a register to memory, when the SAR.PTOP bit becomes asserted get the value out of the mailbox.

It is not necessary to "baby-sit" the SI during a Pointer RAM Operation. This behavior can be used to reduce the cost of reading the Queue Pointers of REQ and PSP queues. It is possible to "schedule" a Pointer RAM "Read" Operation, go perform other work and detect the completion of the operation at a later time. Also, the act of detecting the completion of the PTOP can be made extremely efficient by preloading the mailbox location with a value of x'00000003' (an impossible value for Pointer RAM Registers) prior to starting the PTOP. This scheme avoids accessing the Service Attention Register (SAR); which, on most systems, is more ex-

pensive than accesses to shared memory. Seeing a value other than x'00000003' in the mailbox signifies that the operation has completed.

See Figures 6-1 and 6-2 for illustrations of the steps involved when loading a Pointer RAM Register from memory and when storing a Pointer RAM Register to memory.

FIGURE 6-1. Pointer RAM Operation ("Write") (Loading Register from Memory)

TL/F/12304-24

TL/F/12304-25

FIGURE 6-2. Pointer RAM Operation ("Read") (Storing Register Contents to Memory

21

# 6.2 Limit RAM Operations (LMOP)

The host maintains all Queue Limit values by updating the Limit RAM Registers that are internal to the SI. The host must perform a Limit RAM Operation (LMOP) to load or store one of the Limit RAM Registers. Limit RAM Operations are accomplished solely via the directly accessible Control Bus Registers. Two Control Bus Registers (8-bit) are needed to hold a Limit RAM Register value (9-bit). The steps required to perform an LMOP are:

- make sure that the SAR.LMOP bit is asserted (SI able to do an LMOP)

- configure the LAR (defines load/store, which Limit RAM Register and one bit of data)

- 3. if loading a register, configure the LDR (bottom 8 bits of the Limit RAM value)

- 4. clear the SAR.LMOP bit (causes the SI to do the LMOP)

- if reading a register, poll for the SAR.LMOP bit to become asserted and examine the LAR and LDR Control Bus Registers to get the Limit RAM value.

The act of updating Limit RAM Registers is done quite frequently by the host thus this operation should be coded as efficiently as possible. Limit RAM updates can be done with four accesses of the Control Bus. See *Figure 6-3* for a depiction of the relationship between the LAR, LDR and Limit RAM Registers. See *Figures 6-4* and *6-5* for illustrations of the steps involved in reading and writing to Limit RAM Registers. The "cost" of Limit RAM Operations is discussed in Section 7.5, Performance Issues.

FIGURE 6-3. How LAR and LDR Create a 9-Bit Value

Steps:

- 1. Make sure SAR.LMOP is set

- 2. Place lower 8 bits in LDR

- 3. Configure LAR to define the offset, type of operation (write) and top bit of value

- 4. Clear SAR.LMOP

TL/F/12304-26

FIGURE 6-4. Limit RAM Operation ("Write")

### Steps:

- 1. Make sure SAR.LMOP is set

- 2. Configure LAR to define the offset, type of operation (read)

- 3. Clear SAR.LMOP

- 4. After SAR.LMOP becomes set read LDR and LAR to get the value

TL/F/12304-28

FIGURE 6-5. Limit RAM Operation ("Read")

# 6.3 Reading the SI's Silicon Revision Number

All SIs contain a silicon revision number. This value can be obtained immediately after resetting the SI by:

- clearing the Pointer Control and Address Register (PCAR) Control Bus Register. This setp is important because the PCAR is not initialized to known values at reset time

- reading the Mailbox Address Register (MBAR) Control Bus Register four times.

A 32-bit revision number is returned in most significant byte order. This operation is typically done as part of the initialization of the SI. See Table 6-1 for a list of defined silicon revision numbers and how they correspond to the revisions of the SI.

TABLE 6-1. Correlation of Silicon Revision Numbers

| 10 01 101010               |                  |  |  |  |

|----------------------------|------------------|--|--|--|

| Silicon Revision<br>Number | SI Release Level |  |  |  |

| 0x0000004                  | BSI-1 Rev-B      |  |  |  |

| 0x0000004C                 | BSI-2 Rev B      |  |  |  |

| 0x0000054                  | MACSI Rev C      |  |  |  |

| 0x00000058                 | MACSI Rev D      |  |  |  |

# 6.4 Mailbox Definition

The mailbox location must be defined before any Pointer RAM Operations can be performed. The mailbox address is defined by:

- clearing the Pointer RAM Control and Address Register (PCAR) Control Bus Register. This step is important because the PCAR is not initialized to known values at reset time

- writing the Mailbox Address Register (MBAR) Control Bus Register four times to define a 28-bit address (most significant byte first).

This operation is typically done as part of the initialization of the SI.

# 6.5 Updating Conditional Control Bus Registers