# A Comparison of **Differential Termination Techniques**

National Semiconductor Application Note 903 Joe Vo August 1993

# INTRODUCTION

Transmission line termination should be an important consideration to the designer who must transmit electrical signals from any point A to any point B. Proper line termination becomes increasingly important as designs migrate towards higher data transfer rates over longer lengths of transmission media. However, the subject of transmission line termination can be somewhat confusing since there are so many ways in which a signal can be terminated. Therefore, the advantages and disadvantages of each termination option are not always obvious.

The purpose of this application note is to remove some of the confusion which may surround signal termination. This discussion, however, will focus attention upon signal termination only as it applies to differential data transmission over twisted pair cable. Common differential signal termination techniques will be presented and the advantages and disadvantages of each will be discussed.

Each discussion will also include a sample waveform generated by a setup consisting of a function generator whose signals are transmitted across a twisted pair cable by a differential line driver and sensed at the far end by a differential line receiver. This application note will specifically address the following differential termination options:

- Series/Backmatch

- Parallel

- AC

- Power (Failsafe)

- Alternate Failsafe

- Bi-Directional

For the purposes of discussion, popular TIA/EIA-422 drivers and receivers, such as the DS26LS31 and DS26LS32A, will be used to further clarify differential termination.

#### UNTERMINATED

The selection of one termination option over another is oftentimes dictated by the performance requirements of the application. The selection criteria may also hinge upon other factors such as cost. From this cost perspective the option of not terminating the signal is clearly the most cost effective solution. Consider Figure 1, where a DS26LS31 differential driver and a DS26LS32A differential receiver have been connected (using a twisted pair cable) together without a termination element. Because there is no signal termination element, the DS26LS31 driver's worst case load is the DS26LS32A receiver's minimum input resistance.

FIGURE 1. Unterminated Configuration

Since, TIA/EIA-422-A (RS-422) standard defines the DS26LS32A's minimum input resistance to be 4 k $\Omega$ , the driver's worst case load, as seen in Figure 1, is then 4 k $\Omega$ .

In the unterminated configuration, the DS26LS31 driver is only required to source a minimal amount of current in order to drive a signal to the receiver. This minimal DC current sourcing requirement in turn minimizes the driver's on chip power dissipation. In addition, the 4  $k\Omega$  driver output load results in a higher driver output swing (than if the driver was loaded with  $100\Omega$ ) which in turn increases DC noise margin. This increase in noise margin further diminishes the possibility that system noise will improperly switch the receiver. To be sure that there is no confusion, noise margin is defined as the difference between the minimum driver output swing and the maximum receiver sensitivity. On the other hand, if a receiver was used which complies to TIA/EIA-485 (RS-485), the resulting noise margin would be even greater. This is because the minimum input resistance of an RS-485 receiver must be greater than 12  $k\Omega$  as compared to 4  $k\Omega$  for an RS-422 receiver.

The absence of a termination element at the DS26LS32A's inputs also guarantees that the receiver output is in a known logic state when the transmission line is in the idle or open line state (receiver dependent). This condition is commonly referred to as open input receiver failsafe. This receiver failsafe (Note 1) bias is guaranteed by internal pull up and pull down resistors on the positive and negative receiver inputs, respectively. These pull up and pull down resistors bias the input differential voltage (V<sub>ID</sub>) to a value greater than 200 mV when the line is, for example, idle (un-driven). This bias is significant in that it represents the minimum guaranteed  $V_{\text{\scriptsize ID}}$ required to switch the receiver output into a logic high state.

Note: A complete discussion of receiver failsafe can be found in Application Note 847 (AN-847)

There are, however, some disadvantages with an unterminated cable. The most significant effect of unterminated data transmission is the introduction of signal reflections onto the transmission line. Basic transmission line theory states that a signal propagating down a transmission line will be reflected back towards the source if the outbound signal encounters a mismatch in line impedance at the far end. In the case of Figure 1, the mismatch occurs between the characteristic impedance of the twisted pair (typically  $100\Omega$ ) and the 4 k $\Omega$  input resistance of the DS26LS32A. The result is a signal reflection back towards the driver. This reflection then encounters another impedance mismatch at the driver outputs which in turn generates additional reflections back toward the receiver, and so on. The net result is a number of reflections propagating back and forth between the driver and receiver. These reflections can be observed in Figure 2.

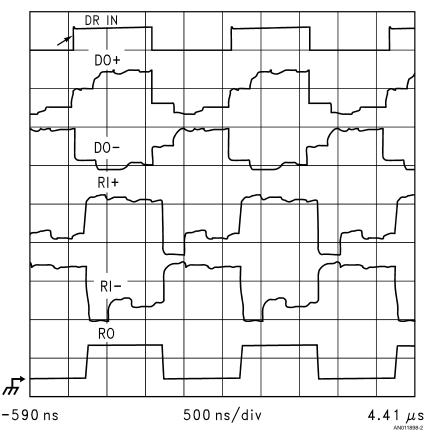

FIGURE 2. Unterminated Waveforms

The main limitation of unterminated signals can be clearly seen in Figure 2. A positive reflection is generated when the signal encounters the large input resistance of the receiver. These reflections propagate back and forth until a steady state condition is reached after several round trip cable delays. The delay is a function of the cable length and the cable velocity. Figure 2 shows that the reflections settle after three round trips. To limit the effect of these reflections, unterminated signals should only be used in applications with low data rates and short driving distances.

The data being transmitted should, therefore, not make any transitions until after this steady state condition has been reached. A low data rate ensures that reflections have sufficient time to settle before the next signal transition. At the same time, a short cable length ensures that the time required for the reflections to settle is kept to a minimum. The low data rate and short cable length dictated by the lack of termination is probably the most significant shortcoming of the unterminated option.

Low speed is generally characterized to be either signalling rates below 200 kbits/sec or when the cable delay (the time required for an electrical signal to transverse the cable) is substantially shorter than the bit width (unit interval) or when

the signal rise time is more than four times the one way propagation delay of the cable (i.e., not a transmission line). As a general rule, if the signal rise time is greater than four times the propagation delay of the cable, the cable is no longer considered a transmission line.

It should be mentioned that most differential data transmission applications provide for some kind of signal termination. This is because most differential applications transmit data at relatively high transfer rates over relatively long distances. In these type of applications, signal termination is critically important. If the application only requires low speed operation over short distances, an unterminated transmission line may be the simplest solution.

# SERIES TERMINATION

Another termination option is popularly known as either series or backmatch termination. Figure 3 illustrates this type of termination. The termination resistors,  $R_{\rm S}$ , are chosen such that their value plus the impedance of the driver's output equal the characteristic impedance of the cable. Now as the driven signal propagates down the transmission line an impedance mismatch is still encountered at the far end of the cable (receiver inputs).

FIGURE 3. Series Termination Configuration

However, when that signal propagates back to the driver the reflection is terminated at the driver output. There is only one reflection before the driven signal reaches a steady state condition. How long it takes for the driven signal to reach steady state is still dependent upon the length of cable the signal must traverse. As with the unterminated option the driver power dissipation is still minimized due to the light loading presented by the  $4\,\mathrm{k}\Omega$  receiver input resistance. The driver loading remains unchanged from the unterminated option. In both cases the driver is effectively loaded with the receiver's input impedance. DC noise margin has again increased and the open input receiver failsafe feature is still supported for idle and open line conditions.

There are three major disadvantages in using series termination. First, the driver output impedances can vary, due to normal process variations, from one manufacturer to another and from one driver load to another. Should there be a problem which involves replacing line drivers, there is a chance that the designer might have to rework the board in order to ensure that the  $R_{\rm S}$  matches the new driver's output impedance.

Second, series termination is commonly limited to only point to point applications. Consider the following example. If a second receiver (multidrop application) was located halfway between the driver and receiver at the far end of the cable, the noise margin seen by the middle receiver would change between the incident signal and the reflected signal. Such a problem would not exist in a point to point application where only one receiver is used with one driver.

Third, there is still an impedance mismatch at the receiver inputs. Again, this mismatch is caused by a signal propagating down a 100 $\Omega$  cable suddenly encountering a 4  $k\Omega$  receiver input resistance. This impedance mismatch will continue to cause reflections on the transmission line as illustrated in Figure 4.

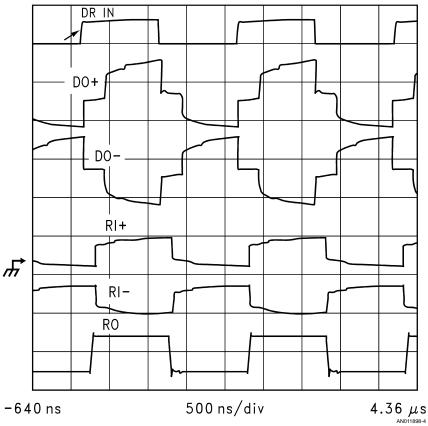

FIGURE 4. Series Termination Waveforms

Notice the reflections which result when the driven signal encounters an impedance mismatch at the receiver input. The reflection propagates back to the driver and is somewhat terminated by the driver's output impedance. The reflected signal is terminated because the combined impedance of the series resistor  $(R_{\rm S})$  and the driver's output impedance

comes close to matching the characteristic impedance of the cable. In contrast with  $Figure\ 2$ s unterminated signal waveform, the waveform seen in  $Figure\ 4$  is characterized by only one reflection.

In all it will take the signal one round trip cable delay to be reflected back towards the signal source. Since all reflections should be allowed to settle before the next data transition (to maintain data integrity), it is imperative that the round trip cable delay be kept much less than the time unit interval (TUI — defined to be the minimum bit width or the "distance" between signal transitions). In other words, series termination should be limited to applications where the cable lengths are short (to minimize round trip cable delays) and the data rate is low (to maximize the TUI). And to a lesser degree, the series termination option may not be the ideal choice from a cost perspective in that it requires two additional external components.

#### PARALLEL TERMINATION

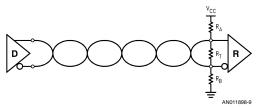

Parallel termination is arguably one of the most prevalent termination schemes today. In contrast to the series termination option, parallel termination employs a resistor across the differential lines at the far (receiver) end of the transmission line to eliminate all reflections. See *Figure 5*.

FIGURE 5. Parallel Termination Configuration

Eliminating all reflections requires that R<sub>T</sub> be selected to match the characteristic impedance  $(Z_{\text{O}})$  of the transmission line. As a general rule, however, it is usually better to select  $R_T$ such that it is slightly greater than  $Z_O$ . Over-termination tends to be more desirable than under-termination since over-termination has been observed to improve signal quality.  $R_{T}$  is typically chosen to be equal to  $Z_{O}.$  When over-termination is used R<sub>T</sub> is typically chosen to be up to 10% larger than  $Z_{\text{O}}$ . The elimination of reflections permits higher data rates over longer cable lengths. Keep in mind, however, that there is an inverse relationship between data rate and cable length. That is, the higher the data rate the shorter the cable and conversely the lower the data rate the longer the cable. Higher data rates and longer cable lengths translate simply into smaller TUI's and longer cable delays. Unlike series termination where high data rates and long cable lengths can negatively impact data integrity, parallel termination can effectively remove all reflections; thereby removing all concerns about reflections interfering with data transitions. See Figure 6.

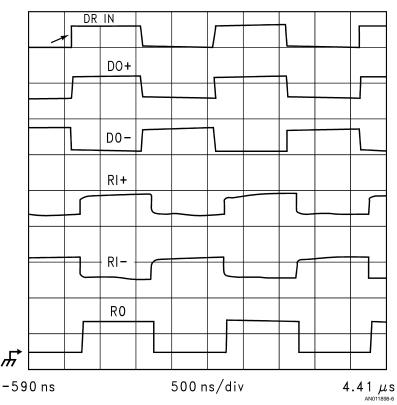

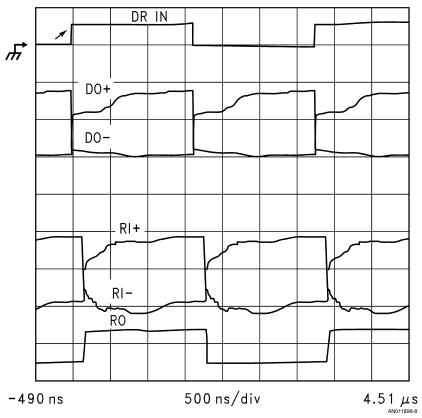

FIGURE 6. Parallel Termination Waveforms

As seen in *Figure 6* both driver output and receiver input signals are free of reflections. Such results make parallel termination optimal for use in either high speed (10 Mb/s), or long cable length (up to 4000 feet), applications.

Another benefit the parallel termination provides is that both point to point and multidrop applications are supported. Recall that multidrop is defined as a distribution system composed of one driver and up to ten receivers spread out along the cable as defined in the TIA/EIA-422 standard. The parallel termination is located at the far end (opposite the driver) of the cable and effectively terminates the signal at that location, preventing reflections.

There are also disadvantages to parallel termination. Let's examine these disadvantages as they pertain to multidrop configurations. An intrinsic assumption to multidrop operation is that stub lengths, as measured by "I" in  $Figure\ 5$ , are minimized. Despite the fact that all receivers are effectively terminated with  $R_{\tau_1}$  long stub lengths will once again reintroduce impedance mis-matches and reflections. So while parallel termination may remove reflections and permit multidrop configurations, it does place a restriction upon the stub lengths associated with these other receivers. Typically stubs should be kept to less that 1/4 of the drivers rise time in length to minimize transmission line effects, and reflections.

TIA/EIA-422-A standard does recommend a  $100\Omega$  resistor to be used when the differential line is parallel terminated. Therefore, applications which use a TIA/EIA-422-A driver such as the DS26LS31 or DS26C31 are commonly terminated.

nated with  $100\Omega$  at the far end of the twisted pair cable. While the  $100\Omega$  parallel termination eliminates all reflections, the power dissipated by the driver will increase substantially with the addition of this resistor. This increased driver power dissipation is a major disadvantage of parallel termination. The absence of this termination resistor keeps driver power dissipation low for unterminated and series terminated drivers and is a major advantage of these two termination options.

Noise margin will also decrease with parallel termination. The relatively light loading (4  $k\Omega$ ) of unterminated and series terminated drivers led to larger driver output swings. The heavier driver load (typically  $100\Omega$ ) brought on by parallel termination reduces the driver's output signal swing. However, even with this reduction, there is ample noise margin left to ensure that the receiver does not improperly switch.

Recall the discussion earlier about receiver failsafe with the unterminated and series options. In both cases, open input receiver failsafe operation was guaranteed because of internal circuitry (receiver dependent) which biases the differential input voltage ( $V_{\rm ID}$ ) to a value greater than its differential threshold. Since the resulting bias voltage at the receivers inputs ( $V_{\rm ID}$ ), is greater than +200 mV, the output of the DS26LS32A receiver remains in a stable HIGH state. Unlike unterminated and series options, parallel termination cannot support open input receiver failsafe when the transmission line is in the idle state. This shortcoming of parallel termination is discussed in much greater detail later in the section

which describes power and alternate failsafe termination (see AN-847 for more of information on failsafe biasing differential buses).

#### **AC TERMINATION**

The effectiveness of parallel termination is oftentimes countered by increased driver power dissipation and receiver failsafe concerns. The DC loop current required by the termination resistor, R<sub>T</sub> (see *Figure 5*), is often too large in order to be useful for power conscious applications or for seldomly switched control lines. In asynchronous applications, parallel termination's is not able to guarantee receiver failsafe during idle bus states which in turn makes the system susceptible to errors such as false start bits and framing errors. The primary reason for the AC termination, however, grew out of the need for effective transmission line termination with minimal DC loop current.

A representation of an AC terminated differential line is shown in  $\it Figure~7.$

FIGURE 7. AC Termination Configuration

The value of  $R_T$  generally ranges from  $100\Omega-150\Omega$  (cable  $Z_O$  dependent) and is selected to match the characteristic impedance  $(Z_O)$  of the cable.  $C_T,$  on the other hand, is selected to be equal to the round trip delay of the cable divided by the cable's  $Z_O.$

EQ1:  $C_T \le (Cable round trip delay) / Z_O$

For this example:

Cable Length = 100 feet Velocity = 1.7 ns/foot Char. Impedance =  $100\Omega$

Therefore,

$C_T \le (100 \text{ ft x 2 x 1.7 ns/ft})/100\Omega \text{ or } \le 3,400 \text{ pF}.$

Further, the resulting  $R_C$  time constant should be less than or equal to 10% of the unit interval (TUI). In the example provided the maximum switching rate therefore should be less than 300 kHz. This termination should now behave like a parallel termination during transitions, but yield the expanded noise margins during steady state conditions. See Figure 8.

Figure 8 illustrates the tradeoff between parallel terminated and unterminated signals. There are no major reflections and driver power dissipation is reduced at the expense of a low pass filtering effect which essentially limits the application of AC termination to low speed control lines. Note that the frequency of the driven signal in Figure 8 is 300 kHz whereas it was 500 kHz for the other plots. This was done to maintain the ratio between bit time and the  $\rm R_{\rm C}$  time constant. The draft revision of RS-422-A will include AC termination as an alternative to parallel termination.

FIGURE 8. AC Termination Waveforms

The waveforms in Figure 8 should be viewed together with the following brief explanation of how AC termination works. When the driven signal transitions from one logic state to another, the capacitor C<sub>T</sub> behaves as a short circuit and consequently, the load presented to the driver is essentially R<sub>T</sub>. However, once the driven signal reaches its intended levels, either a logic HIGH or logic LOW, C<sub>T</sub> will behave as an open circuit. DC loop current is now blocked. The driver power dissipation will then decrease. The load presented to the driver also decreases. This is due to the fact that the driver is now loaded with a large receiver input resistance typically greater than 4 k $\Omega$ ; versus the typical R $_{T}$  of 100 $\Omega$ -120 $\Omega$ . This reduced loading condition increases the signal swing of the driver and results in increased noise margin. The idle bus state also forces C<sub>T</sub> into the open circuit mode. Once this takes place, the receiver's internal pull up and pull down resistors will bias the output into a known state. Therefore, besides minimizing DC loop current, preventing line reflections, and increasing noise margin, AC termination also supports open input receiver failsafe.

As with all the previously discussed termination options, there are disadvantages in using AC termination. AC termination introduces a low pass filtering effect on the driven signal which tends to limit the maximum data rate of the application. This data rate limitation is the result of the impact that  $\rm R_T$  and  $\rm C_T$ , together, have upon the driven signal's rise time.

How much the data rate is limited is dependent upon the selection of  $\mathsf{R}_\mathsf{T}$  and  $\mathsf{C}_\mathsf{T}.$  Long  $\mathsf{R}_\mathsf{C}$  time constants will have a greater impact upon the driven signal's maximum data rate, and vice versa. Because of of these data rate limitations, the transmission lines best suited for AC termination are typically low speed control lines where level sensitivity is desired over edge sensitivity. Finally, the part count required by AC termination can put it at a disadvantage in cost conscious applications.

#### POWER TERMINATION

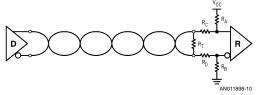

Recall that AC termination is intended primarily to eliminate the large DC loop current inherent in parallel termination. The power termination, on the other hand, addresses parallel termination's inability to support receiver failsafe during the idle bus state. See *Figure 9* for an illustration of a transmission line terminated using the power option.

FIGURE 9. Power Termination Configuration

The lack of  $R_{\rm A}$  and  $R_{\rm B}$ , when the bus is idle, almost assures that the receiver output will not be in a known state. This is due to the insufficient voltage across  $R_{\rm T}$  (on the order of 1 mV–5 mV) as caused by the receiver's internal high value pull up and pull down resistors. The presence of these internal pull up and pull down resistors will guarantee receiver failsafe only for the open input condition. In order to switch the receiver into the logic high state, regardless of whether the bus is open or idle, a minimum of +200 mV (with respect to the inverted receiver input) must be developed across  $R_{\rm T}$ . The sole purpose, then, of  $R_{\rm A}$  and  $R_{\rm B}$  is to establish a voltage divider whereby at least +200 mV will be dropped across  $R_{\rm T}$ . A complete explanation of selection criteria for resistor values ( $R_{\rm A}$  and  $R_{\rm B}$ ) can be found in AN-847.

The addition of external receiver failsafe biasing resistors, however, does pose some concerns. The primary drawback relates to the increased driver loading with the addition of  $R_{\rm A}$  and  $R_{\rm B}$ . The increased driver loading decreases the driver's output swing and, in turn, reduces the noise margin. Higher driver power dissipation is also symptomatic of the increased driver loading since the driver must source the additional current required by the external failsafe network. One last concern is that the extra cost and subsequent handling of two additional resistors (excluding  $R_{\rm T}$ ) might outweigh power termination's advantages in some applications.

# ALTERNATE-FAILSAFE TERMINATION

This version of failsafe termination is essentially an extension of power termination. The addition of  $R_{\rm C}$  and  $R_{\rm D}$  greatly enhances the receiver's ability to operate in harsher environments. See  $\it Figure~10$ .

FIGURE 10. Alternate Failsafe Termination Configuration

The advantages of this failsafe termination point directly to this increased ruggedness. A transmission line terminated using the failsafe option will be able to withstand larger common mode voltages. A careful selection of  $R_{\rm C}$  and  $R_{\rm D}$  will determine how much more common mode voltage a line can endure. This is because  $R_{\rm C}$  and  $R_{\rm D}$  act as a voltage dividers between the receivers input resistance. The TIA/EIA-422-A standard allows for common mode shifting up to 7V in magnitude, however most integrated circuits support absolute maximum rating that exceed the  $\pm$ TV limit. The DS26LS32A

supports a ±25V ABS MAX input rating. Careful selection of resistors can allow common mode voltages in the 35V–45V range on the cable, while still honoring the 25V limit in the receiver input pins.  $R_{C}$  and  $R_{D}$  are typically 4.7  $k\Omega,$  while  $R_{A}$  and  $R_{B}$  are 47  $k\Omega.$  This provides 9.5  $k\Omega$  between the receiver input pins, and also allows the pull up and pull down resistors to be increased in value to 47  $k\Omega.$  This capability lends itself well to applications, such as factory control and building to building data transmission, where the common mode range can occasionally exceed ±7V.

Failsafe termination also guarantees receiver failsafe for open, idle, as well as shorted line conditions. Of all the terminations options discussed, the failsafe option is the only one for which receiver failsafe can be guaranteed for shorted differential lines. Shorting the differential lines together merely shorts out  $R_{\rm T}$ . In this short condition, the receiver will still see the series combination of  $R_{\rm C}$  and  $R_{\rm D}$  across its inputs. Receiver failsafe can, therefore, still be supported. The short condition just described yields another benefit of failsafe termination. The increased impedance between  $V_{\rm CC}$  and ground, with the addition of  $R_{\rm C}$  and  $R_{\rm D}$ , also results in increased fault or short circuit current limiting.

While the addition of  $R_{C}$  and  $R_{D}$  improves the transmission line's ability to withstand larger common mode voltages, it might also negatively impact the receiver's sensitivity. Consider, for example, a TIA/EIA-422 receiver. The minimum differential input signal ( $V_{\rm ID}$ ) required to switch the receiver is normally |200 mV|. Depending on the values of  $R_{C}$  and  $R_{D}$ , it may be necessary to develop a minimum of +400 mV across  $R_{T}$  in order to ensure that there is at least 200 mV across the receiver input terminals. The other significant disadvantage with failsafe termination may be the number of resistors required to implement it. Five resistors per line may prove too costly.

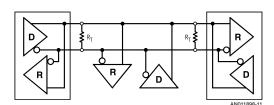

## **BI-DIRECTIONAL TERMINATION**

The last type of termination which will be discussed is known as bi-directional termination. Figure 11 illustrates a typically multipoint application composed of drivers, receivers, and transceivers. Bi-directional termination is parallel termination carried one step further. Bi-directional termination now permits multiple drivers (multipoint configuration) to be connected to the same twisted pair. With multiple drivers connected to the same twisted pair, data can now be transmitted in two directions. Keep in mind, however, that while data transmission can now take place in two directions, only half duplex transmission is allowed (as defined by TIA/EIA-485 standard). Multiple TIA/EIA-485 drivers cannot simultaneously drive the line since this would result in line contention. It should be mentioned that system timing should be carefully inspected to ensure that line contention does not occur. The advantages in using bi-directional termination are almost identical to those with parallel termination.

FIGURE 11. Bi-Directional Termination Configuration

These advantages include the prevention of signal reflections, and the ability to drive long transmission lines at high data rates. As with parallel termination,  $R_{\mathsf{T}}$  should be selected so that it matches the characteristic impedance  $(Z_{\mathsf{O}})$  of the twisted pair cable.

The disadvantages in using parallel termination also extend to bi-directional termination. Receiver failsafe cannot be guaranteed due to the interaction between R<sub>T</sub> and the receiver's open circuit failsafe network. Stub lengths must be minimized and an R<sub>T</sub> must each be placed at both extreme ends of the line in order to minimize transmission line effects. However, when two termination resistors are placed at the far ends of the cable, the effective load of the driver is now  $60\Omega$  (since R<sub>T</sub> is typically  $120\Omega$ ). This "doubling" of the driver load, using bidirectional termination, has two effects. First, it places a greater demand upon the driver's ability to source current. As described above, a multipoint driver must be able to source approximately twice the amount of current that is required from a multidrop driver. A driver expected to meet this increased current demand naturally experiences greater power dissipation. And second, noise margin tends to be reduced since the driver's output levels tend to decrease with increased loading.

#### CONCLUSION

The advantages and disadvantages of unterminated lines and those with series, parallel, AC, power, failsafe, and bi-directional terminations were contrasted. It should now be clear that there is no one termination scheme which is suited for all applications. *Table 1* provides a summary of the differential termination options discussed in this application note.

**TABLE 1. Termination Summary**

| Signal    | Data                               | Comments                                                                 |

|-----------|------------------------------------|--------------------------------------------------------------------------|

| -         |                                    | Commonto                                                                 |

|           |                                    | Law Dawar                                                                |

| Poor      | Low                                | Low Power                                                                |

| Good      | Low                                | Low Power                                                                |

| Excellent | High                               | Single Resistor                                                          |

| Good      | Med.                               | Ideal for use on                                                         |

|           |                                    | control lines                                                            |

| Excellent | High                               | Failsafe bias for idle                                                   |

|           |                                    | line                                                                     |

| Excellent | High                               | Failsafe for open,                                                       |

|           |                                    | shorted, and idle                                                        |

|           |                                    | lines                                                                    |

| Excellent | High                               | Ideal for                                                                |

|           |                                    | bidirectional half                                                       |

|           |                                    | duplex operation                                                         |

|           | Excellent Good Excellent Excellent | OualityRatePoorLowGoodLowExcellentHighGoodMed.ExcellentHighExcellentHigh |

The termination scheme used will essentially be dictated by the needs of the system. Specifically, the choice of termination will depend upon the system's data transmission requirements.

#### SPECIAL NOTES

The waveforms illustrated in this application note were acquired from laboratory testing of TIA/EIA-422 (RS-422) Drivers, and Receivers under the following conditions:

- DS26LS31 Quad Differential Driver

- DS26LS32A Quad Differential Receiver

- Cable = 100', 24AWG, 100Ω, twp cable (Berk-Tek #520382)

- Driver input signal with f = 500 kHz,

$$V_{IH} = 3.0V$$

,  $V_{IL} = 0V$ ,

Duty cycle = 50%

- V<sub>CC</sub>= 5.0V

- T<sub>A</sub>= 25°C

The cable selected for this testing was supplied by Berk-Tek Inc. and represents a typical twisted pair cable commonly used in TIA/EIA-422 applications. Additional information on cables can be obtained from:

Berk-Tek Inc.

132 White Oak Road

New Holland, PA 17557

(717) 354-6200

The RS-422-A standard was developed by the Technical Recommendation (TR30.2) TIA/EIA committee on DTE-DCE Interfaces. Since publication of the revision A, the EIA (Electronic Industries Association) has aligned with the TIA (Telecommunications Industry Association), and future revisions and new standards carry the TIA/EIA prefix, replacing the familiar "RS" (for Recommended Standard) prefix. Revision "B" of RS-422-A is expected in late 1993, and will become TIA/EIA-422-B.

#### **REFERENCES**

Transmission Line Characteristics,

B. Fowler, National Semiconductor, Application Note AN-108.

Data Transmission Lines and Their Characteristics,

K. True, National Semiconductor, Application Note AN-806.

Reflections: Computations and Waveforms, K. True,

National Semiconductor, Application Note AN-807.

FAILSAFE Biasing of Differential Buses,

J. Goldie, National Semiconductor, Application Note AN-847.

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 1 80-530 85 86 Fax: +49 (0) 1 80-530 85 86

Email: europe support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group

Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5620-6175 Fax: 81-3-5620-6179