# Understanding the NS32GX320 Timers

National Semiconductor Application Note 696 Zeev Bikowsky August 1990

Inderstanding the NS32GX320 Timers

## INTRODUCTION

The NS32GX320 contains a set of three programmable timers. Each timer can operate in one of three optional modes. The NS32GX320 timers are very important for real time application. Integrating them on-chip reduces the chip count in the user board.

This application note describes how to program the NS32GX320 internal timers to work with the three basic modes of operation. It contains an example of one of many ways a user can program the three timers. This example and variations on it may be used when programming the timers for a specific application.

## TIMER DESCRIPTION

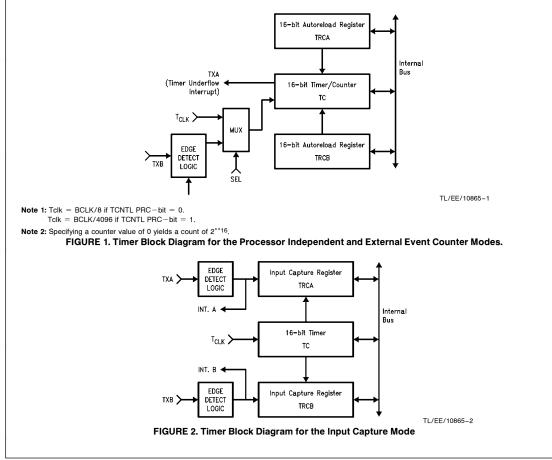

The NS32GX320 provides three on-chip timer blocks. Since these blocks are identical, the descriptions that follow are equally applicable to any of them. Each timer block consists of a 16-bit counter (TC), a control register (TCNTL) and two support registers (TRCA and TRCB). Two external signals (TXA and TXB) for each block handle all the interactions with external logic.

Following are the important fields of the TCNTL:

IPFB Interrupt Pending Flag B.

IENA Interrupt Enable Bit A. When set to 1, enables the interrupts from IPFA, if Mode 3 is selected, it enables the interrupts from TCS as well.

IPFA Interrupt Pending Flag A.

- TCS Timer control and status. In mode 1 or 2, this bit is used to start and stop the timer. The timer starts when TCS is 1. In mode 3, TCS is the underflow interrupt pending flat.

- TMC Timer Mode Control. This three-bit field selects the timer mode of operation. (See Table I)

- PRC Prescaler Control. Used only in modes 1 and 3. PRC controls the frequency of the timer input clock (TCLK). When PRC = 0, TCLK = BCLK/8, when PRC = 1, TCLK = BCLK/4096.

Each timer can operate in one of three modes (Table I): 1. Processor independent

- 2. External event counter

- 2. External event count

- 3. Input capture

| TABLE I. Timer Modes                                                             |                                    |                                          |                       |                    |  |  |

|----------------------------------------------------------------------------------|------------------------------------|------------------------------------------|-----------------------|--------------------|--|--|

| TMC Field                                                                        | Timer Mode                         | Interrupt A<br>Source                    | Interrupt B<br>Source | Timer<br>Counts On |  |  |

| 000                                                                              | IDLE                               | _                                        | _                     | _                  |  |  |

| 001                                                                              | MODE<br>(Processor Independent)    | Autoreload<br>TRCA                       | Autoreload<br>TRCB    | Tclk               |  |  |

| 010                                                                              | MODE 2 (External<br>Event Counter) | Autoreload<br>TRCA                       | Autoreload<br>TRCB    | TXB<br>Rising Edge |  |  |

| 100 MODE 3 (Input Capture)<br>Captures on:<br>TXA Rising Edge<br>TXB Rising Edge |                                    | TXA Rising<br>Edge or Timer<br>Underflow | TXB Rising<br>Edge    | Tclk               |  |  |

**AN-696**

©1995 National Semiconductor Corporation TL/EE10865

RRD-B30M75/Printed in U. S. A.

IENB Interrupt Enable Bit B. When set to 1, enables the interrupts from IPFB.

Following is a detailed description of the three timer processor modes.

#### PROCESSOR INDEPENDENT MODE (Mode 1)

This mode can be used to generate an output signal with minimal software intervention. The software only needs to define the ON and OFF times for the waveform to be generated. Once started, the timer will generate a periodic waveform without further intervention, except when the parameters need to be updated.

In this mode the timer counts down at the Tclk rate. Upon the occurrence of every underflow the timer is alternately reloaded with the contents of one of the support registers TRCA or TRCB. The first timer underflow causes a reload from the TRCA register. Reloads from subsequent underflows alternate from the two support registers, starting with TRCB. Each underflow toggles the TXA output pin.

Timer underflows are alternately latched into the IPFA and IPFB flags. The software is responsible for resetting these flags. Two enable bits, IENA and IENB, allow timer underflow interrupts to be enabled or disabled. Setting the IENA bit will cause an interrupt when a timer underflow causes a reload from TRCA, while setting IENB will cause an interrupt when the reload is from TRCB.

The IENA and IENB bits give the user the flexibility to enable or disable interrupts on either or both edges of the timer output waveform.

### EXTERNAL EVENT COUNTER MODE (Mode 2)

This mode is similar to the processor independent mode. The difference being that the timer is clocked by the rising edge of the signal applied on the TXB input pin.

#### INPUT CAPTURE MODE (Mode 3)

This mode allows the user to perform precise measurements of external frequencies and to time external events. The timer constantly runs at the Tclk rate. The registers TRCA and TRCB act as capture registers and are controlled

by external signals applied on the TXA and TXB pins. The timer value gets copied into the corresponding register

when a trigger event is signaled on either TXA or TXB. A trigger event is specified as a rising edge of the input signal. Trigger events can be programmed to generate interrupts. The occurrence of a trigger event on either TXA or TXB will be latched to IPFA or IPFB respectively. Interrupts are controlled by the setting of IENA and IENB.

Timer underflows can also generate interrupts. Since the underflow interrupt pending flag TCS has a different function in the other timer modes, the software should always reset it when the Input Capture Mode is selected. Timer underflow interrupts are also enabled by the IENA bit. Therefore, when IENA is set to 1 and interrupt occurs, both IPFA and TCS should be checked to determine the origin of the interrupt.

#### PROGRAMMING THE TIMER MODES

This section presents three examples of how to program the timers to function in different modes. Example 1 shows how Timer 0 may be programmed to function in mode 1 (Processor Independent). Example 2 shows how Timer 1 may be programmed to function in mode 2 (External Event Counter). Example 3 shows how Timer 2 may be programmed to function in mode 3 (Input Capture).

Note that these examples are not restricted to the specific instances described here. Thus the code for programming Timer 0 to function in mode 1 may also be used to program Timer 1 and 2 to function in the same mode. The same holds true for the code for programming the other modes.

*Example 1: Programming Processor Independent Mode.* This example programs Timer 0 to function in mode 1 (Processor Independent).

The code below loads values to TC, TRCA and TRCB to generate a pulse width modulation where high time is 8 cycles and low time is 16 cycles (a precise description of high\_0 and low\_0 for this example follow the code listing). The timer begins executing after the TCNTL register is loaded. When this happens, the TXA0 pin toggles from high to low.

Note that this example causes interrupts to be disabled because IENA and IENB are cleared in the TCNTL register.

```

.set high_0, h'0000001  #high time will be 8 cycles

.set low_0, h'0000002  #low time will be 16 cycles

.set tc_0, h'fffff810  #timer 0 counter

.set trcb_0, h'fffff818  #timer 0 reload register a

.set tcnt_0, h'fffff818  #timer 0 reload register b

.set tcnt_0, h'fffff81c  #timer 0 control register

.text

initialize:

```

lprd cfg ,\$h'af0

lprd psr ,\$h'0

start\_0:

| movw | \$high_0        | ,@tc_0   | #initialize timer counter tc               |

|------|-----------------|----------|--------------------------------------------|

| movw | \$low_0         | ,@trca_0 | #initialize trca register                  |

| movw | \$high_0        | ,@trcb_0 | #initialize trcb register                  |

| movw | \$h <b>'</b> 30 | ,@tcnt_0 | #set control register to mode 1            |

|      |                 |          | <pre>#no interrupts, timer frequency</pre> |

|      |                 |          | #is bclk/8                                 |

#register.

#register

#initialize configuration

#programming timer 1

#initialize processor status

| A Descrir                                                                                                            | otion of the high-low parame          | eters:                                                       | Example 2: Programming External Event Counter Mode.                                                                                                                                                                                  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| high_0 Specifies the value which will be loaded to register.<br>This value specifies the high time that TXA stay in. |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       | gh time that TXA0 will                                       | The code below loads values for the TC, TRCA and TRCB to generate a pulse width modulation. This mode is similar                                                                                                                     |  |  |

| low_0                                                                                                                | Specifies the value which v register. | will be loaded to TRCA                                       | to the processor independent mode. The only difference is<br>that the timer is clocked by the rising edge of the signal                                                                                                              |  |  |

|                                                                                                                      | This value specifies the lo stay in.  | w time that TXA0 will                                        | applied on the TXB1 input pin. A precise description of high_1 and low_1 for this example follows the code listing.                                                                                                                  |  |  |

|                                                                                                                      |                                       |                                                              | The timer begins executing after the TCNTL register is load-<br>ed. When this happens, the TXA1 pin toggles from high to<br>low, the high time becomes one rising edge of TXB1 and the<br>low time becomes two rising edges of TXB1. |  |  |

|                                                                                                                      |                                       |                                                              | Note that this example causes interrupts to be disabled be-<br>cause IENA and IENB are cleared in the TCNTL register.                                                                                                                |  |  |

|                                                                                                                      | high_1, h'00000001                    | #high time 1 risi                                            |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      | c_1, h'fffff820                       | #low time 2 rising edges<br>#timer 1 counter                 |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      | crca_1, h'fffff824                    | #timer 1 reload register a                                   |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      | rcb_1, h'fffff828                     |                                                              | #timer 1 reload register b                                                                                                                                                                                                           |  |  |

|                                                                                                                      | cent_1, h'fffff82c                    | #timer 1 control register                                    |                                                                                                                                                                                                                                      |  |  |

| start_                                                                                                               | .1:                                   | #programming time                                            | or 1                                                                                                                                                                                                                                 |  |  |

|                                                                                                                      | <pre>\$high_l ,@tc_l</pre>            | #initialize timer counter tc                                 |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      | <pre>\$low_l ,@trca_l</pre>           | #initialize trca register                                    |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      | \$high_1 ,@trcb_1                     | #initialize trcb register<br>#set control register to mode 2 |                                                                                                                                                                                                                                      |  |  |

| movw                                                                                                                 | \$h'50 ,@tcnt_1                       | #set control regi<br>#no interrupts, t                       |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       | #is external                                                 | imei iledneuch                                                                                                                                                                                                                       |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

|                                                                                                                      |                                       |                                                              |                                                                                                                                                                                                                                      |  |  |

A Description of the high-low parameters: Example 3: Input Capture Mode. high\_1 Specifies the value which will be loaded to TRCB This example programs Timer 2 to function in mode 3 (Input Capture). register. This value is the number of rising edges of TXB1. The code below initializes values for the TC, TRCA and TRCB. On each rising edge of TXA2, TRCA will be loaded It specifies the high time that TXA1 will stay in. with the content of the TC. On each rising edge of TXB2, Specifies the value which will be loaded to TRCA low\_1 TRCB will be loaded with the content of the TC. register. The timer begins executing after the TCNTL register is load-This value is the number of rising edges of TXB1. ed. It specifies the low time that TXA1 will stay in. Also note that this example causes interrupts to be disabled because IENA and IENB are cleared in the TCNTL register. .set tc\_2, h'fffff830 #timer 2 counter .set trca\_2, h'fffff834 #timer 2 reload register a .set trcb\_2, h'fffff838 #timer 2 reload register b .set tcnt\_2, h'fffff83c #timer 2 control register start\_2: #programming timer 2 movw \$h'100 ,@tc\_2 #initialize timer counter tc movw \$h'0 ,@trca\_2 #initialize trca register movw \$h'0 ,@trcb\_2 #initialize trcb register movw \$h'80 ,@tcnt\_2 #set control register to mode 3 #no interrupts, timer frequency #is bclk/8

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.