# Layout Recommendations for a System Using National's FDDI Chip Set

National Semiconductor Application Note 674 Bruce Wolfson January 1991

This application note covers basic PCB layout recommendations and design techniques for high speed signal distribution in National's FDDI system. Due to the high signal speeds in FDDI, proper layout is critical. Many digital designers are not aware of problems that can arise in a high speed system from improper routing, incorrect termination, and poor power and ground layout.

# ROUTING

Line reflections are a reflection of the signal waveform in a transmission line. They are caused by a difference in impedance between the transmission line and the load at the end of the line. If the line propagation delay is small compared to the rise time of the signal, the reflection is hidden during the rise time and is not seen as overshoot or ringing. However with the fast edge rates of the signals in a FDDI system, the line length becomes critical. The distortion that results from reflections can give false triggering or data errors. The signals most susceptible to reflections in a FDDI system are

the differential ECL signals. In National's FDDI chip set these include the following:

- 125 MHz and 12.5 MHz ECL clocks from the DP83241 (CDDTM device)

- Receive Data and Receive Clock from the DP83231 (CRD™ device)

- · Data to and from the fiber optic transceiver, and

- Loopback data from the DP83251/55 (PLAYER™ device)

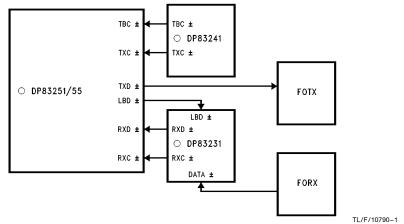

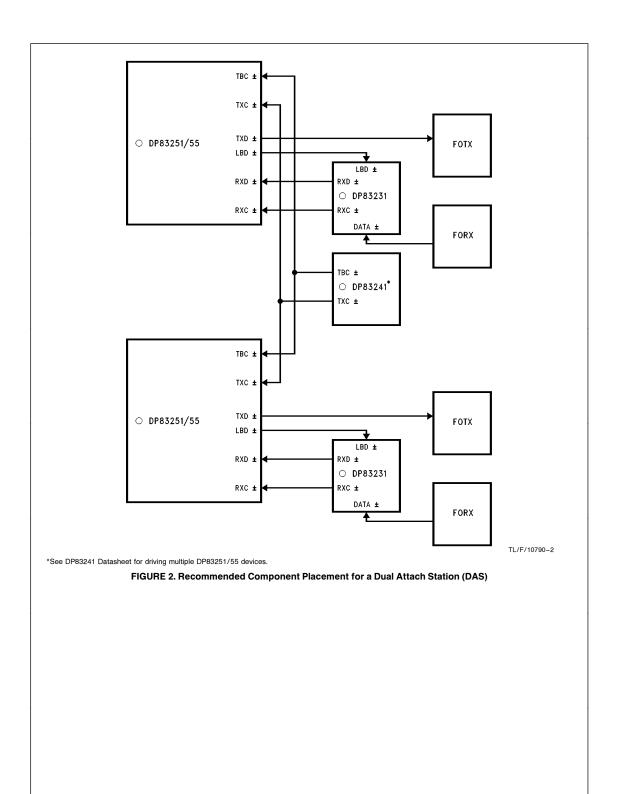

It is imperative that these signal lines be kept as short as possible. To achieve this, the DP83241 should be placed close to the DP83251/55, the DP83231 should be placed close to the fiber optic receiver and the DP83251/55, and the fiber optic transmitter should be placed close to the DP83251/55 (*Figures 1* and 2). The pinout of the DP83251/55 (*Figures 1* and 2). The pinout of the PLAYER device determines the placement of the CDD and CRD devices. All the ECL signals that travel between these devices line up perfectly. To keep the ECL signals traveling between these three devices as short as possible, the CDD and CRD devices should be oriented with pin 1 facing the

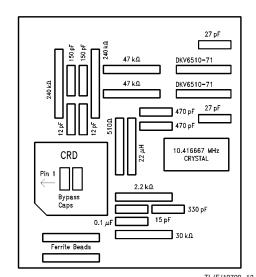

FIGURE 1. Recommended Component Placement for a Single Attach Station (SAS)

PLAYER™, BMAC™, CDD™ and CRD™ are trademarks of National Semiconductor Corporation

PLAYER device. In addition, the PLAYER device must have its ECL signals facing toward the fiber optic transceiver.

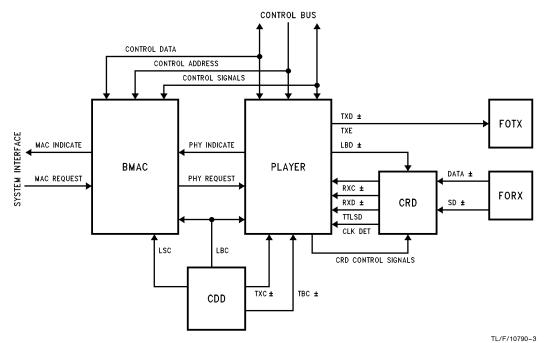

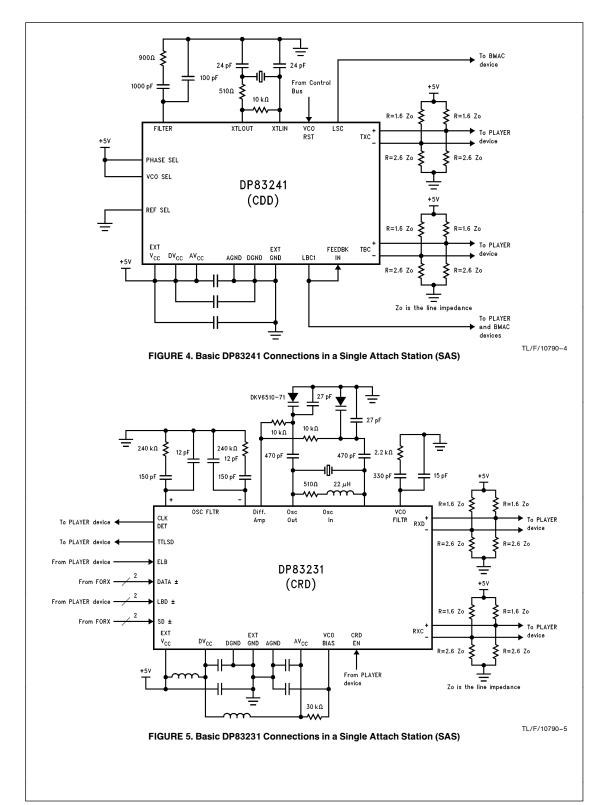

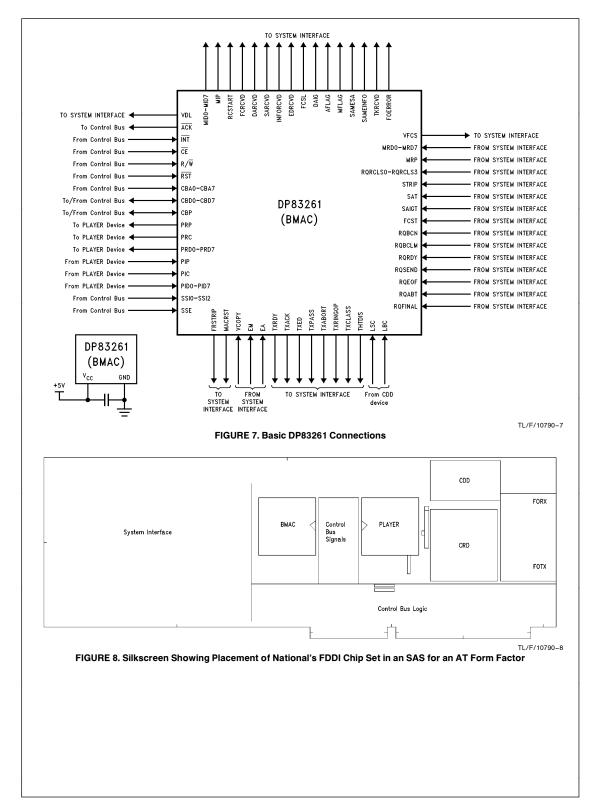

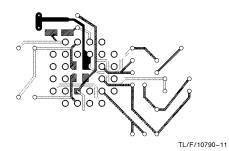

A Single Attach Station (SAS) in an AT form factor was chosen to demonstrate recommended chip placement and signal routing. *Figures 3* through 7 show the basic connections between National's FDDI chips in a Single Attach Station. The silkscreen showing chip and component placement is shown in *Figure 8* and the actual signal traces are shown in *Figure 9*. The FOTX and FORX placement is set by the PMD specification. The CDD, CRD and PLAYER devices should be placed as described in the previous paragraph. However, due to the constraints of the AT form factor, it is necessary to rotate the CDD device and its external components 90 degrees counter clockwise. The only remaining chip to be placed was the DP83261, BMAC™ device. Once again the form factor determined the placement,

but the orientation was chosen to allow an easy connection to the system interface, the control logic and the PLAYER device. Since the system interface logic is on the end of the board opposite the fiber optic transceiver, it was logical to have these signals facing that end of the board. It also allowed the control signals of the BMAC device to be near the control signals of the PLAYER device. All the TTL signals in this design can be autorouted. However, none of these signals should pass through the CDD or CRD device circuitry areas to avoid the possibility of noise due to crosstalk. In a Dual Attach Station (DAS) or a Concentrator design, the CRD device should still be placed as close as possible to the PLAYER device but the one CDD device responsible for clocking all the PLAYER and BMAC devices should be placed so as to minimize the skews between each PHY layer. More information regarding the CDD device driving multiple PLAYER devices can be found in the DP83241 datasheet.

FIGURE 3. Basic Block Diagram of a Single Attach Station Using National's FDDI Chips

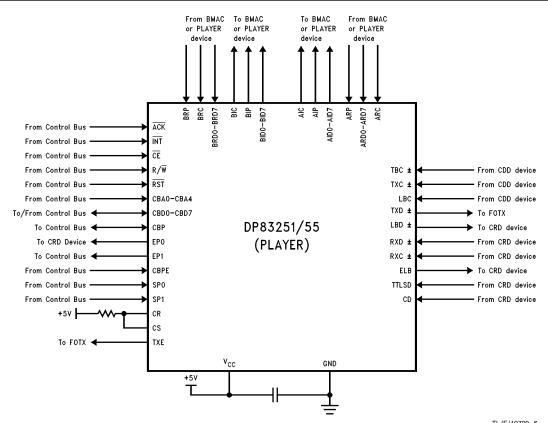

FIGURE 6. Basic DP83251/55 Connections for either an SAS or DAS

TL/F/10790-6

# **TERMINATION**

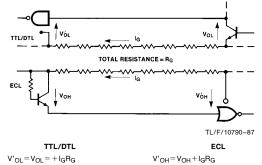

In addition to keeping the ECL signal traces as short as possible to avoid reflections, it is necessary to properly terminate all of the ECL signal traces. If the ECL signals are not properly terminated, line reflections will occur. There are several methods for terminating signal traces but it is recommended that a Thevenin equivalent of the proper parallel termination be used. This method has the advantages of using a single power supply voltage and providing a pulldown resistor for the driver circuit.

Reflections occur not only from mismatched load and source impedances but also from changes in line impedance. The impedance of a signal trace can be set to a fairly accurate degree by setting the trace width to a particular value. The equation in Appendix B, System Considerations,

shows how the line impedance is determined by the dielectric constant of the PCB, the thickness of the trace, the width of the trace and the distance of the trace from the ground plane. The dielectric constant will vary depending on the board manufacturer that is being used, so it is advisable to get this information from the board manufacturer before the ECL signals are routed. In an attempt to prevent line reflections, sharp bends (changes in the characteristic impedance) in the signal line should be avoided. It is recommended that all bends in high speed signal traces be fortyfive degrees or less. More information on reflections and termination schemes can be found in Appendix A, Transmission Line Concepts, and Appendix B, System Considerations.

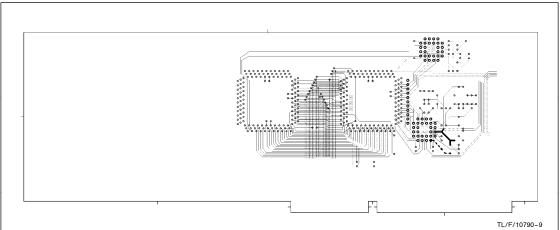

FIGURE 9. Signal Traces Connecting National's FDDI Chip Set in an SAS for an AT Form Factor

TL/F/10790-10

TL/F/10790-12

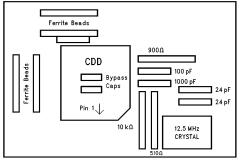

FIGURE 8a. Close Up of Silkscreen for CDD and CRD

Portion of Figure 8

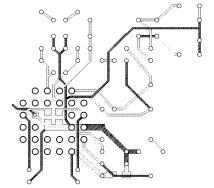

$$^{\rm TL/F/10790-13}$$  FIGURE 9a. Close Up of Signal Traces for CDD and CRD Portion of Figure 9. Black traces represent the component side signal layer and the shaded traces represent the solder side signal layer.

# **POWER AND GROUND**

In the design of a system, most people concern themselves with the layout of the signal lines and components and not with the ground and power layout. In high speed design, the shortest ground return path and the least inductive ground help maintain large signal noise margins. A common technique used to reduce ground noise is to create separate ground islands that are connected at only one point on the board. This point, at which the ground islands should connect is where the ground enters the PCB. The goal of this technique is to separate the noise on the ground plane, due to high current switching devices, from the parts which are susceptible to noise. Since voltage is equal to the inductance multiplied by the change in current divided by the change in time, a high current switching device will affect the noise margin of a signal. It is not necessay to create different ground islands for each part but only to create a separate ground island for the high current switching devices such as line or bus drivers. In the Single Attach Station design example described earlier in this application note there was a ground plane with no islands. The only exceptions to this involved some ground pins on the CDD and CRD devices. These connections are explained in the recommended layout sections of their datasheets.

The ground return path should be kept as short as possible by keeping the ground for an output device and the load (termination) on the same ground island. High speed signals should not be routed across different ground islands since a change in impedance will occur from the break in the ground planes. Ground should be routed on signal layers between signals that run parallel to each other for long distances

Proper power supply bypassing is also recommended so that  $V_{CC}$  levels are not reduced when a sudden switch in current occurs. This reduction of  $V_{CC}$  will not be global, but instead localized and could affect the noise margin of a signal.

Remember that in ECL design,  $V_{CC}$  is connected to a logic ground but is actually the highest voltage level. The  $V_{EE}$  supply level should be treated as the ground and  $V_{CC}$  as the power supply when using National's FDDI chip set since it uses positive referenced ECL signals rather than negative. More information on power and ground can be found in Appendix C, Power Distribution and Thermal Considerations.

# APPENDIX A ECL DESIGN GUIDE: TRANSMISSION LINE CONCEPTS

#### INTRODUCTION

The interactions between wiring and circuitry in high-speed systems are more easily determined by treating the interconnections as transmission lines. A brief review of basic concepts is presented and simplified methods of analysis are used to examine situations commonly encountered in digital systems. Since the principles and methods apply to any type of logic circuit, normalized pulse amplitudes are used in sample waveforms and calculations.

#### SIMPLIFYING ASSUMPTIONS

For the great majority of interconnections in digital systems, the resistance of the conductors is much less than the input and output resistance of the circuits. Similarly, the insulating materials have very good dielectric properties. These circumstances allow such factors as attenuation, phase distortion, and bandwidth limitations to be ignored. With these simplifications, interconnections can be dealt with in terms of characteristic impedance and propagation delay.

#### **CHARACTERISTIC IMPEDANCE**

The two conductors that interconnect a pair of circuits have distributed series inductance and distributed capacitance between them, and thus constitute a transmission line. For any length in which these distributed parameters are constant, the pair of conductors have a characteristic impedance Z<sub>0</sub>. Whereas quiescent conditions on the line are determined by the circuits and terminations, Z<sub>0</sub> is the ratio of transient voltage to transient current passing by a point on the line when a signal charge or other electrical disturbance occurs. The relationship between transient voltage, transient current, characteristic impedance, and the distributed parameters is expressed as follows:

$$\frac{V}{I}=Z_0=\sqrt{\frac{L_0}{C_0}} \tag{eq. 1} \label{eq:Variation}$$

where  $L_0=$  inductance per unit length,  $C_0=$  capacitance per unit length.  $Z_0$  is in ohms,  $L_0$  in Henries,  $C_0$  in Farads.

# PROPAGATION VELOCITY

Propagation velocity  $\nu$  and its reciprocal, delay per unit length  $\delta,$  can also be expressed in terms of  $L_0$  and  $C_0.$  A consistent set of units is nanoseconds, microhenries and picofarads, with a common unit of length.

$$\nu = \frac{1}{\sqrt{L_0 C_0}} \qquad \delta = \sqrt{L_0 C_0} \tag{eq. 2}$$

Equations 1 and 2 provide a convenient means of determining the  $L_0$  and  $C_0$ , of a line when delay, length and impedance are known. For a length / and delay T,  $\delta$  is the ratio T//. To determine  $L_0$  and  $C_0$ , combine Equations 1 and 2.

$$L_0 = \delta Z_0 \tag{eq. 3}$$

$$C_0 = \frac{\delta}{Z_0} \tag{eq. 4}$$

More formal treatments of transmission line characteristics, including loss effects, are available from many sources.1-3

# **TERMINATION AND REFLECTION**

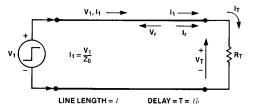

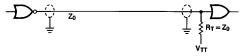

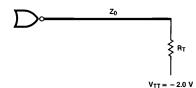

A transmission line with a terminating resistor is shown in Figure 1. As indicated, a positive step function voltage travels from left to right. To keep track of reflection polarities, it is convenient to consider the lower conductor as the voltage reference and to think in terms of current flow in the top conductor only. The generator is assumed to have zero internal impedance. The initial current  $I_1$  is determined by  $V_1$  and  $Z_{\Omega}$ .

TL/F/10790-14

# FIGURE 1. Assigned Polarities and Directions for Determining Reflections

If the terminating resistor matches the line impedance, the ratio of voltage to current traveling along the line is matched by the ratio of voltage to current which must, by Ohm's law, always prevail at  $R_{\rm T}$ . From the viewpoint of the voltage step generator, no adjustment of output current is ever required; the situation is as though the transmission line never existed and  $R_{\rm T}$  had been connected directly across the terminals of the generator. From the  $R_{\rm T}$  viewpoint, the only thing the line did was delay the arrival of the voltage step by the amount of time T.

When  $R_T$  is not equal to  $Z_0$ , the initial current starting down the line is still determined by  $V_1$  and  $Z_0$  but the final steady state current, after all reflections have died out, is determined by  $V_1$  and  $R_T$  (ohmic resistance of the line is assumed to be negligible). The ratio of voltage to current in the initial wave is not equal to the ratio of voltage to current demanded by  $R_T$ . Therefore, at the instant the initial wave arrives at  $R_T$ , another voltage and current wave must be generated so that Ohm's law is satisfied at the line-load interface. This *reflected* wave, indicated by  $V_T$  and  $I_T$  in *Figure 1*, starts to return toward the generator. Applying

Kirchoff's laws to the end of the line at the instant the initial wave arrives, results in the following.

$$I_1 + I_r = I_T = \text{current into R}_T$$

(eq. 5)

Since only one voltage can exist at the end of the line at this instant of time, the following is true:

$$\begin{array}{ccc} & V_1+V_r=V_T\\ \text{thus} & I_T=\frac{V_T}{R_T}=\frac{V_1+V_r}{R_T}\\ \text{also} & I_1=\frac{V_1}{Z_0}\,\text{and}\,I_r=-\frac{V_r}{Z_0} \end{array} \tag{eq. 6}$$

with the minus sign indicating that V<sub>r</sub> is moving toward the generator.

Combining the foregoing relationships algebraically and solving for V<sub>r</sub> yields a simplified expression in terms of V<sub>1</sub>,

$$\begin{split} &\frac{V_1}{Z_0} - \frac{V_r}{Z_0} = \frac{V_1 + V_r}{R_T} = \frac{V_1}{R_T} + \frac{V_r}{R_T} \\ &V_1 \left( \frac{1}{Z_0} - \frac{1}{R_T} \right) = V_r \left( \frac{1}{R_T} + \frac{1}{Z_0} \right) \\ &V_r = V_1 \left( \frac{R_T - Z_0}{R_T + Z_0} \right) = \rho_L \, V_1 \end{split} \tag{eq. 7}$$

The term in parenthesis is called the coefficient of reflection ρ. With R<sub>T</sub> ranging between zero (shorted line) and infinity (open line), the coefficient ranges between -1 and +1 respectively. The subscript L indicates that  $\rho$  refers to the coefficient at the load end of the line.

Equation 7 expresses the amount of voltage sent back down the line, and since

$$\begin{array}{ccc} & V_T = V_1 + V_r & \text{(eq. 8)} \\ \text{then} & V_T = V_1 \, (1 \, + \, \rho_L). \end{array}$$

V<sub>T</sub> can also be determined from an expression which does not require the preliminary step of calculating  $\rho_L$ . Manipulating (1 +  $\rho_L$ ) results in

$$\begin{split} 1 \,+\, \rho_L = 1 \,+\, \frac{R_T - Z_0}{R_T + Z_0} = 2 \left(\frac{R_T}{R_T + Z_0}\right) \\ \text{Substituting in } \textit{Equation 8 gives} \end{split}$$

$$V_T = 2 \left( \frac{R_T}{R_T + Z_0} \right) V_1 \tag{eq. 9}$$

The foregoing has the same form as a simple voltage divider involving a generator V<sub>1</sub> with internal impedance Z<sub>0</sub> driving a load R<sub>T</sub>, except that the amplitude of V<sub>T</sub> is doubled.

The arrow indicating the direction of V<sub>r</sub> in Figure 1 correctly indicates the V<sub>r</sub> direction of travel, but the direction of I<sub>r</sub> flow depends on the  $V_r$  polarity. If  $V_r$  is positive,  $I_r$  flows toward the generator, opposing I<sub>1</sub>. This relationship between the polarity of  $V_r$  and the direction of  $I_r$  can be deduced by noting in Equation 7 that if Vr is positive it is because RT is

greater than  $Z_0$ . In turn, this means that the initial current  $I_r$ is larger than the final quiescent current, dictated by V1 and R<sub>T</sub>. Hence, I<sub>r</sub> must oppose I<sub>1</sub> to reduce the line current to the final quiescent value. Similar reasoning shows that if V<sub>r</sub> is negative, I<sub>r</sub> flows in the same direction as I<sub>1</sub>.

It is sometimes easier to determine the effect of  $V_r$  on line conditions by thinking of it as an independent voltage generator in series with  $\ensuremath{R_{T}}.$  With this concept, the direction of  $\ensuremath{I_{r}}$  is immediately apparent; its magnitude, however, is the ratio of V<sub>r</sub> to Z<sub>0</sub>, i.e., R<sub>T</sub> is already accounted for in the magnitude of V<sub>r</sub>. The relationships between incident and reflected signals are represented in Figure 2 for both cases of mismatch between R<sub>T</sub> and Z<sub>0</sub>.

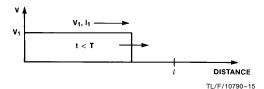

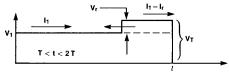

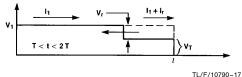

The incident wave is shown in Figure 2a, before it has reached the end of the line. In Figure 2b, a positive Vr is returning to the generator. To the left of  $V_r$  the current is still I<sub>1</sub>, flowing to the right, while to the right of V<sub>r</sub> the net current in the line is the difference between  $I_1$  and  $I_r$ . In Figure 2c, the reflection coefficient is negative, producing a negative V<sub>r</sub>. This, in turn, causes an increase in the amount of current flowing to the right behind the V<sub>r</sub> wave.

a. Incident Wave

TL/F/10790-16

b. Reflected Wave for  $R_{\mbox{\scriptsize T}} > Z_0$

c. Reflected Wave for  $\ensuremath{R_T} < \ensuremath{\text{\textbf{Z}}}_0$ FIGURE 2. Reflections for  $R_T \neq Z_0$

# SOURCE IMPEDANCE, MULTIPLE REFLECTIONS

When a reflected voltage arrives back at the source (generator), the reflection coefficient at the source determines the response to  $V_r$ . The coefficient of reflection at the source is governed by  $Z_0$  and the source resistance  $R_S$ .

$$\rho_{S} = \frac{R_{S} - Z_{0}}{R_{S} + Z_{0}} \tag{eq. 10} \label{eq:eq. 10}$$

If the source impedance matches the line impedance, a reflected voltage arriving at the source is not reflected back toward the load end. Voltage and current on the line are stable with the following values.

$$V_T = V_1 + V_r$$

and  $I_T = I_1 - I_r$  (eq. 11)

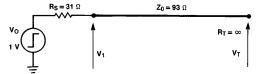

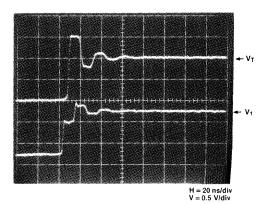

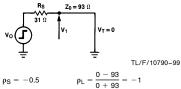

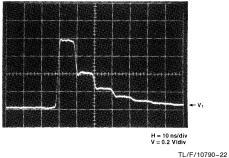

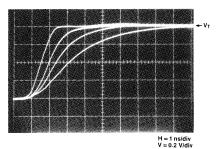

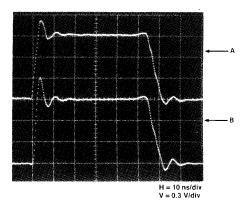

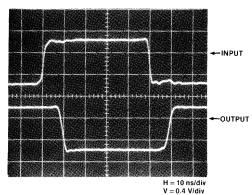

If neither source impedance nor terminating impedance matches  $Z_0$ , multiple reflections occur; the voltage at each end of the line comes closer to the final steady state value with each succeeding reflection. An example of a line mismatched on both ends is shown in Figure 3. The source is a step function of 1V amplitude occurring at time  $t_0$ . The initial value of  $V_1$  starting down the line is 0.75V due to the voltage divider action of  $Z_0$  and  $R_{\rm S}$ . The time scale in the photograph shows that the line delay is approximately 6 ns. Since neither end of the line is terminated in its characteristic impedance, multiple reflections occur.

The amplitude and persistence of the ringing shown in Figure 3 become greater with increasing mismatch between the line impedance and source and load impedances. Re-

TL/F/10790-18

$$\rho_{\text{S}} = \frac{31-93}{31+93} = -0.5 \qquad \qquad \rho_{\text{L}} = \frac{\omega-93}{\omega+93} = +1$$

Initially:

$$V_1 = \frac{Z_0}{Z_0 + R_S} \bullet V_0 = \frac{93}{124} \bullet 1 = 0.75V$$

TL/F/10790-19

FIGURE 3. Multiple Reflections Due to

Mismatch at Load and Source

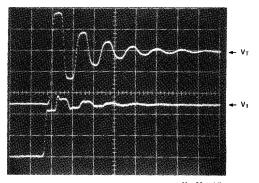

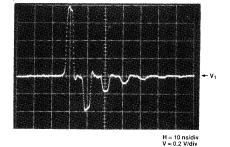

ducing R<sub>S</sub> (Figure 3) to 13 $\Omega$  increases  $\rho_S$  to -0.75V, and the effects are illustrated in Figure 4. The initial value of V<sub>T</sub> is 1.8V with a reflection of 0.9V from the open end. When this reflection reaches the source, a reflection of 0.9V  $\times$  -0.75V starts back toward the open end. Thus, the second increment of voltage arriving at the open end is negative going. In turn, a negative-going reflection of 0.9V  $\times$  -0.75V starts back toward the source. This negative increment is again multiplied by -0.75 at the source and returned toward the open end. It can be deduced that the difference in amplitude between the first two positive peaks observed at the open end is

$$\begin{split} V_T - V'_T &= (1 + \rho_L) \, V_1 - (1 + \rho_L) \, V_1 \, \rho^2_L \, \rho^2_S \\ &= (1 + \rho_L) \, V_1 \, (1 - \rho^2_L \, \rho^2_S). \end{split} \tag{eq. 12}$$

The factor (1 -  $\rho^2_L$   $\rho^2_S)$  is similar to the damping factor associated with lumped constant circuitry. It expresses the attenuation of successive positive or negative peaks of ringing.

H = 20 ns/div V = 0.4 V/div

TL/F/10790-20

FIGURE 4. Extended Ringing when R<sub>S</sub> of Figure 3 is Reduced to  $13\Omega$

# LATTICE DIAGRAM

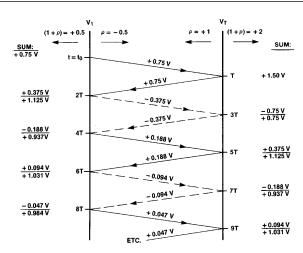

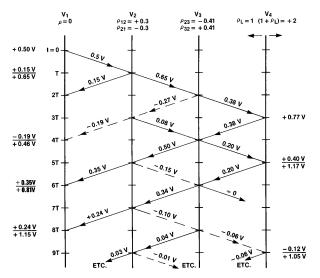

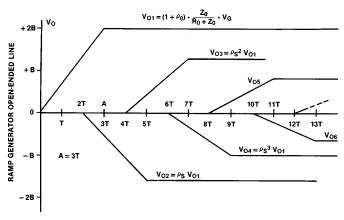

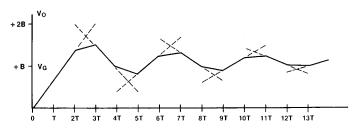

In the presence of multiple reflections, keeping track of the incremental waves on the line and the net voltage at the ends becomes a bookkeeping chore. A convenient and systematic method of indicating the conditions which combines magnitude, polarity and time utilizes a graphic construction called a lattice diagram.<sup>4</sup> A lattice diagram for the line conditions of *Figure 3* is shown in *Figure 5*.

The vertical lines symbolize discontinuity points, in this case the ends of the line. A time scale is marked off on each line in increments of 2T, starting at  $t_0$  for  $V_1$  and T for  $V_T$ . The diagonal lines indicate the incremental voltages traveling between the ends of the line; solid lines are used for positive voltages and dashed lines for negative. It is helpful to write the reflection and transmission multipliers  $\rho$  and  $(1+\rho)$  at each vertical line, and to tabulate the incremental and net voltages in columns alongside the vertical lines. Both the lattice diagram and the waveform photograph show that  $V_1$  and  $V_T$  asymptotically approach 1V, as they must with a 1V source driving an open-ended line.

FIGURE 5. Lattice Diagram for the Circuit of Figure 3

# SHORTED LINE

The open-ended line in Figure 3 has a reflection coefficient of +1 and the successive reflections tend toward the steady state conditions of zero line current and a line voltage equal to the source voltage. In contrast, a shorted line has a reflection coefficient of -1 and successive reflections must cause the line conditions to approach the steady state conditions of zero voltage and a line current determined by the source voltage and resistance.

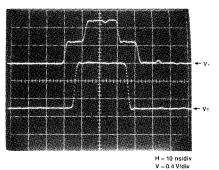

Shorted line conditions are shown in Figure 6a with the reflection coefficient at the source end of the line also negative. A negative coefficient at both ends of the line means that any voltage approaching either end of the line is reflected in the opposite polarity. Figure 6b shows the response to an input step-function with a duration much longer than the

line delay. The initial voltage starting down the line is about +0.75V, which is inverted at the shorted end and returned toward the source as -0.75V. Arriving back at the source end of the line, this voltage is multiplied by (1 +  $\rho_S$ ), causing a -0.37V net change in V<sub>1</sub>. Concurrently, a reflected voltage of +0.37V (-0.75V times  $\rho_S$  of -0.5) starts back toward the shorted end of the line. The voltage at V<sub>1</sub> is reduced by 50% with each successive round trip of reflections, thus leading to the final condition of zero volts on the line.

TL/F/10790-21

When the duration of the input pulse is less than the delay of the line, the reflections observed at the source end of the line constitute a train of negative pulses, as shown in *Figure 6c*. The amplitude decreases by 50% with each successive occurrence as it did in *Figure 6b*.

a. Reflection Coefficients for Shorted Line

b. Input Pulse Duration

Line Delay

$$^{\rm TL/F/10790-23}$$  c. Input Pulse Duration < Line Delay

FIGURE 6. Reflections of Long and Short Pulses on a Shorted Line

# **SERIES TERMINATION**

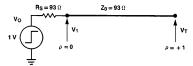

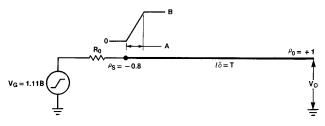

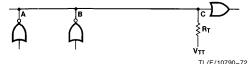

Driving an open-ended line through a source resistance equal to the line impedance is called series termination. It is particularly useful when transmitting signals which originate on a PC board and travel through the backplane to another board, with the attendant discontinuities, since reflections coming back to the source are absorbed and ringing thereby controlled. Figure 7 shows a 93 $\Omega$  line driven from a 1V generator through a source impedance of  $93\Omega.$  The photograph illustrates that the amplitude of the initial signal sent down the line is only half of the generator voltage, while the voltage at the open end of the line is doubled to full amplitude (1 +  $\rho_L$  = 2). The reflected voltage arriving back at the source raises V<sub>1</sub> to the full amplitude of the generator signal. Since the reflection coefficient at the source is zero, no further changes occur and the line voltage is equal to the generator voltage. Because the initial signal on the line is only half the normal signal swing, the loads must be connected at or near the end of the line to avoid receiving a 2step input signal.

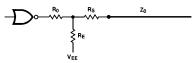

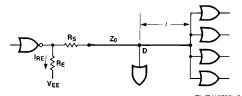

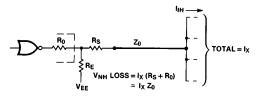

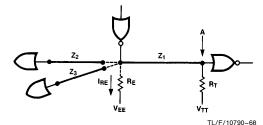

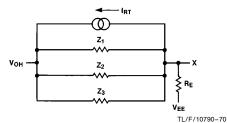

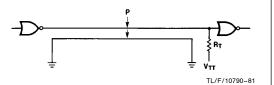

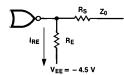

An ECL output driving a series terminated line requires a pull-down resistor to  $V_{EE},$  as indicated in Figure 8. The resistor  $R_0$  shown in Figure 8 symbolizes the output resistance of the ECL gate. The relationships between  $R_0,\,R_S,\,R_E$  and  $Z_0$  are discussed in Appendix B.

TL/F/10790-24

TL/F/10790-25

FIGURE 7. Series Terminated Line and Waveforms

TL/F/10790-26

FIGURE 8. ECL Element Driving a Series Terminated Line

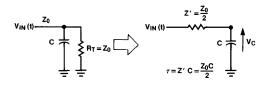

# EXTRA DELAY WITH TERMINATION CAPACITANCE

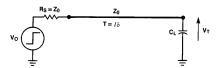

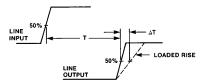

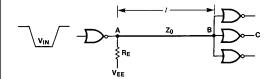

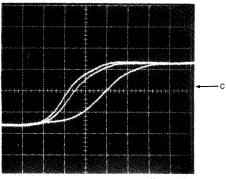

Designers should consider the effect of the load capacitance at the end of the line when using series termination. Figure 9 shows how the output waveform changes with increasing load capacitance. Figure 9b shows the effect of load capacitances of 0, 12, 24, 48 pF. With no load, the delay between the 50% points of the input and output is just the line delay T. A capacitive load at the end of the line causes an extra delay  $\Delta T$  due to the increase in rise time of the output signal. The midpoint of the output is used as a criterion because the propagation delay of an ECL circuit is measured between the 50% points of the input and output signals.

TL/F/10790-27

#### a. Series Terminated Line with Load Capacitance

TL/F/10790-28

# b. Output Rise Time Increase with Increasing Load Capacitance

TL/F/10790-29

c. Extra Delay  $\Delta T$  Due to Rise Time Increase FIGURE 9. Extra Delay with Termination Capacitance

$$\frac{V_{\text{IN}}}{2}(t) \xrightarrow{Z_0} V_{\text{IN}}(t) \xrightarrow{Z' = Z_0} V_{\text{C}}$$

$$\tau = Z' \text{ C} = Z_0 \text{ C}$$

$$TI /F / 10790 - 30$$

a. Thevenin Equivalent for Series Terminated Case

# b. Thevenin Equivalent for Parallel Terminated Case

TL/F/10790-32

$$\begin{split} \nu_{\text{in}}(t) &= \frac{V}{a} \left[ \text{ tu}(t) - (t-a)\text{u} \, (t-a) \right] \\ u(t) &= \frac{0 \text{ for } t < 0}{1 \text{ for } t > 0} \\ u(t-a) &= \frac{0 \text{ for } t < a,}{1 \text{ for } t > a} \\ V_{\text{IN}}(S) &= \frac{V}{as^2} (1 - e^{-as}) \\ V_{\text{C}}(S) &= \frac{V}{ar} \bullet \frac{1}{s^2 \, (s+1/\tau)} \, (1 - e^{-as}) \\ \nu_{\text{c}}(t) &= \frac{V}{a} \left[ t - \tau (1 - e^{-t/\tau}) \right] \, u(t) \\ &- \frac{V}{a} \left[ (t-a) \right] \\ &- \tau (1 - e^{-\frac{t-a}{\tau}}) \right] \, u(t-a) \\ \text{c. Equations for Input and Output Voltages} \end{split}$$

FIGURE 10. Determining the Effect of End-of-Line Capacitance

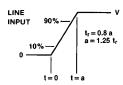

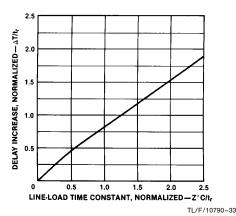

The increase in propagation delay can be calculated by using a ramp approximation for the incident voltage and characterizing the circuit as a fixed impedance in series with the load capacitance, as shown in Figure 10. One general solution serves both series and parallel termination cases by using an impedance Z' and a time constant  $\tau$ , defined in Figure 10a and 10b. Calculated and observed increases in delay time to the 50% point show close agreement when auis less than half the ramp time. At large ratios of  $\tau/a$  (where a = ramp time), measured delays exceed calculated values by approximately 7%. Figure 11, based on measured values, shows the increase in delay to the 50% point as a function of the Z'C time constant, both normalized to the 10% to 90% rise time of the input signal. As an example of using the graph, consider a  $100\Omega$  series terminated line with 30 pF load capacitance at the end of the line and a no-load rise time of 3 ns for the input signal. From Figure 10a, Z' is equal to  $100\Omega$ ; the ratio  $Z'C/t_r$  is 1. From the graph, the ratio  $\Delta T/t_r$  is 0.8. Thus the increase in the delay to the 50% point of the output waveform is 0.8  $t_r$ , or 2.4 ns, which is then added to the no-load line delay T to determine the total delay.

Had the 100 $\Omega$  line in the foregoing example been parallel rather than series terminated at the end of the line, Z' would be 50 $\Omega$ . The added delay would be only 1.35 ns with the same 30 pF loading at the end. The added delay would be only 0.75 ns if the line were 50 $\Omega$  and parallel terminated. The various trade-offs involving type of termination, line impedance, and loading are important considerations for critical delay paths.

FIGURE 11. Increase in 50% Point Delay Due to Capacitive Loading at the End of the Line, Normalized to T<sub>r</sub>

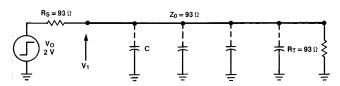

# DISTRIBUTED LOADING EFFECTS ON LINE CHARACTERISTICS

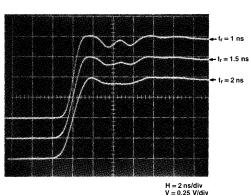

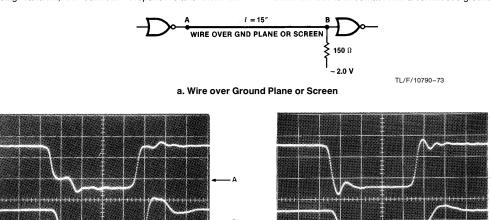

When capacitive loads such as ECL inputs are connected along a transmission line, each one causes a reflection with a polarity opposite to that of the incident wave. Reflections from two adjacent loads tend to overlap if the time required for the incident wave to travel from one load to the next is equal to or less than the signal rise time. 5 Figure 12a illustrates an arrangement for observing the effects of capacitive loading, while Figure 12b shows an incident wave followed by reflections from two capacitive loads. The two capacitors causing the reflections are separated by a distance requiring a travel time of 1 ns. The two reflections return to the source 2 ns apart, since it takes 1 ns longer for the incident wave to reach the second capacitor and an additional 1 ns for the second reflection to travel back to the source. In the upper trace of Figure 12b, the input signal rise time is 1 ns and there are two distinct reflections, although the trailing edge of the first overlaps the leading edge of the second. The input rise time is longer in the middle trace, causing a greater overlap. In the lower trace, the 2 ns input rise time causes the two reflections to merge and appear as a single reflection which is relatively constant (at  $\approx -10\%$ ) for half its duration. This is about the same reflection that would occur if the  $93\Omega$  line had a middle section with an impedance reduced to  $75\Omega$ .

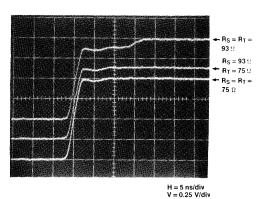

With a number of capacitors distributed all along the line of *Figure 12a*, the combined reflections modify the observed input waveform as shown in the top trace of *Figure 12c*. The reflections persist for a time equal to the 2-way line delay (15 ns), after which the line voltage attains its final value. The waveform suggests a line terminated with a resistance greater than its characteristic impedance ( $R_T > Z_0$ ).

This analogy is strengthened by observing the effect of reducing  $R_T$  from  $93\Omega$  to  $75\Omega,$  which leads to the middle waveform of Figure 12c. Note that the final (steady state) value of the line voltage is reduced by about the same amount as that caused by the capacitive reflections. In the lower trace of Figure 12c the source resistance  $R_S$  is reduced from  $93\Omega$  to  $75\Omega,$  restoring both the initial and final line voltage values to the same amplitude as the final value in the upper trace. From the standpoint of providing a desired signal voltage on the line and impedance matching at either end, the effect of distributed capacitive loading can be treated as a reduction in line impedance.

The reduced line impedance can be calculated by considering the load capacitance  $C_L$  as an increase in the intrinsic line capacitance  $C_0$  along that portion of the line where the loads are connected.  $^6$  Denoting this length of line as  $\emph{I},$  the distributed value  $C_D$  of the load capacitance is as follows.

$$C_D = \frac{C_L}{I}$$

$\text{C}_{\text{D}}$  is then added to  $\text{C}_{0}$  in Equation 1 to determine the reduced line impedance  $\text{Z}_{0}.$

$$Z'_{0} = \sqrt{\frac{L_{0}}{C_{0} + C_{D}}} = \sqrt{\frac{L_{0}}{C_{0}} \left(1 + \frac{C_{D}}{C_{0}}\right)}$$

$$Z'_{0} + \frac{\sqrt{\frac{L_{0}}{C_{0}}}}{\sqrt{1 + \frac{C_{D}}{C_{0}}}} = \frac{Z_{0}}{\sqrt{1 + \frac{C_{D}}{C_{0}}}}$$

(eq. 13)

a. Arrangement for Observing Capacitive Loading Effects

b. Capacitive Reflections Merging as Rise Time Increases

TL/F/10790-34

TL/F/10790-36

c. Matching the Altered Impedance of a Capacitively Loaded Line

FIGURE 12. Capacitive Reflections and Effects on Line Characteristics

TL/F/10790-35

In the example of Figure 12c, the total load capacitance is 33 pF while the total intrinsic line capacitance  $/C_0$  is 60 pF. (Note that the ratio  $C_D/C_0$  is the same as  $C_L//C_0$ .) The calculated value of the reduced impedance is thus

$$Z'_0 = \frac{93}{\sqrt{1 + \frac{33}{60}}} = \frac{93}{\sqrt{1.55}} = 75\Omega$$

(eq. 14)

This correlates with the results observed in Figure 12c when  $\rm R_T$  and  $\rm R_S$  are reduced to 75  $\!\Omega.$

The distributed load capacitance also increases the line delay, which can be calculated from *Equation 2*.

$$\begin{split} \delta' &= \sqrt{L_0 \left( C_0 + C_D \right)} = \sqrt{L_0 C_0} \, \sqrt{1 + \frac{C_D}{C_0}} \\ &= \delta \, \sqrt{1 + \frac{C_D}{C_0}} \end{split} \tag{eq. 15}$$

The line used in the example of  $Figure\ 12c$  has an intrinsic delay of 6 ns and a loaded delay of 7.5 ns which checks with  $Equation\ 15$ .

$$/\delta' = /\delta \sqrt{1.55} = 6\sqrt{1.55} = 7.5 \text{ ns}$$

(eq. 16)

Equation 15 can be used to predict the delay for a given line and load. The ratio  $C_D/C_0$  (hence the loading effect) can be minimized for a given loading by using a line with a high intrinsic capacitance  $C_0$ .

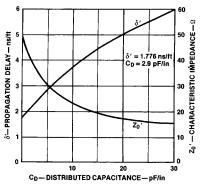

A plot of Z' and  $\delta'$  for a  $50\Omega$  line as a function of  $C_D$  is shown in Figure 13. This figure illustrates that relatively modest amounts of load capacitance will add appreciably to the propagation delay of a line. In addition, the characteristic impedance is reduced significantly.

TL/F/10790-37

# FIGURE 13. Capacitive Loading Effects on Line Delay and Impedance

Worst case reflections from a capacitively loaded section of transmission line can be accurately predicted by using the modified impedance of  $Equation \ 9.6$  When a signal originates on an unloaded section of line, the effective reflection coefficient is as follows.

$$\rho = \frac{Z'_0 - Z_0}{Z'_0 + Z_0} \tag{eq. 17}$$

# MISMATCHED LINES

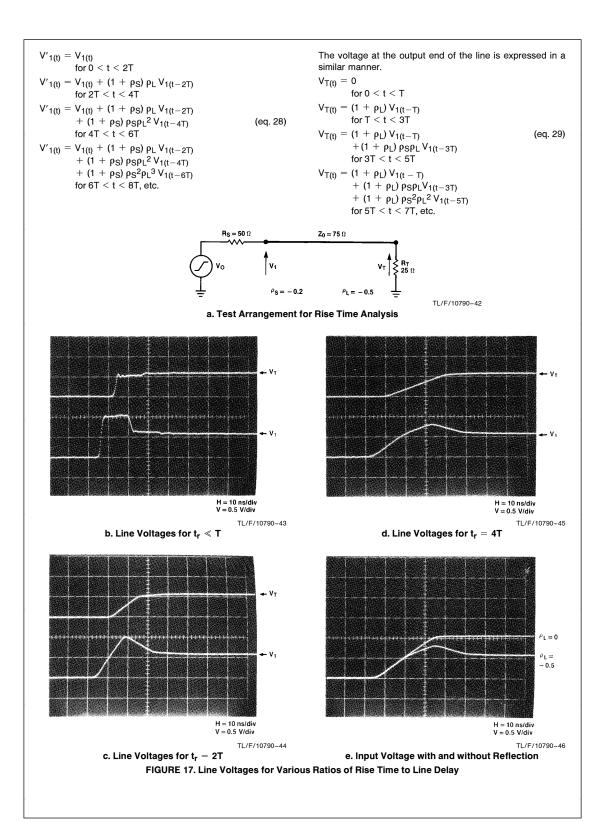

Reflections occur not only from mismatched load and source impedances but also from changes in line impedance. These changes could be caused by bends in coaxial cable, unshielded twisted-pair in contact with metal, or mismatch between PC board traces and backplane wiring. With the coax or twisted-pair, line impedance changes run about 5% to 10% and reflections are usually no problem since the percent reflection is roughly half the percent change in impedance. However, between PC board and backplane wiring, the mismatch can be 2 or 3 to 1. This is illustrated in Figure 14 and analyzed in the lattice diagram of Figure 15. Line 1 is driven in the series terminated mode so that reflections coming back to the source are absorbed.

The reflection and transmission at the point where impedances differ are determined by treating the downstream line as though it were a terminating resistor. For the example of Figure 14, the reflection coefficient at the intersection of lines 1 and 2 for a signal traveling to the right is as follows.

$$\rho_{12} = \frac{Z_2 - Z_1}{Z_2 + Z_1} = \frac{93 - 50}{143} = +0.3 \tag{eq. 18}$$

Thus the signal reflected back toward the source and the signal continuing along line 2 are, respectively, as follows.

$$V_{1r} = \rho_{12} V_1 = +0.3 V_1$$

(eq. 19a)

$$V_2 = (1 \, + \, \rho_{12}) \, V_1 = \, + \, 1.3 \, V_1 \qquad \qquad \text{(eq. 19b)}$$

At the intersection of lines 2 and 3, the reflection coefficient for signals traveling to the right is determined by treating  $Z_3$  as a terminating resistor.

$$\rho_{23} = \frac{Z_3 - Z_2}{Z_3 + Z_2} = \frac{39 - 93}{132} = -0.41 \tag{eq. 20}$$

When V<sub>2</sub> arrives at this point, the reflected and transmitted signals are as follows.

$$\begin{array}{l} V_{2r} = \rho_{23}\,V_2 = \,-0.41\,V_2 \\ = (-0.41)\,(1.3)\,V_1 \\ = \,-0.53\,V_1 \end{array} \tag{eq. 21a}$$

$$\begin{array}{l} V_3 = (1 + \rho_{23}) \, V_2 = 0.59 \, V_2 \\ = (0.59) \, (1.3) \, V_1 \\ = 0.77 \, V_1 \end{array} \tag{eq. 21b}$$

Voltage  $V_3$  is doubled in magnitude when it arrives at the open-ended output, since  $\rho_L$  is +1. This effectively cancels the voltage divider action between  $R_S$  and  $Z_1$ .

$$\begin{aligned} V_4 &= (1 + \rho_L) \, V_3 = (1 + \rho_L) \, (1 + \rho_{23}) \, V_2 \\ &= (1 + \rho_L) \, (1 + \rho_{23}) \, (1 + \rho_{12}) \, V_1 \\ &= (1 + \rho_L) \, (1 + \rho_{23}) \, (1 + \rho_{12}) \, \frac{V_0}{2} \end{aligned} \tag{eq. 22}$$

$$V_4 = (1 + \rho_{23}) (1 + \rho_{12}) V_O$$

Thus, *Equation 22* is the general expression for the initial step of output voltage for three lines when the input is series terminated and the output is open-ended.

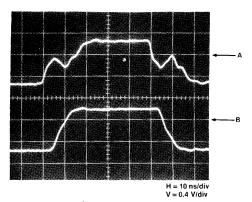

Note that the reflection coefficients at the intersections of lines 1 and 2 and lines 2 and 3 in Figure 15 have reversed signs for signals traveling to the left. Thus the voltage reflected from the open output and the signal reflecting back and forth on line 2 both contribute additional increments of output voltage in the same polarity as  $V_O$ . Lines 2 and 3 have the same delay time; therefore, the two aforementioned increments arrive at the output simultaneously at time 5T on the lattice diagram (Figure 15).

In the general case of series lines with different delay times, the vertical lines on the lattice diagram should be spaced apart in the ratio of the respective delays. *Figure 16* shows this for a hypothetical case with delay ratios 1:2:3. For a sequence of transmission lines with the highest imped-

ance line in the middle, at least three output voltage increments with the same polarity as  $V_{\rm O}$  occur before one can occur of opposite polarity. On the other hand, if the middle line has the lowest impedance, the polarity of the second increment of output voltage is the opposite of  $V_{\rm O}$ . The third increment of output voltage has the opposite polarity, for the time delay ratios of Figure 16.

When transmitting logic signals, it is important that the initial step of line output voltage pass through the threshold region of the receiving circuit, and that the next two increments of output voltage augment the initial step. Thus in a series terminated sequence of three mismatched lines, the middle line should have the highest impedance.

TL/F/10790-39

TL/F/10790-38

FIGURE 14. Reflections from Mismatched Lines

FIGURE 15. Lattice Diagram for the Circuit of Figure 14

TL/F/10790-40

FIGURE 16. Lattice Diagram for Three Lines with Delay Ratios 1:2:3

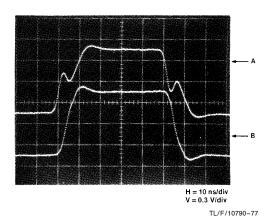

#### **RISE TIME VERSUS LINE DELAY**

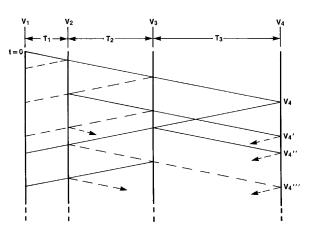

When the 2-way line delay is less than the rise time of the input wave, any reflections generated at the end of the line are returned to the source before the input transition is completed. Assuming that the generator has a finite source resistance, the reflected wave adds algebraically to the input wave while it is still in transition, thereby changing the shape of the input. This effect is illustrated in *Figure 17*, which shows input and output voltages for several comparative values of rise time and line delay.

In Figure 17b where the rise time is much shorter than the line delay, V<sub>1</sub> rises to an initial value of 1V. At time T later, V<sub>T</sub> rises to 0.5V, i.e.,  $1+\rho_L=0.5$ . The negative reflection arrives back at the source at time 2T, causing a net change of -0.4V, i.e.,  $(1+\rho_S)~(-0.5)=-0.4$ .

The negative coefficient at the source changes the polarity of the other 0.1V of the reflection and returns it to the end of the line, causing  $V_T$  to go positive by another 50 mV at time 3T. The remaining 50 mV is inverted and reflected back to the source, where its effect is barely distinguishable as a small negative change at time 4T.

In *Figure 17c*, the input rise time (0% to 100%) is increased to such an extent that the input ramp ends just as the negative reflection arrives back at the source end. Thus the input rise time is equal to 2T.

The input rise time is increased to 4T in Figure 17d, with the negative reflection causing a noticeable change in input slope at about its midpoint. This change in slope is more visible in the double exposure photo of Figure 17e, which shows V<sub>1</sub> (t<sub>r</sub> still set for 4T) with and without the negative reflection. The reflection was eliminated by terminating the line in its characteristic impedance.

The net input voltage at any particular time is determined by adding the reflection to the otherwise unaffected input. It must be remembered that the reflection arriving back at the input at a given time is proportional to the input voltage at a time 2T earlier. The value of  $V_1$  in *Figure 17d* can be calculated by starting with the 1V input ramp.

TL/F/10790-41

$$V_1 = \frac{1}{t_r} \bullet t \quad \text{for } 0 \le t \le 4T$$

(eq. 23)

$=\,1V\qquad\text{for }t\geq4T$

The reflection from the end of the line is

$$V_{r}=\frac{\rho_{L}\left(t-2T\right)}{t_{r}}; \tag{eq. 24}$$

the portion of the reflection that appears at the input is

$${V'}_r = \frac{(1 \, + \, \rho_S) \, \rho_L \, (t - 2T)}{t_r}; \eqno(eq. 25)$$

the net value of the input voltage is the sum.

$$V'_1 = \frac{t}{t_r} + \frac{(1 + \rho_S) + \rho_L (t - 2T)}{t_r}$$

(eq. 26)

The peak value of the input voltage in *Figure 17d* is determined by substituting values and letting t equal 4T.

$$V'_1 = 1 + \frac{(0.8)(-0.5)(4T - 2T)}{t_r}$$

(eq. 27)

= 1 - 0.4 (0.5) = 0.8V

After this peak point, the input ramp is no longer increasing but the reflection is still arriving. Hence the net value of the input voltage decreases. In this example, the later reflections are too small to be detected and the input voltage is thus stable after time 6T. For the general case of repeated reflections, the net voltage  $V_{1(t)}$  seen at the driven end of the line can be expressed as follows, where the signal caused by the generator is  $V_{1(t)}$ .

# RINGING

Multiple reflections occur on a transmission line when neither the signal source impedance nor the termination (load) impedance matches the line impedance. When the source reflection coefficient  $\rho_{S}$  and the load reflection coefficient  $\rho_{L}$  are of opposite polarity, the reflections alternate in polarity. This causes the signal voltage to oscillate about the final steady state value, commonly recognized as ringing.

When the signal rise time is long compared to the line delay, the signal shape is distorted because the individual reflections overlap in time. The basic relationships among rise time, line delay, overshoot and undershoot are shown in a simplified diagram, *Figure 18*. The incident wave is a ramp of amplitude B and rise duration A. The reflection coefficient at the open-ended line output is  $\pm 1$  and the source reflection coefficient is assumed to be  $\pm 0.8$ , i.e.,  $R_0 = Z_0/9$ .

Figure 18b shows the individual reflections treated separately. Rise time A is assumed to be three times the line delay T. The time scale reference is the line output and the first increment of output voltage VO rises to 2B in the time interval A. Simultaneously, a positive reflection (not shown) of amplitude B is generated and travels to the source, whereupon it is multiplied by -0.8 and returns toward the end of the line. This negative-going ramp starts at time 2T (twice the line delay) and doubles to -1.6B at time 2T + A. The negative-going increment also generates a reflection of amplitude -0.8B which makes the round trip to the source and back, appearing at time 4T as a positive ramp rising to + 1.28B at time 4T + A. The process of reflection and rereflection continues, and each successive increment changes in polarity and has an amplitude of 80% of the preceding increment.

a. Ramp Generator Driving Open-Ended Line

TL/F/10790-47

b. Increments of Output Voltage Treated Individually

TL/F/10790-48

c. Net Output Signal Determined by Superposition FIGURE 18. Basic Relationships Involved in Ringing

TL/F/10790-49

In Figure 18c, the output increments are added algebraically by superposition. The starting point of each increment is shifted upward to a voltage value equal to the algebraic sum of the quiescent levels of all the preceding increments (i.e., 0, 2B, 0.4B, 1.68B, etc.). For time intervals when two ramps occur simultaneously, the two linear functions add to produce a third ramp that prevails during the overlap time of the two increments

It is apparent from the geometric relationships, that if the ramp time A is less than twice the line delay, the first output increment has time to rise to the full 2B amplitude and the second increment reduces the net output voltage to 0.4B. Conversely, if the line delay is very short compared to the ramp time, the excursions about the final value  $V_{\rm G}$  are

Figure 18c shows that the peak of each excursion is reached when the earlier of the two constituent ramps reaches its maximum value, with the result that the first peak occurs at time A. This is because the earlier ramp has a greater slope (absolute value) than the one that follows.

Actual waveforms such as produced by ECL or TTL do not have a constant slope and do not start and stop as abruptly as the ramp used in the example of *Figure 18*. Predicting the time at which the peaks of overshoot and undershoot occur is not as simple as with ramp excitation. A more rigorous treatment is required, including an expression for the driving waveform which closely simulates its actual shape. In the general case, a peak occurs when the sum of the slopes of the individual signal increment is zero.

#### SUMMARY

The foregoing discussions are by no means an exhaustive treatment of transmission line characteristics. Rather, they

are intended to focus attention on the general methods used to determine the interactions between high-speed logic circuits and their interconnections. Considering an interconnection in terms of distributed rather than lumped inductance and capacitance leads to the line impedance concept, i.e., mismatch between this characteristic impedance and the terminations causes reflections and ringing.

Series termination provides a means of absorbing reflections when it is likely that discontinuities and/or line impedance changes will be encountered. A disadvantage is that the incident wave is only one-half the signal swing, which limits load placement to the end of the line. ECL input capacitance increases the rise time at the end of the line, thus increasing the effective delay. With parallel termination, i.e., at the end of the line, loads can be distributed along the line. ECL input capacitance modifies the line characteristics and should be taken into account when determining line delay.

# **REFERENCES**

- 1. Metzger, G. and Vabre, J., *Transmission Lines with Pulse Excitation*, Academic Press, (1969).

- 2. Skilling, H., *Electric Transmission Lines*, McGraw-Hill, (1951).

- 3. Matick, R., *Transmission Lines for Digital and Communication Networks*, McGraw-Hill, (1969).

- 4. Millman, J. and Taub, H., *Pulse Digital and Switching Waveforms*, McGraw-Hill, (1965).

- 5. "Time Domain Reflectometry", *Hewlett-Packard Journal*, Vol. 15, No. 6, (February 1964).

- Feller, A., Kaupp H., and Digiacoma, J., "Crosstalk and Reflections in High-Speed Digital Systems", *Proceedings, Fall Joint Computer Conference*, (1965).

# APPENDIX B ECL DESIGN GUIDE: SYSTEM CONSIDERATIONS

#### INTRODUCTION

All of National's ECL input and output impedances are designed to accommodate various methods of driving and terminating interconnections. Controlled wiring impedance makes it possible to use simplified equivalent circuits to determine limiting conditions. Specific guidelines and recommendations are based on assumed worst-case combinations. Many of the recommendations may seem conservative, compared to typical observations, but the intent is to help the designer achieve a reliable system in a reasonable length of time with a minimum amount of redesign.

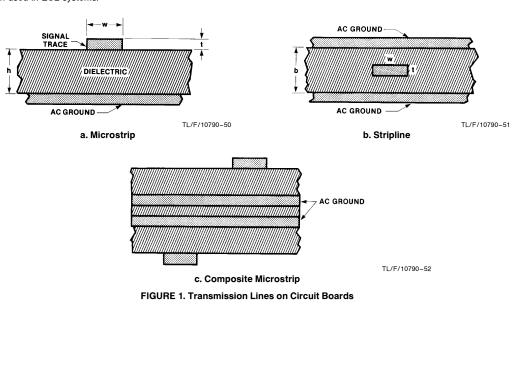

# PC BOARD TRANSMISSION LINES

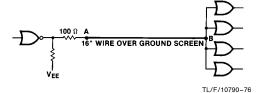

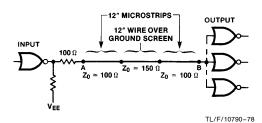

Strictly speaking, transmission lines are not always required for F100K ECL but, when used, they provide the advantages of predictable interconnect delays as well as reflection and ringing control through impedance matching. Two common types of PC board transmission lines are microstrip and stripline, *Figure 1*. Stripline requires multilayer construction techniques; microstrip uses ordinary double-clad boards. Other board construction techniques are wire wrap, stitch weld and discrete wired.

Stripline, *Figure 1b*, is used where packing density is a high priority because increasing the interconnect layers provides short signal paths. Boards with as many as 14 layers have been used in ECL systems.

Microstrip offers easier fabrication and higher propagation velocity than stripline, but the routing for a complex system may require more design effort. In Figure 1a, the ground plane can be a part of the VEE distribution as long as adequate bypassing from VEE to VCC (ground) is provided. Also, signal routing is simplified and an extra voltage plane is obtained by bonding two microstrip structures back to back, Figure 1c.

#### Microstrip

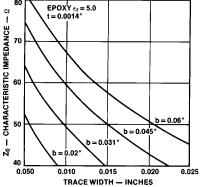

Equation 1 relates microstrip characteristic impedance to the dielectric constant and dimensions. Electric field fringing requires that the ground extend beyond each edge of the signal trace by a distance no less than the trace width.

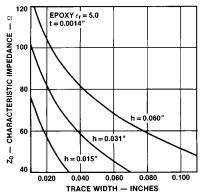

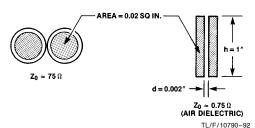

$$\begin{split} Z_0 &= \left(\frac{60}{\sqrt{0.475}\,\epsilon_r + 0.67}\right) \ln \left(\frac{4h}{0.67\,(0.8\,w + t)}\right) \\ &= \left(\frac{87}{\sqrt{\epsilon_r + 1.41}}\right) \ln \left(\frac{5.98\,h}{0.8\,w + t}\right) \end{split} \tag{eq. 1}$$

where h = dielectric thickness, w = trace width, t = trace thickness,  $\epsilon_r$  = board material dielectric constant relative to air

Equation 1 was developed from the impedance formula for a wire over ground plane transmission line, Equation 2.

$$Z_0 = \left(\frac{60}{\sqrt{\epsilon_r}}\right) \ln\left(\frac{4h}{d}\right)$$

(eq. 2)

where  $d=\mbox{wire}$  diameter,  $h=\mbox{distance}$  from ground to wire center.

Comparing Equation 1 and 2, the term 0.67 (0.8 w + t) shows the equivalence between a round wire and a rectangular conductor. The term 0.475  $\epsilon_{\rm f}$  + 0.67 is the *effective* dielectric constant for microstrip  $\epsilon_{\rm e}$ , considering that a microstrip line has a compound dielectric consisting of the board material and air. The effective dielectric constant is determined by measuring propagation delay per unit of line length and using the following relationship.

$$\delta = 1.016 \bullet \sqrt{\epsilon_{\rm e}} \, \text{ns/ft} \tag{eq. 3}$$

where  $\delta$  = propagation delay, ns/ft.

Propagation delay is a property of the dielectric material rather than line width or spacing. The coefficient 1.016 is the reciprocal of the velocity of light in free space. Propagation delay for microstrip lines on glass-filled G-10 epoxy boards is typically 1.77 ns/ft, yielding an effective dielectric constant of 3.04.

TL/F/10790-53

# FIGURE 2. Microstrip Impedance Versus Trace Width, G-10 Epoxy

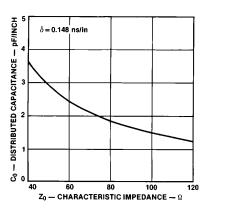

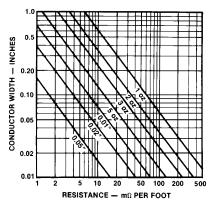

Using  $\epsilon_{\rm r}=5.0$  in Equation 1, Figure 2 provides microstrip line impedance as a function of width for several G-10 epoxy board thicknesses. Figure 3 shows the related C0 values, useful for determining capacitive loading effects on line characteristics, (Equation 15).

System designers should ascertain tolerances on board dimensions, dielectric constant and trace width etching in order to determine impedance variations. If conformal coating is used the effective dielectric constant of microstrip is increased, depending on the coating material and thickness.

TL/F/10790-54

FIGURE 3. Microstrip Distributed Capacitance Versus Impedance, G-10 Epoxy

Stripline

Stripline conductors are totally embedded. As a result, the board material determines the dielectric constant. G-10 epoxy boards have a typical propagation delay of 2.26 ns/ft. Equation 4 is used to calculate stripline impedances.<sup>1,2</sup>

$$Z_{0} = \left(\frac{60}{\sqrt{\epsilon_{\rm f}}}\right) \ln \left(\frac{4b}{0.67 \,\pi \, (0.8 \,\mathrm{w} + \mathrm{t})}\right) \tag{eq. 4}$$

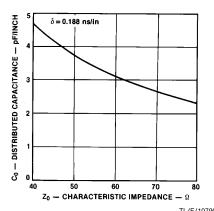

where b = distance between ground planes, w = trace width, t = trace thickness, w/(b-t) < 0.35 and t/b < 0.25. Figure 4 shows stripline impedance as a function of trace width, using Equation 4 and various ground plane separations for G-10 glass-filled epoxy boards. Related values of  $C_0$  are plotted in Figure 5.

TL/F/10790-55

FIGURE 4. Stripline Impedance Versus Trace Width, G-10 Epoxy

FIGURE 5. Stripline Distributed Capacitance Versus Impedance, G-10 Epoxy

# Wire Wrap

Wire-wrap boards are commercially available with three voltage planes, positions for several 24-pin Dual-In-Line Packages (DIP), terminating resistors, and decoupling capacitors. The devices are mounted on socket pins and interconnected with twisted pair wiring. One wire at each end of the twisted pair is wrapped around a signal pin, the other around a ground pin. The #30 insulated wire is uniformly twisted to provide a nominal  $93\Omega$  impedance line. Positions for Single-In-Line Package (SIP) terminating resistors are close to the inputs to provide good termination characteristics.

# Stitch Weld

Stitch-weld boards are commercially available with three voltage planes and buried resistors between planes. The devices are mounted on terminals and interconnected with insulated wires that are welded to the backside of the terminals. The insulated wires are placed on a controlled thickness over the ground plane to provide a nominal impedance of  $50\Omega$ . The boards are available for both DIPs and flatpaks. Use of flatpaks can increase package density and provide higher system performance.

# Discrete Wired

Custom Multiwire\* boards are available with integral power and ground planes. Wire is placed on a controlled thickness above the ground plane to obtain a nominal impedance line of 55Ω. Then holes are drilled through the wire and board. Copper is deposited in the drilled holes by an additive-electrolysis process which bonds each wire to the wall of the holes. Devices are soldered on the board to make connection to the wires.

\*Multiwire is a registered trademark of the Multiwire Corporation.

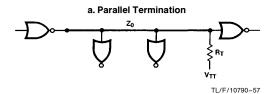

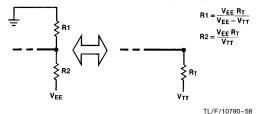

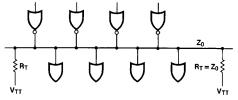

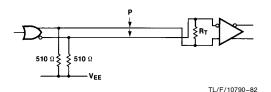

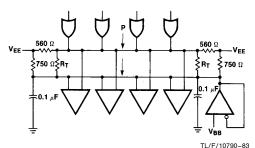

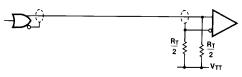

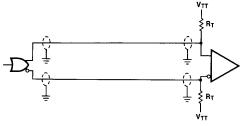

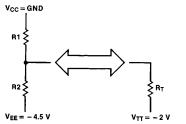

# **Parallel Termination**

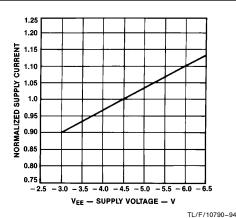

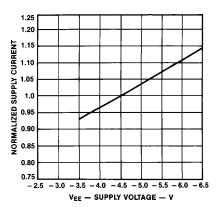

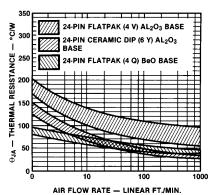

Terminating a line at the receiving end with a resistance equal to the characteristic line impedance is called parallel termination, Figure 6a. F100K circuits do not have internal pull-down resistors on outputs, so the terminating resistor must be returned to a voltage more negative than  $V_{\rm OL}$  to establish the LOW-state output voltage from the emitter follower. A -2V termination return supply is commonly used. This minimizes power consumption and correlates with standard test specifications for ECL circuits. A pair of resistors connected in series between ground (VCC) and the VEE

supply can provide the Thevenin equivalent of a single resistor to -2V if a separate termination supply is not available, *Figure 6b*. The average power dissipation in the Thevenin equivalent resistors is about 10 times the power dissipation in the single resistor returned to -2V, as shown in *Figures 10* and 13. For either parallel termination method, decoupling capacitors are required between the supply and ground (Chapter 6).

# b. Thevenin Equivalent of R<sub>T</sub> and V<sub>TT</sub>

#### TL/F/10/90-58

# c. Equivalent Circuit for Determining Approximate V<sub>OH</sub> and V<sub>OL</sub> Levels

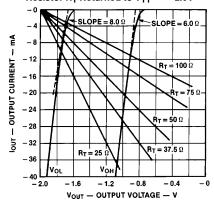

# d. F100K Output Characteristic with Terminating Resistor $R_T$ Returned to $V_{TT}=-2.0 \text{V}$

TL/F/10790-60 FIGURE 6. Parallel Termination

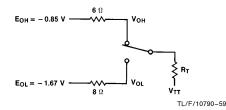

F100K output transistors are designed to drive low-impedance loads and have a maximum output current rating of 50 mA. The circuits are specified and tested with a  $50\Omega$  load returned to -2V. This gives nominal output levels of -0.955V at 20.9 mA and -1.705V at 5.9 mA. Output levels will be different with other load currents because of the transistor output resistance. This resistance is nonlinear with load current since it is due, in part, to the base-emitter voltage of the emitter follower, which is logarithmic with output current. With the standard  $50\Omega$  load, the effective source resistance is approximately  $6\Omega$  in the HIGH state and  $8\Omega$  in the LOW state.

The foregoing values of output voltage, output current, and output resistance are used to estimate quiescent output levels with different loads. An equivalent circuit is shown in Figure 6c. The ECL circuit is assumed to contain two internal voltage sources  $E_{OH}$  and  $E_{OL}$  with series resistances of  $6\Omega$  and  $8\Omega$  respectively. The values shown for  $E_{OH}$  and  $E_{OL}$  are -0.85 V and -1.67 V respectively.

The linearized portion of the F100K output characteristic can be represented by two equations:

For

$$V_{OH}$$

:  $V_{OUT} = -850 - 6_{OUT}$

For  $V_{OL}$ :  $V_{OUT} = -1670 - 8_{IOUT}$

where  $I_{\mbox{\scriptsize OUT}}$  is in mA,  $V_{\mbox{\scriptsize OUT}}$  is in mV.

If the range of  $I_{OUT}$  is confined between 8 mA to 40 mA for  $V_{OH},$  and 2 mA to 16 mA for  $V_{OL},$  the output voltage can be estimated within  $\pm$ 10 mV (Figure 6d).

An ECL output can drive two or more lines in parallel, provided the maximum rated current is not exceeded. Another consideration is the effect of various loads on noise margins. For example, two parallel 75 $\Omega$  terminations to -2V (*Figure 6d*) give output levels of approximately -1.000V and -1.716V. Noise margins are thus 35 mV less in the HIGH state and 11 mV more in the LOW state, compared to 50 $\Omega$  load conditions. Conversely, a single 75 $\Omega$  load to -2V causes noise margins 38 mV greater in the HIGH state and 11 mV less in the Low state, compared to a 50 $\Omega$  load.

The magnitude of reflections from the terminated end of the line depends on how well the termination resistance  $R_{\text{\scriptsize T}}$  matches the line impedance  $Z_{\text{\scriptsize O}}.$  The ratio of the reflected voltage to the incident voltage  $V_i$  is the reflection coefficient

$$\frac{V_{r}}{V_{i}} = \rho = \frac{R_{T} - Z_{0}}{R_{T} + Z_{0}} \tag{eq. 5} \label{eq. 5}$$

The initial signal swing at the termination is the sum of the incident and reflected voltages. The ratio of termination signal to incident signal is thus:

$$\frac{V_T}{V_i} = 1 \, + \, \rho = \frac{2R_T}{R_T + Z_0} \tag{eq. 6} \label{eq. 6}$$

The degree of reflections which can be tolerated varies in different situations, but to allow for worst-case circuits, a good rule of thumb is to limit reflections to 15% to prevent excursions into the threshold region of the ECL inputs connected along the line. The range of permissible values of  $R_{\rm T}$  as a function of  $Z_0$  and the reflection coefficient limitations can be determined by rearranging Equation 5.

$$R_T = Z_0 \frac{1+\rho}{1-\rho} \tag{eq. 7}$$

Using 15% reflection limits as examples, the range of the  $\ensuremath{R_T/Z_0}$  ratio is as follows.

$$\frac{1.15}{0.85} > \frac{R_T}{Z_0} > \frac{0.85}{1.15} \quad 1.35 > \frac{R_T}{Z_0} > 0.74 \tag{eq. 8}$$

The permissible range of the  $R_T/Z_0$  ratio determines the tolerance ranges for  $R_T$  and  $Z_0$ . For example, using the foregoing ratio limits,  $R_T$  tolerances of  $\pm 10\%$  allow  $Z_0$  tolerance limits of  $\pm 22\%$  and  $\pm 10\%$ ,  $R_T$  tolerances of  $\pm 5\%$  allow  $Z_0$  tolerance limits of  $\pm 28\%$  and  $\pm 23\%$ .

An additional requirement on the maximum value of R<sub>T</sub> is related to the value of quiescent IOH current needed to insure sufficient negative-going signal swing when the ECL driver switches from the HIGH state to the LOW state. The npn emitter-follower output of the ECL circuit cannot act as a voltage source driver for negative-going transitions. When the voltage at the base of the emitter follower starts going negative as a result of an internal state change, the output current of the emitter follower starts to decrease. The transmission line responds to the decrease in current by producing a negative-going change in voltage. The ratio of the voltage change to the current change is, of course, the characteristic impedance Z<sub>0</sub>. Since the maximum decrease in current that the line can experience is from IOH to zero, the maximum negative-going transition which can be produced is the product  $I_{OH} Z_0$ .

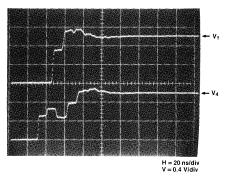

If the  $I_{OH}$   $Z_0$  product is greater than the normal negative-going signal swing, the emitter follower responds by limiting the current change, thereby controlling the signal swing. If, however, the  $I_{OH}$   $Z_0$  product is too small, the emitter follower is momentarily turned off due to insufficient forward bias of its base-emitter junctions, causing a discontinuous negative-going edge such as the one shown in *Figure 14*. In the output-LOW state the emitter follower is essentially nonconducting for  $V_{OL}$  values more positive than about -1.55V. Using this value as a criterion and expressing  $I_{OH}$  and  $V_{OH}$  in terms of the equivalent circuit of *Figure 6c*, an upper limit on the value of  $R_T$  can be developed.

$$\begin{split} \Delta V &= I_{OH} Z_0 > 1.55 - \left| V_{OH} \right| \\ &\left( \frac{E_{OH} - V_{TT}}{R_0 + R_T} \right) Z_0 > 1.55 - \left| \frac{V_{TT} \, R_0 = E_{OH} R_T}{R_0 + R_T} \right| \\ R_T &< \frac{\left( E_{OH} - V_{TT} \right) Z_0 - \left( 1.55 - \left| V_{TT} \right| \right) R_0}{1.55 - \left| E_{OH} \right|} \end{split} \tag{eq. 9}$$

For a V<sub>TT</sub> of  $-2\text{V},\,\text{R}_0$  of  $6\Omega$  and E<sub>OH</sub> of  $-0.85\text{V},\,\text{Equation}$  4-9 reduces to

$$R_T < 1.64 \, Z_0 \, + \, 3.86 \Omega$$

For  $Z_0=50\Omega,$  the emitter follower cuts off during a negative-going transition if  $R_T$  exceeds  $86\Omega.$  Changing the voltage level criteria to -1.60V to insure continuous conduction in the emitter follower gives an upper limit of  $77\Omega$  for a  $50\Omega$  line. For a line terminated at the receiving end with a resistance to -2V, a rough rule-of-thumb is that termination resistance should not exceed line impedance by more than 50%. This insures a satisfactory negative-going signal swing to ECL inputs connected along the line. The quiescent  $V_{OL}$  level, after all reflections have damped out, is determined by  $R_T$  and the ECL output characteristic.

# INPUT IMPEDANCE

The input impedance of ECL circuits is predominately capacitive. A single-function input has an effective value of about 1.5 pF for F100K flatpak, as determined by its effect on reflected and transmitted signals on transmission lines.

In practical calculations, a value of 2 pF should be used. Approximately one third of this capacitance is attributed to the internal circuitry and two thirds to the flatpak pin and internal bonding.

For F100K flatpak circuits, multiple input lines may appear to have up to 3 pF to 4 pF but never more. For example, in the F100102, an input is connected internally to all five gates, but because of the philosophy of buffering these types of inputs in the F100K family this input appears as a unit load with a capacitance of approximately 2 pF. For applications such as a data bus, with two or more outputs connected to the same line, the capacitance of a passive-LOW output can be taken as 2 pF.

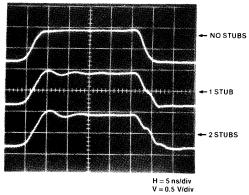

Capacitive loads connected along a transmission line increase the propagation delay of a signal along the line. The modified delay can be determined by treating the load capacitance as an increase in the intrinsic distributed capacitance of the line, discussed in Chapter 3. The intrinsic capacitance of any stubs which connect the inputs to the line should be included in the load capacitance. The intrinsic capacitance per unit length for G-10 epoxy boards is shown in Figure 3 and 5 for microstrip and stripline respectively. For other dielectric materials, the intrinsic capacitance  $C_0$  can be determined by dividing the intrinsic delay  $\delta$  (Equation 3) by the line impedance  $Z_0$ .

The length of a stub branching off the line to connect an input should be limited to insure that the signal continuing along the line past the stub has a continuous rise, as opposed to a rise (or fall) with several partial steps. The point where a stub branches off the line is a low impedance point. This creates a negative coefficient of reflection, which in turn reduces the amplitude of the incident wave as it continues beyond the branch point. If the stub length is short enough, however, the first reflection returning from the end of the stub adds to the attenuated incident wave while it is still rising. The sum of the attenuated incident wave and the first stub reflection provides a step-free signal, although its rise time will be longer than that of the original signal. Satisfactory signal transitions can be assured by restricting stub lengths according to the recommendations for unterminated lines (Figure 10). The same considerations apply when the termination resistance is not connected at the end of the line; a section of line continuing beyond the termination resistance should be treated as an unterminated line and its length restricted accordingly.

# **SERIES TERMINATION**

Series termination requires a resistor between the driver and transmission line, *Figure 7*. The receiving end of the line has no termination resistance. The series resistor value should be selected so that when added to the driver source resistance, the total resistance equals the line impedance. The voltage divider action between the net series resistance and the line impedance causes an incident wave of half amplitude to start down the line. When the signal arrives at the unterminated end of the line, it doubles and is thus restored to a full amplitude. Any reflections returning to the source are absorbed without further reflection since the line and source impedance match. This feature, source absorption, makes series termination attractive for interconnection paths involving impedance discontinuities, such as occur in backplane wiring.

A disadvantage of series termination is that driven inputs must be near the end of the line to avoid receiving a 2-step signal. The initial signal at the driver end is half amplitude, rising to full amplitude only after the reflection returns from the open end of the line. In *Figure 7*, one load is shown connected at point D, aways from the line end. This input receives a full amplitude signal with a continuous edge if the distance I to the open end of the line is within recommended lengths for unterminated line (*Figure 10*).

FIGURE 7. Series Termination

The signal at the end has a slower rise time that the incident wave because of capacitive loading. The increase in rise time to the 50% point effectively increases the line propagation delay, since the 50% point of the signal swing is the input signal timing reference point. This added delay as a function of the product line impedance and load capacitance is discussed in Chapter 3.

Quiescent  $V_{OH}$  and  $V_{OL}$  levels are established by resistor  $R_E$  (*Figure 7*), which also acts with  $V_{EE}$  to provide the negative-going drive into  $R_S$  and  $Z_0$  when the driver output goes to the LOW state. To determine the appropriate  $R_E$  value, the driver output can be treated as a simple mechanical switch which opens to initiate the negative-going swing. At this instant,  $Z_O$  acts as a linear resistor returned to  $V_{OH}$ . Thus the components form a simple circuit of  $R_E$ ,  $R_S$  and  $Z_O$  in a series, connected between  $V_{EE}$  and  $V_{OH}$ . The initial current in this series circuit must be sufficient to introduce a 0.38V transient into the line, which then doubles at the load end to give 0.75V swing.

$$I_{RE} = \frac{V_{OH} - V_{EE}}{R_E + P_S + Z_0} \ge \frac{0.38}{Z_0} \tag{eq. 10} \label{eq:IRE}$$

Any  $I_{OH}$  current flowing in the line before the switch opens helps to generate the negative swing. This current may be quite small, however, and should be ignored when calculating  $R_{E}$ .

Increasing the minimum signal swing into the line by 30% to 0.49V insures sufficient pull-down current to handle reflection currents caused by impedance discontinuities and load capacitance. The appropriate  $R_{\mbox{\footnotesize E}}$  value is determined from the following relationship.

$$\frac{V_{OH} - V_{EE}}{R_E + R_S + Z_0} \ge \frac{0.49}{Z_0} \tag{eq. 11} \label{eq:eq. 11}$$

For the  $R_E$  range normally used, quiescent  $V_{OH}$  averages approximately 0.955V and  $V_{EE}=-4.5 V.$  The value of  $R_S$  is equal to  $Z_0$  minus  $R_0$  ( $R_0$  averages  $7\Omega)$ . Inserting these values and rearranging Equation 11 gives the following.

$$R_{\text{E}} \leq 5.23 \, Z_0 \, + \, 7\Omega \tag{eq. 12} \label{eq:eq. 12}$$

Power dissipation in  $R_E$  is listed in *Figure 14*. The power dissipation in  $R_E$  is greater than in  $R_T$  of a parallel termination to -2V, but still less than the two resistors of the Thevenin equivalent parallel termination, see *Figure 10, 13* and *14*.

The number of driven inputs on a series terminated line is limited by the voltage drop across  $R_{\rm S}$  in the quiescent HIGH state, caused by the finite input currents of the ECL loads.  $I_{\rm IH}$  values are specified on data sheets for various types of

inputs, with a worst-case value of 265  $\mu A$  for simple gate inputs. The voltage drop subtracts from the HIGH-state noise margin as outlined in *Figure 8a*.

However, there is more HIGH-state noise margin initially, because there is less  $I_{OH}$  with the  $R_E$  load than with the standard  $50\Omega$  load to -2V. This makes  $V_{OH}$  more positive; the increase ranges from 43 mV for a  $50\Omega$  line to 82 mV for a  $100\Omega$  line. Using this  $V_{OH}$  increase as a limit on the voltage drop across  $R_S$  assures that the HIGH-state noise margin is as good as in the parallel terminated case. Dividing the  $V_{OH}$  increase by  $R_S+R_0$  (=  $Z_0$ ) gives the allowed load input current (Ix in Figure 8a). This works out to 0.86 mA for a  $50\Omega$  line, 0.92 mA for a  $75\Omega$  line and 0.82 mA for a  $100\Omega$  line. Load input current greater than these values can be tolerated at some sacrifice in noise margin. If, for example, an additional 50 mV loss is feasible, the maximum values of current become 1.86 mA, 1.59 mA and 1.32 mA for  $50\Omega$ ,  $75\Omega$  and  $100\Omega$  lines respectively.

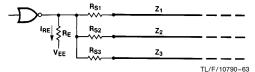

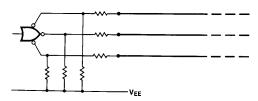

An ECL output can drive more than one series terminated line, as suggested in *Figure 8b*, if the maximum rated output current of 50 mA is not exceeded. Also, driving two or more lines requires a lower  $R_{\rm E}$  value. This makes the quiescent  $I_{\rm OH}$  higher and consequently  $V_{\rm OH}$  lower, due to the voltage drop across  $R_{\rm O}$ . This voltage drop decreases the HIGH-state noise margin, which may become the limiting factor (rather than the maximum rated current), depending on the particular application.

The appropriate  $\rm R_{E}$  value can be determined using Equation 13 for  $\rm V_{EE}\,=\,-\,4.5V.$

$$\frac{1}{R_E} \ge \frac{1}{6.23 \, Z_1 - R_{S1}} + \frac{1}{6.23 \, Z_2 - R_{S2}} + \frac{1}{6.23 \, Z_3 - T_{S3}}$$

(eq. 13)

Circuits with multiple outputs (such as the F100112) provide an alternate means of driving several lines simultaneous (*Figure 8c*). Note, each output should be treated individually when assiging load distribution, line impedance, and  $R_E$  value.

# **UNTERMINATED LINES**

Lines can be used without series or parallel termination if the line delay is short compared to the signal rise time. Ringing occurs because the reflection coefficient at the open (receiving) end of the line is positive (nominally +1) while the reflection coefficient at the driving end is negative (approximately -0.8). These opposite polarity reflection coefficients cause any change in signal voltage to be reflected back and forth, with a polarity change each time the signal is reflected from the driver. Net voltage change on the line is thus a succession of increments with alternating polarity and decreasing magnitude. The algebraic sum of these increments if the observed ringing. The general relationships among rise time, line delay, overshoot and undershoot are discussed in Chapter 3, using simple waveforms for clarity. Excessive overshoot on the positive-going edge of the signal drives input transistors into saturation. Although this does not damage an ECL input, it does cause excessive recovery times and makes propagation delays unpredict-

TL/F/10790-62

# a. Noise Margin Loss Due to Load Input Current

#### b. Driving Several Lines from one Output

TL/F/10790-64

# c. Using Multiple Output Element for Load Sharing

# FIGURE 8. Loading Considerations for Series Termination

able. Undershoot (following the overshoot) must also be limited to prevent signal excursions into the threshold region of the loads. Such excursions could cause exaggerated transition times at the driven circuit outputs, and could also cause multiple triggering of sequential circuits. Signal swing, exclusive of ringing, is slightly greater on unterminated lines that on parallel terminated lines;  $I_{OH}$  is less and  $I_{OL}$  is greater with the  $R_{E}$  load, (Figure 9a) making  $V_{OH}$  higher and  $V_{OL}$  lower.

For worst case combinations of driver output and load input characteristics, a 35% overshoot limit insures that system speed is not compromised either by saturating an input on overshoot or extending into the threshold region on the following undershoot.

For distributed loading, ringing is satisfactorily controlled if the 2-way modified line delay does not exceed the 20% to 80% rise time of the driver output. This relationship can be expressed as follows, using the symbols from Chapter 3 and incorporating the effects of load capacitance on line delay.

$$t_r = 2T' = 2 \ell \delta' = 2 \ell \delta \sqrt{1 + \frac{C_L}{\ell C_0}}$$

Solving this expression for the line length (  $\ell$  ):

$$\ell_{\text{max}} = \frac{1}{2} \sqrt{\left(\frac{C_L}{C_0}\right)^2 + \left(\frac{t_r}{\delta}\right)^2} - \frac{C_L}{2C_0}$$

(eq. 14)

a. Unterminated Line

b. Line Voltages Showing Stair-step Trailing Edges

H = 1 ns/div

= 0.3 V/div TL/F/10790-67

c. Load Gate Output Showing Net Propagation Increase for Increasing Values of R<sub>E</sub>: 330 $\Omega$ , 510 $\Omega$ , 1 k $\Omega$

# FIGURE 9. Effect on R<sub>E</sub> Value on Trailing-Edge Propagation

The shorter the rise time, the shorter the premissible line length. For F100K ECL, the minimum rise time from 20% to 80% is specified as 0.5 ns. Using this rise time and 2 pF per fan-out load, calculated maximum line lengths for G-10 epoxy microstrip are listed in *Figure 10a*. The length ( $\ell$ ) in the table is the distance from the terminating resistor to the input of the device(s). For F100K ECL the case described in *Figure 10a* is the only one calculated, since all other combinations are approximately the same. For other combinations of rise time, impedance, fan-out or line characteristics

( $\delta$  and C<sub>0</sub>), maximum lengths are calculated using Equation 14. For the convenience of those who are also using 10K ECL, maximum recommended lengths of unterminated lines are listed in *Figure 10b* to *10e*.

| Z <sub>0</sub> | Number of Fan-Out Loads |      |      |      |  |  |

|----------------|-------------------------|------|------|------|--|--|

| 20             | 1                       | 2    | 3    | 4    |  |  |

| 50             | 1.37*                   | 1.13 | 0.95 | 0.81 |  |  |

| 62             | 1.33                    | 1.07 | 0.87 | 0.70 |  |  |

| 75             | 1.25                    | 0.95 | 0.75 | 0.61 |  |  |

| 90             | 1.18                    | 0.85 | 0.66 | 0.53 |  |  |

| 100            | 1.15                    | 0.82 | 0.61 | 0.49 |  |  |

<sup>\*</sup>Length in inches.

TL/F/10790-65

Unit load = 2 pF,  $\delta$  = 0.148 ns/inch

# FIGURE 10a. F100K Maximum Worst-Case Line Lengths for Unterminated Microstrip, Distributed Loading

| Z <sub>0</sub> | Number of Fan-Out Loads |      |      |      |      |  |

|----------------|-------------------------|------|------|------|------|--|

| 20             | 2                       | 3    | 4    | 6    | 8    |  |

| 50             | 4.15*                   | 3.75 | 3.45 | 2.85 | 2.45 |  |

| 62             | 3.95                    | 3.50 | 3.15 | 2.55 | 2.10 |  |

| 75             | 3.75                    | 3.25 | 2.85 | 2.25 | 1.85 |  |

| 90             | 3.55                    | 3.00 | 2.60 | 2.00 | 1.60 |  |

| 100            | 3.45                    | 2.85 | 2.45 | 1.85 | 1.45 |  |

<sup>\*</sup>Length in inches.

Unit load = 3 pF,  $\delta$  = 0.148 ns/in.

# FIGURE 10b. 10K Maximum Worst-Case Line Lengths for Unterminated Microstrip, Distributed Loading

| $z_0$ | Number of Fan-Out Loads |      |      |      |      |  |  |

|-------|-------------------------|------|------|------|------|--|--|

| -0    | 1                       | 2    | 4    | 6    | 8    |  |  |