# Interfacing the NS32CG821 to the NS32CG16

#### National Semiconductor Application Note 576 Chris Koehle Rich Levin May 1989

#### INTRODUCTION

This application note explains how to interface the NS32CG821 to the NS32CG16 microprocessor. It is assumed that the reader is familiar with the NS32CG16 access cycles and operation of the NS32CG821.

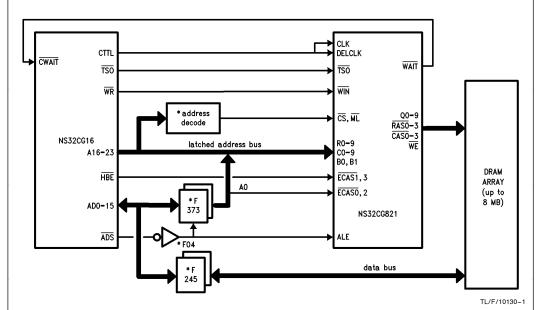

#### **DESIGN DESCRIPTION**

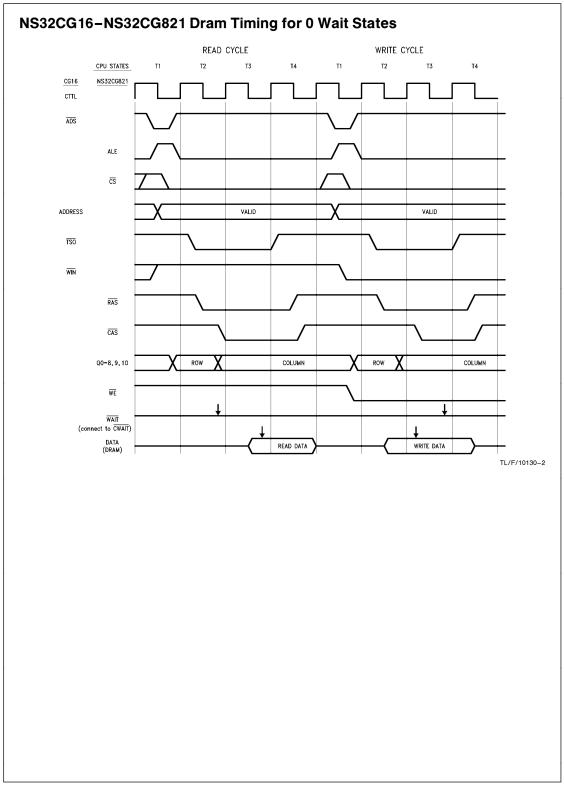

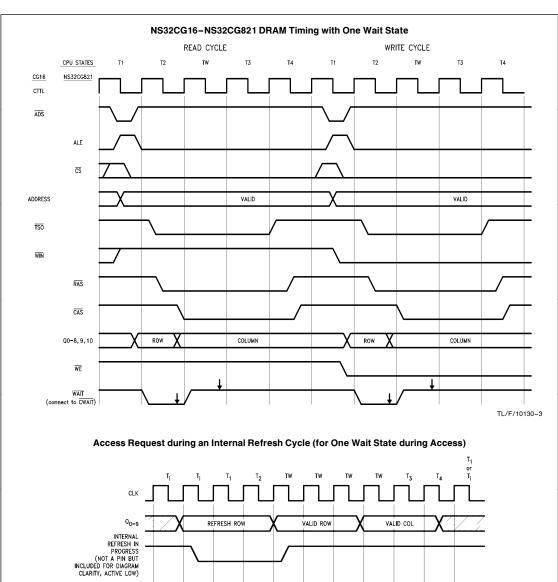

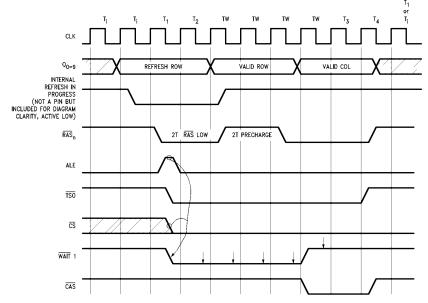

This design is a simple circuit to interface the NS32CG821 to the NS32CG16 and up to 8 Mbytes of DRAM. An access cycle begins when the NS32CG16 asserts the  $\overline{\text{ADS}}$  signal and places a valid address on the bus. The  $\overline{\text{ADS}}$  places a pair of 74F373 fall-through latches in fall-through mode and on the negating edge of ADS latches the address to guarantee that the address is valid throughout the entire access. The  $\overline{\text{ADS}}$  signal is inverted to produce the signal ALE to the NS32CG821. On the next rising clock edge, after the ALE signal is asserted, the NS32CG821 will assert RAS. After guaranteeing the row address hold time, t<sub>RAH</sub>, the NS32CG821 will place the column address on the DRAM address bus, guarantee the column address setup time and assert CAS. During read cycles, the DRAM will place valid data on the bus after the DRAM, t<sub>CAC</sub>, timing has been met. During write cycles, CAS will be delayed until after T3re, to ensure that the CPU's write data is valid before  $\overline{\text{CAS}}$  is asThe N32CG821 will also take complete care of the DRAM's refresh needs. There is an internal 15 microsecond timer, and a refresh address counter. Refresh access arbitration will be controlled by an internal state machine. It will allow current cycles to complete before starting the refresh cycle. If a refresh cycle is in progress the NS32CG16 will be held off completing the access by asserting the CWAIT signal to the NS32CG16

During programming of the chip, it is recommended that the user gate  $\overline{\text{ML}}$  (Mode Load) and  $(\overline{\text{TSO}})$  (Timing State Output) for the connection onto the  $\overline{\text{ML}}$  pin of the NS32CG821. This is to ensure that the chip will be programmed while a valid access address is present.

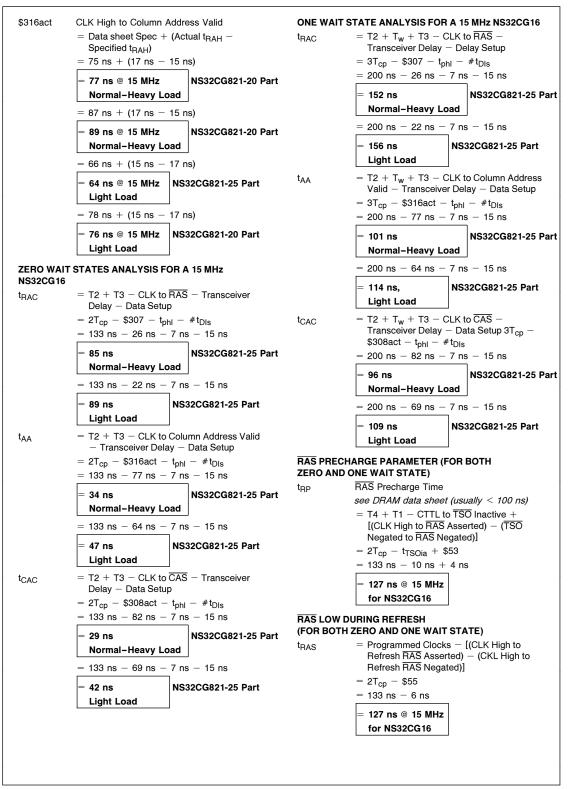

Timing parameters are referenced to the numbers shown in the NS32CG821 data sheet, and are included in each equation in *italics* to indicate the target specifications that need to be satisfied. Times that begin with a "\$" refer to the NS32CG821 data sheet unless otherwise stated times use "NS32CG821-20" part's parameters with heavy loading; these times are generally worse than the "NS32CG821-25" part. Times that begin with a "#" refer to the NS32CG16 data sheet. Equations are provided so that the user can calculate timing based on their frequency and application.

## NS32CG16-NS32CG821 Connection Diagram

\*Standard components in any NS32CG16 design.

\N-576

```

DESIGN TIMING PARAMETERS

Timing parameter to guarantee RAS Precharge with 2 Clock

Precharge

Timing diagrams are supplied further on in this document.

$29b:

TSO negated Setup to CLK High

Clock Period = T_{cp}10 = 100 ns @ 10 MHz

with > 1 Period of Precharge

= T_{cp}15 = 66 \text{ ns } @ 15 \text{ MHz}

19 ns Min @ NS32CG821-20,

$300:

CS Asserted to CLK High (only A20-A23 are

15 ns Min @ NS32CG821-25

used for decode)

= T4 - CTTL to TSO Inactive

14 ns Min @ NS32CG821-20, 13 ns Min @

= T_{cp} - \#TSO_{ia}

NS32CG821-25

= 100 ns -12 ns

= T1 - (CTTL to address valid + B-PAL de-

lay)

88 ns @ 10 MHz

= T_{cp} - \#t_{AHv} - t_{Bpal}

= 66 ns -10 ns

= 100 \text{ ns} - 40 \text{ ns} - 15 \text{ ns}

= 56 ns @ 15 MHz

= 45 ns @ 10 MHz

CWAIT:

Setup for Wait States, before T3re

= 66 ns - 30 ns - 15 ns

#tCWs, 20 ns Min @ 10 MHz

= 21 ns @ 15 MHz

& 15 MHz for NS32CG16

= T1 + T2 - (Time in T1 until \overline{CS}

$301a:

ALE Setup to CLK High

Asserted + \overline{CS} to \overline{WAIT} Asserted)

16 ns Min @ NS32CG821-20,

= 2T_{cp} - (\#T_{AHv} + t_{Bpal} + \$311)

15 ns Min @ NS32CG821-25

= 200 \text{ ns} - (40 \text{ ns} + 15 \text{ ns} + 26 \text{ ns})

= T1 - Inverter Max - CTTL to \overline{ADS}

= T_{cp} - t_{plh} - \#t_{ADSa}

= 119 ns @ 10 MHz

= 100 \text{ ns} - 5 \text{ ns} - 35 \text{ ns}

= 133 \text{ ns} - (30 \text{ ns} + 15 \text{ ns} + 22 \text{ ns})

= 60 ns @ 10 MHz

66 ns @ 15 MHz

66 \text{ ns} - 5 \text{ ns} - 26 \text{ ns}

CWAIT:

Hold, after T3re

= 35 ns @ 15 MHz

#tCWh, 5 ns Min @ 10 MHz

& 15 MHz for NS32CG16

$302:

ALE Pulse Width

= T3re to WAIT Negated

18 ns Min @ NS32CG821-20,

= $17 Min

13 ns Min @ NS32CG821-25

7 ns @ NS32CG821-20

= #t<sub>ADSw</sub>

= 7 ns @ NS32CG821-25

= 30 ns @ 10 MHz

CWAIT:

Setup for Termination of Access

= 25 ns @ 15 MHz

#tCWs. 20 ns Min

$303 & $304: Address Setup to CLK

@ 10 MHz & 15 MHz

20 ns Min @ NS32CG821-20.

for NS32CG16

18 ns Min @ NS32CG821-25

= T3 - CLK to \overline{\text{WAIT}} Negated

= T_{cp} - $17 Max

= T1 - CTTL to Address - F373 In to Out

= 100 ns - 39 ns

= T_{cp} - t_{AHv} - t_{phl}

= 100 \text{ ns} - 40 \text{ ns} - 6 \text{ ns}

= 61 ns @ 10 MHz | NS32CG821-20 Part

= 54 ns @ 10 MHz

= 66 \text{ ns} - 39 \text{ ns}

66 ns - 30 ns - 6 ns

= 27 ns @ 15 MHz | NS32CG821-20 Part

= 30 ns @ 15 MHz

DRAM SPECIFIC TIMING WHEN USING

$310:

WIN Setup to CLK High that starts the access

THE NS32CG16 @ 10 MHz

RAS (to guarantee CAS is delayed)

Since systems and DRAM times vary, the user is encour-

-21 ns Min @ NS32CG821-20 &

aged to change the following equations to match their sys-

tem requirements. Timing has been supplied for systems

-16 ns Min @ NS32CG821-25

with 0 or 1 wait states. The times assume worst case load.

= T1 - (time until \overline{WR} active)

As such, the time will improve with lower circuit loads.

= T_{cp} - (T_{cp} + t_{WRa})

= 100 \text{ ns} - (100 \text{ ns} + 20 \text{ ns})

= -20 ns @ 10 MHz

= 66 \text{ ns} - (66 \text{ ns} + 15 \text{ ns})

- 15 ns @ 15 MHz

```

```

DRAM SPECIFIC TIMING WHEN USING THE NS32CG16

Zero Wait States Analysis for a 10 MHz NS32CG16

@ 15 MHz

= T2 + T3 - CLK to \overline{RAS} - Transceiver

t_{RAC}

The input DELCLK controls the internal delay line and

Delay - Data Setup

should be a multiple of 2 MHz. Since DELCLK is 15 MHz

=\,2T_{cp}\,-\,\$307\,-\,t_{phl}\,-\,\#\,t_{DIs}

(when directly connected to CTTL) and is not a multiple of

= 200 \text{ ns} - 32 \text{ ns} - 7 \text{ ns} - 18 \text{ ns}

2 MHz, t<sub>RAH</sub> and t<sub>ASC</sub> will vary from the programmed times

= 143 ns @ 10 MHz | NS32CG821-20 Part

according to the equations listed below.

In addition, please note the following pertaining to the timing

= T2 + T3 - CLK to Column Address Valid

t_{AA}

equations:

- Transceiver Delay - Data Setup

1. Times for t_{\mbox{\scriptsize RAH}} and t_{\mbox{\scriptsize ASC}} at light loads are specified 2 ns

= 2T_{cp} - \$316act - t_{phl} - \#t_{Dls}

longer than for normal-heavy loads. (See data sheet

= 200 \text{ ns} - 87 \text{ ns} - 7 \text{ ns} - 18 \text{ ns}

2. Light load is defined as 4 banks of four x 4 DRAMs

= 88 ns @ 10 MHz | NS32CG821-20 Part

3. When using normal-heavy loads at 15 MHz a DELCLK

= T2 + T3 - CLK to \overline{CAS} - Transceiver

t_{CAC}

divisor of 8 is used and when using light loads at 15 MHz

Delay - Data Setup

a DELCLK divisor of 7 is used.

= 2T_{cp} - \$308act - t_{phl} - \#t_{Dls}

= 200 ns - 89 ns - 7 ns - 18 ns

= 30 * [(DELCLK divisor * 2 MHz/DELCLK

t<sub>RAHact</sub>

freq) -1] ns +15 ns (+2 ns for light load

only)

= 86 ns @ 10 MHz NS32CG821-20 Part

= 30 * [(8 * 2 MHz/15 MHz) - 1]ns + 15 ns

One Wait State Analysis for a 10 MHz NS32CG16

= 17 ns @ 15 MHz

= T2 + T<sub>w</sub> + T3 - CLK to \overline{RAS} -

t_{RAC}

Normal-Heavy Loads

Transceiver Delay - Data Setup

= 3T<sub>cp</sub> - $307 - t<sub>phl</sub> - #t<sub>Dls</sub>

= 30 * [(7 * 2 MHz/15 MHz) - 1]ns + 15 ns

= 300 ns - 32 ns - 7 ns - 18 ns

+ 2 ns

= 243 ns @ 10 MHz | NS32CG821-20 Part

= 15 ns @ 15 MHz

Light Loads

= T2 + T<sub>w</sub> + T3 - CLK to ColumnAddress

t_{AA}

Valid - Transceiver Delay - Data Setup

= 15 * [DELCLK Divisor * 2 MHz/DELCLK

t<sub>ASCact</sub>

= 3T_{cp} - \$316act - t_{phl} - \#t_{Dls}

Freq]ns - 15 ns (+2 ns for light load only)

= 300 \text{ ns} - 87 \text{ ns} - 7 \text{ ns} - 18 \text{ ns}

= 15 * [8 * 2 MHz/15 MHz]ns - 15 ns

= 188 ns @ 10 MHz | NS32CG821-20 Part

1 ns @ 15 MHz

Normal-Heavy Loads

= T2 + T<sub>w</sub> + T3 - CLK to \overline{CAS} -

tCAC

Transceiver Delay - Data Setup

= 15 * [(7 * 2 MHz/15 MHz] ns - 15 ns + 2

= 3T_{cp} - \$308act - t_{phl} - \#t_{Dls}

= 300 \text{ ns} - 89 \text{ ns} - 7 \text{ ns} - 18 \text{ ns}

1 ns @ 15 MHz

= 186 ns @ 10 MHz | NS32CG821-20 Part

Light Loads

RAS Precharge Parameter (for both zero and one wait

PARAMETER ADJUSTMENTS FOR 15 MHz DELCLK

state)

DUE TO CHANGED tRAH and tASC

RAS Precharge Time

t_{RP}

$308act

CLK High to \overline{CAS} = Data Sheet Spec +

see DRAM data sheet (usually < 100 ns)

(Actual t<sub>RAH</sub> - Spec t<sub>RAH</sub>) + (Actual t<sub>ASC</sub> -

= T4 + T1 - CTTL to \overline{TSO} inactive +

Spec t<sub>ASC</sub>)

[(CLK high to \overline{RAS} asserted) – (\overline{TSO}

= 79 \text{ ns} + (17 \text{ ns} - 15 \text{ ns}) + (1 \text{ ns} - 0 \text{ ns})

negated to RAS negated)]

82 ns @ 15 MHz NS32CG821-25 Part

= 2T_{cp} - #t_{TSOia} + $53

Heavy Load

200 ns - 12 ns + 4 ns

89 \text{ ns} + (17 \text{ ns} - 15 \text{ ns}) + (1 \text{ ns} - 0 \text{ ns})

192 ns @ 10 MHz for NS32CG16

92 ns @ 15 MHz NS32CG821-20 Part

RAS Low During Refresh (for both zero and one wait state)

Heavy Load

= Programmed Clocks - [(CLK High to

t<sub>RAS</sub>

Refresh RAS asserted) - (CLK High to

72 \text{ ns} + (15 \text{ ns} - 17 \text{ ns}) + (1 \text{ ns} - 2 \text{ ns})

Refresh RAS negated)]

69 ns @ 15 MHz | NS32CG821-25 Part

= 2T_{CD} - $55

Light Load

= 200 \text{ ns} - 5 \text{ ns}

81 \text{ ns} + (15 \text{ ns} - 17 \text{ ns}) + (1 \text{ ns} - 2 \text{ ns})

195 ns @ 10 MHz for NS32CG16

78 ns @ 15 MHz NS32CG821-20 Part

Light Load

```

| ogramming Bits* |              |                                                                                      |

|-----------------|--------------|--------------------------------------------------------------------------------------|

| Bit             | Value        | Description                                                                          |

| R1, R0          | 1, 0         | $\overline{RAS}$ Low during Refresh = 2T $\overline{RAS}$ Precharge Time = 2T        |

| R3, R2          | 0, 0<br>1, 1 | No Wait States during Non-Delayed Access<br>One Wait State during Non-Delayed Access |

| R5, R4          | 0, 0         | No Wait States during Burst                                                          |

| R6              | User Defined | Add Wait States with WAITIN                                                          |

| R9              | User Defined | Staggered or all RAS Refresh                                                         |

| C0, C1, C2      | **           | Divisor for DELCLK                                                                   |

| C3              | ***          | Time between Refreshes                                                               |

| C6, C5, C4      | User Defined | Depends on User's DRAM Configurations                                                |

| C7              | 1            | Choose t <sub>ASC</sub> = 0 ns                                                       |

| C8              | 1            | Choose t <sub>RAH</sub> = 15 ns                                                      |

| C9              | 1            | Delay CAS for Write Accesses                                                         |

| В0              | 1            | Address Latches are Fall Through                                                     |

| _ <u></u>       | ·            | 222 23333                                                                            |

$<sup>^{*}</sup>$   $\overline{\text{ECASO}}$ , B1, and R7 must be programmed low and R8 must be programmed high for operation of chip.

<sup>\*\*</sup>Choose C2, C1, C0 =

<sup>1, 0, 1</sup> for NS32CG16 @ 10 MHz 0, 1, 0 for NS32CG16 @ 15 MHz, w/Heavy Load 0, 1, 1 for NS32CG16 @ 15 MHz, w/Light Load

<sup>\*\*\*</sup> Choose C3 =

<sup>0</sup> for NS32CGG16 @ 10 MHz

<sup>1</sup> for NS32CG16 @ 15 MHz Normal-Heavy Load 0 for NS32CG16 @ 15 MHz Light Load

TL/F/10130-4

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**AN-576**

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor**

Europe Fax: (+49) 0-180-530 85 86 Fax: (+49) 0-180-530 85 86 Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 78 38 Italiano Tel: (+49) 0-180-534 16 80

**National Semiconductor** National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 **National Semiconductor** Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408