# nterfacing A Serial EEPROM to the National HPC16083

# AN-552

# Interfacing A Serial EEPROM to the National HPC16083

National Semiconductor Application Note 552 Brian Marley September 1988

# **ABSTRACT**

This application note describes how to interface the HPC16083 High-Performance microController to a MI-CROWIRE™ serial EEPROM (Electrically Erasable Programmable Read-Only Memory) device. The technique uses interrupt-driven scheduling from one of the eight on-chip timers, and so can run in the "background", sharing the HPC gracefully with other control applications running at the same time. Source code is included.

# 1.0 INTRODUCTION

It is often the case in control-oriented applications that a piece of equipment, on being installed, must be set up with certain semi-permanent configuration mode settings. In the past, jumpers and switches have been the methods used, but in recent years these have been largely supplanted by EEPROM devices, which hold more information and are not prone to mechanical problems. In addition, the presence of an EEPROM allows certain information about the status of the equipment (for example, in printers, a page or character count for monitoring the "age" of the cartridge or print head) to be stored to assist in maintenance.

The most cost-effective type of EEPROM device is one with a serial interface, such as the 256-bit NMC9306 (COP494) or the 1024-bit NMC9345 (COP495). These reside in an

8-pin DIP package, and require only four connections (besides  $V_{CC}$  and Ground). These connections are provided by the HPC family of High-Performance Microcontrollers, on a serial port called the MICROWIRE/PLUSTM Interface.

Because one of the HPC's strong suits is Concurrent Control applications (applications in which several control tasks are executing simultaneously, scheduled by interrupts), the code given in this exercise is written to be completely interrupt-driven as well. Instead of timing events with software loops, interrupts from HPC Timer T5 are used both to signal the end of each MICROWIRE transfer and to time the ERASE and WRITE pulse durations for the EEPROM.

# 2.0 CONNECTIONS AND COMMANDS

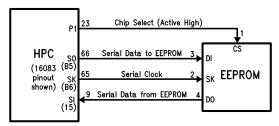

The connection between the HPC and the EEPROM device is a completely traditional MICROWIRE connection, as shown in *Figure 1*. The SI (Serial Input), SO (Serial Output) and SK (Serial Clock) signals of the HPC connect directly to the DO, DI and SK pins of the EEPROM, respectively. The EEPROM's required Chip Select signal (CS: active high) could come from any port bit of the HPC, but the P1 pin of Port P was chosen because Port P pins present zeroes on reset (instead of floating), and this will automatically deselect the EEPROM.

FIGURE 1. MICROWIRE/PLUS Connections

TL/DD/9978-1

MICROWIRE™ and MICROWIRE/PLUS™ are trademarks of National Semiconductor Corporation

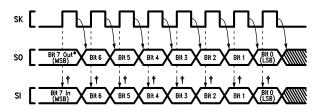

To communicate with the EEPROM, the signal CS (pin P1) is set high, and then each 8-bit serial transfer is triggered by writing a value to the HPC's eight-bit SIO register, which is effectively just a shift register. The data placed into the SIO register is shifted out, most-significant bit first, and eight clock pulses are presented on the SK pin corresponding to each shift. Serial data is simultaneously accepted from the SI pin, and at the end of the eight clock pulses the SIO register has been changed to reflect the value presented by the EEPROM (if any). The timing involved in a single MI-CROWIRE transfer is shown in *Figure 2*.

While reading from the EEPROM, the value written to SIO doesn't matter, since it is ignored by the EEPROM. The CS signal must be active throughout a command (which may involve more than one eight-bit transfer), and it must be set inactive between commands for at least one microsecond. Also, the time between an ERASE or WRITE command and the following command (as measured by the amount of time the CS signal remains low between them) determines the length of the corresponding ERASE or WRITE pulse within the EEPROM chip. These pulse widths have strict limits which, if exceeded, can damage some EEPROMs.

EEPROM commands are 8-bit values. However, they must start with an additional "1" bit (the Start bit), and READ commands require a trailing "pad" bit, to provide timing

control for the access. Since HPC MICROWIRE transfers must consist of integral numbers of 8-bit transfers, at least two such transfers must be used per command.

Note that the formats shown below (with 6 address bits) support an EEPROM with up to 1K bits (64 16-bit words). To use a 256-bit EEPROM, one would not specify an address greater than binary 001111, because the two most-significant address bits are ignored by the EEPROM.

### 2.1 Read Commands

Reading a 16-bit word from the EEPROM is accomplished with a single READ command. For the READ command, the format is:

where the bits marked "A" constitute the address of the EEPROM word to be accessed. These two command transfers are followed by two additional 8-bit transfers, in which the 16 bits of data from the addressed EEPROM word are read by the HPC (most significant bit first).

TL/DD/9978-2

\*This bit becomes valid immediately when the transmitting device loads its SIO register. The HPC guarantees it to be valid for at least 1 full SK period before the rising edge of the first SK pulse presented.

† Arrows indicate points at which SI is sampled.

# FIGURE 2. MICROWIRE/PLUS Transfer

Master presents eight pulses on SK pin; each pulse transfers one bit in and out.

# 2.2 Write Commands

To write data into the EEPROM, a sequence of commands is entered:

```

an EWEN command (Erase/Write Enable):  0 \ 0 \ 0 \ 0 \ 0 \ 1 \qquad 0 \ 0 \ 1 \ 1 \ 0 \ 0 \ 0  an ERASE command:

```

most-significant bit first)

a pause of 16 to 25 milliseconds, with CS low.

a WRITE command:

"D" = Data bits,

most-significant bit first)

a pause of 16 to 25 milliseconds, with  $\mathtt{CS}$  low,

and, finally, an EWDS command (Erase/Write

Disable):

00000001 0000000

## 3.0 LISTING AND COMMENTARY

The listing provided shows three necessary segments of a program to access the EEPROM device:

- 1) initialization of the MICROWIRE/PLUS port on the HPC,

- 2) two program fragments of a Main Program which would initiate a Read or a Write operation,

- 3) an interrupt service routine (attached to Timer T5) which actually performs the transfers.

# 3.1 Initialization

On receiving a Reset signal, the HPC begins execution at the label "start". It loads the PSW register (to select 1 Wait state), and then removes all interrupt enables.

At label "sram", all RAM within the HPC is initialized to zero.

At "suwire", the MICROWIRE/PLUS interface pins are initialized. The MICROWIRE/PLUS interface is then set to the CKI/128 bit rate (125 KHz clocking at 16 MHz crystal frequency). The internal interface is not completely cleared by the Reset signal, so the firmware must set it up and wait (at label "suwlp") for the interface to become ready. Once this has been done, a byte of all zeroes is sent to the EEPROM to terminate any Write operation that might have been in progress when the Reset was received.

At "tminit", the timers T1-T7 are stopped and any interrupts pending from timers T0-T7 are cleared. The individual timer interrupt enables are then cleared.

The program then continues to label "minit", which initializes the variables in the HPC's on-chip RAM to their proper contents.

At label "runsys", the necessary interrupt is enabled (from the timers), and execution continues to the body of the Main Program.

There follow now two fragments of illustrative main program code which can be used to trigger the process of reading and writing the EEPROM.

### 3.2 Reading

The main program and interrupt routines given here enable reading from one to eight bytes from the EEPROM, starting at the beginning of any word.

At label "rnvr", an EEPROM READ command is constructed from the EEPROM starting address and placed in the variable "nvrcmd". The number of bytes to be transferred is placed in the variable "nvrnum". Control is then transferred to the label "nvrx", where Timer T5 is set up to generate scheduling interrupts for reading data from the EEPROM.

The variable "nvrs" indicates the state of an EEPROM access from one interrupt to another: its top bit ("nvravl") shows whether the EEPROM is already being used, bit 6 ("nvrwr") shows whether it is being written or read, and the low-order 4 bits hold a state number, which is used to transfer control to the appropriate code within the Timer T5 interrupt service routine.

On each Timer T5 interrupt (see labels "tmrint", "t5poll", "t5int"), the timer is stopped, a check is made to determine whether the EEPROM is being read or written (T5 interrupts are used for both), and then a multiway branch (jidw) is performed based on the state number in the variable "nvrs". The state number is incremented on each interrupt. On a Read transfer, five states are entered, at the following labels:

t5rd0 activates the chip select to the EEPROM and initiates the MICROWIRE transfer to send the first byte of a READ command. Timer T5 is started to time out the MICROWIRE transfer.

t5rd1 sends the second byte of the READ command.

Timer T5 is started to time out the MICROWIRE

t5rd2 initiates the MICROWIRE transfer to read the first byte of data from the current EEPROM word. Timer T5 is started to time out the MICROWIRE transfer

t5rd3 accepts the first byte of the data into the high-order byte of the variable "inword", and initiates the transfer to read the second byte of the current EEPROM word. Timer T5 is started to time out the MICROWIRE transfer.

t5rd4 accepts the second byte from the EEPROM into the low-order byte of the variable "nvword", and then moves the word into the EEPROM string buffer, called "nvrbuf", using a pointer called "nvrptr". It then checks whether the requested number of bytes has been read (by decrementing the "nvrnum" variable). If so, it leaves Timer T5 stopped, disables its interrupt and returns. This would also be the proper place to set a semaphore flag to acknowledge to the main program that the reading is complete. (Code for this is not included here: it would vary from system to system.) If the requested number of bytes has not yet been read, it increments the address field of the READ command in "nvrcmd", resets the state field in "nvrs" to zero, leaves Timer T5 interrupts enabled, and jumps directly to the "t5rd0" routine to continue.

# 3.3 Writing

At label "wnvr", an EEPROM ERASE command is constructed from the word address supplied by the CPU. The 16-bit value to be written is placed in the variable "nvword". As in the READ-NVR command above, the "nvrs" variable is initialized to select the first state of an EEPROM write operation, and Timer T5 is used to provide the interrupts

that schedule the steps. There are 13 states involved in writing a word to the EEPROM, at the following labels:

t5wr0 activates the chip select signal to the EEPROM, and sends the first byte of an EWEN command to enable ERASE and WRITE commands. Timer T5 is started to time out the MICROWIRE transfer.

t5wr1 sends the second byte of the EWEN command.

Timer T5 is started to time out the MICROWIRE transfer.

t5wr2 removes the chip select signal briefly (to signal the beginning of a new command), then sends the first byte of an ERASE command. Timer T5 is started to time out the MICROWIRE transfer.

t5wr3 sends the second byte of the ERASE command, from the variable "nvrcmd". Timer T5 is started to time out the MICROWIRE transfer.

t5wr4 removes the chip select signal, then sets up the Timer T5 interval to 20 milliseconds, to time the duration of the EEPROM's internal Erase pulse.

t5wr5 (entered 20 milliseconds after "t5wr4") re-asserts the chip select signal to the EEPROM, and transfers the first byte of a WRITE command. Timer T5 is started to time out the MICROWIRE transfer.

t5wr6 alters the command in "nvrcmd" to a WRITE command, then transfers it as the second command byte to the EEPROM. Timer T5 is started to time out the MICROWIRE transfer.

t5wr7 transfers the first byte of data to be written. Timer

T5 is started to time out the MICROWIRE transfer.

t5wr8 transfers the second byte of data to be written.

Timer T5 is started to time out the MICROWIRE transfer.

t5wr9 removes the chip select signal, then sets up the Timer T5 interval to 20 milliseconds, to time the duration of the EEPROM's internal Write pulse.

t5wr10 (entered 20 milliseconds after "t5wr9") re-asserts the chip select signal to the EEPROM, and transfers the first byte of an EWDS command (Erase/Write Disable). Timer T5 is started to time out the MICROWIRE transfer.

t5wr11 transfers the second byte of the EWDS command.

Timer T5 is started to time out the MICROWIRE transfer.

t5wr12 removes the chip select signal to the EEPROM, keeps Timer T5 stopped, disables its interrupt, and returns. This would also be the proper place to set a semaphore flag to acknowledge to the main program that the writing is complete. (Code for this is not included here; it would vary from system to system.)

```

3.4 Source Listing

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

EEPROM

03-May-88 10:53

PAGE

.title EEPROM, 'HPC-Based Driver for NMC9306/9345'

23456789

; This code is written to drive either the 256-bit NMC9306 (COP494); or the 1024-bit NMC9345 (COP495) MICROWIRE(tm) EEPROM.

; NOTE: Timing values assume that the HPC is running at 16MHz crystal frequency. For correct programming pulse widths, one should not deviate far from this without adjusting the timing constant below.

9

10

11 4E1F

12

13

14

19999 ; 20000 counts at 1 usec = 20 msec.

; Timing constant for ERASE and WRITE

; pulse widths.

TIMCON =

TL/DD/9978-3

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Declarations: Register Addresses

FERROM

03-May-88 10:53

PAGE 2

.form 'Declarations: Register Addresses'

; PSW register

; Low byte of Accumulator.

; High byte of Accumulator.

; Low byte of Register B.

; High byte of Register B.

; Low byte of Register X.

; High Byte of Register X.

psw

al

ah

bl

x'C0:w

x'C8:b

x'C9:b

x'CC:b

bh

xl

xh

x'CD:b

x'CE:b

x'CF:b

x'Of:b ; High Byte of Registe

x'D6:b

x'D4:b

x'D6:b

x'D6:b

x'D6:b

x'E1:b ; (Low byte of PORTA.)

x'E1:b ; High byte of PORTB.

x'E2:b ; Low byte of PORTB.

x'E3:b ; High byte of DIRA.)

x'F6:b ; (Low byte of DIRA.)

x'F7:b ; (Low byte of DIRB.

x'F7:b ; Low byte of BFUN.

x'F7:b ; Low byte of BFUN.

x'F9184-b

enir

irpd

ircd

sio

porti

obuf

; (Low byte of PORTA.)

; High byte of PORTA.

portah

portb

portbl

portbh

upic

ibuf

dirah

dirb

dirbl

dirbh

bfun

bfunl

bfunh

x'9194:b

portd

x'9129:b

x'9122:b

x'9122:b

x'9124:b

x'9126:b

x'9128:b

rbuf

thuf

x'9149:w

x'9142:w

x'9144:w

t4

r4

t5

TL/DD/9978-4

```

```

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Declarations: Register Addresses

EEPROM

Ø3-May-88 10:53

PAGE 3

x'0146:w

x'0148:w

x'0144:w

x'014C:w

x'014C:w

x'0150:b

x'0150:b

x'0152:b

x'0152:b

x'0155:w

r5

t6

r6

t7

r7

pwmode

pwmdl

pwmdh

portp

portpl

portpl

eicon

; Low byte of PWMODE.

; High byte of PWMODE.

; Low byte of PORTP.

; High byte of PORTP.

t1

r1

r2

t2

r3

t3

divby

divbyl

divbyl

divbyl

x'9182:w

x'9184:w

x'9186:w

x'9188:w

x'018A:w

x'018C:w

x'018E:w

x'918E:w

x'918E:b

x'918F:b

x'9199:w

x'9199:b

x'9192:b

; Low byte of DIVBY.

; High byte of DIVBY.

tmmdl

tmmdh

tøcon

; Low byte of TMMODE.

; High byte of TMMODE.

TL/DD/9978-5

NSC ASMHPC, Version E2 (Nov Ø2 15:51 1987)

HPC-Based Driver for NMC93Ø6/9345

Declarations: Bit Positions

FEPROM

03-May-88 10:53

PAGE 4

83

84

85

86

87

88 9899

99 9892

91 9893

92 9894

93 9895

96 97 9891

97 9891

98 9899

191 9891

102 9894

103 9895

104 9892

105 9893

111 9893

112 9897

113 9893

114 9893

115 9891

116 9892

117 9893

118 9894

119 9891

110 9892

111 9893

112 9891

119 9891

119 9891

110 9892

111 9893

112 9891

112 9891

119 9894

119 9894

119 9894

119 9894

119 9894

119 9894

119 9894

119 9894

119 9894

119 9894

119 9894

119 9894

129 9898

129 9898

129 9898

129 9898

129 9898

129 9898

129 9898

129 9898

129 9898

129 9898

129 9898

129 9898

129 9898

.form 'Declarations: Bit Positions'

; Name

Position

Register(s)

gie

iØ

i2

i3

enir

enir

porti only

enir, irpd,

enir, irpd,

enir, irpd,

enir, irpd

enir, irpd

enir, irpd

ircd

ircd

ircd

tmrs

uart

ei

uwmode

uwdone

; ired

; irpd

tbmt

9145236791237

enu

enu

enu

rbfl

b8or9

xbit9

enu

enur

enur

wakeup

rbit9

frmerr

enur

enur

enui

enui

doeerr

eti

eri

xtclk

xrclk

b2stp

enui

enui

enui

upic

upic

upic

upic

upic

wrrdy

rdrdy

ła@

Ø

1

2

3

4

unien

b8or16

tØtie

tmmdl

tmmdl

tmmdl

tøpnd

tøack

TL/DD/9978-6

```

```

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Declarations: Bit Positions

EEPROM

03-May-88 10:53

PAGE 5

123 9894

124 9895

125 9896

126 9897

127 9899

128 9891

129 9892

133 9895

133 9895

133 9895

134 9897

137 9891

138 9894

141 9895

142 9895

144 9895

144 9895

155 9896

155 9896

155 9896

155 9896

155 9896

155 9896

155 9896

156 9897

157 9898

t1tie

t1pnd

t1stp

t1ack

t2tie

t2pnd

t2stp

t2ack

t3tie

t3pnd

t3stp

t3ack

tmmdl

tmmdl

456791234567

. . . . . . . . . . . .

tmmdl

tmmdl

tmmdh

tmmdh

tmmdh

tmmdh

tmmdh

tmmdh

tmmdh

tmmdh

t4tie

t4pnd

t4stp

t4ack

t5tie

t5pnd

t5stp

t5ack

t6tie

t6pnd

t6stp

t6ack

t7tie

t7pnd

t7stp

t7ack

9123456791234567

pumdl

pumdl

pumdl

pumdl

pumdl

pumdl

pumdh

pumdh

pumdh

pumdh

pumdh

pumdh

pumdh

pumdh

. . . . . . . . . . . . . .

t4out

t4tfn

t5out

t5tfn

t6out

t6tfn

t7out

t7tfn

; portpl

; portpl

; portpl

; portpl

; portph

; portph

; portph

; portph

93479347

eipol

; eicon

TL/DD/9978-7

NSC ASMHPC, Version E2 (Nov Ø2 15:51 1987)

HPC-Based Driver for NMC93Ø6/9345

Declarations: Bit Positions

EEPROM

03-May-88 10:53

PAGE 6

163 9991

164 9992

165

166 9999

167 9993

168 9995

169 9996

179

171

eimode =

1

; eicon

; eicon

; portbl, dirbl, bfunl

; portbl, dirbl

; portbl, dirbl, bfunl

; portbl, dirbl, bfunl

txd

t2in

Ø

3

5

6

TL/DD/9978-8

```

```

NSC ASMHPC, Version E2 (Nov Ø2 15:51 1987)

HPC-Based Driver for NMC93Ø6/9345

EFPROM

93-May-88 19:53

Space Declarations

172

173 9999

174

.form 'Space Declarations'

.sect DSECT,BASE,REL

175

176

177 0000

; WORD-ALIGNED VARIABLES

stackb: .dsw 16 ; Space for 16 words.

nvrbuf: .dsw 4 ; EEPROM String Buffer.

nvrptr: .dsw 1 ; Pointer into EEPROM Data buffer.

nvword: .dsw 1 ; Scratch location for gathering EEPROM data as words.

178 0020

179 0028

180 002A

181

182

183

;BYTE-ALIGNED VARIABLES

nvrcmd: .dsb 1 ; Current EEPROM command.

nvrnum: .dsb 1 ; Byte count for current EEPROM Read command.

nvrs: .dsb 1 ; EEPROM status byte: phase number for sequencing MICROWIRE ; transfers.

184 ØØ2C

185 ØØ2D

186 ØØ2E

187

187

188

189

190

191

192

193

194 0007

195 0006

196

;BIT DEFINITIONS

; NVRS byte: Status of EEPROM MICROWIRE transfers.

Contains phase (step number) of current EEPROM command in low-order 4 bits. Top two bits are as follows:

; When set, indicates that no EEPROM command is in progress.

6 ; Ø means an EEPROM Read is in progress; 1 means EEPROM Write.

nvravl= 7

TL/DD/9978-9

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

EEPROM

03-May-88 10:53

PAGE 8

Code Section

198

199 0000

'Code Section'

CSECT,ROM16,REL ; Code space.

.form

.sect

; Set one WAIT state.

; Disable interrupts

; individually.

ld

ld

enir,#x'00

; Clear all RAM locations.

sram:

; Basepage bank:

BK,#x'9000,#x'00BE ; Establish loop base and limit.

ld

sraml1: clr

A,[B+].w

sraml1

; Non-basepage bank:

BK,#x'01C0,#x'01FE ; Establish loop base and limit.

sraml2: clr

A

A,[B+].w

sraml2

jp

; MICROWIRE setup.

; (EEPROM is automatically

; deselected on reset, since

; Port P is cleared.)

suwire:

sbit

so.bfunl

: Enable SO output.

sbit

rbit

sbit

so,dirbl

sk,portbl

sk,dirbl

; Set up SK output.

sk,bfunl

uwmode,ircd

divby,#x'2225

sbit

sbit

ld

; Set Master Mode.

; Set MICROWIRE frequency.

uwdone,irpd

snvr1

; Wait until MICROWIRE

; interface ready (uWDONE

; bit set).

suwlp: ifbit

jp

jp

suwlp

; Cancel any EEPROM Write in progress:

; Set EEPROM Chip Select active.

; Send a byte of zeroes.

snvr1:

sbit

ld

t5out,portpl

sio,#9

TL/DD/9978-10

```

```

Ø3-May-88 10:53

PAGE 9

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Code Section

EEPROM

238 9939 960219

239 993C 41

249 993D 64

241 993E B691521C

242 9942 839891928B

; Wait until MICROWIRE

; interface ready (uWDONE

; bit set).

; Remove EEPROM Chip Select.

uwdone,irpd

snvr2

suwlp1

t5out,portpl

suwlp1: ifbit

jp

snvr2: rbit

t0con,#x'08

tmmode,#x'4440

divby,#x'0055

tminit: ld

243 9942 8398891928B

244 9947 8744499199AB

245 9940 8355918EAB

247 9952 87CCC89199AB

248

249

259 9958 8744449159AB

251 995E 49

252 995F 49

253 9969 87CCCC9159AB

254

; Stop timers T1, T2, T3.

; MICROWIRE frequency set

; to CKI/128.

; Clear and disable timer

; T0-T3 interrupts.

ld

tmmode, #x¹CCC8

ld

; Stop timers T4-T7.

; Wait for Pending bits to

; trickle through before clearing them.

; Clear and disable

; interrupts from all

; PWM timers.

pwmode, #x 14444

ld

nop

nop

ld

pwmode, #x¹CCCC

254

255

256

257 9966 87FFFF9146AB

258

r5,#x'FFFF

; No modulus for EEPROM timer.

ld

TL/DD/9978-11

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Main Program Initialization

EEPROM

Ø3-May-88 10:53

PAGE 10

.form

'Main Program Initialization'

259

269

261 996C

262 996C 97892E

263 996F B7992928

minit:

Ιđ

nvrs,#x'80 ; Set EEPROM available.

nvrptr,#nvrbuf ; Set EEPROM pointer to start of buffer.

ίď

263 996F B799292

264

265 9973

266

267 9973 96D99D

268

runsys:

; Enable timer interrupts, and go to main.

; Enable timer interrupts. (Done here

; to allow engine commands without an

; INITIALIZE command first.)

; Enable interrupt system.

sbit

tmrs,enir

269

270 0076 960008

271

272

sbit

gie,enir

TL/DD/9978-12

```

```

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Main Program Fragments

EEPROM

03-May-88 10:53

PAGE 11

273 | 274 | 275 | 276 | 275 | 276 | 277 | 278 | 279 | 280 | 281 | 280 | 282 | 283 | 284 | 285 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 | 287 |

.form 'Main Program Fragments'

These values are declared as constants; more typically they would be contained within variables. Note that the pound-sign character must then be deleted in the instructions referencing them.

8 ; EEPROM address: change to suit your application.

x'ABCD ; Written data: change to suit.

4 ; Number of bytes to read (1-8): change to suit.

nvradr =

nvrbvt

; Read Fragment: reads up to 4 words (8 bytes) from EEPROM.

; Get NVR starting address.

; Truncate to legal limit.

; Create NVR READ command.

; Place it in memory.

; Get number of bytes requested.

; Save byte count in memory.

; Set up NVR access status flags:

; Read transfer in progress, first phase.

; Reset buffer pointer to beginning.

; Go start up transfer.

A,#nvradr

rnvr:

A,#x'3F

R

st

ld

st

ld

A.nvrcmd

A,#nvrbyt

A,nvrnum

nvrs,#Ø

R

ld

nvrptr,#nvrbuf

jmpl

; Write Fragment: writes one word to EEPROM.

nvword, #nvrdta ; Get data word.

wnvr:

ld

; Get data word.

; Get EFROM address.

; Mask it for proper range.

; Store it in Command byte in memory.

; (Opcode = ββ at this point.)

; Set up NVR access status flags:

; Write transfer in progress, first phase.

; Go start up transfer.

id

and

A.nvrcmd

st

ld

nvrs,#x'4Ø

jmpl

nvrx

; Common routine, performed by both READ and WRITE.

; Start interrupts from Timer T5 to schedule ; accesses to EEPROM.

TL/DD/9978-13

NSC ASMHPC, Version E2 (Nov Ø2 15:51 1987)

HPC-Based Driver for NMC93Ø6/9345

Main Program Fragments

93-May-88 19:53

PAGE 12

EEPROM

; Interrupts are not repetitive; give R5 a; high value.

; Set Timer T5 to interrupt (almost); immediately when started.

; Enable interrupt from Timer T5.

; Start Timer T5.

313 009A 87FFFF0146AB

314

r5,#x'FFFF

315 00A0 83000144AB

ld

t5,#@

316

317 99A5 B691599C

318 99A9 B691591E

t5tie,pwmdl

t5stp,pwmdl

sbit

319

320

321

*** One could replace the following instruction with one that

*** looks for an appropriate semaphore bit to be set, indicating

*** that the requested operation has been completed. See other

comments beginning with "***".

322

324

325 00AD 60

; Stops HPC, except for interrupt service.

iр

END OF MAIN PROGRAM FRAGMENTS.

TL/DD/9978-14

```

```

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Timer Interrupt Handler

EEPROM

Ø3-May-88 10:53

PAGE

329

33ø

331

.form 'Timer Interrupt Handler'

The Timer T5 interrupt service routine does all the work. Each interrupt sequences the next step of the READ or WRITE operation in progress.

332

333

334

335 FFF4 AE00

.ipt

5, tmrint

; Declare entry point for Timer Interrupt.

336

337 00AE AFC8

338 00B0 AFC0

tmrint: push

; Save context.

DSW.W

330

340 0082 B6015015

341 0086 41

t5pnd,pwmdl

t5int

; Poll for Timer T5 interrupt (EEPROM Timing

t5poll: ifbit

impl

; Interrupt).

343 90B7 60

344

345 90B8 B601500E

; Otherwise, error. Stop HPC.

jр

t5int:

sbit

t5stp,pwmdl

t5ack,pwmdl

Stop Timer T5.

Clear interrupt request. (Doing this immediately is acceptable here.)

Check whether Read or Write operation is

346 00BC B601500F

sbit

347

348 ØØCØ 962E16

ifbit

NYTWI. NYTS

is in progress.

If Write, go perform

Enable/Erase/Write/Disable operation.

350 00C3 9483

jmpl

t5wr

35

Else, program is reading from EEPROM.

Get phase info.

Increment memory value for next T5 interrupt.

Extract phase number.

352 00C5

t5rd:

353 00C5 882E

354 00C7 892E

355 00C9 990F

A,nvrs

nvrs

14

inc

and

shl

A,#x'ØF

356 00CB E7

00CC 40

357 00CD

Jump based on this number.

.odd

357 MUCD

358 MUCD EC

359 MUCE MAMM

MUCD 1800

MUCD 2800

jidw

t5rd0,t5rd1,t5rd2,t5rd3,t5rd4

.ptw

00D4 3500

9906 4599

360

361 00D8 B601520C

; Set chip select signal to EEPROM.

; Send first part of NVR Read command.

; Format is: 1/10/A5-A0/0 ,

t5rdØ: sbit

ld

t5out,portpl

sio,#x'03

99DC 9793D6

TL/DD/9978-15

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Timer Interrupt Handler

Ø3-May-88 10:53

EEPROM

PAGE

364

365

366

367

368

369 000F 835A0144AB

370 00E4 8601501E

where first bit is start bit (always '1'),

next two bits are operation (10=read),

next 6 bits are EEPROM address,

last bit is "padding" for access time.

This phase sends top two bits of command.

Set up for interrupt after MICROWIRE transfer.

Start Timer I5.

t5,#9Ø

١d

37Ø

371

t5stp,pwmdl

tmrret

rbit

00E8 B40151

jmpl

Return from interrupt.

Send second part of NVR Read command (bottom

R t5rd1: ld

373 00FB 8020D6

sio, nvrcmd

eight bits).

Set up for interrupt after MICROWIRE transfer.

Start Timer 15.

375 PPEE 835A0144AB

376 PPF3 B601501E

377 PPF7 B40142

t5,#90

t5stp,pwmdl

tmrret

rbit

jmpl

Return from interrupt.

378

379 00FA 9700D6

380 00FD 835A0144AB

381 0102 B601501E

382 0106 B40133

Start reading MSB of EEPROM data.

Set up for interrupt after MICROWIRE transfer.

Start Timer T5.

t5rd2:

ld

sio,#Ø

t5,#90

t5stp,pwmdl

tmrret

ld

rbit

jmpl

382

383

384 0109 8CD62B

385 010C 9700D6

386 010F 835A0144AB

387 0114 B601501E

Accept MSB of EEPROM data to word buffer.

Start reading LSB of EEPROM data.

Set up for interrupt after MICROWIRE transfer.

Start Timer T5.

R t5rd3:

ld

nvword+1.b.sio

nvword+1.b,

sio,#0

t5,#90

t5stp,pwmdl

tmrret

ίd

rbit

388 Ø118 B4Ø121

Return from interrupt.

; Accept LSB of EEPROM data to word buffer.

Remove EEPROM chip select signal.

; Get EEPROM data word.

; Store in EEPROM buffer for CPU.

390 011B 8CD6ZA

R t5rd4:

ld

nvword.b,sio

391 0118 6C052A

391 011E 8601521C

392 0122 A82A

393 0124 AD28AB

394 0127 A928

395 0129 8A2D

rbit

t5out,portpl

A,nvword

ld

A, [nvrptr].w

nvrptr

nvrnum

Increment EEPROM buffer pointer once.

Check whether both bytes of the word were

inc

requested.

Yes: continue.

396

397 Ø12B 41

jp

jp

inc

t5rdh

No: done with reading.

Increment EEPROM buffer pointer a second time (to signal that a whole word was input to buffer).

398 Ø12C 45

399 Ø12D A928

t5rddn

nvrptr

t5rdh:

400

401

402 012F 8A2D

403 0131 4A

decsz

Check whether done.

No: Initiate another Read command.

iρ

t5rnxt

TI /DD/9978-16

```

```

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Timer Interrupt Handler

EEPROM

Ø3-May-88 10:53

PAGE 15

t5rddn: rbit t5tie,pwmdl ; Yes: Terminate and pass data to CPU. ; Disable fimer 15 interrupts. ; Set NVR available for more commands. ;*** Here you'll want to set a semaphore bit saying that the READ ;*** transfer is done. jmpl tmrret ; Return from interrupt.

494

495 9132 8691591C

496 9136 962E9F

498

499 9139 849199

411 913C

413 913C 97992E

414 913F 892C

415 9141 892C

415 9141 892C

416 417 9143 962C1F

418

419 9146 9581

422 9148 882E

424 9148 882E

424 9148 892E

426 914C 999F

427 914E 429

428 914F

429 9146 EC

439 9159 1A99

9156 48899

431 9158 58899

9156 48899

431 9158 58999

9156 4899

9156 4899

9156 7999

9156 7999

9156 7999

9156 7999

9156 7999

9156 7999

9156 7999

9156 7999

9164 AE99

Here, more data needs to be read from the EEPROM. Initiate another read cycle.

Set up new transfer phase = 0.

Increment address field of NVR command.

(Two increments are needed: field starts in Bit 1.)

Prevent increments from altering operation field. This allows addresses to roll over. Rather than triggering a Timer T5 interrupt, just jump to T5 Read interrupt service again.

t5rnxt:

ld

nvrs,#x'99

inc

nvrcmd

nvrcmd

rbit

7,nvrcmd

jmpl

t5rd

; EEPROM Write sequence starts here.

; Get phase info.

; Increment memory value for next T5 interrupt.

; Extract phase number.

; Jump based on this number.

t5wr:

A, nvrs

nvrs

A, #x'ØF

A

ld

inc

and

shl

.odd

jidw

R

R

t5wr0,t5wr1,t5wr2,t5wr3

.ptw

t5wr4,t5wr5,t5wr6,t5wr7

t5wr8,t5wr9,t5wr10,t5wr11

.ptw

.ptw

t5wr12

```

TL/DD/9978-17

| C ASMHPC, Version E2 (Nov 02 15:51 1987)<br>C-Based Driver for NMC9306/9345<br>mer Interrupt Handler |               |                     | EEPROM                               | 03-May-88 10:53<br>PAGE 16                                                                                                    |

|------------------------------------------------------------------------------------------------------|---------------|---------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 435 Ø16A B6Ø152ØC<br>436 Ø16E 97Ø1D6<br>437 Ø171 835AØ144AB                                          | t5wrØ:        | sbit<br>ld<br>ld    | t5out,portpl<br>sio,#x'01<br>t5,#90  | ; Set chip select signal to EEPROM.<br>; Send start bit of EWEN command.<br>; Set up for interrupt at end of MICROWIRE        |

| 438<br>439 Ø176 B6Ø15Ø1E<br>440 Ø17A 94CØ<br>441                                                     |               | rbit<br>jmpl        | t5stp,pwmdl<br>tmrret                | ; transfer.<br>; Start timer T5.<br>; Return from interrupt.                                                                  |

| 42 017C 9730D6<br>43 017F 835A0144AB                                                                 | t5wr1:        | ld<br>ld            | sio,#x'30<br>t5,#90                  | ; Send body of EWEN command.<br>; Set up for interrupt at end of MICROWIRE<br>; transfer.                                     |

| 45 Ø184 B6Ø15Ø1E<br>46 Ø188 94B2<br>47                                                               |               | rbit<br>jmpl        | t5stp,pwmdl<br>tmrret                | ; Start timer T5.<br>; Return from interrupt.                                                                                 |

| 48 018A B601521C<br>49 018E 40<br>50 018F B601520C                                                   | t5wr2:        | rbit<br>nop<br>sbit | t5out,portpl<br>t5out,portpl         | ; Remove EEPROM select momentarily to signal<br>; end of EWEN command, then:                                                  |

| 51 0193 9701D6<br>52 0196 835A0144AB<br>53                                                           |               | ld<br>ld            | sio,#x'01<br>t5,#90                  | ; Send Start Bit for ERASE command.<br>; Set up for interrupt at end of MICROWIRE<br>; transfer.                              |

| 54 0198 B601501E<br>55 019F 949B<br>56                                                               |               | rbit<br>jmpl        | t5stp,pwmdl<br>tmrret                | ; Start timer T5.<br>; Return from interrupt.                                                                                 |

| 57 Ø1A1 82CØ2CDA<br>58 Ø1A5 8C2CD6<br>59 Ø1A8 835AØ144AB<br>60                                       | R t5wr3:<br>R | or<br>ld<br>ld      | nvrcmd,#x1CØ<br>sio,nvrcmd<br>t5,#9Ø | ; Change NVR Command byte to ERASE command.<br>; Send to EEPROM.<br>; Set up for interrupt at end of MICROWIRE<br>; transfer. |

| 61 01AD B601501E<br>62 01B1 9489<br>63                                                               |               | rbit<br>jmpl        | t5stp,pwmdl<br>tmrret                | ; Start timer T5.<br>; Return from interrupt.                                                                                 |

| .64 Ø1B3 B6Ø1521C<br>.65                                                                             | t5wr4:        |                     | t5out,portpl                         | ; Remove EEPROM chip select signal, starting<br>; ERASE pulse inside EEPROM.                                                  |

| 66 Ø1B7 874E1FØ144AB                                                                                 |               | ld                  | t5,#TIMCON                           | ; Set up for delay of 20; milliseconds (erase pulse width).                                                                   |

| .68                                                                                                  |               | rbit<br>jmpl        | t5stp,pwmdl<br>tmrret                | ; Start timer T5.<br>; Return from interrupt.                                                                                 |

| 71 01C3 B601520C<br>72                                                                               | t5wr5:        |                     | t5out,portpl                         | ; Set EEPROM chip select signal again, ending<br>; the ERASE pulse inside EEPROM.                                             |

| 473 Ø1C7 97Ø1D6<br>474 Ø1CA 835AØ144AB                                                               |               | ld<br>ld            | sio,#x'Ø1<br>t5,#9Ø                  | ; Send Start bit for Write command.<br>; Set up for interrupt at end of MICROWIRE                                             |

TL/DD/9978-18

```

03-May-88 10:53

PAGE 17

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Timer Interrupt Handler

EEPROM

transfer.

475 01CF 8601501E

477 01D3 9467

478 01D3 9467

479 01D5 962C1F

480 01D8 8C2CD6

481 01DB 835A0144AB

rbit

jmpl

t5stp,pwmdl

tmrret

Start timer T5.

Return from interrupt.

rbit

ld

ld

Create WRITE command in NVR Command byte.

Send to EEPROM.

Set up for interrupt at end of MICROWIRE

transfer.

t5wr6:

7.nvrcmd

sio,nvrcmd

t5,#90

482

483 Ø1EØ B6Ø15Ø1E

484 Ø1E4 9456

485

rbit

t5stp,pwmdl

Start timer T5.

Return from interrupt.

jmpl

tmrret

485

486 p1E6 8C2BD6

487 p1E9 835Ap144AB

488

489 p1EE B6p15p1E

490 p1F2 9448

491

492 p1F4 8C2AD6

493 p1F7 835Ap144AB

494

495 p1FC B6p15p1E

496 p2pp 943A

497

498 p2p2 B6p1521C

499

50p p2p6 874E1Fp144A

Send MSB of data to EEPROM.

Set up for interrupt at end of MICROWIRE transfer.

ld

sio,nvword+1.b

t5,#90

R t5wr7:

t5stp,pwmdl

tmrret

rbit

jmpl

Send LSB of data to EEPROM.

Set up for interrupt at end of MICROWIRE transfer.

Start timer T5.

Return from interrupt.

R t5wr8:

ld

sio,nvword.b

t5stp,pwmdl

tmrret

rbit

jmpl

Remove EEPROM chip select, starting Write pulse within EEPROM.

Set up for delay of 20 milliseconds (write pulse width).

Start timer 15.

Return from interrupt.

t5wr9: rbit

t5out,portpl

499

598 9296 874E1FØ144AB

591 929C B6Ø1591E

593 9219 942A

594

595 9212 B6Ø152ØC

596 9212 B6Ø152ØC

596 9219 942A

598

599 9219 835AØ144AB

518

ld

t5,#TIMCON

rbit

t5stp,pwmdl

jmpl

Set EEPROM chip select signal, ending Write pulse within EEPROM.

Send Start bit for EWDS command (Disable Write/Erase).

t5wr10: sbit

t5out.portpl

ld

sio,#x'91

, miles/crase),

Set up for interrupt at end of MICROWIRE

; transfer.

; Start timer 15.

; Return from interrupt.

ld

t5.#90

510

511 021E B601501E

512 0222 59

rbit

t5stp,pwmdl

jmpl

514 0223 9700D6

t5wr11: ld

sio,#x'99

; Send body of EWDS command.

TL/DD/9978-19

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Timer Interrupt Handler

EEPROM

Ø3-May-88 10:53

PAGE

515 9226 835A9144AB

516

517 9228 8691591E

518 922F 4C

519

529 9239 8691521C

521 9234 8691591C

522 9238 962E9F

524

525 9238 49

526

527 923C 3FC9

528 923E 3FC8

529 9249 3E

539

531 9241

; Set up for interrupt at end of MICROWIRE

; transfer.

; Start timer T5.

; Return from interrupt.

ld

t5,#90

rbit

t5stp,pwmdl

impl

; Remove EEPROM chip select signal.

; Disable Timer T5 interrupts.

; Set EEPROM Available.

semaphore bit saying that the WRITE

t5wr12: rbit

t5out,portpl

rbit t5tie,pwmdl

sbit nvravl,nvrs

Here you'll want to set

transfer is done.

jmpl

tmrret

psw.w

A

; Restore context.

tmrret: pop

pop

reti

.end

start

TL/DD/9978-20

```

```

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Timer Interrupt Handler

EEPROM

Ø3-May-88 10:53

PAGE 19

ah

al

b2stp

b8or16

b8or9

bfun

bfunh

bfunl

bh

bl

dirah

dirbh

dirbh

dirbly

divbyh

divbyl

bfunh

doeerr

ei

eiack

eicon

eimode

eipol

enir

enu

enui

enur

eri

eti

frmerr

gie

iØ

i2

i3

i4

ibuf

ircd

irpd

laØ

TL/DD/9978-21

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Timer Interrupt Handler

Ø3-May-88 10:53

PAGE 20

EEPROM

HPC-Based Driver for NMC9306/

Timer Interrupt Handler

nvradr 9999 Abs Null

nvrbut 9997 Abs Null

nvrbut 9998 Abs Null

nvrcmd 9922 Rel Word BASE

nvrdta ABCD Abs Null

nvrnum 9922 Rel Byte BASE

nvrmr 9928 Rel Word BASE

nvrmr 9928 Abs Null

9928 Abs Null

9929 Abs Byte

9919 Abs Word

9151 Abs Byte

9919 Abs Word

9151 Abs Byte

9159 Abs Word

9151 Abs Word

12 9184 Abs Word

12 9185 Abs Word

13 9184 Abs Word

14 9142 Abs Word

15 9184 Abs Word

16 9146 Abs Word

17 9146 Abs Word

17 9146 Abs Word

17 9146 Abs Word

18 9911 Abs Null

18 9911 Abs Null

18 9911 Abs Null

18 9911 Abs Null

18 9913 Abs Null

18 9913 Abs Null

18 9914 Abs Byte

18 9918 Abs Null

18 9918 Abs Null

18 9919 Abs Byte

nvword obuf portab portab portbl portbl portbl portpl portpl psw pwmdh pwmdl pwmode r1 r2 r3 r4 r5 r6 r7 rbfl rbit9

0006 Abs Byte

TL/DD/9978-22

```

```

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Timer Interrupt Handler

EEPROM

Ø3-May-88 10:53

PAGE

TL/DD/9978-23

NSC ASMHPC, Version E2 (Nov 02 15:51 1987)

HPC-Based Driver for NMC9306/9345

Timer Interrupt Handler

FEPROM

Ø3-May-88 10:53

PAGE 22

9144 Abs Word

9007 Abs Nutl

9088 Rel Nutl ROM16

9094 Abs Nutl

9085 Abs Nutl

9085 Abs Nutl

9085 Abs Nutl

9086 Rel Nutl ROM16

9008 Rel Nutl ROM16

9008 Rel Nutl ROM16

9199 Rel Nutl ROM16

9199 Rel Nutl ROM16

9132 Rel Nutl ROM16

9134 Rel Nutl ROM16

9164 Rel Nutl ROM16

9176 Rel Nutl ROM16

9176 Rel Nutl ROM16

9176 Rel Nutl ROM16

9177 Rel Nutl ROM16

9178 Rel Nutl ROM16

9179 Rel Nutl ROM16

91

tSack

t5int

t5out

t5pnd

t5pnd

t5rdd

t5rdd

t5rdd

t5rdd

t5rdd

t5rdd

t5rdd

t5rdh

t5rdh

t5tfn

t5tfr

t5wr1

t5wr3

t5wr3

t5wr5

t5wr5

t5wr5

t5wr5

t5wr5

t5wr8

t5wr9

t6

t6ack

t6out

t6pnd

t6stp

t6tfn

t6tie

t7

TL/DD/9978-24

```

```

NSC ASMHPC, Version E2 (Nov Ø2 15:51 1987)

HPC-Based Driver for NMC93Ø6/9345

Timer Interrupt Handler

93-May-88 19:53

PAGE 23

EEPROM

Track 9997 Abs Null

t7pot 9996 Abs Null

t7pot 9996 Abs Null

t7tfn 9996 Abs Null

t7tfn 9996 Abs Null

t7tfn 9997 Abs Null

t7tfn 9997 Abs Null

t7tfn 9997 Abs Null

ttrtf 9126 Abs Byte

tminit 9942 Rel Null ROM16

tmmdh 9197 Abs Byte

tmmdd 9199 Abs Byte

tmmdd 9199 Abs Byte

tmmdd 9199 Abs Null

ROM16

tmret 923C Rel Null ROM16

tmret 923C Rel Null ROM16

tmret 923C Rel Null ROM16

tmret 9296 Abs Null

uart 9996 Abs Null

uart 9998 Abs Null

wmode 9991 Abs Null

wmode 9991 Abs Null

wmode 9991 Abs Null

xbit 9992 Abs Null

xbit 9996 Abs Null

xbit 9998 Abs Null

xbit 9988 Abs Null

xtclk 9998 Abs Null

**** Errors: Ø, Warnings:

ø

TL/DD/9978-25

```

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**AN-552**

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) 0-180-530 85 86 Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 78 38 Italiano Tel: (+49) 0-180-534 16 80

**National Semiconductor** National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 **National Semiconductor** Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408