# **Reducing Noise on** Microcomputer Buses

Abstract: This paper focuses on the noise components that have a significant impact on the performance of a high speed microcomputer bus. An overview of their nature is followed by ways to minimize their contribution by suitable design of the PC board backplane, the termination network and the bus transceiver. The DS3662 trapezoidal bus transceiver, which is specifically designed to minimize such noise on high speed buses, is presented along with its performance data.

And to conclude, some possible new transceiver designs for

further improvement of the bus performance are explored.

#### INTRODUCTION

As the microcomputer bus bandwidth is extended to handle ever increasing clock rates, the noise susceptibility of a single-ended bus poses a serious threat to the overall system integrity. Thus, it is mandatory that the various noise contributions be taken into account in the design of the bus transceiver, the PC board backplane and the bus terminations to avoid intermittent or total failure of the system.

Although noise such as crosstalk and reflections are inevitable in any practical bus configuration, their impact on the system can be determined and minimized by careful design of all three components mentioned above. The combined contribution of the noise under worst-case conditions should be within the noise margin for reliable bus operation

The design of the transceiver plays a significant role in minimizing crosstalk and reflection. The bus can be optimized for minimum noise at a given bandwidth by using a trapezoidal driver having suitable rise and fall times along with a matched low pass filtered receiver which provides a symmetrical noise margin. The DS3662 is one such transceiver, the first member in the family of trapezoidal bus transceviers available from National Semiconductor Corporation. This device represents a significant improvement in high speed bus circuit design and provides a solution to commonly encountered bus noise problems.

# THE MICROCOMPUTER BUS

A typical microcomputer bus usually consists of a printed circuit board backplane with signal and ground traces on one side and a ground plane on the other. The length ranges from a few inches to several feet with as many as 32 closely spaced (0.6" typical) card edge connectors. Each signal line interacts with the ground plane to form a transmission line with characteristic impedance "Z" in the range of  $90\Omega$ – $120\Omega$ typical. It is desirable to have as large a "Z" as possible in order to reduce the drive requirement of the bus driver and to reduce the power dissipated at the terminations. But much larger values of "Z" translate to significantly larger physical dimensions and therefore are not very practical.

The bus appears like a transmission line to any signal having a transition time " $t_r$ " less than the round trip delay " $2T_L$ " of the bus. The bus delay "TL" is given by:

$$T_{L} = L\sqrt{L1 C1} \tag{1}$$

AN005281

National Semiconductor Application Note 337 R. V. Balakrishnan July 1986

where

L = length of the bus

L1 = distributed inductance per unit length

C1 = distributed capacitance per unit length

For a typical unloaded 100 $\Omega$  microstrip line, C1  $\cong$  20 pF/ft and L1  $\cong$  0.2  $\mu$ H/ft. Therefore, T<sub>L</sub> = 2.0 ns/ft. This corresponds to approximately half the speed of light. However, the capacitive loading at each connector on the backplane increases the delay time significantly. The loaded delay time "T., " is given by:

$$T_{LL} = T_L \sqrt{1 + (C_L/C_1)}$$

(2)

where C<sub>1</sub> = distributed load capacitance/unit length

Given a 10 pF loading at each connector (connector + transceiver capacitance) and a 0.6" spacing between connectors,  $C_L = 200 \text{ pF/ft}$  and  $T_{LL} = 6.6 \text{ ns/ft}$ . So even a 6" long bus has a  $2T_{LL}$  = 6.6 ns, which is higher than the transition time (t<sub>r</sub>) of many high speed bus drivers. When in doubt, it is always better to use the transmission line approach than the lumped circuit approach as the latter is an approximation of the former, Also, the transmission line analysis gives more pessimistic (worst-case) values of crosstalk and reflection and is, hence, safer.

#### CROSSTALK REDUCTION

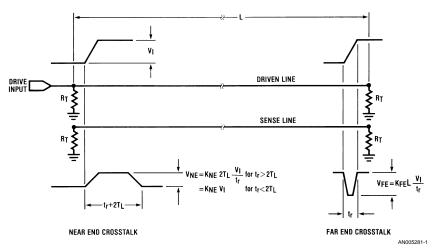

The crosstalk is due to the distributed capacitive coupling C<sub>C</sub> and the distributed inductive coupling L<sub>C</sub> between two lines. When crosstalk is measured on an undriven sense line next to a driven line (both terminated at their characteristic impedances), the near end crosstalk and the far end crosstalk have quite distinct features, as shown in Figure 1 Their respective peak amplitudes are:

$$V_{NE} = K_{NE}(2T_L)(V_I/t_r)$$

for  $t_r > 2 T_L$  (3)

$$V_{NE} = K_{NE}(V_I) \text{ for } t_r < 2 T_L$$

(4)

$$V_{FE} = K_{FE}(L)(V_I/t_r)$$

(5)

where  $V_1$  = signal swing on the drive line.

The coupling constants are given by the expressions:

$$\label{eq:KNE} \mathsf{K}_{NE} = \frac{\mathsf{L}(C_C Z + \mathsf{L}_C / Z)}{4 \mathsf{T}_L} \tag{6}$$

$$K_{FE} = \frac{C_C Z - L_C / Z}{2} \, \text{ns/ft} \tag{7}$$

The near end component reduces to zero at the far end and vice versa. At any point in between, the crosstalk is a fractional sum of near and far end crosstalk waveforms shown. It should be noted from expressions Equations (6), (7) that

the far end crosstalk can have either polarity whereas the near end crosstalk always has the same polarity as the signal causing it. In microstrip backplanes the far end crosstalk pulse is usually the opposite polarity of the original signal.

Although the real world bus is far from the ideal situation depicted in *Figure 1*, several useful observations that apply to a general case can be made:

- 1. The crosstalk always scales with the signal amplitude.

- 2. Absolute crosstalk amplitude is proportional to slew rate  $V_{l} t_{r}, \ \text{not just } 1/t_{r}.$

- 3. Far end crosstalk width is always tr.

- 4. For  $t_r < 2T_L$ , the near end crosstalk amplitude  $V_{NE}$  expressed as a fraction of signal amplitude  $V_I$  is a function of physical layout only.

- 5. The higher the value of " $t_r$ " the lower the percentage of crosstalk (relative to signal amplitude).

The corresponding design implications are:

1. The noise margin expressed as a percentage of the signal swing is what's important, not the absolute noise margin. Therefore, to improve noise immunity, the percentage noise margin has to be maximized. This is achieved by reducing the receiver threshold uncertainty region and by centering the threshold between the high and low levels.

- Smaller signal amplitude with the same transition time reduces bus drive requirements without reducing noise immunity.

- 3. Far end crosstalk is eliminated if the receiver is designed to reject pulses having pulse widths less than or equal to t<sub>r</sub>.

- 4. When  $t_r < 2T_L$ , the near end crosstalk immunity for a given percentage noise margin has to be built into the backplane PC layout. Since  $(V_{NE}/V_I) = K_{NE}$  for this case,  $K_{NE}$  should be kept lower than the available worst-case noise margin.  $K_{NE}$  may be reduced by either increasing the spacing between lines or by introducing a ground line in between. The ground line, in addition to increasing the spacing between the signal lines, forces the electric field lines to converge on it, significantly reducing crosstalk.

- 5. For minimum crosstalk the rise and fall times of the signal waveform should be as large as possible consistent with the minimum pulse width requirements of the bus. A driver that automatically limits the slew rate of the transition can go a long way in reducing crosstalk.

FIGURE 1. Crosstalk under Ideal Conditions

## CROSSTALK MEASUREMENT

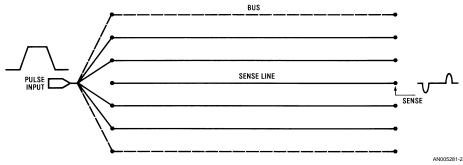

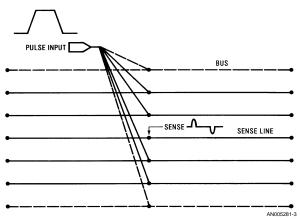

When multiple lines on either side of the sense lines switch simultaneously the crosstalk is considerably larger, typically 3.5 times the single line switching case for microstrip backplanes. Also, the location of the drivers on the driven lines and the receiver on the sense line for worst-case crosstalk differs for the near end and far end cases as shown in Figure 2 and Figure 3 for a uniformly loaded bus. But if the far end crosstalk is not of the opposite polarity, then the combined effect of far end and near end crosstalk could have a larger amplitude and pulse width at a point near the middle of the sense line in Figure 2. So in a general case, or in the case of a non-uniformly loaded bus, it is advisable to check the sense line at several locations along the length of the bus to determine the worst-case crosstalk. The measurement should be made for both the positive and the negative transition of the drive signal.

## THE TERMINATION

A properly terminated transmission line has no reflections. But a practical microcomputer bus is neither a perfect transmission line nor is it properly terminated under all conditions. The capacitive loading at discrete locations, such as a used card slot, act as sources of reflection. However, in the limiting case when the bus is uniformly populated with a large number of modules, the bus behaves like a lower impedance transmission line. The loaded impedance " $\mathbf{Z_L}$ " of the bus is given by the expression:

$$Z_{L} = \frac{Z}{\sqrt{1 + C_{L}/C_{1}}} \tag{8}$$

where Z = unloaded line impedance

Unfortunately, uniform loading of the bus is not guaranteed at all times and even if it were (by dummy loading of the un-

used slots)  $Z_L$  is usually too low for proper termination of the bus. For example, a 10 pF per module loading of the  $100\Omega$  microstrip bus at  $0.6^{\rm m}$  spacing results in a  $Z_L=30\Omega$ . One such termination at each end will require a 200 mA drive capacity on the bus driver for a nominal 3V swing. Such large drive currents and low value terminations increase the power dissipation of the system significantly in addition to causing other problems such as increased ground drop, inductive drops in traces due to large current being switched, etc. As a compromise the bus is usually terminated at an impedance higher than  $Z_L$  but less than or equal to Z. Consequently,

there is always some amount of reflection present. For a perfect transmission line the reflection coefficient "T" is given by the well known expression:

$$\Gamma = \frac{Z - R_t}{Z + R_t} \tag{9}$$

where

Z = impedance of the bus

R<sub>t</sub> = termination resistance

Note: All lines terminated at both ends (not shown)

FIGURE 2. Worst-Case Near End Crosstalk Measurement

Note: All lines terminated at both ends (not shown)

FIGURE 3. Worst-Case Near End Crosstalk Measurement

The net effect, in the general case of a nonuniformly loaded bus, is that it may take several round trip bus delays after a bus driver output transition, before the quiescent voltage level is established. However, this delay is avoided by using a bus driver that has sufficient drive to generate a large enough voltage step during the first transition to cross well beyond the receiver threshold region under the worst-case load conditions.

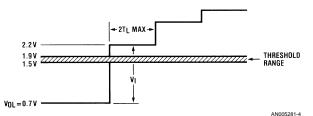

Figure 4 illustrates the driver output waveform under such a condition. Here the fully loaded bus (with  $Z_L=30\Omega$ ), of the previous example, is driven by the DS3662 bus transceiver

at the mid point. The driver is actually driving two transmission lines of Z<sub>L</sub> =  $30\Omega$  in either direction from the middle and hence the initial step is given by:

$$V1 = \left(\frac{Z_L}{2}\right) 2I_S \tag{10}$$

where  $I_S$  = Standing current on the bus due to each termination

For the DS3662, the termination can be designed for  $2l_S = 100$  mA and therefore:

V1 = (30/2)100 = 1.5V

This value of the initial swing is large enough to cross the narrow threshold region of the receiver as shown and therefore no waiting period is required for the reflections to build up the output high level. On the negative transition the problem is less critical due to the much higher sink capability of the DS3662 during pull down.

Reflections can also be caused by resistive loading of the bus by the DC input current of the receiver. The resulting reflectoin coefficient ( $\Gamma$ ) is given by the expression:

$$\Gamma = -\frac{1}{2} \left( \frac{I_{R}}{I_{S}} \right) \tag{11}$$

where  $I_R$  = receiver input current

Having a receiver with a high input impedance not only makes this component of reflection insignificant but also reduces the DC load on the driver, allowing the use of lower value termination resistors. This is particularly true when a large number of modules are connected to the bus.

The design implications of the above discussion may be summarized as follows:

- 1. If the driver has adequate drive to produce the necessary voltage swing under the worst-case loading ( $Z_L/2$ ), reflections do not restrict the bus performance. This translates to a 100 mA minimum drive requirement for a typical microstrip bus.

- 2. If the drive is insufficient, time should be allowed for the reflections to build up the voltage level before the data is sampled.

- 3. For signals such as clock, strobe, etc., wherein the edge is used for triggering events, it is mandatory that the driver meet the above drive requirements if delayed or multiple triggering is to be avoided.

- 4. An ideal TTL bus transceiver should have at least a 100 mA drive, a high input impedance receiver with a narrow threshold uncertainty region.

FIGURE 4. Worst-Case DS3662 Output Transition for Z<sub>L</sub> = 15 $\Omega$  and R<sub>T</sub> = 50 $\Omega$

# THE DS3662 TRANSCEIVER

The DS3662 quad trapezoidal bus transceiver has been designed specifically to minimize the noise problems discussed previously. The driver generates precise trapezoidal waveforms that reduce crosstalk and the receiver uses a low pass filter to reject noise pulses having pulse widths up to the maximum driver output transition times. Precision output circuitry optimizes noise immunity without sacrificing the high data rate capability of Schottky transceivers.

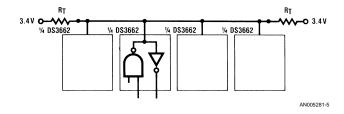

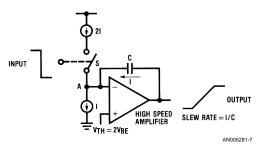

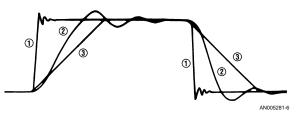

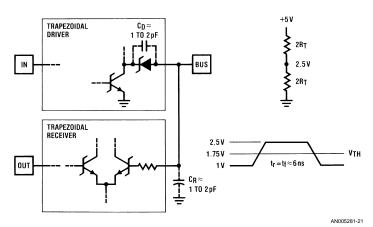

Figure 5 shows the recommended configuration for microcomputer buses. The use of a 3.4V source with a single termination resistor at each end reduces the average power dissipation of the bus. However, a two resistor termination connected between the line and the power rails, having the same Thevenin's equivalent, can be substituted for lower cost. Using a Miller integrator circuit, the driver generates a linearly rising and falling waveform with a constant slew rate of 0.2 V/ns (*Figure 6*). This corresponds to a nominal transition time of 15 ns. *Figure 7* compares the output waveform of a typical high speed driver to that of DS3662 under different load conditions. It should be noted that even under heavy loading, the regular drivers have peak slew rates that are much higher than the average. On the other hand, the trapezoidal waveform has a much lower slew rate with only a slight increase in the transition time. Such an increase in the transition time has little or no effect on the data rates. In fact, the high fidelity of the DS3662 driver output waveform allows pulse widths as low as 20 ns to be transmitted on the bus.

$R_T$  =  $50\Omega$  to  $90\Omega$

FIGURE 5. Recommended Bus Termination for Heavily Loaded Microstrip Backplanes

www.national.com

FIGURE 6. DS3662 Driver

Note 1: Typical high speed driver output unloaded;  $t_{\text{f}}$  =  $t_{\text{f}} \approx 3~\text{ns}$

Note 2: Typical high speed driver output unloaded;  $t_r = t_f \approx 10 \text{ ns}$

Note 3: Typical output of controlled slew rate driver which is load independent;  $t_r$  =  $t_f \approx 15$  ns

FIGURE 7. Waveform Comparison

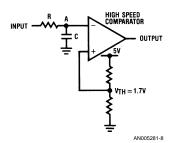

The receiver consists of a low pass filter followed by a high speed comparator, with a typical threshold of 1.7V (Figure 8). The noise immunity of the receiver is specified in terms of the width of a 2.5V pulse that is guaranteed to be rejected by the receiver. The receiver typically rejects a 20 ns pulse going positive from the ground level or going negative from the 3.4V logic 1 level. The receiver threshold lies within a specified 400 mV region over the supply and temperature range and is centered between the low and high levels of the bus for a symmetrical noise margin.

FIGURE 8. DS3662 Receiver

Other features of the device include a 100  $\mu$ A maximum DC bus loading specification under power ON or OFF condition and a glitch-free power up/down protection on the bus output

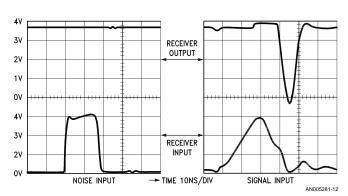

Waveforms in *Figure 9* demonstrate the ability of the receiver to distinguish the trapezoidal signal from noise. Here the receiver rejects a noise pulse of 19 ns width, while accepting a narrower signal pulse (16 ns) of the same peak amplitude (the signal is triangular because of the pulse width which is smaller than the transition time).

The real-world performance of the DS3662 transceiver shows an order of magnitude improvement in noise immunity over conventional transceivers under actual operating conditions (Reference #3). The controlled rise and fall times on the driver output significantly reduces both near end and the far end crosstalk. As expected, the pulse discrimination at the receiver input virtually eliminates the far end crosstalk, even on extremely long buses (over 100 feet). The near end crosstalk, which is particularly severe on the state of the art backplanes due to the tight spacing between the signal lines, is easily accommodated by the large percentage noise margin (>75%) provided by the receiver.

Field reports indicate that the DS3662 not only solves those mysterious intermittent failure problems in mini and microcomputer systems, but also helps them meet the new FCC emission requirements due to the reduced RF radiation from the bus.

FIGURE 9. DS3662 Receiver Response

FIGURE 10. High Speed Bus Transceiver with Low Output Loading for MicroComputer Backplanes

#### WHAT NEXT?

Since crosstalk scales with the signal amplitude, reducing the signal swing has not effect on the noise immunity as long as the percentage noise margin remains the same. On the other hand, there are several advantages in having lower signal swing. It reduces the drive current requirement of the driver thus reducing its output capacitance. Lower capacitive loading on the bus decreases its impedance reducing the drvie requirement even further. Having a lower current drive not only reduces the power dissipated at the terminations but also allows better matching of the termination due to the increased line impedance. In the ideal limiting case the driver has negligible loading effect on the bus and thus allows perfect termination under all load conditions.

In practice however, there are some obvious limitations. The receiver thresholds have to be maintained within tighter limits at lower signal swings to maintain the same percentage noise margin. Also, the capacitive loading is difficult to reduce beyond a certain point, due to the diminishing return in the way of lower current rating, as the loaded bus impedance approaches the unloaded impedance. However, the capacitance of an open collector driver output can be reduced significantly by using a Schottky diode as shown in *Figure 10*. The diode isolates the driver capacitance when the output is disabled. Using reduced signal swings and precise receiver

thresholds, such a transceiver can provide significant improvements in microcomputer bus performance. The transceiver design presented in *Figure 10* is being considered for incorporation into the Futurebus standard by the IEEE.

#### CONCLUSION

A well designed bus transceiver goes a long way in improving the noise immunity of a single-ended TTL bus. Further improvements in bus performance may come from the use of reduced voltage swings and better transceiver designs for lower bus loading and tighter receiver threshold limits. Although such approaches may not be TTL compatible, the improvement in performance gained may indeed justify a new standard for bus transceivers.

# REFERENCES

- 1) Bill Fowler, "Transmission Line Characteristics," National Semiconductor Application Note 108, May 1974.

- 2) A. Feller, H. P. Kaupp, and J. J. Digiacomo, "Crosstalk And Reflections In High Speed Digital Systems," proceedings—Fall Joint Computer Conference, pp. 511–525, 1965

- 3) R. V. Balakrishnan, *"Bus Optimizer,"* National Semiconductor Application Note 259, April 1981

www.national.com 6

| 4) David Montgomery, "Borrowing RF Techniques For Digital Design," Computer Design, pp. 207–217, May 1982 | 5) R. V. Balakrishnan, "Eliminating Crosstalk Over Long Distance Busing," Computer Design, pp. 155–162, March 1982 |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

|                                                                                                           |                                                                                                                    |

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 1 80-530 85 86 Fax: +49 (0) 1 80-530 85 86

Email: europe support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group

Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560

Fax: 81-3-5639-7507