# Appendix H Safe Operating Areas for Peripheral Drivers

National Semiconductor Application Note 213 Bill Fowler July 1986

Peripheral Drivers is a broad definition given to Interface Power devices. The devices generally have open-collector output transistors that can switch hundreds of milliamps at high voltage, and are driven by standard Digital Logic gates. They serve many applications such as: Relay Drivers, Printer Hammer Drivers, Lamp Drivers, Bus Drivers, Core Memory Drivers, Voltage Level Transistors, and etc. Most IC devices have a specified maximum load such as one TTL gate can drive ten other TTL gates. Peripheral drivers have many varied load situations depending on the application, and requires the design engineer to interpret the limitations of the device vs its application. The major considerations are *Peak Current, Breakdown Voltage*, and *Power Dissipation*.

### **OUTPUT CURRENT AND VOLTAGE CHARACTERISTICS**

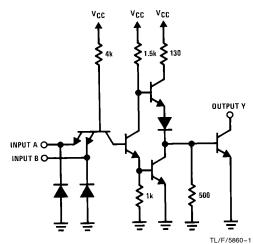

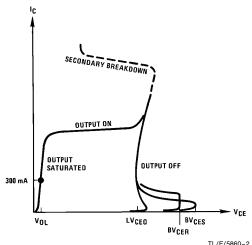

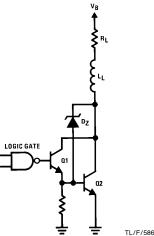

Figure 1 shows the circuit of a typical peripheral driver, the DS75451. The circuit is equivalent to a TTL gate driving a 300 mA output transistor. Figure 2 shows the characteristics of the output transistor when it is ON and when it is OFF. The output transistor is capable of sinking more than one amp of current when it is ON, and is specified at a  $V_{\rm OL} = 0.7V$  at 300 mA. The output transistor is also specified to operate with voltages up to 30V without breaking down, but there is more to that as shown by the breakdown voltages labeled BVCES. BVCER. and LVCEO.

FIGURE 1. Typical Peripheral Driver DS75451

BVCES corresponds to the breakdown voltage when the output transistor is held off by the lower output transistor of the TTL gate, as would happen if the power supply (V<sub>CC</sub>) was 5V. BVCER corresponds to the breakdown voltage when the output transistor is held off by the 500 resistor, as would happen if the power supply (V<sub>CC</sub>) was off (0V). LVCEO corresponds to the breakdown voltage of the output transistor if it could be measured with the base open. LVCEO can be measured by exceeding the breakdown voltage BVCES and measuring the voltage at output currents of 1 to 10 mA on a transistor curve tracer (LVCEO is some

times measured in an Inductive Latch-Up Test). Observe that all breakdown voltages converge on LVCEO at high currents, and that destructive secondary breakdown voltage occurred (shown as dotted line) at high currents and high voltage corresponding to exceeding the power dissipation of the device. The characteristics of secondary breakdown voltage vary with the length of time the condition exists, device temperature, voltage, and current.

FIGURE 2. Output Characteristics ON and OFF

# OUTPUT TRANSFER CHARACTERISTICS VS INDUCTIVE AND CAPACITIVE LOADS

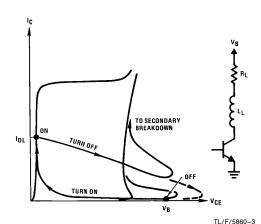

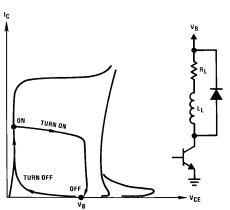

Figure 3 shows the switching transfer characteristics superimposed on the DC characteristics of the output transistor for an inductive load. Figure 4 shows the switching transfer characteristics for a capacitor load. In both cases in these examples, the load voltage  $(V_B)$  exceeds LVCEO. When the output transistor turns on with an inductive load the initial current through the load is 0 mA, and the transfer curve switches across to the left (VOL) and slowly charges the inductor. When the output transistor turns off with an inductive load, the initial current is IOL, which is sustained by the inductor and the transistor curve switches across to the right (V<sub>B</sub>) through a high current and high voltage area which exceeds LVCEO and instead of turning off (shown as dotted line) the device goes into secondary breakdown. It is generally not a good practice to let the output transistor's voltage exceed LVCEO with an inductive load.

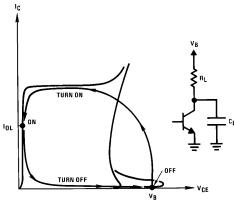

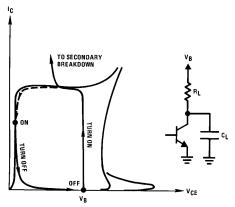

In a similar case with a capacitive load shown in Figure 4, the switching transfer characteristics rotate counter-clockwise through the DC characteristics, unlike the inductive load which rotated clockwise. Even though the switching transfer curve exceeds LVCEO, it didn't go into secondary breakdown. Therefore, it is an acceptable practice to let the output transistor voltage exceed LVCEO, but not exceed BVCER with a capacitive load.

FIGURE 3. Inductive Load Transfer Characteristics

TL/F/5860-4

# FIGURE 4. Capacitive Load Transfer Characteristics

Figure 5 shows an acceptable application with an inductive load. The load voltage ( $V_B$ ) is less than LVCEO, and the inductive voltage spike caused by the initial inductive current is quenched by a diode connected to  $V_B$ .

TL/F/5860-5

FIGURE 5. Inductive Load Transfer Characteristics

Clamped by Diode

Figure 6 shows the switching transfer characteristics of a capacitive load which leads to secondary breakdown. This condition occurs due to high sustained currents, not breakdown voltage. In this example, the large capacitor prevented the output transistor from switching fast enough through the high current and high voltage region; in turn the power dissipation of the device was exceeded and the output transistor went into secondary breakdown.

TL/F/5860-6

FIGURE 6. Capacitive Load Transfer Characteristics

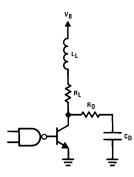

Figure 7 shows another method of quenching the inductive voltage spike caused by the initial inductive current. This method dampens the switching response by the addition of  $R_D$  and  $C_D$ . The values of  $R_D$  and  $C_D$  are chosen to critically dampen the values of  $R_L$  and  $L_L$ ; this will limit the output voltage to 2  $\times$   $V_B$ .

$$\frac{L_L}{(R_L + R_D)} \times \sqrt{\frac{1}{L_L \, C_D}} \leq 0.5$$

TL/F/5860-7

## FIGURE 7. Inductive Load Dampened by Capacitor

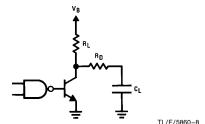

Figure 8 shows a method of reducing high sustaining currents in a capacitive load.  $R_{D}$  in series with the capacitor  $(C_{L})$  will limit the switching transistor without affecting final amplitude of the output voltage, since the IR drop across  $R_{D}$  will be zero after the capacitor is charged.

As an additional warning, beware of parasitic reactance. If the driver's load is located some distance from the driver (as an example: on the inclosure panel or through a connecting cable) there will be additional inductance and capacitance which may cause ringing on the driver output which will exceed LVCEO or transient current that exceeds the sustaining current of the driver. A 300 mA current through a small inductor can cause a good size transient voltage, as compared with 20 mA transient current observed with TTL gates. For no other reason than to reduce the noise associated with these transients, it is good practice to dampen the driver's output.

In conclusion, transient voltage associated with inductive loads can damage the peripheral driver, and transient currents associated with capacitive loads can also damage the driver. In some instances the device may not exhibit failure with the first switching cycle, but its conditions from ON to OFF will worsen after many cycles. In some cases the device will recover after the power has been turned off, but its long term reliability may have been degraded.

### POWER DISSIPATION

Power Dissipation is limited by the IC Package Thermal Reactance and the external thermal reactance of the environment (PC board, heat sink, circulating air, etc.). Also, the power dissipation is limited by the maximum allowable junction temperature of the device. There are two contributions to the power: the internal bias currents and voltage of the

device, and the power on the output of the device due to the Driver Load.

#### POWER LIMITATIONS OF PACKAGE

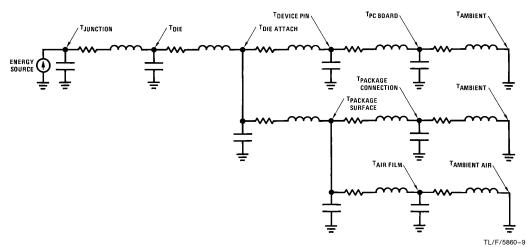

Figure 9 shows the equivalent circuit of a typical power device in its application. Power is shown equivalent to electrical current, thermal resistance is shown equivalent to electrical resistance, the electrical reactance C and L are equivalent to the capacity to store heat, and the propagation delay through the medium. There are two mediums of heat transfer: conduction through mass and radiant convection. Convection is insignificant compared with conduction and isn't shown in the thermal resistance circuits. From the point power is generated (device junction) there are three possible paths to the ultimate heat sink: 1) through the device leads; 2) through the device surface by mechanical connection; and 3) through the device surface to ambient air. In all cases, the thermal paths are like delay lines and have a corresponding propagation delay. The thermal resistance is proportional to the length divided by the cross sectional area of the material. The Thermal Inductance is proportional to the length of the material (copper, molding compound, etc.) and inversely proportional to the cross sectional area. The thermal capacity is proportional to the volume of the material

FIGURE 8. Capacitive Load with Current Limiting Resistor

FIGURE 9. Thermal Reactance from Junction to Ambient

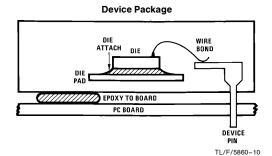

FIGURE 10. Components of Thermal Reactance for a Typical IC Package

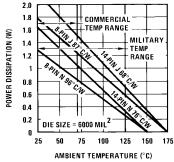

National Semiconductor specifies the thermal resistance from device junction through the device leads soldered in a small PC board, measured in one cubic foot of still air. Figure 11 shows the maximum package power rating for an 8 pin Molded, an 8 pin Ceramic, 14 pin Molded and a 14 pin Ceramic package. The slope of the line corresponds to thermal resistance ( $\varphi_{JA} = \Delta P/\Delta T$ ).

TL/F/5860-11

# FIGURE 11. Maximum Package Power Rating

The maximum allowable junction temperature for ceramic packages is 175°C; operation above this temperature will reduce the reliability and life of the device below an acceptable level. At a temperature of 500°C the aluminum metallization paths on the die start to melt. The maximum allowable junction temperature for a molded device is 150°C, operations above this may cause the difference in thermal expansion between the molding compound and package lead frame to sheer off the wire bonds from the die to the package lead. The industry standard for a molded device is 150°C, but National further recommends operation below 135°C if the device in its application will encounter a lot of thermal cycling (such as powered on and off over its life).

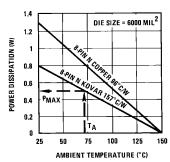

The way to determine the maximum allowable power dissipation from Figure 11, is to project a line from the maximum ambient temperature  $(T_A)$  of the application vertically (shown dotted in Figure 12), until the line intercepts the diagonal line of the package type, and then project a line (shown dotted) horizontally until the line intercepts the Power Dissipation Axis  $(P_{MAX})$ .

TL/F/5860-12

FIGURE 12. Maximum Package Rating Copper vs Kovar Lead Frame Packages

Figure 11 shows that 14 pin packages have less thermal resistance than 8 pin packages; which should be expected since it has more pins to conduct heat and has more surface area. Something that may not be expected is that the Thermal Resistance of the molded devices is comparable to the ceramic devices. The reason for the lower thermal resistance of the molded devices is the Copper lead frame, which is a better thermal conductor than the Kovar lead frame of the ceramic package. Almost all the peripheral drivers made by National Semiconductor are constructed with Copper lead frames (refer to  $\phi_{\rm JA}$  on the specific devices data sheet). The difference between the thermal resistance of Copper and Kovar in a molded package is shown in Figure 12.

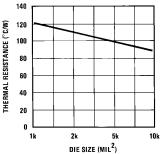

Another variance in thermal resistance is the size of the IC die. If the contact area to the lead frame is greater, then the thermal resistance from the Die to the Lead Frame is reduced. This is shown in *Figure 13*. The thermal resistance shown in *Figure 11* corresponds to die that are 6000 mil<sup>2</sup> in area.

TL/F/5860-13

FIGURE 13. Thermal Resistance vs Die Size

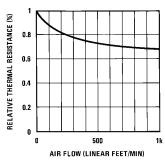

In most applications the prime medium for heat conduction is through the device leads to the PC board, but the thermal resistance can be significantly improved by cooling air driven across the surface of the package. The conduction to air is limited by a stagnant film of air at the surface of the package. The film acts as an additional thermal resistance. The thickness of the film is proportional to its resistance. The thickness of the film is reduced by the velocity of the air

across the package as shown in *Figure 14*. In most cases, the thermal resistance is reduced 25% to 250 linear feet/min, and 30% at 500 linear feet/min, above 500 linear feet/min the improvement flattens out.

TL/F/5860-14

# FIGURE 14. Thermal Resistance vs Air Velocity

The thermal resistance can also be improved by connecting the package to the PC board copper or by attaching metal wings to the package. The improvement by these means is outside the control of the IC manufacturer, but is available from the manufacturer of the heat sink device. If the IC is mounted in a socket rather than soldered to a PC board, the thermal resistance through the device leads will worsen. In most cases, the thermal resistance is increased by 20%; again this is a variable subject to the specific socket type.

The maximum package rating shown in this note corresponds to a 90% confidence level that the package will have thermal resistance equal to or less than the value shown. The thermal resistance varies  $\pm 5\%$  about the mean due to variables in assembly and package material.

#### **CALCULATIONS OF POWER DISSIPATION**

Most IC devices (such as  $T^2L$ ) operate at power levels well below the device package rating, but peripheral drivers can easily be used at power levels that exceed the package rating unknowingly, if the power dissipation isn't calculated. As an example, the DS3654 Ten Bit Printer Driver could dissipate 3 watts (DC and, even more AC), and it is only in a 0.8 watt package. In this example, the device would be destroyed in moments, and may even burn a hole in the PC board it is mounted on. The DS3654 data sheet indicated that the 10 outputs could sink 300 mA with a  $V_{\rm OL}$  of 1 volt, but it wasn't intended that all the outputs would be sinking this current at the same time, and if so, not for a long period. The use of the DS3654 requires that the power be calculated vs the duty cycle of the outputs.

The DC power dissipation is pretty obvious, but in another example, a customer used the DS3686 relay driver to drive 6.5h inductive load. The DS3687 has an internal clamp network to quench the inductive back swing at 60V. At 5 Hz the device dissipates 2 watts, with transient peaks up to 11 watts. After 15 minutes of operation, the driver succumbs to thermal overload and becomes non-functional. The DS3687 was intended for telephone relay, which in most applications switches 20 times a day.

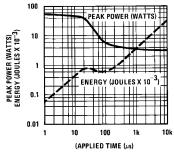

Peripheral driver will dissipate peak power levels that greatly exceed the average DC power. This is due to the capacity of the die and package to consume the transient energy while still maintaining the junction temperature at a safe level.

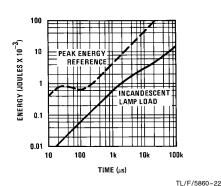

This capacity is shown as a capacitor in Figure 9. In the lab (under a microscope) a device may be observed to glow orange around the parameter of the junction under excessive peak power without damage to the device. Figure 15 shows a plot of maximum peak power vs applied time for the DS3654, and the same information plotted as energy vs applied time. To obtain these curves, the device leakage current when it switches off was used to monitor device limitation. Note in Figure 15 there is a transition in the curve about 10  $\mu s$ . At this point, the thermal capacity of the die has been exceeded. The thermal delay to the next thermal capacity (the package) was too long, and limited the peak power. These levels are not suggested operating levels, but an example of a Peripheral Driver to handle peak transient power.

TL/F/5860-15

FIGURE 15. Peak Power and Energy vs the Period of Time the Power was Applied

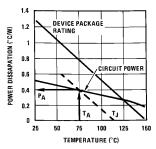

To calculate power dissipation, the only information available to the design engineer is the parametric limits in the device data sheet, and the same information about the load reactance. If the calculations indicate the device is within its limits of power dissipation, then using those parametric limits is satisfactory. If the calculation of power dissipation is marginal, the parametric limits used in the calculations might be worst case at low temperature instead of high temperature due to a positive temperature coefficient (T<sub>C</sub>) of resistance. IC resistors and resistors associated with the load generally have a positive T<sub>C</sub>. On the other hand, diodes and transistor emitter base voltages have a negative T<sub>C</sub>; which may in some circuits negate the effect of the resistors T<sub>C</sub>. Peripheral output transistors have a positive T<sub>C</sub> associated with VOL; while output Darlington transistors have a negative T<sub>C</sub> at low currents and may be flat at high currents. Figure 16 shows an example of power dissipation vs temperature; note that the power dissipation at the application's maximum temperature (TA) was less than the power dissipation at lower temperatures. Since maximum junction temperature is the concern of the calculation, then maximum ambient temperature power should be used. The junction temperature may be determined by projecting a line (shown dotted in Figure 16), with a slope proportional to  $\phi_{JA}$  back to the horizontal axis (shown as T<sub>J</sub>). If the point is below the curve then T<sub>J</sub> will be less than 150°C. T<sub>J</sub> must not exceed the maximum junction temperature for that package type. In this example. T<sub>1</sub> is less than 150°C as required by a molded package. To calculate the power vs temperature, it is necessary to characterize the device parameters vs temperature. Unfortunately, this information is not always provided by IC manufacturers in the device data sheets. A method to calcu-

late I<sub>CC</sub> vs temperature is to measure a device, then normalize the measurements vs the typical value for  $I_{\mbox{\footnotesize{CC}}}$  in the data sheet, then worst case the measurements by adding 30%. Thirty percent is normally the worst-case resistor tolerance that IC devices are manufactured to.

TL/F/5860-16 FIGURE 16. IC Power Dissipation vs Temperature

# **CALCULATION OF OUTPUT POWER WITH** AN INDUCTIVE LOAD

For this example, the device output circuit is similar to the DS3654 (10-Bit Printer Solenoid Driver) and the DS3686 and DS3687 (Telephone Relay Driver) as shown in Figure 17. Special features of the circuit type are the Darlington output transistors Q1 and Q2 and the zener diode from the collector of Q1 to the base of Q2. The Darlington output requires very little drive from the logic gate driving it and in turn dissipates less power when the output is turned ON and OFF, than a single saturating transistor output would. The zener diode (DZ) quenches the inductive backswing when the output is turned OFF.

### **Device and Load Characteristics Used for Power Calculation**

| $V_{OL}$         | Output Voltage ON    | 1.5V         |

|------------------|----------------------|--------------|

| $V_{C}$          | Output Clamp Voltage | 65V          |

| $V_B$            | Load Voltage         | 30V          |

| $R_L$            | Load Resistance      | 120 $\Omega$ |

| $L_{L}$          | Load Inductance      | 5h           |

| $T_{ON}$         | Period ON            | 100 ms       |

| T <sub>OFF</sub> | Period OFF           | 100 ms       |

| Т                | Total Period         | 200 ms       |

FIGURE 17. Peripheral Driver with Inductive Load

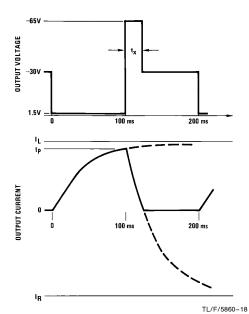

Refer to Figure 18 voltage and current waveforms corresponding to the power dissipation calculated for this example of an inductive load.

PON = Average power dissipation in device output when device is ON during total period (T)

when device is ON during total period

$$\tau = \frac{L_L}{R_L} = \frac{5h}{120\Omega} = 41.7 \text{ ms}$$

$$I_L = \frac{V_B - V_{OL}}{R_L} = \frac{30 - 1.5}{120} = 237.5 \text{ mA}$$

$$I_P = I_L (1 - e^{-T_{ON/7}})$$

$$I_P = 237.5 \text{ mA} (1 - e^{-100 \text{ ms}/41.7 \text{ ms}})$$

$$I_P = 237.5 \text{ mA (1} - e^{-100 \text{ ms/41.7 ms})}$$

$I_P = 215.9 \, \text{mA}$

$$P_{ON} = V_{OL} \times I_{L} \times \frac{T_{ON}}{T} \left[ 1 - \int_{\circ}^{T_{ON}} \frac{e^{-t/\tau} dt}{T_{ON}} \right]$$

$$P_{ON} = V_{OL} \times I_{L} \times \frac{T_{ON}}{T} \left[ 1 - \frac{\tau}{T_{ON}} (1 - e^{-T_{ON/\tau}}) \right]$$

$$100 \left[ -41.7 \right]$$

$$P_{ON} = 1.5 \times 237.5 \text{ mA} \times \frac{100}{200} \left[ 1 - \frac{41.7}{100} (1 - e^{-100/41.7}) \right]$$

$P_{\mbox{ON}} = 110.6 \ \mbox{mW}$

P<sub>OFF</sub> = Average power dissipation in device output when device is OFF during total period (T)

$$\begin{split} I_{R} &= \frac{V_{C} - V_{B}}{R_{L}} = \frac{65 - 30}{120\Omega} = 291.7 \text{ mA} \\ t_{x} &= \tau \, \ell \, n \left( \frac{I_{P} + I_{R}}{I_{R}} \right) \\ t_{x} &= 41.7 \text{ ms } \, \ell \, n \left( \frac{215.9 + 291.7}{291.7} \right) = 23.1 \text{ ms} \\ P_{OFF} &= V_{C} \times \frac{t_{x}}{T} \left[ \left( I_{P} + I_{R} \right) \int_{s}^{t_{x}} \frac{e^{-t/\tau} \, dt}{t_{x}} - I_{R} \right] \\ P_{OFF} &= V_{C} \times \frac{t_{x}}{T} \left[ \left( I_{P} + I_{R} \right) \times s \frac{\tau}{t_{x}} (1 - e^{-t_{x/\tau}}) - I_{R} \right] \\ P_{OFF} &= 65 \times \frac{23.1}{200} \left[ (215.9 \text{ mA} + 291.7 \text{ mA}) \frac{41.7}{23.1} \right] \\ &\qquad \qquad (1 - e^{-23.1/41.7}) - 291.7 \text{ mA} \end{split}$$

$P_{OFF} = 736 \, mW$

$P_O = Average power dissipation in device output$

$$P_{O} = P_{ON} + P_{OFF} = 110.6 + 736 = 846.6 \text{ mW}$$

In the above example, driving a  $120\Omega$  inductive load at 5 Hz, the power dissipation exceeded a more simple calculation of power dissipation, which would have been:

$$\begin{split} P_O &= \frac{V_{OL} \left( V_B - V_{OL} \right)}{R_L} \times \frac{T_{ON}}{T} \\ P_O &= \frac{1.5 \left( 30 - 1.5 \right)}{120} \times \frac{100 \text{ ms}}{200 \text{ ms}} = 182.5 \text{ mW} \end{split}$$

An error 460% would have occurred by not including the reactive load. The total power dissipation must also include other outputs (if the device has more than one output), and the power dissipation due to the device power supply currents. This is an example where the load will most likely exceed the device package rating. If the load is fixed, the power can be reduced by changing the period (T) and duty rate (T<sub>ON</sub>/T<sub>OFF</sub>).

FIGURE 18. Voltage and Current Waveforms

Corresponding to Inductive Load

# CALCULATION OF OUTPUT POWER WITH AN INCANDESCENT LAMP

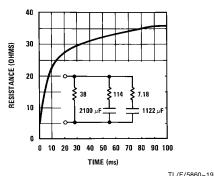

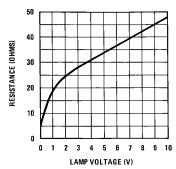

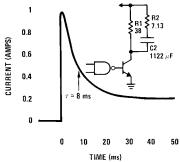

An incandescent lamp is equivalent to a reactive load. The reactance is related to the period of time required to heat the lamp and the filaments positive temperature coefficient of resistance. *Figure 19* shows the transient response for a typical lamp used on instrument panels, and the equivalent electrical model for the lamp. Much like IC packages the lamp has a thermal circuit and its associated propagation delay. This lamp filament has an 8 ms time constant, and a longer 250 ms time constant from the lamp body to ambient. The DC characteristics are shown in *Figure 20*. Note the knee in the characteristics at 2 volts; this is where power starts to be dissipated in the form of light. This subject is important, since more peripheral drivers are damaged by lamps than any other load.

FIGURE 19. Transient Response of an Incandescent Lamp

TL/F/5860-20

FIGURE 20. DC Characteristics of an Incandescent Lamp

Figure 21 shows the transient response of a driver similar to a DS75451 driving the lamp characterized in Figures 19 and 20. The equivalent load doesn't include the reactance of the lamp base to ambient, which has a 250 ms time constant, since 10 ms to an IC is equivalent to DC. The peak transient current was 1 amp, settling to 200 ms, with an 8 ms time constant. Observe the peak current is clamped at 1 amp, by the sinking ability of the driver; otherwise the peak current may have been 1.2 amps. The DS75451 is only rated at 300 mA, but it is reasonable to assume it could sink 1 amp because of the designed force β required for switching response and worst case operating temperature.

TL/F/5860-21

FIGURE 21. Transient Incandescent Lamp Current

Calculation of the energy dissipated by a peripheral driver for the transient lamp current shown in Figure 21 is shown above, and the plot of energy vs time is shown in Figure 22. Figure 22 also includes as a reference the maximum peak energy from Figure 15. It can be seen from Figure 22 that in this example there is a good safety margin between the lamp load and the reference max peak energy. If there were more drivers than one per package under the same load, the margin would have been reduced. Also, if the peripheral driver couldn't saturate because it couldn't sink the peak transient lamp current, then the energy would also reduce the margin of safe operation.

FIGURE 22. Energy vs Time for a Peripheral **Driver with an Incandescent Lamp Load**

# **CALCULATION OF ENERGY IN AN INCANDESCENT LAMP**

$$\begin{split} \text{Energy} &= \int_{\bullet}^{t} \text{V}_{OL} \left( \text{I}_{R1} + \text{I}_{R2} \right) \text{dt} \\ \text{i}_{R1} &= \frac{\text{V}_{B} - \text{V}_{OL}}{\text{R1}} = \text{I}_{R1} \\ \text{i}_{R2} &= \left( \frac{\text{V}_{B} - \text{V}_{OL}}{\text{R2}} \right) \text{e}^{-\text{t}/\tau} \\ &= \text{I}_{R2} \, \text{e}^{-\text{t}/\tau} \quad \tau = \text{R2C2} \\ \text{Energy} &= \int_{\bullet}^{t} \text{V}_{OL} \left( \text{I}_{R1} + \text{I}_{R2} \, \text{e}^{-\text{t}/\tau} \right) \text{dt} \\ &= \text{V}_{OL} \left[ \text{I}_{R1} t + \text{I}_{R2} \tau \left( \text{i} - \text{e}^{-\text{t}/\tau} \right) \right] \\ \text{Given:} \quad \text{V}_{OL} &= 0.6 \text{V} \\ \text{I}_{R1} &= 0.2 \, \text{Amps} \end{split}$$

$I_{B1} + I_{B2} = 1 \text{ Amp}$

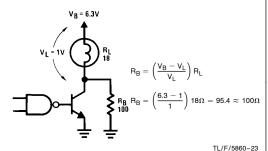

A common technique used to reduce the 10 to 1 peak to DC transient lamp current is to bias the lamp partially ON, so the lamp filament is warm. This can be accomplished as shown in Figure 23. From Figure 20 it can be seen that the lamp resistance at 0V is  $5.7\Omega$ , but at 1V the resistance is 18 $\Omega$ . At 1V the lamp dosen't start to emit light. Using a lamp resistance of  $100\Omega$  and lamp voltage of 1V, R<sub>B</sub> was calculated to be approximately  $100\Omega$ . This circuit will reduce the peak lamp current from 1 amp to 316 mA.

FIGURE 23. Circuit Used to Reduce Peak **Transient Lamp Current**

# PERIPHERAL DRIVER SECTION

National Semiconductor has a wide selection of peripheral drivers as shown in this section's guide. The DS75451, DS75461, DS3631 and the DS3611 series have the same selection of logic function in an 8-pin package. The DS75461 is a high voltage selection of the DS75451 and may switch slower. The DS3611 and DS3631 are very high voltage circuits and were intended for slow relay applications. The DS3680, DS3686, and DS3687 were intended for 56V telephone relay applications. The DS3654 contains a 10-bit shift register followed by ten 250 mA clamped drivers. The DS3654 was intended for printer solenoid applications. High current and high voltage peripheral drivers find many applications associated with digital systems, and it is the intention of the application note to insure that reliability and service life of peripheral drivers equal or exceed the performance of the other logic gates made by National.

For additional information, please contact the Interface Marketing Department at National or one of the many field application engineers world-wide.

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** Corporation 1111 West Bardin Road Arlington, TX 76017

Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 **National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwege etevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tei: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408