# N-200

## CMOS A/D Converter Chips Easily Interface to 8080A Microprocessor Systems

National Semiconductor Application Note 200 March 1978

### SUMMARY

This paper describes techniques for interfacing National Semiconductor's new ADC3511 and ADC3711 microprocessor compatible analog-to-digital converter chips to 8080A microprocessor systems. The hardware interface and the software interrupt service routine will be described for single and multiple A/D converter data acquisition systems.

### INTRODUCTION

The recent introduction of monolithic digital voltmeter chips has encouraged designers to consider their use as analogto-digital converters in data acquisition systems. While the high accuracy afforded at low cost was attractive, certain difficulties in applying these devices in digital systems were encountered. Most of these difficulties were due to the DVM chip's output structure being oriented towards driving 7-segment displays with internally generated digit scanning rates. National Semiconductor has recently introduced a family of monolithic CMOS A/D converters-2 of these devices are directed towards LED display DPM and DVM applications (ADD3501 3 1/2-digit DPM and ADD3701 3 3/4-digit DPM) while the other 2 (ADC3511 3 1/2-digit A/D and ADC3711 3 3/4-digit A/D) have addressable BCD outputs. These last 2 devices allow easy interface to microprocessor and calculator-oriented (COPS) systems.

Single or multiple channel monitoring of physical variables can be achieved with high accuracy despite the lack of complexity and low overall cost.

### A/D CONVERSION

All A/D converters in this family operate from a single 5V supply and convert inputs from 0 to  $\pm$ 2V. The converters use a pulse-width modulation technique which requires no precision components and exhibits low offset, low drift, high linearity and no rollover error. An additional advantage is that the voltage reference is of the same polarity as the supply.

Two resolutions are offered: the 3 1/2-digit types divide the input into 2,000 counts plus sign, while the 3 3/4-digit types provide 4,000 counts plus sign which is roughly equivalent to the resolution of a 12-bit plus sign binary converter. The 3 1/2-digit converters require 200 ms per conversion; 3 3/4-digit types require 400 ms.

The converters handle negative inputs by internally switching the inputs and forcing the sign bit low. While this technique allows conversion of positive and negative inputs with only a single supply, the supply must be isolated from the inputs. Without an isolated supply, only positive voltages may be converted.

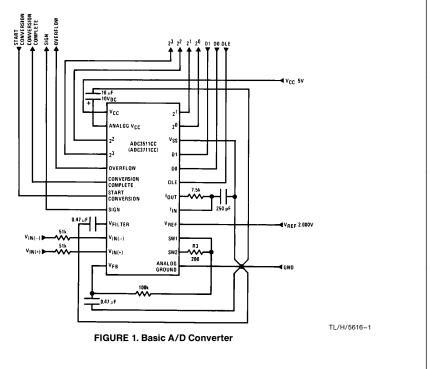

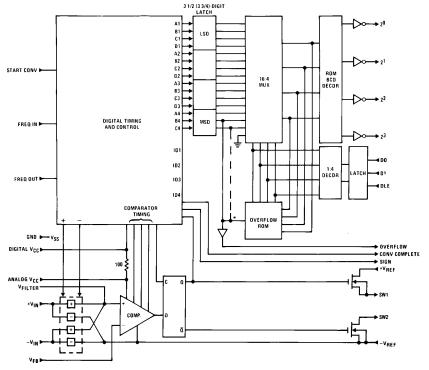

The basic converter is shown in *Figure 1*. The actual conversion technique is described in Appendix A.

### **BCD OUTPUT DESCRIPTION**

The ADC3511 and ADC3711 present the output data in BCD form on a single 4-line output port, plus a separate sign output. The desired digit is selected by a 2-bit address which is latched by a high level at the Digit Latch Enable input (DLE); a low level at DLE allows flow thru operation. Since the output is BCD, it is compatible with many standard instruments and can easily be converted into binary by the processor if this format should be desired. Overrange inputs are indicated by a hexidecimal "EEEE" plus an Overflow output

A new conversion is begun by a positive pulse or high level at the Start Conversion (SC) input. The analog section of the converter continuously tracks the analog input. The Start Conversion command controls only the transfer of new data to the output latches, consequently the delay from the SC pulse to the Conversion Complete (CC) signal may vary from several milliseconds to several hundred milliseconds. In interrupt driven systems the delay is no problem, since the processor does not execute delay instructions while waiting for the data. However, if in-line or program I/O is used where the program waits for the data to be ready, the maximum delay between SC and CC must be programmed into the wait routine. This type of I/O is therefore not as efficient as interrupt I/O.

The CC output goes low immediately after the SC pulse. At the end of a conversion, CC goes high and remains high until a new conversion is initiated. Continuous conversion operation is obtained by tying the SC input to  $V_{CC}$ .

### REFERENCE VOLTAGE

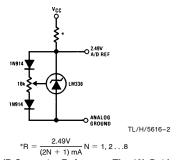

The 2.000V reference is derived from the LM336, a recently announced monolithic reference which provides 2.5V with low drift at low cost. This active reference is adjusted for minimum thermal drift of about 20 ppm/°C by using a third terminal on the device to adjust its output to 2.490V.

Total reference current consumption is low, as the LM336 requires only 1 mA of bias current, and the resistor divider about 2 mA. The reference circuit is shown in *Figure 2*.

FIGURE 2. A/D Converter Reference. The 10k Pot is Adjusted to a Voltage of 2.49V on the Output; at this Voltage Minimum Drift Occurs. The Reference can Supply up to 8 A/D Converters.

One reference can be used for many A/D's. The values of the upper series resistor R1 depends on the number of converters used.

### A SINGLE CHANNEL CONVERTER

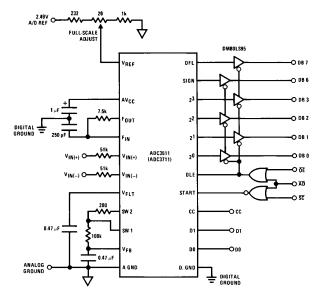

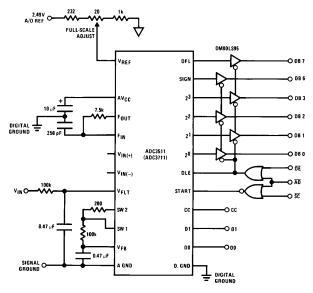

A complete A/D port is seen in Figures 3 and 4. Figure 3 shows a Dual Polarity converter and Figure 4 a Positive Only Polarity converter. Each port contains an A/D converter, TRI-STATE® bus driver, and 2 gates to control I/O. This A/D port is easily used in single or multi-channel systems. In multichannel systems a converter is used on every channel allowing digital multiplexing of the outputs.

Data from the A/D converter in a single channel system is easily processed using an OUT command to start a conversion and IN commands to read the data after the microprocessor has been interrupted by a Conversion Complete.

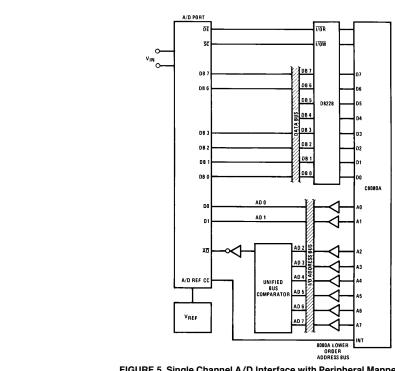

As seen in *Figure 5*, a single channel A/D port uses a 6-bit bus comparator to decode its assigned peripheral address from the lower address bits of the 8080A address bus.

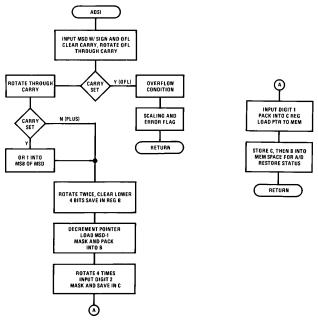

When an interrupt is received, the present status of the processor is stored on the stack memory by a series of push commands. The interrupt is serviced by reading digit 4 (MSD) into the processor and checking the overflow bit. If the overflow bit is high, the converter input has exceeded its range and an error signal is generated, indicating that scaling must be done to attenuate the input signal. If the OFL is low, the sign bit is then checked to determine the polarity of the conversion. If the sign bit is low, a "1" is added to the MSB of digit 4. Since this bit would normally be low, (maximum converter range allows MSB ≤ 3 or 0011) a "1" in this position is used to denote a negative input voltage. The 4 bits of digit 4 which now include the sign are shifted into the upper half of the first byte and the 4 bits of digit 3 are packed into the lower half. Similarly, digits 2 and 1 are packed into the second byte and both bytes stored in mem-

Figure 6 and routine 1 are the flow chart and assembly lanquage routine used to implement this action.

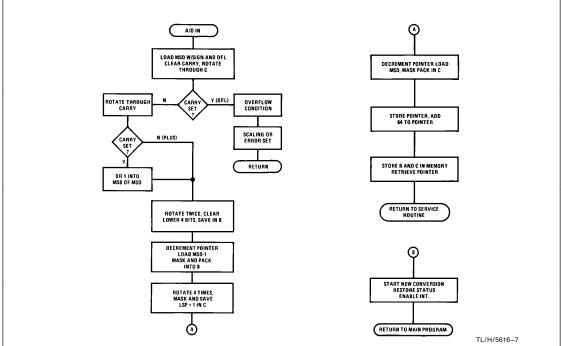

### 8-CHANNEL A/D WITH SOFTWARE PRIORITY

The basic A/D port can easily be expanded to multiple channel systems. An 8-channel system is seen in *Figure 7*. This system interrupts the processor when one of the Conversion Complete outputs goes high. The processor saves the current status and reads the status word of the A/D system. The status word is then compared to a priority table. Each level in the table corresponds to a priority level with high priority converters which are first in the table. If 2 or more converters have the same priority and are ready at the same time, the converter with the highest number gets serviced first.

The program determines which service routine to use by the bit position of "1's" in the status word. The routine loads the address pointer to digit 4 of the selected converter. The

program then calls a subroutine which goes through the process of checking overflow, sign and packs 4 BCD digits into 2 bytes. These 2 bytes are then stored in a table in the memory directly above the converter addresses. After a

channel is serviced, the original processor status is restored and the interrupt enabled. If additional channels need service, they immediately interrupt so the new status word is then read and a new priority established.

FIGURE 3. Dual Polarity A/D Requires that Inputs are Isolated from the Supply. Input Range Is  $\pm\,1.999V.$

FIGURE 4. Positive Polarity A/D Operating from 5V Supply. Input Range Is  $\,+$  1.999V.

FIGURE 5. Single Channel A/D Interface with Peripheral Mapped I/O

FIGURE 6. Flow Chart for Single Channel A/D Converter

| LABEL  | OPCODE | OPERAND                                    | COMMENT                | LABEL         | OPCODE  | OPERAND                                                   | COMMENT                |

|--------|--------|--------------------------------------------|------------------------|---------------|---------|-----------------------------------------------------------|------------------------|

| ADIS:  | PUSH   | PSW                                        |                        | LADEL         | IN      | ADD 2                                                     | ; delay                |

| ADIS.  | РОЗП   | POW                                        | ; A/D interrupt        |               | RAL     | ADD 2                                                     |                        |

|        | DUIGU  |                                            | service                |               |         |                                                           | ; rotate               |

|        | PUSH   | Н                                          | ; save                 |               | RAL     |                                                           | ; into                 |

|        | PUSH   | В                                          | ; current status       |               | RAL     |                                                           | ; upper                |

|        | IN     | ADD 4                                      | ; input A/D digit 4    |               | RAL     |                                                           | ; 4 bits               |

|        | IN     | ADD 4                                      | ; delay                |               | ANI     | FO                                                        | ; mask lower bits      |

|        | ORA    |                                            | ; reset carry          |               | MOV     | C, A                                                      | ; save in C            |

|        | RAL    |                                            | ; rotate OFL thru      |               | IN      | ADD 1                                                     | ; in digit 1           |

|        |        |                                            | carry                  |               | IN      | ADD 1                                                     | ; delay                |

|        | JC     | OFL                                        | ; overflow condition   |               | ANI     | OF                                                        | ; mask upper bits      |

|        | RAL    |                                            | ; rotate sign thru     |               | OR      | С                                                         | ; pack                 |

|        |        |                                            | carry                  |               | MOV     | C, A                                                      | ; save in C            |

|        | JC     | PLUS                                       | ; positive input       |               | LXI     | H, ADMS                                                   | ; load ptr to A/D      |

|        | ORI    | 20H                                        | ; OR 1 into MSB,       |               |         |                                                           | ; Mem, space           |

|        |        |                                            | neg input              |               | MOV     | M, C                                                      | ; save C in memory     |

| PLUS:  | RAL    |                                            | ; shift                |               | INX     | н                                                         | ; point next           |

| . 200. | RAL    |                                            | ; into position        |               | MOV     | M, B                                                      | ; save B in memory     |

|        | ANI    | FO                                         | ; mask lower bits      |               | OUT     | ADD 1                                                     | ; start new conver-    |

|        | MOV    | BA                                         | ; save in B            |               | 001     | ו מטא                                                     | sion                   |

|        |        |                                            | •                      |               | DOD     | D                                                         |                        |

|        | IN     | ADD 3                                      | ; input digit 3        |               | POP     | В                                                         | ; restore              |

|        | IN     | ADD 3                                      | ; delay                |               | POP     | H                                                         | ; previous             |

|        | ANI    | OF                                         | ; mask higher bits     |               | POP     | PSW                                                       | ; status               |

|        | OR     | В                                          | ; pack into B          |               | EI      |                                                           | ; enable interrupts    |

|        | MOV    | B, A                                       | ; save in B            |               | RET     |                                                           | ; return to main       |

|        | IN     | ADD 2                                      | ; input digit 2        |               |         |                                                           | program                |

|        |        | VREF 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | Sign (1)               | UNI BUS COM   | AD 11 1 | D2 D1 D0 A15 A14 A13 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 |                        |

|        | FIGURE | 7. 8-Channel A                             | /D System with Maskabl | e Priority In | AD 2    | A1 A0 Memory Mapp                                         | TL/H/5616-5<br>red I/O |

|        | FIGURE | 7. 8-Channel A                             | /D System with Maskabl | e Priority In | AD 0    | A1 A0                                                     |                        |

FIGURE 8. Flow Charts of A/D Routines (Continued)

| Routine 2. 8-Channel Interrupt Service Routine with Software Priority |        |                                         |                               |          |            |                |                                      |  |  |

|-----------------------------------------------------------------------|--------|-----------------------------------------|-------------------------------|----------|------------|----------------|--------------------------------------|--|--|

| LABEL                                                                 | OPCODE | OPERAND                                 | COMMENT                       | LABEL    | OPCODE     | <b>OPERAND</b> | COMMENT                              |  |  |

| IAD:                                                                  | PUSH   | PSW                                     | ; interrupt from A/D          |          | XCGH       |                | ; exchange DE, HL                    |  |  |

|                                                                       | PUSH   | Н                                       | ; save H & L on               |          | PCHL       |                | ; jump to input                      |  |  |

|                                                                       |        |                                         | stack                         |          |            |                | routine                              |  |  |

|                                                                       | PUSH   | В                                       | ; save B & C on<br>stack      | INAD1:   | LXI        | H, AD1         | ; pickup pointer to<br>A/D 1         |  |  |

|                                                                       | PUSH   | D                                       | ; save D & E on<br>stack      |          | CALL       | ADIN           | ; call common input routine          |  |  |

|                                                                       | LXI    | H, ADWD                                 | ; pickup A/D status<br>word   |          | MOV<br>JMP | M, A<br>DONE   | ; start new conversion<br>; all done |  |  |

|                                                                       | MOV    | 6, M                                    | ; move word into B            | INAD2:   | LXI        | H, AD2         | ; pickup pointer to                  |  |  |

|                                                                       | LXI    | H, PRTBL                                | ; pickup priority tbl         | IIV/IDZ. | LXI        | 11,7102        | A/D 2                                |  |  |

|                                                                       |        | .,,                                     | pointer                       |          | CALL       | ADIN           | ; call input routine                 |  |  |

| TEST:                                                                 | MOV    | A, B                                    | ; place status word in accum. |          | MOV        | M, A           | ; start new conver-<br>sion          |  |  |

|                                                                       | ANA    | М                                       | ; mask with priority          |          | JMP        | DONE           | ; all done                           |  |  |

|                                                                       | 711471 | IVI                                     | table                         |          | •          | BOILE          | , an done                            |  |  |

|                                                                       | JNZ    | FIND                                    | ; match jump to<br>Find       |          | •          |                |                                      |  |  |

|                                                                       | INX    | Н                                       | ; point to lower              | DONE:    | POP        | D              | ; restore D                          |  |  |

|                                                                       |        | • • • • • • • • • • • • • • • • • • • • | priority                      | 50.12.   | POP        | В              | : restore B                          |  |  |

|                                                                       | JMP    | TEST                                    | ; try again                   |          | POP        | H              | ; restore H                          |  |  |

| FIND:                                                                 | LXI    | H, RTBL                                 | ; pickup routine tbl          |          | POP        | PSW            | ; restore PSW                        |  |  |

|                                                                       |        | ,                                       | pointer                       |          | EI         |                | ; enable interrupts                  |  |  |

|                                                                       | ORA    | Α                                       | ; reset carry                 |          | RET        |                | ; return to main                     |  |  |

| GTBIT:                                                                | RAR    |                                         | ; rotate thru carry           |          |            |                | program                              |  |  |

|                                                                       | JC     | GTAD                                    | ; bit was found               | PRTBL:   | DB         | 04H            | ; 0000C100 AD3                       |  |  |

|                                                                       | INX    | Н                                       | ; point to                    |          |            |                | highest priority                     |  |  |

|                                                                       | INX    | Н                                       | ; next routine                |          | DB         | 03H            | ; 0000011 AD2 &                      |  |  |

|                                                                       | JMP    | GTBIT                                   | ; try again                   |          |            |                | AD1 next priority                    |  |  |

| GTAD:                                                                 | MOV    | E, M                                    | ; move first byte into E      |          |            |                |                                      |  |  |

|                                                                       | INX    | Н                                       | ; point to next byte          |          |            |                |                                      |  |  |

|                                                                       | MOV    | D, M                                    | ; move second byte into D     |          |            |                |                                      |  |  |

| Poutine 2 8-char    | nnel Interrupt Service       | Pouting with Soft | ware Priority (Co  | ntinued)            |

|---------------------|------------------------------|-------------------|--------------------|---------------------|

| noullile 2. o-ciiai | III CI III LEII UDL SEI VICE | TOULINE WILL SON  | IWale Filolity (OU | i i i i i i u e u i |

| LABEL OPCODE OPERAND |     | OPERANI | COMMENT LABEL         |  | OPCODE | OPERAND | COMMENT               |  |

|----------------------|-----|---------|-----------------------|--|--------|---------|-----------------------|--|

| PRTBL:               | DB  | 10H     | ; 00010000 AD5        |  | MOV    | B, A    | ; save in B           |  |

|                      |     |         | lowest priority       |  | DCR    | Н       | ; point to LSD + 1    |  |

| RTBL:                | DW  | 1000H   | ; routine for A/D 1   |  | MOV    | A, M    | ; input LSD + 1       |  |

|                      | DW  | 100CH   | ; routine for A/D 2   |  | MOV    | A, M    | ; delay               |  |

|                      | •   |         |                       |  | RAL    |         | ; rotate              |  |

|                      | •   |         |                       |  | RAL    |         | ; into                |  |

|                      | •   |         |                       |  | RAL    |         | ; upper               |  |

|                      | DW  | 1060H   | ; routine for A/D 8   |  | RAL    |         | ; 4 bits              |  |

| ADIN:                | MOV | A, M    | ; Input MSD plus      |  | ANI    | FO      | ; mask lower bits     |  |

|                      |     |         | OFL & SIGN            |  | MOV    | C, A    | ; save in C           |  |

|                      | MOV | A, M    | ; delay               |  | DCR    | Н       | ; point to LSD        |  |

|                      | ORA | Α       | ; reset carry         |  | MOV    | A, M    | ; input LSD           |  |

|                      | RAL |         | ; rotate left thru    |  | MOV    | A, M    | ; delay               |  |

|                      |     |         | carry, OFL            |  | ANI    | OF      | ; mask upper bits     |  |

|                      | JC  | OFL     | ; jump to overflow    |  | OR     | С       | ; pack                |  |

|                      |     |         | if set                |  | MOV    | C, A    | ; save in C           |  |

|                      | RAL |         | ; rotate left thru    |  | SHLD   | TEMP    | ; store HL in temp    |  |

|                      |     |         | carry, sign           |  | MOV    | A, L    | ; move L in accum.    |  |

|                      | JC  | PLUS    | ; jump to plus if set |  | ACI    | 64      | ; generate lower      |  |

|                      | OR1 | 20H     | ; OR1 into BCD,       |  |        |         | address               |  |

|                      |     |         | MSB for minus         |  | MOV    | L, A    | ; above memory        |  |

| PLUS:                | RAL |         |                       |  |        |         | mapped                |  |

|                      | RAL |         |                       |  | MOV    | A, H    | ; converter addresses |  |

|                      | ANI | FO      | ; mask lower order    |  | ACI    | 0       | ; include carry       |  |

|                      |     |         | bits                  |  | MOV    | H, A    | ; to upper bits       |  |

|                      | MOV | B, A    | ; save in B           |  | MOV    | M, C    | ; store C             |  |

|                      | DCR | Н       | ; point to MSD-1      |  | INX    | Н       | ; then                |  |

|                      | MOV | A, M    | ; input MSD-1         |  | MOV    | M, B    | ; store B             |  |

|                      | MOV | A, M    | ; delay               |  | LHLD   | TEMP    | ; retrieve HL         |  |

|                      | ANI | OF      | ; mask higher 4 bits  |  | RET    |         | ; return              |  |

|                      | OR  | В       | ; pack MSD and MSD-1  |  |        |         |                       |  |

### **ADJUSTMENT AND TESTING**

Adjustment and testing of a single channel A/D is done by monitoring the memory space where the interrupt routine stores the data word. The microprocessor is forced to loop around a section of program with interrupts enabled. As the input voltage of the converter is changed, this data word should also change as the converter updates it. A precision voltage reference is connected to the input of the A/D and incremental voltage steps are applied. The A/D data word should also change according to the voltage steps.

At full-scale input voltage, the data word should be at its maximum value. If not, check the full-scale adjust on the A/D by adjusting it so the OFL bit goes high when the input is exactly 2.000V.

Multichannel systems are more difficult to check. Start by individually checking the full-scale adjustments so the converters overflow at 2.000V. Check the software priority routine by forcing all status bits of the status word high. This corresponds to all converters being ready at the same time, a very unlikely worst-case condition. The microprocessor should respond by outputting the address of all 4 digits of the A/D port with the highest priority along with the memR strobes, then with a memW strobe to start a new conversion. The next highest priority converter should then receive its addresses and memR strobes and so on down the line.

Once the priority routine has been debugged, each data word is monitored as the input to its converter is adjusted. Since a common input routine is used, once 1 channel operates, all the other channels should also.

Debugging may most easily be done by single stepping through the program at these critical areas. No timing problems should be encountered since the A/D port appears to be a standard peripheral or memory. In the ADC3511 and ADC3711 the desired output is merely addressed the same as a memory location.

The memory requirements of the interface depends, of course, on the complexity of the system. The single channel converter requires approximately 60 bytes of program storage plus 2 bytes for data storage and 4 peripheral addresses.

The multichannel system requires about 40 bytes for the priority routine and 10 bytes of program for each converter routine. The common input routine requires about 50 bytes of program and is used by all the converter routines in the form of a subroutine.

Memory mapped I/O causes 64 memory locations to be used to input an 8-channel system. The data space is located directly above the address space for the converters and 16 memory locations are used to store the data for 8 converters.

### CONCLUSION

The ADC3511 and ADC3711 microprocessor compatible A/D converters eliminate the difficulties previously encountered in applying DPM chips to microprocessor systems. The low parts count and low cost per channel make distributed or remote A/D conversion practical for a variety of data acquisition applications.

### APPENDIX A

### THEORY OF OPERATION

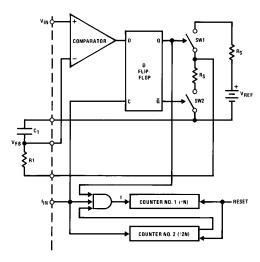

A schematic for the analog loop is shown in Figure A1. The output of SW 1 is either at  $V_{REF}$  or 0V, depending on the state of the D flip-flop. If Q is at a high level,  $V_{OUT}=V_{REF}$  and if Q is at a low level  $V_{OUT}=0$ V. This voltage is then applied to the low pass filter comprised of R1 and C1. The output of this filter,  $V_{FB}$ , is connected to the negative input of the comparator, where it is compared to the analog input voltage,  $V_{IN}$ . The output of the comparator is connected to the D input of the D flip-flop. Information is then transferred from the D input to the Q and  $\overline{\rm Q}$  outputs on the positive edge of clock. This loop forms an oscillator whose duty cycle is precisely related to the analog input voltage  $V_{IN}$ .

An example will demonstrate this relationship. Assume the input voltage is equal to 0.500V. If the Q output of the D flipflop is high, then  $V_{\rm OUT}$  will equal  $_{\rm REF}$  (2.000V) and VFg will charge toward 2V with a time constant equal to R1C1. At some time VFg will exceed 0.500V and the comparator output will switch to 0V. At the next clock rising edge, the Q output of the D flip-flop will switch to ground, causing VOUT to switch to 0V. At this time, VFg will start discharging toward 0V with a time constant R1C1. When VFg is less than 0.5V, the comparator output will switch high. On the rising edge of the next clock, the Q output of the D flip-flop will switch high and the process will repeat. There exists at the output of SW 1 a square wave pulse train with positive amplitude  $V_{\rm REF}$  and negative amplitude 0V.

The DC value of this pulse train is:

$$V_{OUT}\!=\!V_{REF}\frac{t_{ON}}{t_{ON}\!+\!t_{OFF}}\!=\!V_{REF} \text{ (duty cycle)}$$

The low pass filter will pass the DC value and then:

Since the closed loop system will always force  $V_{\text{FB}}$  to equal  $V_{\text{IN}}$ , we can then say that:

or

$$\frac{V_{IN}}{V_{REF}} = \text{(duty cycle)}$$

The duty cycle is logically ANDed with the input frequency  $f_{\text{IN}}$ . The resultant frequency f equals:

$$f = (duty cycle) \times (f_{IN})$$

Frequency f is accumulated by counter no. 1 for a time determined by counter no. 2. The count contained in counter no. 1 is then:

$$count = \frac{f}{(f_{IN})/N} = \frac{(duty \ cycle) \times (f_{IN})}{(f_{IN})/N} = \frac{V_{IN}}{V_{REF}} \times N$$

For the ADC3511 N = 2000.

For the ADC3711 N = 4000.

$$V_{IN} = V_{FB} = V_{REF} \times \text{(duty cycle)}$$

$f = \text{(duty cycle)} \times f_{IN}$

$$\text{Count in Counter No. 1} = \frac{f}{f_{\text{IN}}/N} = \frac{(\text{duty cycle}) \times f_{\text{IN}}}{f_{\text{IN}}/N} = \frac{V_{\text{IN}}}{V_{\text{REF}}} \times N$$

FIGURE A1. Analog Loop Schematic Pulse Modulation A/D Converter

### **Electrical Characteristics**

ADC3511CC, ADC3711CC 4.75  $\leq$  VCC  $\leq$  5.25V;  $-40^{\circ}\text{C} \leq$  TA+85°C, f=5 conv./sec (ADC3511CC): 2.5 conv./sec (ADC3711CC); unless otherwise specified.

| Parameter             |                      | Conditions                                                                                          | Min   | Typ<br>(Note 2) | Max  | Units           |

|-----------------------|----------------------|-----------------------------------------------------------------------------------------------------|-------|-----------------|------|-----------------|

|                       | Non-Linearity        | (Note 3) $V_{\text{IN}} = 0 - 2\text{V Full-Scale}$ $V_{\text{IN}} = 0 - 200 \text{ mV Full-Scale}$ | -0.05 | +0.025          | 0.05 | % of Full-Scale |

|                       | Organization Error   |                                                                                                     | -1    |                 | 0    | Counts          |

|                       | Offset Error         | V <sub>IN</sub> = 0V, (Note 4)                                                                      | -0.5  | 1.0             | 3.0  | mV              |

|                       | Rollover Error       |                                                                                                     | -0    | ·               | 0    | Counts          |

| $V_{IN}+$ , $V_{IN}-$ | Analog Input Current | T <sub>A</sub> =25°C                                                                                | -5    | 1               | 5    | nA              |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: All typicals are given for  $T_A = 25^{\circ}C$ .

Note 3: For the ADC3511CC: full-scale = 1999 counts; therefore, 0.025% of full-scale = ½ counts and 0.05% of full-scale = 1 count. For the ADC3711CCL: full-scale = 3999 counts; therefore, 0.025% of full-scale = 2 counts.

Note 4: For full-scale = 2.000V: 1 mV = 1 count for the ADC3511CC; 1 mV = 2 counts for the ADC3711CC.

FIGURE A2. ADC3511  $3\frac{1}{2}$ -Digit A/D (\*ADC3711  $3\frac{3}{4}$ -Digit A/D) Block Diagram

# CMOS A/D Converter Chips Easily Interface to 8080A Microprocessor Systems

# **AN-200**

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor**

Europe Fax: (+49) 0-180-530 85 86 Fax: (+49) 0-180-530 8b so Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 8 8 80 Italiano Tel: (+49) 0-180-534 16 80

**National Semiconductor** National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408