# LM3641 Application Information Guide

National Semiconductor Application Note 1067 Greg J Smith Luc Van de Perre January 1997

#### INTRODUCTION

The LM3641 Lithium Protection Integrated Circuit resides inside a 3.6V Lithium-Ion battery pack consisting of a single cell or multiple parallel cells. The IC controls the ON/OFF state of a pair of low threshold N-channel power MOSFETs placed in series with the battery cell(s). The purpose of this MOSFET pair is to protect the cell(s) from inadvertent electrical over-stress. The IC compares the cell voltage against internally programmed minimum and maximum limits.

The IC also monitors the bi-directional current flow in the battery pack by measuring the voltage across a robust 4 m $\Omega$  current sensing resistor internal to the protection IC package. The IC turns OFF the MOSFET pair whenever any fault limit is exceeded. The limits for overcharge and overdischarge voltage, as well as independent limits for each direction of overcurrent are factory adjusted employing EEPROM. A Control pin allows external ON/OFF control of the MOS-

FET pair and resets the IC after the MOSFET pair is turned

off and the pack is safe to operate again.

In this application note, there will be a description of the Low Cell Charge Enable (LCCE) feature and the Active Rectification (AR) feature.

#### LOW CELL CHARGE ENABLE FEATURE

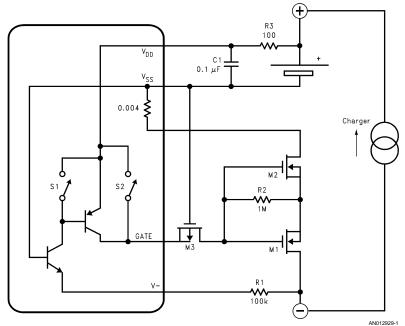

Low Cell Charge Enable (LCCE) is a passive method of enabling the cell to be charged when the cell voltage is too low to keep the active IC circuitry operational. The circuit in Figure 1 illustrates the effective signal path to the GATE pin of the IC resulting from a connection of a charger to the pack. The base of the PNP is pulled low with bias current from the charger through R1 and the NPN. The collector of the PNP pulls high on the GATE pin. When the cell voltage is high enough to power up the rest of the IC, the logic will short the base-emitter of the PNP with switch, S1. This occurs at about 1.4V. The logic is able to determine at this time if a charger is applied to the pack and turn on the normal switches that activate GATE =  $\rm V_{DD}$  drive with switch S2.

FIGURE 1. Low Cell Charge Enable Circuit

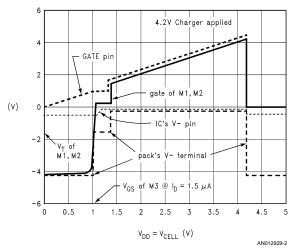

The various PCB voltages related to LCCE operation are shown in *Figure 2*. This plot illustrates the relative value of terminal voltages versus cell voltages that ranges from 0V to greater than  $V_{MAX}$ . The GATE pin of the IC tracks the cell voltage as it increases from 0V, except for a narrow flat region. This flat region occurs between the point that the M3

cascode can conduct and the logic of the IC powers up. The reason for the flat region will be explained. First, notice the gate voltage of the power MOSFETs M1 and M2. These FETs do not turn on until the initial conduction of M3 and also exhibit the flat region of operation. The power FETs' gate voltage equals the cell voltage beyond this region and below

$\rm V_{MAX}.$  Next, the IC's V– pin voltage is seen as being slightly below 0V (V\_{SS}) whenever V\_{CELL} is less than approximately 1.4V. This because the power FETs have not turned on, or fully turned on, the V– pin is pulled below 0V. The V– pin voltage is determined by the V\_BE of the NPN for the bias current allowed by R1. The V– terminal of the pack follows the same track as the V– pin of the IC except during the flat re-

gion. This because during the flat region, the pack's V– terminal is set by the  $\rm V_{GS}$  of the power FET's necessary to conduct the charger's compliance current. The pack's components operate in a feedback loop in the flat region. The PNP drive to the GATE pin can not pull any higher without also pulling the IC's V– pin higher, which would deprive base current to the PNP.

FIGURE 2. FET Drive vs CELL Voltage (Charging)

The cell voltage that allows the power FETs to initially conduct is determined by the threshold voltage of M3. When  $V_{CELL}$  = M3's  $V_{GS(ON)}$  for  $I_D \approx V_{T(M1)}/1$  m $\Omega$ , then the M1 and M2 are able to start conducting. This is also the start of the flat region. In the flat region loop that maintains the PNP in the active region keeps the power FETs on. Finally at  $\approx 1.4 V_{\rm c}$ , the IC's logic will now pull the GATE pin high in open loop mode.

If at any time the charger is removed and the cell voltage is below  $V_{\text{MIN}}$ , then the GATE pin will turn off and the power FETs will not conduct.

## **ACTIVE RECTIFICATION FEATURE**

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas Tel: 1-800-272-9959

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

National Semiconductor Europe

Fax: +49 (0) 1 80-530 85 86 Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85 English Tel: +49 (0) 1 80-532 78 32 Français Tel: +49 (0) 1 80-532 93 58 Italiano Tel: +49 (1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507