## Use of the NS32332 with the NS32082 and the NS32201

National Semiconductor Application Brief 27 Systems Applications Group August 1986

Use of the NS32332 with the NS32082 and the NS32201

Care should be taken when the NS32332 is designed in a system with the NS32201 and the NS32082. Two configurations need to be considered, one with MMU and one without.

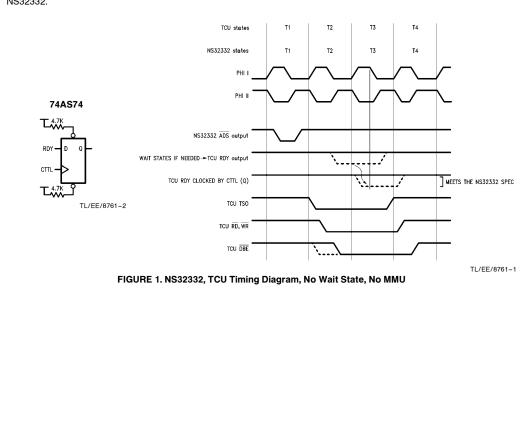

In a configuration without an MMU, TCU and CPU both run a four clock cycle bus (Figure 1). The RDY signal is the only incompatible signal between the CPU and TCU and therefore the RDY output of the TCU should not be directly connected to the RDY input of the NS32332. The NS32332 samples its RDY input in the middle of T3 while the NS32201 asserts its RDY output shortly after the middle of T2 and removes it shortly after the middle of T3, thus the NS32332 RDY input hold time (tRDYh) is not met. To meet tRDYh, the RDY output of the NS32201 should be clocked by the rising edge of the CTTL using a D-type flip-flop (74AS74) and then taken to the NS32332. It should be noted that the NS32332 outputs the data in a write cycle in T3 unless DT/SDONE pin is sampled low on the rising edge of the reset in which case the data is output during T2. The DT/SDONE pin is implemented as of revision B of the NS32332.

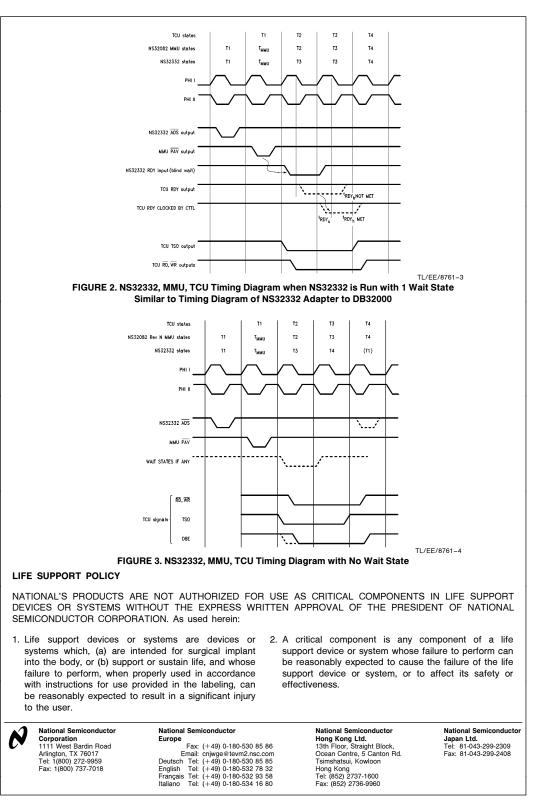

In a configuration with MMU the NS32332 runs a four clock cycle bus while the NS32082 runs a five cycle bus. Two options can be exercised.

The first option is extending the NS32332 bus cycle to five clocks by adding a blind wait state that bypasses the NS32201 (*Figure 2*). This configuration generally requires the minimum hardware modification for a 320xx based design to run the NS32332. Here the NS32201 output signals can be used to interface the NS32332 and the NS32082 to the memory or I/O. Additional wait states can be inserted by clocking the RDY output of the TCU.

The second option is to have the NS32332 run a four clock cycle bus (*Figure 3*). In this configuration the NS32201 output signals cannot be used to interface the NS32332 to memory or I/O; they can only be used to interface the NS32082 to the memory. In this configuration a revision N of the NS32082 should be used.

©1995 National Semiconductor Corporation TL/EE/8761

RRD-B30M105/Printed in U. S. A

AB-2

Use of the NS32332 with the NS32082 and the NS32201

**AB-27**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.