### 256Kx32 SGRAM

## **Preliminary Information**

### **Features**

- SGRAM protocol

- High bandwidth 100MHz-166MHz operation

- Reduced Latency

- Improved critical timing parameter limits

- 2 Internal Banks for hiding Row Precharge

- Independent byte operation via DQM[3:0]

- Burst length 1,2,4,8 and full page

- Burst Type: Linear, Wrap

- Capacity: 8Mb

- Organization: 256Kx32 (8Mbit)

- Refresh Interval 15.6uSec

- CBR Refresh.

- LVTTL Interface

- Supply voltages 3.3 V ± 0.3V

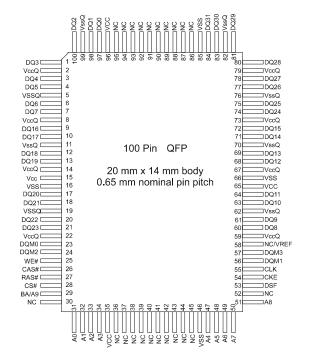

- Package 100-pin QFP

### Overview

The MoSYs SGRAM is a synchronous memory for graphics, multimedia, networking and other applications. It implements SGRAM commands and offers shorter Precharge ( $t_{RP}$ ), faster Access Latency ( $t_{RC}$ ,  $t_{RAS}$ ,  $t_{RCD}$  and CL=2) and better pipelining capability. In addition to the SGRAM command set, the MoSYs SGRAM implements an eight column Block Write function and a Masked Write (Write Per Bit) function to accommodate graphics applications.

### **Options**

MoSys SGRAM supports the following device options

| Option           | Marking |

|------------------|---------|

| 6.0ns Cycle Time | -6      |

| 6.6ns Cycle Time | -6R6    |

| 7.5ns Cycle Time | -7R5    |

| 8ns Cycle Time   | -8      |

| 10ns Cycle Time  | -10     |

### **Part Number Designation**

Example: MG802C256QR -8

Device Designation: MG8, Series: 02C

Organization: 256Kx32

Package Type: Q = PQFP, L = LQFPPinout: R = Reverse (Mirror Image)

Speed: -8=125MHz

## Key Timing Parameters

| Speed<br>Grade | Clock<br>Frequency<br>(MHz) | Access<br>Time<br>(ns) | Setup<br>Time<br>(ns) | Hold<br>Time<br>(ns) | CAS<br>Latency<br>(CL) | RAS Access<br>Time - tRAS<br>(ns) | Cycle Time -<br>tRC<br>(ns) |

|----------------|-----------------------------|------------------------|-----------------------|----------------------|------------------------|-----------------------------------|-----------------------------|

| -6             | ≤ 166                       | 5                      | 2                     | 1                    | 3                      | 24                                | 42                          |

| -6R6           | ≤ 150                       | 5                      | 2                     | 1                    | 3                      | 26.4                              | 46.2                        |

| -7R5           | ≤ 133                       | 6                      | 2.2                   | 1                    | 3                      | 30                                | 53                          |

| -8             | ≤ 125                       | 6                      | 2.3                   | 1                    | 2                      | 24                                | 40                          |

| -10            | ≤ 100                       | 7                      | 2.5                   | 1                    | 2                      | 30                                | 50                          |

256Kx32 SGRAM

# **Preliminary Information**

## **Functional Description**

## Pin Description

| Pin      | Pin Number      | Pin   | I/O | Description                                                                                                       |

|----------|-----------------|-------|-----|-------------------------------------------------------------------------------------------------------------------|

| Name     |                 | Total |     |                                                                                                                   |

| CLK      | 55              | 1     | 1   | System Clock: All inputs are sampled on positive edge.                                                            |

| CS#      | 28              | 1     | 1   | Chip select: Disables or enables the device operation by                                                          |

|          |                 |       |     | masking or enabling all inputs except CLK, CKE and DQM.                                                           |

| CKE      | 54              | 1     | 1   | Clock Enable: CKE controls the Power Down Mode in                                                                 |

|          |                 |       |     | MoSys SGRAM. When in Power Down Mode all input and                                                                |

| 110.01   |                 |       |     | output buffers are de-activated.                                                                                  |

| A[8:0]   | 51-47, 34-31    | 10    |     | <b>Address Inputs:</b> Row & Column address are multiplexed on the same pins.                                     |

| RAS#     | 27              | 1     | 1   | <b>Row Address Strobe:</b> Latches Row address on the positive                                                    |

| INAS#    | 21              | '     | '   | edge of clock with RAS# low. Enables Row access.                                                                  |

| CAS#     | 26              | 1     | I   | Column Address Strobe: Latches Column Address on the                                                              |

|          |                 |       |     | positive edge of clock. Enables column access.                                                                    |

| WE#      | 25              | 1     |     | Write Enable: Enables write operation.                                                                            |

| DSF      | 53              | 1     | 1   | <b>DSF:</b> Enables the Write Per Bit and Block Write function.                                                   |

|          |                 |       |     | This pin has an internal pull-down resistor.                                                                      |

| DQM[3:0] | 57, 24, 56, 23  | 4     | I   | Data Input/Output Mask: Write data byte mask, Read                                                                |

|          |                 |       |     | output byte enables. Read latency is two cycle from DQM                                                           |

|          |                 |       |     | and zero cycle for write. The DQM masking occurs two                                                              |

|          |                 |       |     | cycles later in the Read operation and in the same cycle during Write operation. DQM is synchronous to the clock, |

|          |                 |       |     | thus the masking occurs for the whole clock.                                                                      |

| DQ[31:0] | 84, 83, 81, 80, | 32    | I/O | Data Input/Output: Bidirectional data bus.                                                                        |

| DQ[31.0] | 78, 77, 75, 74, | 32    | 1/0 | Data Input/Output: Biuli ectional data bus.                                                                       |

|          | 1, 20, 18, 17,  |       |     |                                                                                                                   |

|          | 13, 12, 10, 9,  |       |     |                                                                                                                   |

|          | 72, 71, 69, 68, |       |     |                                                                                                                   |

|          | 64, 63, 61, 60, |       |     |                                                                                                                   |

|          | 7, 6, 4, 3, 1,  |       |     |                                                                                                                   |

|          | 100, 98, 97     |       |     |                                                                                                                   |

| ВА       | 29              | Input | I   | Bank Address 0: Bank Address defines to which Bank the                                                            |

|          |                 |       |     | Activate, Read, Write or Precharge Command is issued.                                                             |

|          |                 |       |     | BA0 is also used to program the 10 <sup>th</sup> bit of the Mode                                                  |

|          |                 |       |     | Register.                                                                                                         |

### Signal description for 256Kx32 MoSys SGRAM

| Parameter      |        |

|----------------|--------|

| Bank Address   | BA     |

| Row Address    | A[8:0] |

| Column Address | A[7:0] |

| Auto Precharge | A8     |

| Page Size      | 256x32 |

Bank, Row and Column Address mapping

256Kx32 SGRAM

## **Preliminary Information**

### **CONTROL REGISTERS**

Mosys SGRAM incorporates four programmable registers, the Mode Select Register (MSR), Special Mode Register (SMR), Color Register (CR) and the Mask Register (MR). This section describes the use of these registers. In describing the functionality, the following terms are used.

WO Write Only. A register bit with this attribute is Write Only.R Reserved. A register bit with this attribute is Reserved.

### Mode Register (MSR)

MoSys SGRAM's mode register is accessed through the Mode Register Write Command (op code '00000'). Mode Register is used to load the value of CAS Latency and Burst Length of MoSys SGRAM.

| Bit | Default | Attribute | Description     |           |                    |               |

|-----|---------|-----------|-----------------|-----------|--------------------|---------------|

| 8:7 | 00      | WO        | Reserved:       |           |                    |               |

|     |         |           |                 |           |                    |               |

|     |         |           |                 | 00        | Standard operation |               |

|     |         |           |                 | 00        | Reserved (for Mo   |               |

|     |         |           |                 | 01        | Reserved (for Mo   | 3,            |

|     |         |           |                 | 01        | Reserved (for Mo   | Sys Use only) |

| 6:4 | 011     | WO        | CAS Latency:    |           |                    |               |

|     |         |           |                 | 000       | Reserved           |               |

|     |         |           |                 | 001       | Reserved           |               |

|     |         |           |                 | 010       | 2                  |               |

|     |         |           |                 | 011       | 3                  |               |

|     |         |           |                 | 100       | 4                  |               |

|     |         |           |                 | 101       | Reserved           |               |

|     |         |           |                 | 110       | Reserved           |               |

|     |         |           |                 | 111       | Reserved           |               |

| 3   | 0       | WO        | Burst Type: 0=L | _inear Βι | urst Mode, 1=Wrap  | Mode          |

| 2:0 | 010     | WO        | Burst Length:   |           | BT=0               | <u>BT=1</u>   |

|     |         |           |                 | 000       | 1                  | 1             |

|     |         |           |                 | 001       | 2                  | 2             |

|     |         |           |                 | 010       | 4                  | 4             |

|     |         |           |                 | 011       | 8                  | 8             |

|     |         |           |                 | 100       | Reserved           | Reserved      |

|     |         |           |                 | 101       | Reserved           | Reserved      |

|     |         |           |                 | 110       | Reserved           | Reserved      |

|     |         |           |                 | 111       | Full Page          | Reserved      |

Description of Mode Register

256Kx32 SGRAM

## **Preliminary Information**

### Special Mode Register (SMR)

MoSys SGRAM's Special Mode Register is accessed through the Mode Register Read/Write Command (op code '00001'). Special Mode Register is used to load data into the Color Register or the Mask register. During the execution of the Special Mode Register Command Bits A[6:5] are used to determine if a new value is to be loaded into the Color and Mask Registers.

| Bit         | Default | Attribute | Description                                                      |  |  |  |  |

|-------------|---------|-----------|------------------------------------------------------------------|--|--|--|--|

| BA0, A[8:7] | 000     | WO        | Reserved: For Standard operation these bits should always b      |  |  |  |  |

|             |         |           | "000".                                                           |  |  |  |  |

| A[6]        | 0       | WO        | Color Register: 0=Leave data unchanged for Color Register,       |  |  |  |  |

|             |         |           | 1=Load new data into Color Register.                             |  |  |  |  |

| A[5]        | 0       | WO        | Mask Register: 0=Leave data unchanged for Mask Register,         |  |  |  |  |

|             |         |           | 1=Load new data into Mask Register.                              |  |  |  |  |

| A[4:0]      | 0000    | WO        | <b>Reserved:</b> For Standard operation these bits should always |  |  |  |  |

|             |         |           | be "0000".                                                       |  |  |  |  |

Description of Special Mode Register

### Color Register (CR)

Data is loaded into the Color Register through the Special Mode Register Write Command. During the execution of the Special Mode Register Command, bit A[6] is used to determine if a new value is to be loaded into the Mask Registers. If A[6] =1 during the Special Mode Register Command then the value on DQ[31:0] is loaded into the Color Register. The Color Register supplies data for the Block Write Command.

| E  | Bit  | Default   | Attribute | Description                                                 |

|----|------|-----------|-----------|-------------------------------------------------------------|

| () | 31:0 | 00000000h | WO        | Color Register Data: Data from these bits is used for Block |

|    |      |           |           | Write Command.                                              |

#### Description of Color Register

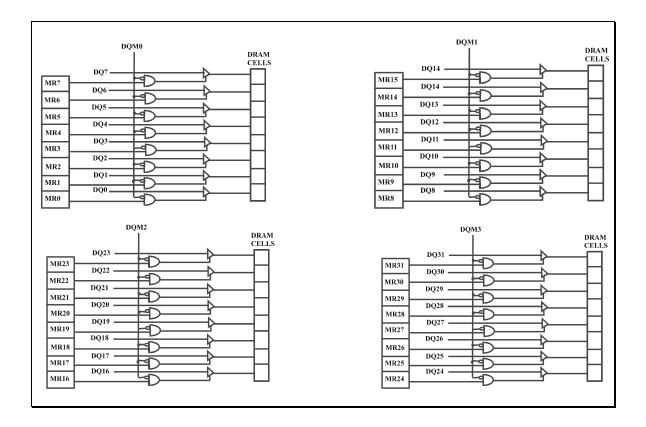

### Mask Register (MR)

Data is loaded into the Mask Register through the Special Mode Register Write Command. During the execution of the Special Mode Register Command, bit A[5] is used to determine if a new value is to be loaded into the Mask Registers. If A[5] =1 during the Special Mode Register Command then the value on DQ[31:0] is loaded into the Mask Register. The Mask Register is used for Mask Per Bit functionality during the Masked Write of Masked Block Write Command. Mask Per Bit is used in conjunction with the DQM[3:0] to determine the mask for each bit.

| Bit  | Default   | Attribute | Description                                                 |

|------|-----------|-----------|-------------------------------------------------------------|

| 31:0 | 00000000h | WO        | Mask Register Data: Data from these bits is used for Masked |

|      |           |           | Write and Block Write Command.                              |

Description of Mask Register

256Kx32 SGRAM

## **Preliminary Information**

### **DEVICE OPERATION**

This section provides a description of MoSys SGRAM device.

#### **Device Function**

The following command table lists all supported MoSYS SGRAM commands. All fixed length burst (non full page burst length) operations can be self terminated, terminated by BST, interrupted by another Read or Write operation or by a Precharge operation to the same Bank. For Auto Precharge Read or Write, the operation cannot be interrupted and has to self-terminate after the programmed burst length. Auto Precharge has no effect for a full page burst length operation. To provide backward compatibility with SDRAM command set, the MoSYS SGRAM incorporates an internal pull-down resistor for the DSF pin.

### Mode Register Write

The Mode Register stores data for controlling various functions of MoSYs SGRAM. Through the mode register the CAS Latency, Burst Type, Burst Length and the PLL enable mode can be programmed for the device. The default value of the Mode Register is defined as CAS Latency of 3, Burst Type of linear and Burst Length of 4. The Mode Register is written to by driving CS#, RAS#, CAS#, WE# and DSF low.

### Special Mode Register Write

The Special Mode Register controls the data written to Color or Mask Register of MoSYS SGRAM. During the Special Mode Register Command A[6:5] are used to indicate to the MoSYS SGRAM whether a new data pattern is to be written to Color or Mask Registers. The Special Mode Register is written to by driving CS#, RAS#, CAS#, WE# and DSF high.

#### Bank Activate

The Bank Activate Command selects a Row in a Bank. Bank is activated by driving CS# low, RAS# low, CAS# high, WE# high and DSF low with the correct Bank and Row specified on BA and A[8:0]. The Read/Write Command can follow the Activate Command after the  $t_{\tiny RCD}$  timing has been met. Every Bank Activate Command must satisfy the minimum  $t_{\tiny RAS}$  before a Precharge Command can be issued to that Bank.

### Activate with WPB

The Bank Activate with WPB Command selects a random Row in an idle Bank. Bank is activated by driving CS# low, RAS# low, CAS# high, WE# high and DSF high with the correct Bank and Row specified on A[10/9:0]. The Write or Block Write Command can follow the Activate Command after the  $t_{\tiny RCD}$  timing has been met. A Write Command to the selected Bank will be masked according to the contents of the Mask Register and DQM[3:0]. A Block Write Command following the Activate with WPB Command will be masked according to the contents of the Mask Register, DQM[3:0] and the Column/Byte Mask information on the DQ[31:0] pins.

### Read

The Read Command is used to access data from an active Row and Bank within the device. The Read Command is issued by driving CS# low, RAS# high, CAS# low, WE# high and A8 low (no

256Kx32 SGRAM

## **Preliminary Information**

Auto Precharge). The Bank must have been active for at least the minimum  $t_{\mbox{\tiny RCD}}$  before the Read Command is issued. The first data appears on the output in CAS Latency (number of Clocks) after the Read Command is issued. Upon completion of the burst Read access (assuming that no new command is pipelined after the existing Read Command) the DQ[31:0] will go to high Z state. A fixed length Burst Read (1,2,4 or 8) can be either terminated by another Read, Write (for a Read interrupted by Write Command the DQMs should be used control to prevent data contention of the DQ pins), Precharge Command to the same Bank or a Burst Stop Command .

A Full Page Burst Read can be interrupted by a Burst Stop Command (BST) or a Precharge Command to the same Bank. A Full Page Burst is used in conjunction with the BST Command to generate an arbitrary burst length. A Full Page Burst is not self-terminating; the address wraps around after the last address in the page.

Read with Auto Precharge is issued by driving CS# low, RAS# high, CAS# low, WE# high and A8 high. The Bank must have been active for at least the minimum  $t_{\tiny RCD}$  before the Read with Auto Precharge Command is issued. The first data appears on the output in CAS Latency (number of Clocks) after the Read Command is issued. The accessed Bank is automatically Precharged after the Read Command (after providing the burst read data as specified by the burst length field in the Mode Register). For Burst Length of 1,2,4 and 8 the Precharge is carried out one clock after the Column Address is latched and is independent of the CAS latency. For a full page burst, Read with Auto Precharge has no effect (no Precharge is carried out after the full page burst read access).

Read with Auto Precharge cannot be terminated by another command. Read with Auto Precharge is self terminated after the read data is provided for the fixed length burst Read.

### Write

The Write Command is used to write data to an active Row and Bank within the device. The Write Command is issued by driving CS# low, RAS# high, CAS# low, WE# low and A8 low. The Bank must have been active for at least the minimum  $t_{\tiny RCD}$  before the Write Command is issued. The write latency of the device is 0.

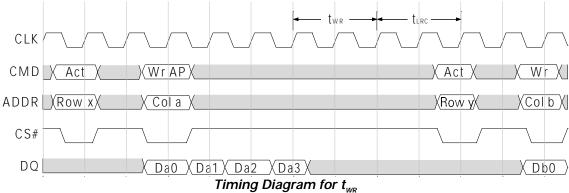

Write with Auto Precharge is issued by driving CS# low, RAS# high, CAS# low, WE# low and A8 high. The Bank must have been active for at least the minimum  $t_{\text{RCD}}$  before the Write with Auto Precharge Command is issued. The accessed Bank is automatically Precharged after the Write Command. Auto Precharge is carried out, starting two clocks ( $t_{\text{WR}}$ ) after the last data is sampled. The Precharged Bank can be activated after  $t_{\text{RP}}$  has been met.

256Kx32 SGRAM

## **Preliminary Information**

#### Masked Write

Any Write Command to a Row that was opened (activated) using an Activate with WPB Command is a Masked Write Command. Data is written to the Column Address subject to the Mask Write information in the Mask Register. If a particular bit in the Mask Register is '0' then the data on the corresponding DQ pin will be ignored (masked) and the existing data in that particular DRAM cell will be unchanged. If a particular bit in the Mask Register is '1' then the data on the corresponding DQ pin, based on the value of DQM[3:0] signals, will be written to the particular DRAM cell. For a Masked Write operation the overall Write Mask consists of the DQM[3:0] information (which specify the Write Mask Per Byte) and the MR[31:0] information (which specify the Write Per Bit Mask). A particular bit is written only if the corresponding DQM is low ('0') and the corresponding MR[x] is high ('1').

256Kx32 SGRAM

## **Preliminary Information**

#### Block Write

The Block Write Command is used to Write a block of data to an active Row and Bank within the device. The Block Write Command is issued by driving CS# low, RAS# high, CAS# low, WE# low and DSF high. A Block Write Command is a non-burst Write Command that writes data to eight columns simultaneously. The data value contained in the Color Register (CR) is written to eight consecutive column locations addressed by A[7:3]. When the Block Write Command is executed, the value on DQ[31:0] pins is used to mask the particular column and byte within the 8 column block. For example DQ0 controls byte 0 for address '000' (within the eighth column block), DQ8 controls byte 1 for address '000', DQ16 controls byte 2 for address '000' and DQ24 controls byte 3 for address '000'.

When a '0' is sampled on a particular DQ with the Block Write Command the corresponding column and byte combination is masked. When a '1' is sampled the Color Register data will be written to the corresponding locations (based on the value of DQM and MR[31:0] bits). The following Table specifies the column and byte combination controlled by each DQ.

| DQ Input | Column | Address Contro | olled | Address Controlled | Byte Controlled |  |

|----------|--------|----------------|-------|--------------------|-----------------|--|

| _        | A2     | A1             | A0    |                    |                 |  |

| DQ0      | 0      | 0              | 0     | 0h                 | Byte 0          |  |

| DQ1      | 0      | 0              | 1     | 1h                 | Byte 0          |  |

| DQ2      | 0      | 1              | 0     | 2h                 | Byte 0          |  |

| DQ3      | 0      | 1              | 1     | 3h                 | Byte 0          |  |

| DQ4      | 1      | 0              | 0     | 4h                 | Byte 0          |  |

| DQ5      | 1      | 0              | 1     | 5h                 | Byte 0          |  |

| DQ6      | 1      | 1              | 0     | 6h                 | Byte 0          |  |

| DQ7      | 1      | 1              | 1     | 7h                 | Byte 0          |  |

| DQ8      | 0      | 0              | 0     | 0h                 | Byte 1          |  |

| DQ9      | 0      | 0              | 1     | 1h                 | Byte 1          |  |

| DQ10     | 0      | 1              | 0     | 2h                 | Byte 1          |  |

| DQ11     | 0      | 1              | 1     | 3h                 | Byte 1          |  |

| DQ12     | 1      | 0              | 0     | 4h                 | Byte 1          |  |

| DQ13     | 1      | 0              | 1     | 5h                 | Byte 1          |  |

| DQ14     | 1      | 1              | 0     | 6h                 | Byte 1          |  |

| DQ15     | 1      | 1              | 1     | 7h                 | Byte 1          |  |

| DQ16     | 0      | 0              | 0     | 0h                 | Byte 2          |  |

| DQ17     | 0      | 0              | 1     | 1h                 | Byte 2          |  |

| DQ18     | 0      | 1              | 0     | 2h                 | Byte 2          |  |

| DQ19     | 0      | 1              | 1     | 3h                 | Byte 2          |  |

| DQ20     | 1      | 0              | 0     | 4h                 | Byte 2          |  |

| DQ21     | 1      | 0              | 1     | 5h                 | Byte 2          |  |

| DQ22     | 1      | 1              | 0     | 6h                 | Byte 2          |  |

| DQ23     | 1      | 1              | 1     | 7h                 | Byte 2          |  |

| DQ24     | 0      | 0              | 0     | 0h                 | Byte 3          |  |

| DQ25     | 0      | 0              | 1     | 1h                 | Byte 3          |  |

| DQ26     | 0      | 1              | 0     | 2h                 | Byte 3          |  |

| DQ27     | 0      | 1              | 1     | 3h                 | Byte 3          |  |

| DQ28     | 1      | 0              | 0     | 4h                 | Byte 3          |  |

| DQ29     | 1      | 0              | 1     | 5h                 | Byte 3          |  |

| DQ30     | 1      | 1              | 0     | 6h                 | Byte 3          |  |

| DQ31     | 1      | 1              | 1     | 7h                 | Byte 3          |  |

Mapping of DQ[31:0] to column and byte location within the block

256Kx32 SGRAM

## **Preliminary Information**

The overall mask for a Block Write Command consists of DQM[3:0], MR[31:0] and the DQ[31:0] information provided with the Block Write Command.

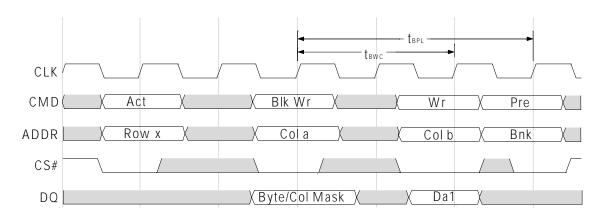

A Block Write access requires a minimum time of  $t_{\text{WBC}}$  to execute. No new commands can be executed until  $t_{\text{WBC}}$  is met, except for the Activate and Precharge Commands to the second Bank.

### **DQM** Operation

DQM is used to mask Read and Write operations. Read latency is two cycles from DQM and zero cycles for write. The DQM masking occurs two cycles later in the Read operation and in the same cycle during Write operation. DQM is synchronous to the clock.

### Precharge

The Precharge Command is issued by driving CS# low, RAS# low, CAS# high, WE# low, Valid Bank Address and A8. If A8 is low during the assertion of the Precharge Command, then the Bank specified by the Bank address is Precharged. If A8 is high during the assertion of the Precharge Command, then both Banks are Precharged. For a Precharge Command the minimum value of  $t_{\rm RP}$  should be satisfied before a new command is issued. After Precharge the Bank goes into the idle state.

#### **CBR Refresh**

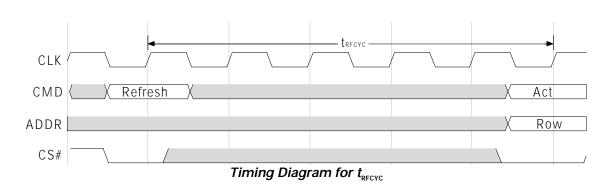

The CBR Refresh Command is issued by driving CS# low, RAS# low, CAS# low and WE# high. Before executing the CBR Refresh Command all Banks should be Precharged. The internal counter increments internally on the CBR Refresh Command. The time required to complete the refresh cycle is specified by  $t_{\rm RC}$  (min). The CBR Refresh should be performed at least every 15.6 usec, since the device does not do self refresh in the Power Down Mode.

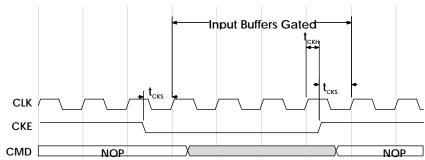

#### Device Power Down

The device power down for MoSys SGRAM can be entered when both Banks are in idle state (Precharged) and CKE is asserted low. In device power down all input and output buffers are deactivated (except for CKE). If the device stays in the Power Down Mode for more than 15.6 usec (refresh interval), then the MoSys SGRAM will lose data.

The device power down can be terminated by driving CKE high again. CKE assertion and deassertion should meet the CKE setup and hold time ( $t_{cks}$  and  $t_{ckh}$ ).

Timing Diagram for Power Down Mode

### Power on Condition

The MoSys SGRAM device generates power-on reset at power up. The internal power-on reset sets all the internal mode register values to the default state.

256Kx32 SGRAM

# **Preliminary Information**

## **Command Table**

| Operation              | Cmd       | Command |   |   |   |   | BA, A[8:0] |   |                                       |

|------------------------|-----------|---------|---|---|---|---|------------|---|---------------------------------------|

|                        |           | С       | R | С | W | D | D          | Α |                                       |

|                        |           | S       | Α | Α | Ε | S | Q          | 8 |                                       |

|                        |           | #       | S | S | # | F | М          |   |                                       |

|                        |           |         | # | # |   |   |            |   |                                       |

| Mode Register Write    | MSR Wr    | 0       | 0 | 0 | 0 | 0 | Х          | V | BA, A[8:0] carry data for MSR.        |

| Special Mode Register  | SMR Wr    | 0       | 0 | 0 | 0 | 1 | Х          | V | BA, A[8:0] carry data for SMR,        |

| Write                  |           |         |   |   |   |   |            |   | DQ[31:0] carry the data for           |

|                        |           |         |   |   |   |   |            |   | Color or Mask Register.               |

| CBR Refresh            | Ref       | 0       | 0 | 0 | 1 | 0 | Х          | Χ | X                                     |

| Activate (Single Bank) | Act       | 0       | 0 | 1 | 1 | 0 | Х          | V | BA, A[8:0] carry the Bank and         |

|                        |           |         |   |   |   |   |            |   | Row Address.                          |

| Activate with WPB      | Act       | 0       | 0 | 1 | 1 | 1 | Х          | V | BA, A[8:0] carry the Bank and         |

| (Single Bank)          | 147       |         |   |   |   |   |            |   | Row Address.                          |

| Write                  | Wr        | 0       | 1 | 0 | 0 | 0 | V          | 0 | BA carries the Bank Address           |

|                        |           |         |   |   |   |   |            |   | and A[7:0] carry the Column           |

| Dia ali Marita         | DII. M/n  | 0       | 1 | 0 | 0 | 1 |            | 0 | Address.  BA carries the Bank Address |

| Block Write            | Blk Wr    | 0       | ' | 0 | U | ı | V          | 0 | and A[7:0] carry the Column           |

|                        |           |         |   |   |   |   |            |   | Address.                              |

| Write with Auto        | Wr AP     | 0       | 1 | 0 | 0 | 0 | V          | 1 | BA carries the Bank Address           |

| Precharge              | *** / *** |         | ' |   |   | O | V          | ' | and A[7:0] carry the Column           |

| , realise              |           |         |   |   |   |   |            |   | Address.                              |

| Read                   | Rd        | 0       | 1 | 0 | 1 | 0 | V          | 0 | BA carries the Bank Address           |

|                        |           |         |   |   |   |   |            |   | and A[7:0] carry the Column           |

|                        |           |         |   |   |   |   |            |   | Address.                              |

| Read with Auto         | Rd AP     | 0       | 1 | 0 | 1 | 0 | V          | 1 | BA carries the Bank Address           |

| Precharge              |           |         |   |   |   |   |            |   | and A[7:0] carry the Column           |

|                        |           |         |   |   |   |   |            |   | Address.                              |

| Burst Stop             | BST       | 0       | 1 | 1 | 0 | 0 | Х          | Х | X                                     |

| Precharge Single Bank  | Pre       | 0       | 0 | 1 | 0 | 0 | Х          | 0 | BA carry the Bank Address.            |

| Precharge All Banks    | Pre ALL   | 0       | 0 | 1 | 0 | 0 | Χ          | 1 | X                                     |

| No Operation           | NOP       | 0       | 1 | 1 | 1 | 0 | Х          | Х | X                                     |

| No Operation           | NOP       | 1       | Χ | Χ | Х | Χ | Χ          | Χ | X                                     |

MoSys SGRAM Command Table

256Kx32 SGRAM

# **Preliminary Information**

## **Electrical Characteristics**

## **DC Specifications**

| Symbol           | Parameter                                 | Min | Max | Units | Notes |

|------------------|-------------------------------------------|-----|-----|-------|-------|

| V <sub>CC</sub>  | Voltage on $V_{CC}$ relative to $V_{SS}$  | -1  | 4.6 | V     | 1     |

| V <sub>CCQ</sub> | Voltage on $V_{CCQ}$ relative to $V_{SS}$ | -1  | 4.6 | V     | 1     |

| Pwr              | Power Dissipation                         |     | 1.6 | W     | 1     |

| Isc              | Short Circuit Current                     |     | 50  | mA    | 1     |

| Tst              | Storage Temperature                       | -55 | 150 | °C    | 1     |

| Та               | Operating Temperature                     | 0   | 70  | °C    | 1     |

### Absolute Maximum Ratings

Note 1: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating and functional operation of the device at these or any other conditions above those indicated in operational sections of this specifications is not implied.

| Symbol           | Parameter                                               | Min  | Тур | Max                   | Units |

|------------------|---------------------------------------------------------|------|-----|-----------------------|-------|

| $V_{CC}$         | Supply Voltage                                          | 3.0  | 3.3 | 3.6                   | V     |

| V <sub>CCQ</sub> | I/O Supply Voltage                                      | 3.0  | 3.3 | 3.6                   | V     |

| V <sub>ih</sub>  | Input High Voltage                                      | 2.0  |     | V <sub>CCQ</sub> + .3 | V     |

| V <sub>il</sub>  | Input Low Voltage                                       | -0.3 |     | 0.8                   | V     |

| l <sub>il</sub>  | Input Leakage Current                                   | -2   |     | +2                    | μΑ    |

|                  | Any luput 0V≤ V <sub>IN</sub> ≤V <sub>CC</sub>          |      |     |                       |       |

|                  | (All other pins not under test =0V)                     |      |     |                       |       |

| l <sub>oz</sub>  | Output Leakage Current                                  | -10  |     | +10                   | μΑ    |

|                  | DQs are disabled;0V≤ V <sub>out</sub> ≤V <sub>ccq</sub> |      |     |                       |       |

| V <sub>oh</sub>  | Output High Voltage @ I <sub>OUT</sub> =8mA             | 2.4  |     |                       | V     |

| V <sub>ol</sub>  | Output Low Voltage @I <sub>OUT</sub> =8mA               |      |     | 0.4                   | V     |

| C <sub>in</sub>  | Input Pin Capacitance                                   | 2    |     | 4                     | pF    |

| C <sub>I/O</sub> | I/O Pin Capacitance                                     | 2    |     | 5                     | pF    |

| C <sub>OUT</sub> | Output Pin Capacitance                                  | 2    |     | 5                     | pF    |

| L <sub>pin</sub> | Pin Inductance                                          |      |     | 10                    | nH    |

| Та               | Ambient Temperature                                     | 0    | 25  | 70                    | °C    |

**DC Operating Requirements**

## 256Kx32 SGRAM

# **Preliminary Information**

| Parameter                                                                                                                                                                                                                                                                                | Symbol           | - 6<br>Max | - 6R6<br>Max | - 7R5<br>Max | - 8<br>Max | -10<br>Max | Units |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|--------------|--------------|------------|------------|-------|

| Standby Current, Power Down Mode CKE $\leq$ V <sub>IL</sub> (MAX), both Banks idle.                                                                                                                                                                                                      | I <sub>cc1</sub> | 1.5        | 1.5          | 1.5          | 1.5        | 1.5        | mA    |

| Standby Current, $CS\# \geq V_{IH}$ (MIN), $t_{CK} \geq t_{CK}$ (MIN), $CKE \geq V_{IH}$ (MIN), both Banks idle.                                                                                                                                                                         | I <sub>CC2</sub> | 60         | 55           | 53           | 50         | 40         | mA    |

| $ \begin{array}{lll} \text{Standby Current, CS\#} \geq \text{V}_{\text{IH}} \text{ (MIN),} \\ \text{t}_{\text{CK}} \geq \text{t}_{\text{CK}} \text{ (MIN), CKE } \geq \text{V}_{\text{IH}} \text{ (MIN),} \\ \text{both Banks active after t}_{\text{RCD}} \text{ is met.} \end{array} $ | I <sub>CC3</sub> | 70         | 65           | 63           | 60         | 50         | mA    |

| Auto Refresh Current.                                                                                                                                                                                                                                                                    | I <sub>CC4</sub> | 160        | 160          | 145          | 135        | 110        | mA    |

| Operating Current: Active mode, burst =2 Read or Write $t_{RC} \ge t_{RC}$ (MIN), one Bank active.                                                                                                                                                                                       | <sub>CC5</sub>   | 200        | 190          | 180          | 160        | 130        | mA    |

| Operating Current: Active mode, burst =2 Read or Write $t_{RC} \ge t_{RC}$ (MIN), two Banks active.                                                                                                                                                                                      | _ <sup>CC6</sup> | 300        | 280          | 260          | 230        | 190        | mA    |

| Operating Current: Burst Mode, Full Page Burst after $t_{RCD}$ met, Read or Write, $t_{CK} \ge t_{CK}$ (MIN), other Bank idle.                                                                                                                                                           | I <sub>CC7</sub> | 250        | 235          | 225          | 195        | 160        | mA    |

| Operating Current: Block Write, $t_{cK} \ge t_{cK}$ (MIN), $t_{WBC} \ge t_{WBC}$ (MIN), one Bank active.                                                                                                                                                                                 | I <sub>CC8</sub> | 200        | 190          | 180          | 160        | 130        | mA    |

ICC Specifications and Conditions

256Kx32 SGRAM

# **Preliminary Information**

## **Timing and Measurement**

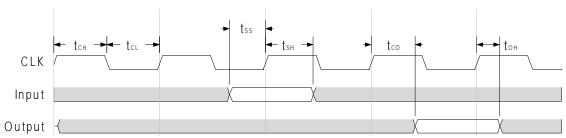

## **Device Timing Specification**

| Parameter                                                                   | Symbol             | - 6     | - 6R6   | - 7R5   | - 8     | -10     | Units |

|-----------------------------------------------------------------------------|--------------------|---------|---------|---------|---------|---------|-------|

|                                                                             |                    | Min Max |       |

| System Clock Cycle Time                                                     | t <sub>ck</sub>    | 6       | 6.6     | 7.5     | 8       | 10      | ns    |

| CAS Latency                                                                 | CL                 | 3 3     | 3 3     | 3 3     | 2 3     | 2 3     | CLK   |

| CLK to Valid Output Delay                                                   | T <sub>co</sub>    | 5       | 5       | 5.5     | 6       | 7       | ns    |

| Output Data Hold Time                                                       | t <sub>oh</sub>    | 3       | 3       | 3.3     | 3 .5    | 4       | ns    |

| CLK High Pulse Width                                                        | t <sub>ch</sub>    | 3       | 3       | 3.3     | 3.6     | 4       | ns    |

| CLK Low Pulse Width                                                         | t <sub>cL</sub>    | 3       | 3       | 3.3     | 3.6     | 4       | ns    |

| Input Setup Time                                                            | t <sub>ss</sub>    | 2       | 2       | 2       | 2       | 2.5     | ns    |

| Input Hold Time                                                             | t <sub>sh</sub>    | 1       | 1       | 1       | 1       | 1       | ns    |

| Activate to Activate Delay (Different Bank)                                 | t <sub>RRD</sub>   | 2       | 2       | 2       | 2       | 2       | CLK   |

| Read to Read Command<br>Delay, Write to Write<br>Command Delay <sup>1</sup> | t <sub>ccd</sub>   | 1       | 1       | 1       | 1       | 1       | CLK   |

| Activate to Read, Write or Block Write Delay                                | t <sub>RCD</sub>   | 3       | 3       | 3       | 2       | 2       | CLK   |

| Precharge to Activate Delay (single Bank Precharge)                         | t <sub>RP</sub>    | 3       | 3       | 3       | 2       | 2       | CLK   |

| Activate to Precharge Delay                                                 | t <sub>ras</sub>   | 4       | 4       | 4       | 3       | 3       | CLK   |

| Activate to Activate Delay (Same Bank), Refresh Cycle time                  | t <sub>RC</sub>    | 7       | 7       | 7       | 5       | 5       | CLK   |

| Refresh Cycle Time                                                          | t <sub>RFCYC</sub> | 7       | 7       | 7       | 6       | 6       | CLK   |

| Block Write to Precharge<br>Delay                                           | t <sub>BPL</sub>   | 3       | 3       | 3       | 2       | 2       | CLK   |

| Block Write Cycle Time                                                      | t <sub>BWC</sub>   | 2       | 2       | 2       | 2       | 2       | CLK   |

| Last Write Data to<br>Precharge                                             | t <sub>wR</sub>    | 2       | 2       | 2       | 1       | 1       | CLK   |

| Load Register (Special or<br>Mode) Command to<br>Command                    | t <sub>LRC</sub>   | 2       | 2       | 2       | 2       | 2       | CLK   |

| Refresh Interval                                                            | t <sub>Ref</sub>   | 15.6    | 15.6    | 15.6    | 15.6    | 15.6    | us    |

| CKE Setup Time                                                              | t <sub>cks</sub>   | 2       | 2       | 2       | 2       | 3       | ns    |

| CKE Hold Time                                                               | t <sub>ckh</sub>   | 1       | 1       | 1       | 1       | 1       | ns    |

**Device Timing Parameters**

<sup>&</sup>lt;sup>1</sup> The Write Command could be a Write or Masked Write Command.

256Kx32 SGRAM

## **Preliminary Information**

## **Device Timing Parameters**

Timing Diagram for Input Setup/Hold, Clock and Output

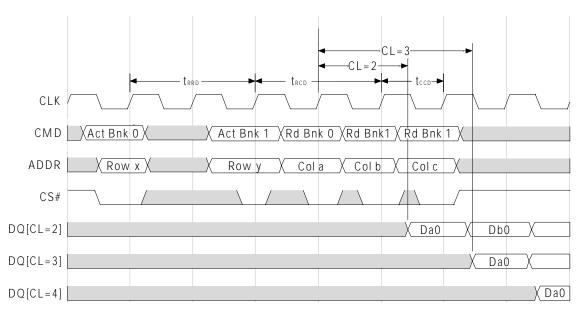

# Timing Diagram for $\mathbf{t}_{\scriptscriptstyle RCD'}$ $\mathbf{t}_{\scriptscriptstyle CCD'}$ $\mathbf{t}_{\scriptscriptstyle RRD}$ and CL

### 256Kx32 SGRAM

## **Preliminary Information**

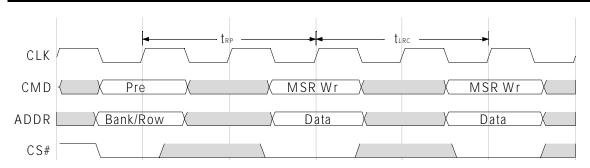

Timing Diagram for  $t_{LRC}$

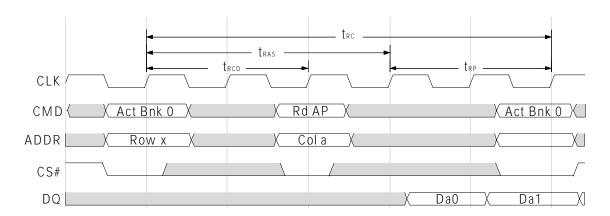

Timing Diagram for  $t_{RC}$ ,  $t_{RAS}$  and  $t_{RP}$

Timing Diagram for  $t_{BWC}$  and  $t_{BPL}$

256Kx32 SGRAM

## **Preliminary Information**

### **Test and Measurement**

### **Test Structure and Measurement Points**

### **Notes**

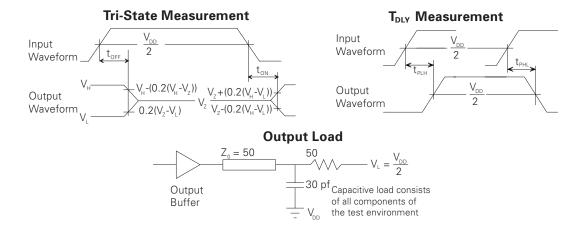

- 1 Valid Delay Measurement is made from the VDDQ / 2 on the input waveform to the VDDQ / 2 on the output waveform. Input waveform should have a slew rate of 1V/ns.

- 2 Tri-state  $t_{\text{off}}$  measurement is made from the VDDQ/2 on the input waveform to the output waveform moving 20% from its initial to final value VDDQ/2.

256Kx32 SGRAM

## **Preliminary Information**

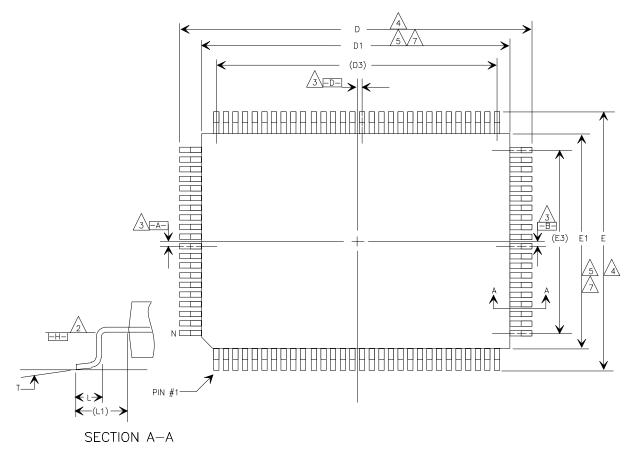

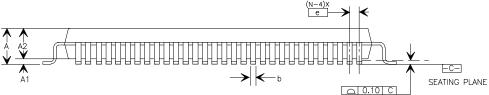

## **Mechanical Specifications**

|        |                     | Plastic Quad<br>Flatpack (PQFP)                                      |         | Thin Quad Flatpack<br>(LQFP) |       |

|--------|---------------------|----------------------------------------------------------------------|---------|------------------------------|-------|

| Symbol | Description         | Min                                                                  | Max     | Min                          | Max   |

| Ref    | Reference Standards | JEDEC MO-108-CC-1 JEDEC MO-<br>JEDEC MO-108-CC-2<br>EIAJ QFP1420-065 |         | )-136-DJ                     |       |

|        | Identification      | Footprint                                                            | =3.2 mm | Body Thickness=1.4 mm        |       |

| А      | Overall Height      |                                                                      | 3.40    |                              | 1.60  |

| A1     | Stand Off           | note 9                                                               |         | note 9                       |       |

| A2     | Body Thickness      | 2.55                                                                 | 3.05    | 1.35                         | 1.45  |

| AAA    | Lead True Position  | 0.12                                                                 |         | 0.1                          |       |

| b      | Lead Width          | 0.20                                                                 | 0.40    | 0.20                         | 0.40  |

| С      | Lead Thickness      | 0.13                                                                 | 0.23    | 0.150                        | 0.188 |

| D      | Terminal Dimension  | 22.95                                                                | 23.45   | 21.90                        | 22.10 |

| D1     | Package Body        | 19.90                                                                | 20.10   | 19.90                        | 20.10 |

| D3     | Reference           | 18.85 REF.                                                           |         | 18.85 REF.                   |       |

| Е      | Terminal Dimension  | 16.95                                                                | 17.45   | 15.90                        | 16.10 |

| E1     | Package Body        | 13.90                                                                | 14.10   | 13.90                        | 14.10 |

| E3     | Reference           | 12.35 REF.                                                           |         | 12.35 REF.                   |       |

| е      | Lead Pitch          | 0.65                                                                 |         | 0.65                         |       |

| L      | Foot Length         | 0.60                                                                 | 1.00    | 0.45                         | 0.75  |

| L1     | Lead Length         | 1.60 REF                                                             |         | 1.00 REF                     |       |

| Т      | Lead Angle          | 0°                                                                   | 10°     | 0°                           | 10°   |

| N      | Lead Count          | 100                                                                  |         | 100                          |       |

| Υ      | Coplanarity         | 0.10                                                                 |         | 0.10                         |       |

### PQFP and LQFP Package Dimensions

### Notes:

- 1 All dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2 Datum plan --H-- located at bottom of lead and is coincident with the lead where the lead exits the plastic body at the bottom of the parting line.

- Datums A--B and --D-- to be determined at datum plane --H-- where the center two leads exit the plastic body.

- 4 To be determined at seating plane -- C--.

- 5 Dimensions D1 and E1 do not include mold protrusions. Allowable protrusion is 0.25 mm per side. D1 and E1 do include mold mismatch and are determined at datum plane -H-.

- 6 Details of pin 1 identifier are optional.

- 7 These dimensions to be determined at datum plane --H--.

- 8 Controlling dimension: millimeter.

- 9 0.1 mm stand-off requires capped vias under body with a SMT process that requires cleaning. A 0.25 mm stand-off does not require capped vias. A 0.05 mm or less stand-off is acceptable for a "no-clean" process only.

256Kx32 SGRAM

# **Preliminary Information**

**Packaging Dimensions**

256Kx32 SGRAM

## **Preliminary Information**

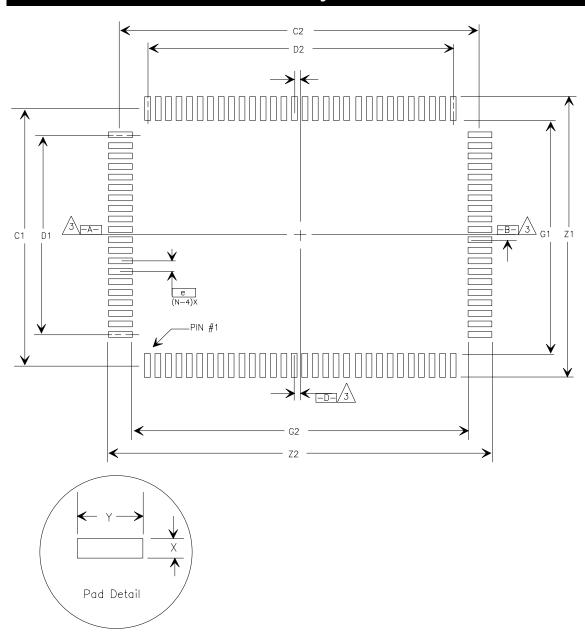

#### PCB Land Pattern

The land pattern shown in Figure 7.2.1 accommodates the QFP and LQFP packages described in 7.1.1 above. Note that the pad required to accommodate the two packages is larger than what would be required if only one package type is accommodated. SMT manufacturing capabilities vary from manufacturer to manufacturer. Check with your SMT processes to ensure that the mounting pad recommended is within your manufacturing process capability.

|            |                     | QFP        |       |  |

|------------|---------------------|------------|-------|--|

| Symbo<br>I | Description         | Min        | Max   |  |

| C1         | Reference           | 15.98 REF. |       |  |

| C2         | Reference           | 21.98 REF. |       |  |

| D1         | Reference           | 12.35 REF. |       |  |

| D2         | Reference           | 18.85 REF. |       |  |

| е          | Pad Pitch           | 0.65       |       |  |

| G1         | Pad Inner Dimension | 13.69      | 13.79 |  |

| G2         | Pad inner Dimension | 19.69      | 19.79 |  |

| N          | Pad Count           | 100        |       |  |

| Х          | Pad Width           | 0.35       | 0.38  |  |

| Υ          | Pad Length          | 2.24 REF.  |       |  |

| Z1         | Pad Outer Dimension | 18.16      | 18.26 |  |

| <b>Z</b> 2 | Pad Outer Dimension | 24.16      | 24.26 |  |

PCB Land Pattern

### Notes:

- All dimensioning and tolerancing conforms to ANSI Y14.5M-1982.

- 2 Controlling dimension: millimeter.

- 3 Datums A--B and --D-- to be determined from the center two leads

- 4 Based on the Surface Mount Design and Land Pattern Standard in IPC-SM-782 revision A, Subsection 11.3, 8/93 for QFP. (IPC is the Institute for Interconnecting and Packaging Electronics Circuits, 7380 N. Lincoln Ave., Lincolnwood, Illinois 60646-1705, Tel. 708 677-2850).

256Kx32 SGRAM

## **Preliminary Information**

**PCB Land Pattern**

© MoSys Inc. 1997 Printed in United States All Rights reserved MoSys®, MultiBank® DRAM are registered trademarks of MoSys Inc