# Section 20. Comparator

# HIGHLIGHTS

This section of the manual contains the following major topics:

| 20.1  | Introduction                             |       |

|-------|------------------------------------------|-------|

| 20.2  | Control Register                         | 20-3  |

| 20.3  | Comparator Configuration                 | 20-4  |

| 20.4  | Comparator Operation                     |       |

| 20.5  | Comparator Reference                     |       |

| 20.6  | Comparator Response Time                 |       |

| 20.7  | Comparator Outputs                       |       |

| 20.8  | Comparator Interrupts                    |       |

| 20.9  | Comparator Operation During SLEEP        |       |

| 20.10 | 0 Effects of a RESET                     |       |

| 20.1  | 1 Analog Input Connection Considerations | 20-10 |

| 20.12 | 2 Initialization                         | 20-11 |

|       | 3 Design Tips                            |       |

| 20.14 | 4 Related Application Notes              |       |

|       | 5 Revision History                       |       |

### 20.1 Introduction

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the I/O pins. The on-chip Voltage Reference (see the "Voltage Reference" section) can also be an input to the comparators.

The CMCON register, shown in Figure 20-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 20-1.

- n = Value at POR reset

# 20.2 Control Register

|         | <b>j</b>                                                 |                             | <b>j</b>       |        |       |       |       |       |

|---------|----------------------------------------------------------|-----------------------------|----------------|--------|-------|-------|-------|-------|

|         | R-0                                                      | R-0                         | U-0            | U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         | C2OUT                                                    | C10UT                       | —              | _      | CIS   | CM2   | CM1   | CM0   |

|         | bit 7                                                    |                             |                |        |       |       |       | bit 0 |

|         |                                                          |                             |                |        |       |       |       |       |

| bit 7   |                                                          | omparator2 C                | Output Indicat | or bit |       |       |       |       |

|         |                                                          | + > C2 VIN-                 |                |        |       |       |       |       |

| 1.11.0  | $0 = C2 \operatorname{Vin} + < C2 \operatorname{Vin} +$  |                             |                |        |       |       |       |       |

| bit 6   |                                                          | omparator1 C<br>+ > C1 VIN– | output Indicat | or dit |       |       |       |       |

|         | 0 = C1 VIN                                               |                             |                |        |       |       |       |       |

| bit 5:4 | Unimplem                                                 | ented: Read                 | as '0'         |        |       |       |       |       |

| bit 3   | CIS: Comparator Input Switch bit                         |                             |                |        |       |       |       |       |

|         | When CM2:CM0: = 001:                                     |                             |                |        |       |       |       |       |

|         | 1 = C1 VIN- connects to AN3                              |                             |                |        |       |       |       |       |

|         | 0 = C1 VIN- connects to ANO                              |                             |                |        |       |       |       |       |

|         | <u>When CM2:CM0 = 010:</u>                               |                             |                |        |       |       |       |       |

|         | 1 = C1 VIN - connects to AN3                             |                             |                |        |       |       |       |       |

|         | C2 VIN- connects to AN2                                  |                             |                |        |       |       |       |       |

|         | 0 = C1 VIN - connects to AN0                             |                             |                |        |       |       |       |       |

| bit 2:0 | C2 VIN- connects to AN1                                  |                             |                |        |       |       |       |       |

| DIL 2.0 | CM2:CM0: Comparator Mode Select bits<br>See Figure 20-1. |                             |                |        |       |       |       |       |

|         | eee rigare                                               |                             |                |        |       |       |       |       |

|         | Legend                                                   |                             |                |        |       |       |       |       |

|         | R = Reada                                                | ble bit                     | W = Writabl    | e bit  |       |       |       |       |

|         |                                                          |                             |                |        |       |       |       |       |

#### Register 20-1: CMCON Register

U = Unimplemented bit, read as '0'

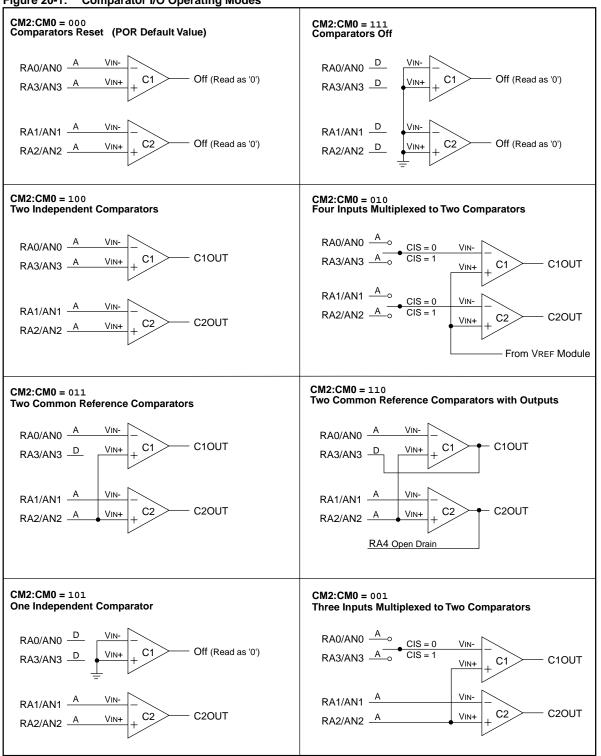

### 20.3 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 20-1 shows the eight possible modes. The TRIS register controls the data direction of the comparator I/O pins for each mode. If the comparator mode is changed, the comparator output level may not be valid for the new mode for the delay specified in the electrical specifications of the device.

**Note:** Comparator interrupts should be disabled during a comparator mode change, otherwise a false interrupt may occur.

Figure 20-1: Comparator I/O Operating Modes

A = Analog Input, port reads as zeros always.

D = Digital Input.

CIS (CMCON<3>) is the Comparator Input Switch.

#### 20.4 Comparator Operation

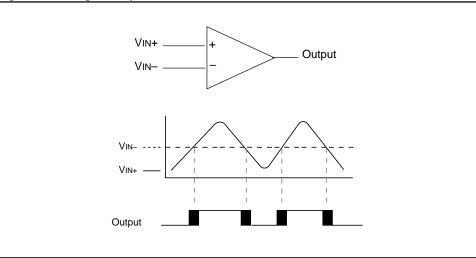

A single comparator is shown in Figure 20-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 20-2 represent the uncertainty due to input offsets and response time.

## 20.5 Comparator Reference

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal that is present at VIN– is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 20-2).

#### Figure 20-2: Single Comparator

#### 20.5.1 External Reference Signal

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. The reference signal must be between VSS and VDD, and can be applied to either pin of the comparator(s).

#### 20.5.2 Internal Reference Signal

The comparator module also allows the selection of an internally generated voltage reference for the comparators. The "**Voltage Reference**" section contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM2:CM0 = 010 (Figure 20-1). In this mode, the internal voltage reference is applied to the ViN+ input of both comparators.

The internal voltage reference may be used in any comparator mode. When used in this fashion the I/O/VREF pin may be used for I/O. The voltage reference is connected to the VREF pin.

#### 20.6 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is guaranteed to have a valid level. If the internal reference is changed, the maximum settling time of the internal voltage reference must be considered when using the comparator outputs. Otherwise the maximum response time of the comparators should be used.

## 20.7 Comparator Outputs

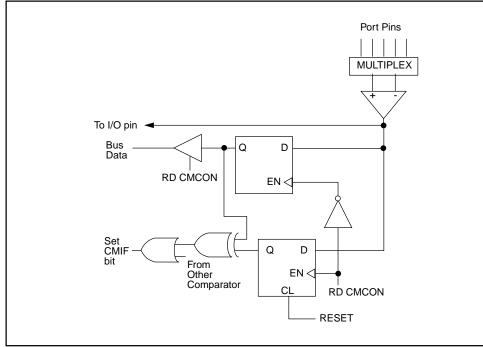

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the I/O pins. When CM2:CM0 = 110, multiplexors in the output path of the I/O pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 20-3 shows the comparator output block diagram.

The TRIS bits will still function as the output enable/disable for the I/O pins while in this mode.

- **Note 1:** When reading the Port register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- **Note 2:** Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

Figure 20-3: Comparator Output Block Diagram

#### 20.8 Comparator Interrupts

The comparator interrupt flag is set whenever the comparators value changes relative to the last value loaded into CMxOUT bits. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, is the comparator interrupt flag. The CMIF bit must be cleared. Since it is also possible to set this bit, a simulated interrupt may be initiated.

The CMIE bit and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of the CMCON register. This will load the CMCON register with the new value with the CMxOUT bits.

- b) Clear the CMIF flag bit.

An interrupt condition will continue to set the CMIF flag bit. Reading CMCON will end the interrupt condition, and allow the CMIF flag bit to be cleared.

### 20.9 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake up the device from SLEEP mode when enabled. While the comparator is powered-up, each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM2:CM0 = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

#### 20.10 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM2:CM0 = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

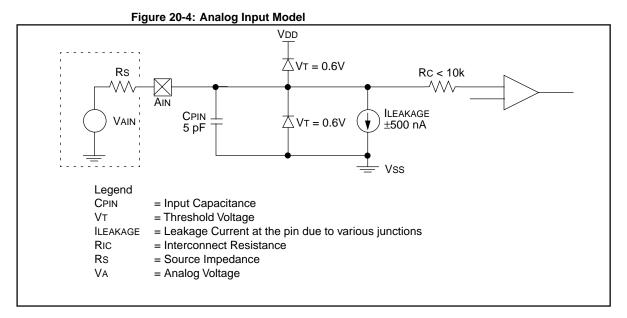

#### 20.11 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 20-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and VSS. The analog input therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources.

Table 20-1: Registers Associated with Comparator Module

| Name   | Bit 7               | Bit 6 | Bit 5 | Bit 4 | Bit 3               | Bit 2 | Bit 1 | Bit 0               | Value on<br>POR,<br>BOR | Value on<br>All Other<br>Resets |

|--------|---------------------|-------|-------|-------|---------------------|-------|-------|---------------------|-------------------------|---------------------------------|

| CMCON  | C2OUT               | C1OUT | _     | —     | CIS                 | CM2   | CM1   | CM0                 | 00 0000                 | 00 0000                         |

| VRCON  | VREN                | VROE  | VRR   |       | VR3                 | VR2   | VR1   | VR0                 | 000- 0000               | 000- 0000                       |

| INTCON | GIE                 | PEIE  | TOIE  | INTE  | RBIE <sup>(2)</sup> | TOIF  | INTF  | RBIF <sup>(2)</sup> | 0000 000x               | 0000 000x                       |

| PIR    | CMIF <sup>(1)</sup> |       |       |       |                     |       |       |                     | 0                       | 0                               |

| PIE    | CMIE <sup>(1)</sup> |       |       |       |                     |       |       | 0                   | 0                       |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'.

Shaded cells are not used for Comparator Module.

Note 1: The position of this bit is device dependent.

2: These bits can also be named GPIE and GPIF.

#### 20.12 Initialization

The code in Example 20-1 depicts example steps required to configure the comparator module of the PIC16C62X devices. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

| Example 20-1: Ir | nitializing Comparator | Module (PIC16C62X) |

|------------------|------------------------|--------------------|

|------------------|------------------------|--------------------|

| FLAG_REG | EQU 0X20     |                                              |

|----------|--------------|----------------------------------------------|

| ;        |              |                                              |

| CLRF     | FLAG_REG     | ; Init flag register                         |

| CLRF     | PORTA        | ; Init PORTA                                 |

| ANDLW    | 0xC0         | ; Mask comparator bits                       |

| IORWF    | FLAG_REG,F   | ; Store bits in flag register                |

| MOVLW    | 0x03         | ; Init comparator mode                       |

| MOVWF    | CMCON        | ; CM<2:0> = 011                              |

| BSF      | STATUS, RPO  | ; Select Bank1                               |

| MOVLW    | 0x07         | ; Initialize data direction                  |

| MOVWF    | TRISA        | ; Set RA<2:0> as inputs, RA<4:3> as outputs, |

|          |              | ; TRISA<7:5> always read `0'                 |

| BCF      | STATUS, RPO  | ; Select Bank0                               |

| CALL     | DELAY 10     | ; 10µs delay                                 |

| MOVF     | CMCON, F     | ; Read CMCON to end change condition         |

| BCF      | PIR1,CMIF    | ; Clear pending interrupts                   |

| BSF      | STATUS, RPO  | ; Select Bankl                               |

| BSF      | PIE1,CMIE    | ; Enable comparator interrupts               |

| BCF      | STATUS, RPO  | ; Select Bank0                               |

| BSF      | INTCON, PEIE | ; Enable peripheral interrupts               |

| BSF      | INTCON,GIE   | ; Global interrupt enable                    |

|          |              |                                              |

#### 20.13 Design Tips

#### Question 1: My program appears to lock up.

#### Answer 1:

You may be getting stuck in an infinite loop with the comparator interrupt service routine if you did not follow the proper sequence to clear the CMIF flag bit. First you must read the CMCON register, and then you can clear the CMIF flag bit.

#### 20.14 Related Application Notes

This section lists application notes that are related to this section of the manual. These application notes may not be written specifically for the Mid-Range MCU family (that is they may be written for the Base-Line, or High-End families), but the concepts are pertinent, and could be used (with modification and possible limitations). The current application notes related to the comparator module are:

#### Title

Application Note #

AN611

Resistance and Capacitance Meter using a PIC16C622

20

## 20.15 Revision History

**Revision A**

This is the initial released revision of the Comparator module description.