#

# 500Msps, 8-Bit ADC with Track/Hold

### General Description

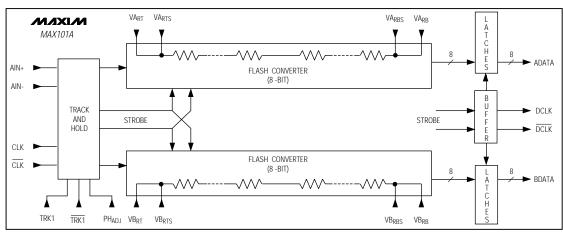

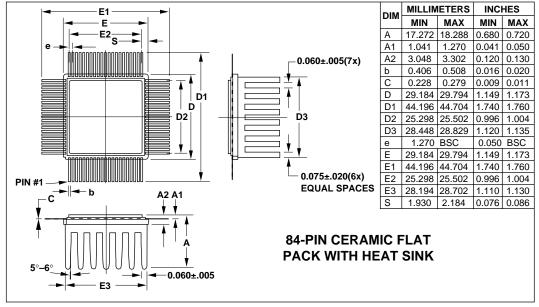

The MAX101A ECL-compatible, 500Msps, 8-bit analogto-digital converter (ADC) allows accurate digitizing of analog signals from DC to 250MHz (Nyquist frequency). Dual monolithic converters, driven by the track/hold (T/H), operate on opposite clock edges (time interleaved). Designed with Maxim's proprietary advanced bipolar processes, the MAX101A contains a high-performance T/H amplifier and two quantizers in an 84-pin ceramic flat pack.

The innovative design of the internal T/H ensures an exceptionally wide 1.2GHz input bandwidth and aperture delay uncertainty of less than 2ps, resulting in a high 7.0 effective bits at the Nyquist frequency. Special comparator output design and decoding circuitry reduce out-of-sequence code errors. The probability of erroneous codes due to metastable states is reduced to less than 1 error per 10<sup>15</sup> clock cycles. And, unlike other ADCs that can have errors resulting in false full-scale or zero-scale outputs, the MAX101A keeps the error magnitude to less than 1LSB.

The analog input is designed for either differential or single-ended use with a  $\pm 250$ mV range. Sense pins for the reference input allow full-scale calibration of the input range or facilitate ratiometric use.

Phase adjustment is available to adjust the relative sampling of the converter halves for optimizing converter performance. Input clock phasing is also available for interleaving several MAX101As for higher effective sampling rates.

- 500Msps Conversion Rate

- ♦ 7.0 Effective Bits Typical at 250MHz

- 1.2GHz Analog Input Bandwidth

- Less than ±1/2LSB INL

- 50Ω Differential or Single-Ended Inputs

- ♦ ±250mV Input Signal Range

- Ratiometric Reference Inputs

- Dual Latched Output Data Paths

- ◆ Low Error Rate, Less than 10<sup>-15</sup> Metastable States

- ♦ 84-Pin Ceramic Flat Pack

### \_Applications

Features

High-Speed Digital Instrumentation High-Speed Signal Processing Medical Systems Radar/Signal Processing High-Energy Physics Communications

### **Ordering Information**

| $M\Delta X = (1)^{1}\Delta (1+B^{2})$ (1°(1+O + /(1°(1+O + 1)))) |    | PIN-PACKAGE                             | TEMP. RANGE  | PART        |

|------------------------------------------------------------------|----|-----------------------------------------|--------------|-------------|

| (with heatsink)                                                  | ck | 84 Ceramic Flat Pack<br>(with heatsink) | 0°C to +70°C | MAX101ACFR* |

\*Contact factory for 84-pin ceramic flat pack without heatsink.

### Functional Diagram

### M/IXI/M

Maxim Integrated Products 1

For the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

MAX101A

### ABSOLUTE MAXIMUM RATINGS

| Supply Voltages (Note 1)                    | DIV10 Input Voltag    |

|---------------------------------------------|-----------------------|

| V <sub>CC</sub> 0V to +7                    | / Output Current, (Ic |

| VEE7V to 0                                  | / TJ <100°C           |

| V <sub>CC</sub> - V <sub>EE</sub> +12       | / 100°C < Tر <120     |

| Analog Input Voltage±2                      | / Operating Temper    |

| Reference Voltage (VART, VBRT)0.3V to +1.5V | / Operating Junction  |

| Reference Voltage (VARB, VBRB)1.5V to +0.3  | / Storage Temperatu   |

| Clock Input Voltage (VIH, VIL)2.3V to 0     | / Lead Temperature    |

|                                             |                       |

| DIV10 Input Voltage (V <sub>IH</sub> , V <sub>IL</sub> )<br>Output Current, (I <sub>OUT(max</sub> )) | V <sub>EE</sub> to OV         |

|------------------------------------------------------------------------------------------------------|-------------------------------|

| TJ <100°C<br>100°C < TJ <120°C                                                                       |                               |

| Operating Temperature Range<br>Operating Junction Temperature (Note 2)<br>Storage Temperature Range  | 0°C to +70°C<br>0°C to +120°C |

| Lead Temperature (soldering, 10sec)                                                                  |                               |

Note 1: The digital control inputs are diode protected. However, limited protection is provided on other pins. Permanent damage may occur on unconnected units under high-energy electrostatic fields. Keep unused units in supplied conductive carrier or shunt the terminals together.

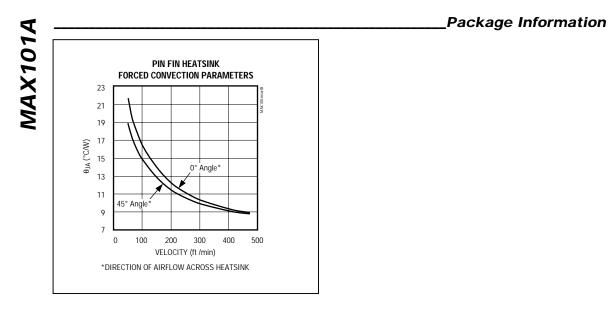

**Note 2:** Typical thermal resistance, junction-to-case  $R_{\theta JC} = 5^{\circ}C/W$  and thermal resistance, junction to ambient (MAX101ACFR)  $R_{\theta JA} = 12^{\circ}C/W$ , if 200 lineal ft/min airflow is provided. See *Package Information*.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ELECTRICAL CHARACTERISTICS

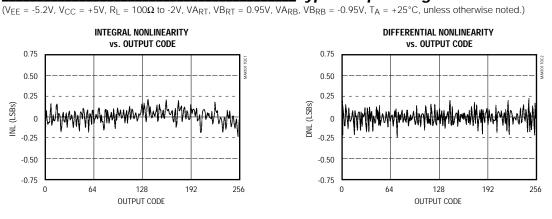

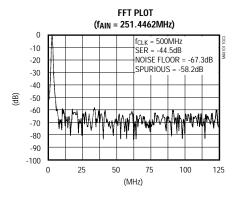

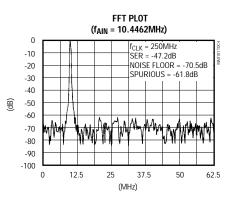

$(V_{EE} = -5.2V, V_{CC} = +5V, R_L = 100\Omega \text{ to } -2V, VA_{RT}, VB_{RT} = 0.95V, VA_{RB}, VB_{RB} = -0.95V, T_A = +25^{\circ}C, \text{ unless otherwise noted}.$  $T_{MIN} \text{ to } T_{MAX} = 0^{\circ}C \text{ to } +70^{\circ}C.) \text{ (Note 3)}$

| PARAMETER                                   | SYMBOL            | COND                                                                             | ITIONS               | MIN  | TYP   | MAX   | UNITS |

|---------------------------------------------|-------------------|----------------------------------------------------------------------------------|----------------------|------|-------|-------|-------|

| ACCURACY                                    |                   | I                                                                                |                      |      |       |       |       |

| Resolution                                  |                   |                                                                                  |                      | 8    |       |       | Bits  |

| Integral Nonlinearity (Note 4)              | INL               | AData, BData                                                                     | $T_A = +25^{\circ}C$ |      |       | ±0.50 | LSB   |

| Integral Nonlinearity (Note 4)              | INL               | ADala, DDala                                                                     | TA = TMIN to TMAX    |      |       | ±0.75 | LJD   |

| Differential Nonlinearity                   | DNL               | AData, BData,                                                                    | $T_A = +25^{\circ}C$ |      |       | ±0.75 | LSB   |

| Differential Norninearity                   | DINL              | no missing codes                                                                 | TA = TMIN to TMAX    |      |       | ±0.85 | LJD   |

| DYNAMIC SPECIFICATIONS                      |                   |                                                                                  |                      |      |       |       |       |

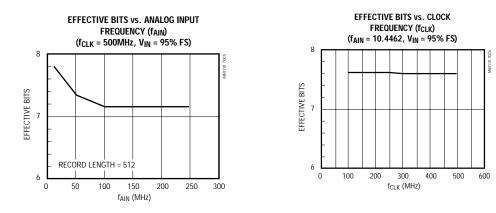

|                                             |                   | fclk = 500MHz,                                                                   | $f_{AIN} = 10MHz$    |      | 7.6   |       |       |

| Effective Bits                              | ENOB              | VIN = 95% full scale                                                             | fain = 125MHz        |      | 7.1   |       | Bits  |

|                                             |                   | (Note 5)                                                                         | fain = 250MHz        | 6.7  | 7.0   |       |       |

| Signal-to-Noise Ratio                       | SNR               | $f_{AIN} = 125MHz$ , $f_{CLK} = 500MHz$ ,<br>$V_{IN} = 95\%$ full scale (Note 6) |                      |      | 44.5  |       | dB    |

| Maximum Conversion Rate                     | fclk              | (Note 7)                                                                         |                      | 500  |       |       | Msps  |

| Analog Input Bandwidth                      | BW <sub>3dB</sub> |                                                                                  |                      |      | 1.2   |       | GHz   |

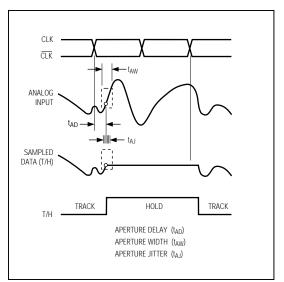

| Aperture Width                              | tAW               | Figure 4                                                                         |                      |      | 270   |       | ps    |

| Aperture Delay                              | tad               | Figure 4                                                                         |                      |      | 1     |       | ns    |

| Aperture Jitter                             | taj               | Figure 4                                                                         |                      |      | 2     |       | ps    |

| ANALOG INPUT                                |                   |                                                                                  |                      |      |       |       |       |

| Input Voltage Range                         | VIN               | AIN+ to AIN-, Table 2,                                                           | Full scale           | 205  |       | 290   | mV    |

| liiput voltage kange                        | VIN               | $T_A = T_{MIN}$ to $T_{MAX}$                                                     | Zero scale           | -290 |       | -205  | IIIV  |

| Input Offset Voltage                        | Vio               | AIN+, AIN-, TA = TMIN to TMAX                                                    |                      | -23  |       | 23    | mV    |

| Least Significant Bit Size                  | LSB               | $T_A = T_{MIN}$ to $T_{MAX}$                                                     |                      | 1.65 |       | 2.35  | mV    |

| Input Resistance                            | RI                | AIN+, AIN-, to GND                                                               |                      | 49   |       | 51    | Ω     |

| Input Resistance<br>Temperature Coefficient |                   |                                                                                  |                      |      | 0.008 |       | Ω/°C  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{EE} = -5.2V, V_{CC} = +5V, R_L = 100\Omega$  to -2V, VA<sub>RT</sub>, VB<sub>RT</sub> = 0.95V, VA<sub>RB</sub>, VB<sub>RB</sub> = -0.95V, T<sub>A</sub> = +25°C, unless otherwise noted. T<sub>MIN</sub> to T<sub>MAX</sub> = 0°C to +70°C.) (Note 3)

| PARAMETER                                              | SYMBOL          | CONI                                                                                                            | DITIONS                          | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|-------|------|-------|-------|

| REFERENCE INPUT                                        | 1               |                                                                                                                 |                                  |       |      |       | I     |

| Reference String Resistance                            | RREF            | VA <sub>RT</sub> to VA <sub>RB</sub>                                                                            |                                  | 100   |      | 190   | Ω     |

| Reference String Resistance<br>Temperature Coefficient |                 |                                                                                                                 |                                  |       | 0.02 |       | Ω/°C  |

| LOGIC INPUTS                                           | 1               |                                                                                                                 |                                  |       |      |       | 1     |

| Digital Input Low Voltage                              | VIL             | $CLK, \overline{CLK}, T_A = T_{MIN}$                                                                            | to T <sub>MAX</sub>              |       |      | -1.50 | V     |

| Digital Input High Voltage                             | VIH             | $CLK, \overline{CLK}, T_A = T_{MIN}$                                                                            | to T <sub>MAX</sub>              | -1.1  |      |       | V     |

| Digital Input High Current                             | Ін              | $DIV10 = 0V, T_A = T_{MI}$                                                                                      | <sub>N</sub> to T <sub>MAX</sub> | 1.1   |      | 3.1   | mA    |

| Input Bias Current                                     | IB              | PHADJ = 0V, TA = TM                                                                                             | IN to T <sub>MAX</sub>           | -40   |      | 40    | μA    |

| Clock Input Bias Current                               | ICLK            | CLK, $\overline{\text{CLK}}$ = -0.8V (no termination),<br>T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> |                                  | -50   |      | 50    | μΑ    |

| LOGIC OUTPUTS (Note 8)                                 | 1               |                                                                                                                 |                                  |       |      |       |       |

|                                                        | V <sub>OL</sub> | AData, BData                                                                                                    | $T_A = +25^{\circ}C$             | -1.95 |      | -1.60 |       |

| Digital Output Low Voltage                             |                 |                                                                                                                 | $T_A = T_{MIN}$ to $T_{MAX}$     | -1.95 |      | -1.50 | V     |

| Digital Output Low Voltage                             |                 | DCLK, DCLK                                                                                                      | $T_A = +25^{\circ}C$             | -1.3  |      | -1.00 |       |

|                                                        |                 | DOER, DOER                                                                                                      | $T_A = T_{MIN}$ to $T_{MAX}$     | -1.4  |      | -0.9  |       |

| Digital Output High Voltage                            | Vон             | AData, BData,                                                                                                   | $T_A = +25^{\circ}C$             | -1.02 |      | -0.70 | v     |

| Digital Output High Voltage                            | VOH             | DCLK, DCLK                                                                                                      | $T_A = T_{MIN}$ to $T_{MAX}$     | -1.10 |      | -0.60 | v     |

| Digital Output Voltage                                 | Voh - Vol       | DCLK, $\overline{\text{DCLK}}$ , $T_{\text{A}} = T_{\text{MIN}}$ to $T_{\text{MAX}}$                            |                                  | 275   |      | 445   | mV    |

| POWER REQUIREMENTS                                     | 1               |                                                                                                                 |                                  |       |      |       |       |

| Positive Supply Current                                | lvcc            | $V_{CC} = 5.0V$                                                                                                 | $T_A = +25^{\circ}C$             | 415   |      | 855   | mA    |

| rostive supply current                                 | IVCC            | vuu = 5.0v                                                                                                      | $T_A = T_{MIN}$ to $T_{MAX}$     |       |      | 910   |       |

| Negative Supply Current                                | - L             | VFF = -5.2V                                                                                                     | $T_A = +25^{\circ}C$             | -895  |      | -500  | mA    |

| Tregative Suppry Current                               | IVEE            | VEE = -0.2V                                                                                                     | $T_A = T_{MIN}$ to $T_{MAX}$     | -935  |      |       | A     |

| Common-Mode Rejection Ratio                            | CMRR            | $V_{INCM} = \pm 0.5V$                                                                                           | TA = TMIN to TMAX                | 35    |      |       | dB    |

| Power-Supply Rejection Ratio                           | PSRR            | TA = TMIN to TMAX                                                                                               | $V_{CC}(nom) = \pm 0.25V$        |       |      |       | dB    |

| Tower Supply Rejection Ratio                           |                 |                                                                                                                 | $V_{EE}(nom) = \pm 0.25V$        | 40    |      |       |       |

MAX101A

### **TIMING CHARACTERISTICS**

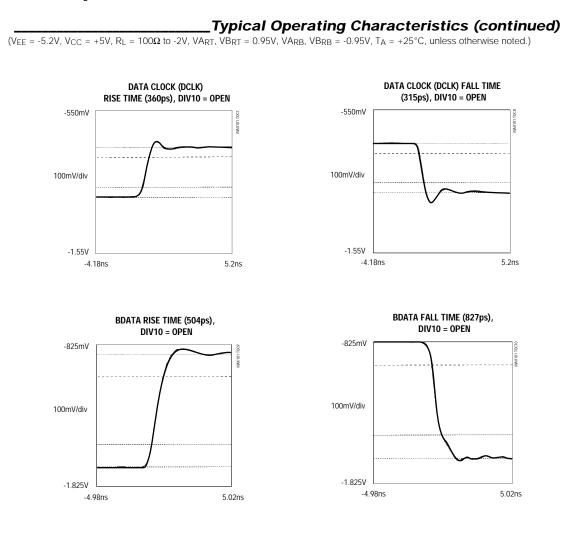

$(V_{EE}=-5.2V, V_{CC}=+5V, R_L=100\Omega \text{ to } -2V, VA_{RT}, VB_{RT}=0.95V, VA_{RB}, VB_{RB}=-0.95V, T_A=+25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                            | SYMBOL           | C                          | MIN  | TYP | MAX | UNITS           |    |

|--------------------------------------|------------------|----------------------------|------|-----|-----|-----------------|----|

| Clock Pulse Width Low                | tpwL             | CLK, CLK                   |      | 0.9 |     | 2.5             | ns |

| Clock Pulse Width High               | tpwh             | CLK, CLK                   |      | 0.9 |     | 2.5             | ns |

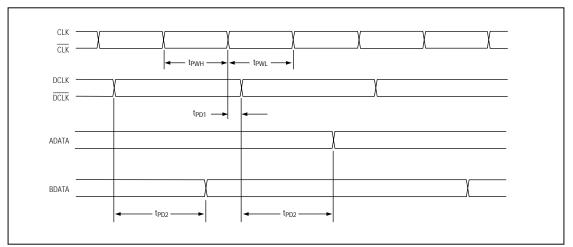

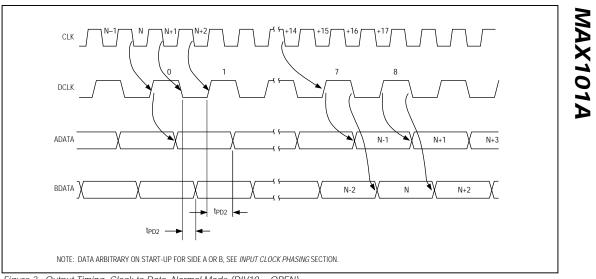

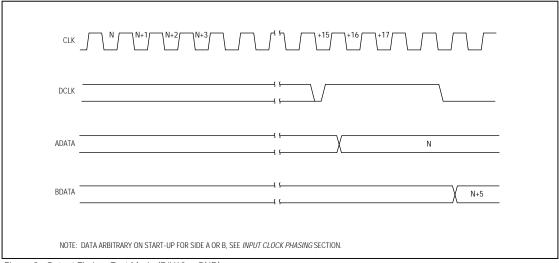

| CLK to DCLK<br>Propagation Delay     | tPD1             | DIV10 = 0, Figure          | 1.2  | 2.3 | 3.4 | ns              |    |

| DCLK to A/BData<br>Propagation Delay | tPD2             | DIV10 = 0, Figures 1 and 2 |      | 0.7 | 1.3 | 1.8             | ns |

| Rise Time                            | to               | te 20% to 80%              |      |     | 300 |                 | nc |

| Rise Tille                           | t <sub>R</sub>   | 20% 10 80%                 | DATA |     | 500 |                 | ps |

| Fall Time                            |                  | 20% to 80%                 | DCLK |     | 300 |                 |    |

| Fair Time                            | tF               | 20% 10 80%                 | DATA |     | 800 |                 | ps |

| Pipeline Delay (Latency)             | t <sub>NPD</sub> | Divide-by-1 mode           | 15   |     | 15  | Clock<br>Cycles |    |

**Note 3:** All devices are 100% production tested at  $+25^{\circ}$ C and are guaranteed by design for  $T_A = T_{MIN}$  to  $T_{MAX}$  as specified. **Note 4:** Deviation from best-fit straight line. See *Integral Nonlinearity* section.

**Note 5:** See the Signal-to-Noise Ratio and Effective Bits section in the Detailed Description of Specifications.

**Note 6:** SNR calculated from effective bits performance using the following equation: SNR(dB) = 1.76 + 6.02 x effective bits.

**Note 7:** Clock pulse width minimum requirements t<sub>PWL</sub> and t<sub>PWH</sub> must be observed to achieve stated performance.

**Note 8:** Outputs terminated through  $100\Omega$  to -2.0V.

### **Typical Operating Characteristics**

M/IXI/M

MAX101A

.

### \_Typical Operating Characteristics (continued)

$(V_{EE} = -5.2V, V_{CC} = +5V, R_L = 100\Omega \text{ to } -2V, VA_{RT}, VB_{RT} = 0.95V, VA_{RB}, VB_{RB} = -0.95V, T_A = +25^{\circ}C$ , unless otherwise noted.)

MAX101A

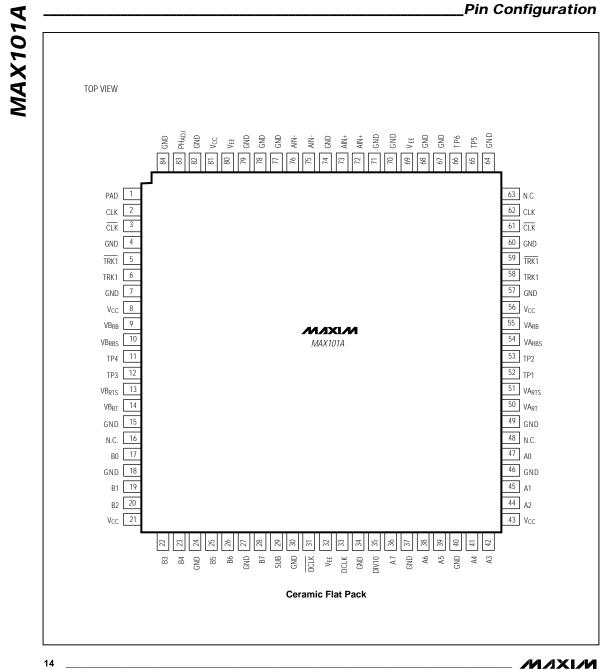

# \_Pin Description

| PIN                                                                                                                   | NAME              | FUNCTION                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                     | PAD               | Internal connection, leave open.                                                                                                                                                                             |

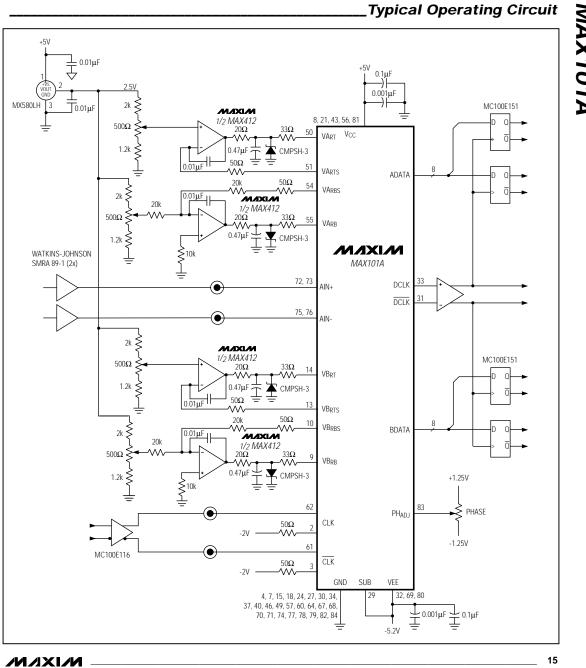

| 2, 62                                                                                                                 | CLK               | Complementary Differential Clock Inputs. Can be driven from standard 10KH ECL with the following considerations: Internally, pins 2, 62 and 3, 61 are the ends of a $50\Omega$ transmission line. Either end |

| 3, 61                                                                                                                 | CLK               | can be driven with the other end terminated with $50\Omega$ to -2V. See <i>Typical Operating Circuit</i> .                                                                                                   |

| 4, 7, 15, 18,<br>24, 27, 30,<br>34, 37, 40,<br>46, 49, 57,<br>60, 64, 67,<br>68, 70, 71,<br>74, 77, 78,<br>79, 82, 84 | GND               | Power-Supply Ground                                                                                                                                                                                          |

| 5, 59                                                                                                                 | TRK1              | Phasing inputs (normally left open). See Applications Information section.                                                                                                                                   |

| 6, 58                                                                                                                 | TRK1              |                                                                                                                                                                                                              |

| 8, 21, 43,<br>56, 81                                                                                                  | V <sub>CC</sub>   | Positive Power Supply, +5V ±5% nominal                                                                                                                                                                       |

| 9                                                                                                                     | VB <sub>RB</sub>  | "B" side negative reference voltage input (Note 9)                                                                                                                                                           |

| 10                                                                                                                    | VB <sub>RBS</sub> | "B" side negative reference voltage sense (Note 9)                                                                                                                                                           |

| 11                                                                                                                    | TP4               | Internal connection, leave pin open.                                                                                                                                                                         |

| 12                                                                                                                    | TP3               | Internal connection, leave pin open.                                                                                                                                                                         |

| 13                                                                                                                    | VB <sub>RTS</sub> | "B" side positive reference voltage sense (Note 9)                                                                                                                                                           |

| 14                                                                                                                    | VB <sub>RT</sub>  | "B" side positive reference voltage input (Note 9)                                                                                                                                                           |

| 16, 48, 63                                                                                                            | N.C.              | No Connect—no internal connection to these pins.                                                                                                                                                             |

| 29                                                                                                                    | SUB               | Circuit Substrate contact. This pin <b>must</b> be connected to V <sub>EE</sub> .                                                                                                                            |

| 31                                                                                                                    | DCLK              | Complementary Differential Clock Outputs. Used to synchronize following circuitry: Outputs A0–A7<br>are valid after DCLK's rising edge. B0–B7 output data are valid after DCLK's falling edge (see Figure 1  |

| 33                                                                                                                    | DCLK              | for output timing information).                                                                                                                                                                              |

| 32, 69, 80                                                                                                            | VEE               | Negative Power Supply, -5.2V ±5% nominal                                                                                                                                                                     |

| 35                                                                                                                    | DIV10             | Divide by 10 mode. Leave open for normal operation. Selects test mode when grounded.                                                                                                                         |

| 36, 38, 39,<br>41, 42, 44,<br>45, 47                                                                                  | A7-A0             | AData and BData Outputs. A0 and B0 are the LSBs, and A7 and B7 are the MSBs. AData and BData outputs conform to ECL logic swings and drive $100\Omega$ transmission lines. Terminate with $100\Omega$ to -2V |

| 28, 26, 25,<br>23, 22, 20,<br>19, 17                                                                                  | B7-B0             | (120 $\Omega$ for Tj > +100°C). See Figures 1–3.                                                                                                                                                             |

# MAX101A

\_Pin Description (continued)

| PIN    | NAME              | FUNCTION                                                                                                                                                                                                 |

|--------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50     | VA <sub>RT</sub>  | "A" side positive reference voltage input (Note 9)                                                                                                                                                       |

| 51     | VA <sub>RTS</sub> | "A" side positive reference voltage sense (Note 9)                                                                                                                                                       |

| 52     | TP1               | Internal connection, leave pin open.                                                                                                                                                                     |

| 53     | TP2               | Internal connection, leave pin open.                                                                                                                                                                     |

| 54     | VA <sub>RBS</sub> | "A" side negative reference voltage sense (Note 9)                                                                                                                                                       |

| 55     | VA <sub>RB</sub>  | "A" side negative reference voltage input (Note 9)                                                                                                                                                       |

| 65     | TP5               | Internal connection, leave pin open.                                                                                                                                                                     |

| 66     | TP6               | Internal connection, leave pin open.                                                                                                                                                                     |

| 72, 73 | AIN+              | Analog Inputs, internally terminated with 50 $\Omega$ to ground. Full-scale linear input range is approximately                                                                                          |

| 75, 76 | AIN-              | ±250mV. Drive AIN+ and AIN- differentially for best high-frequency performance.                                                                                                                          |

| 83     | PHADJ             | Phase adjustment for T/H. Normally connected to ground. A phase adjustment of approximately ±18ps can be made by varying this pin's bias point to optimize interleaving between sides A and B (Note 10). |

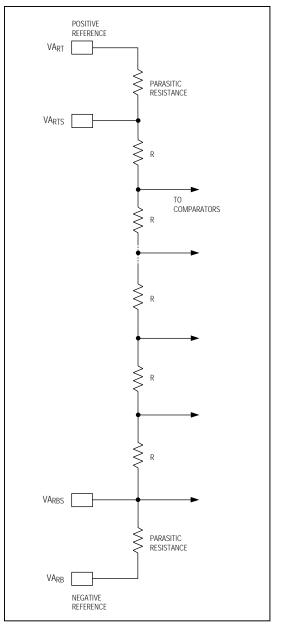

Note 9: VA<sub>RT</sub>, VA<sub>RB</sub>, VB<sub>RT</sub>, and VB<sub>RB</sub> should be adjusted separately from a well bypassed reference circuit to ensure proper amplitude and offset matching. The sense connections to each of these terminals allows precision setting of the reference voltage. The reference ladder is similar for both converter halves (check electrical section for values). Any noise on these terminals will severely reduce overall performance.

**Note 10:** Good results are obtained by connecting the PH<sub>ADJ</sub> input to ground. Improve performance by applying a voltage between ±1.25V to this input. The time that the "A" T/H bridge samples relative to the time that the "B" T/H bridge samples can be varied through a ±18ps range.

Figure 1. Output Timing, Normal Mode (DIV10 = OPEN)

**M**\X\M

MAX101A

Figure 2. Output Timing, Clock to Data, Normal Mode (DIV10 = OPEN)

Figure 3. Output Timing, Test Mode (DIV10 = GND)

**WIXIW**

MAX101A

# \_\_\_\_Definitions of Specifications

**Signal-to Noise Ratio and Effective Bits** Signal-to-noise ratio (SNR) is the ratio between the RMS amplitude of the fundamental input frequency to the RMS amplitude of all other analog-to-digital (A/D) output signals. The theoretical minimum A/D noise is caused by quantization error and is a direct result of the ADC's resolution: SNR = (6.02N + 1.76)dB, where N is the number of effective bits of resolution. Therefore, a perfect 8-bit ADC can do no better than 50dB. The FFT plots in the *Typical Operating Characteristics* show the output level in various spectral bands.

Effective bits is calculated from a digital record taken from the ADC under test. The quantization error of the ideal converter equals the total error of the device. In addition to ideal quantization error, other sources of error include all DC and AC nonlinearities, clock and aperture jitter, missing output codes, and noise. Noise on references and supplies also degrades effective bits performance.

The ADC's input is sine-wave filtered with an anti-aliasing filter to remove any harmonic content. The digital record taken from this signal is compared against a mathematically generated sine wave. DC offsets, phase, and amplitudes of the mathematical model are adjusted until a best-fit sine wave is found. After subtracting this sine wave from the digital record, the residual error remains. The RMS value of the error is applied in the following equation to yield the ADC's effective bits.

Effective bits = N -

$$\log_2 \frac{\text{measured RMS error}}{\text{ideal RMS error}}$$

where N is the resolution of the converter. In this case, N = 8.

The worst-case error for any device will be at the converter's maximum clock rate with the analog input near the Nyquist rate (one-half the input clock rate).

### Aperture Width and Jitter

Aperture width is the time the T/H circuit takes to disconnect the hold capacitor from the input circuit (i.e., to turn off the sampling bridge and put the T/H in hold mode). Aperture jitter is the sample-to-sample variation in aperture delay (Figure 4).

### Error Rates

Errors resulting from metastable states may occur when the analog input voltage, at the time the sample is taken, falls close to the decision point for any one of the input comparators. The resulting output code for many

Figure 4. T/H Aperture Timing

typical converters can be incorrect, including false full- or zero-scale output. The MAX101A's unique design reduces the magnitude of this type of error to 1LSB, and reduces the probability of the error occurring to less than one in every 10<sup>15</sup> clock cycles. If the MAX101A were operated at 500MHz, 24 hours a day, this would translate to less than one metastable state error every 46 days.

### Integral Nonlinearity

Integral nonlinearity is the deviation of the transfer function from a reference line measured in fractions of 1LSB using a "best straight line" determined by a least square curve fit.

### Differential Nonlinearity

Differential nonlinearity (DNL) is the difference between the measured LSB step and an ideal LSB step size between adjacent code transitions. DNL is expressed in LSBs and is calculated using the following equation:

where  $V_{\mbox{\scriptsize MEAS}}$  - 1 is the measured value of the previous code.

A DNL specification of less than 1LSB guarantees no missing codes and a monotonic transfer function.

### Detailed Description

### **Converter Operation**

The parallel or "flash" architecture used by the MAX101A provides the fastest multibit conversion of all common integrated ADC designs. The basic element of a flash, as with all other ADC architectures, is the comparator, which has a positive input, a negative input, and an output. If the voltage at the positive input is higher than the negative input (connected to a reference), the output will be high. If the positive input voltage is lower than the reference, the output will be low. A typical n-bit flash consists of  $2^n$  - 1 comparators with negative inputs evenly spaced at 1LSB increments from the bottom to the top of the reference ladder. For n = 8, there are 255 comparators.

For any input voltage, all the comparators with negative inputs connected to the reference ladder below the input voltage will have outputs of 1 and all comparators with negative inputs above the input voltage will have outputs of 0. Decode logic is provided to convert this information into a parallel n-bit digital word (the output) corresponding to the number of LSBs (minus 1) that the input voltage is above the bottom of the ladder.

The comparators contain latch circuitry and are clocked. This allows the comparators to function as described previously when, for example, clock is low. When clock goes high (samples) the comparator will latch and hold its state until the clock goes low again.

The MAX101A uses a monolithic, dual-interleaved parallel quantizer chip with two separate 8-bit converters. These converters deliver results to the A and B output latches on alternate negative edges of the input clock.

### Track/Hold

As with all ADCs, if the input waveform is changing rapidly during the conversion, the effective bits and SNR will decrease. The MAX101A has an internal track/hold (T/H) that increases attainable effective-bits performance and allows more accurate capture of analog data at high conversion rates.

The internal T/H circuit provides two important circuit functions for the MAX101A:

- Its nominal voltage gain of 4 reduces the input driving signal to ±250mV differential (assuming a ±0.95V reference).

- 2) It provides a differential  $50\Omega$  input that allows easy interface to the MAX101A.

### Table 1. Output Mode Control

| DIV10 | DCLK*<br>(MHz) | MODE                     | DESCRIPTION                                                                                                                                                       |  |  |  |  |  |

|-------|----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| OPEN  | 250            | Normal<br>Divide<br>by 2 | AData and BData valid on oppo-<br>site DCLK edges (AData on rise,<br>BData on fall).                                                                              |  |  |  |  |  |

| GND   | 50             | Test<br>Divide<br>by 10  | AData and BData valid on oppo-<br>site DCLK edges (AData on rise,<br>BData on fall). Data sampled at<br>input CLK rate but 4 out of every<br>5 samples discarded. |  |  |  |  |  |

MAX101A

$^{\ast}$  Input clocks (CLK,  $\overline{\text{CLK}}$ ) = 500MHz for all above combinations. In all modes, the output clock DCLK will be a 50% duty-cycle signal.

### Data Flow

The MAX101A's internal T/H amplifier samples the analog input voltage for the ADC to convert. The T/H is split into two sections that operate on alternate negative clock edges. The input clock, CLK, is conditioned by the T/H and fed to the A/D section. The output clock, DCLK, used for output data timing, will be divided by 2 or 10 from the input clock (Table 1). This results in an output data rate of 250Mbps on each output port in normal mode and 50Mbps in test mode. The differential inputs, AIN+ and AIN-, are tracked continuously between data samples. When a negative strobe edge is sensed, one-half of the T/H goes into hold mode (Figure 4). When the strobe is low, the just-acquired sample is presented to the ADC's input comparators. Internal processing of the sampled data takes an additional 15 clock cycles before it is available at the outputs, AData and BData. See Figures 1-3 for timing.

### \_Applications Information

### Analog Input Ranges

Although the normal operating range is  $\pm 250$ mV, the MAX101A can be operated with up to  $\pm 500$ mV on each input with respect to ground. This extended input level includes the analog signal and any DC common-mode voltage.

To obtain full-scale digital output with differential input drive, a nominal +250mV must be applied between AIN+ and AIN-. That is, AIN+ = +125mV and AIN- = -125mV (with no DC offset). Mid-scale digital output code occurs when there is no voltage difference across the analog inputs. Zero-scale digital output code, with differential -250mV drive, occurs when AIN+ = -125mV and AIN- = +125mV. Table 2 shows how the output of the converter stays at all ones (full scale) when over-ranged or all zeros (zero scale) when underranged.

### **M**IXIM

### Table 2. Input Voltage Range

|                 | inpar i      | enage        | nange          |               |

|-----------------|--------------|--------------|----------------|---------------|

| INPUT           | AIN+<br>(mV) | AIN-<br>(mV) | OUTPUT<br>CODE | MSB to<br>LSB |

| Differential    | +125         | -125         | 11111111       | full scale    |

|                 | 0            | 0            | 1000000        | mid scale     |

|                 | -125         | +125         | 00000000       | zero scale    |

| Single<br>Ended | +250         | 0            | 11111111       | full scale    |

|                 | 0            | 0            | 1000000        | mid scale     |

|                 | -250         | 0            | 00000000       | zero scale    |

\* An offset Vio, as specified in the DC electrical parameters, will be present at the input. Compensate for this offset by adjusting the reference voltage. Offsets may be different between side A and side B.

For single-ended operation:

- 1) Apply a DC offset to one of the analog inputs, or leave one input open. (Both AIN+ and AIN- are terminated internally with  $50\Omega$  to analog ground.)

- Drive the other input with a ±250mV + offset to obtain either full- or zero-scale digital output. If a DC common-mode offset is used, the total voltage swing allowed is ±500mV (analog signal plus offset with respect to ground).

### Reference

The ADC's reference resistor is a Kelvin-sensed, resistor string that sets the ADC's LSB size and dynamic operating range. Normally, the top and bottom of this string are driven with an external buffer amplifier. It will need to supply approximately 19mA due to the  $100\Omega$  minimum resistor string impedance. A ±0.95V reference voltage is normally applied to inputs VART, VBRT, VARB, and VBRB. The reference inputs VARTS, VARBS, VBRTS, and VBRBs allow Kelvin sensing of the applied voltages to increase precision.

An RC network at the ADC's reference terminals is needed for best performance. This network consists of a 33 $\Omega$  resistor connected in series with the buffer output that drives the reference. A 0.47µF capacitor must be connected near the resistor at the buffer's output (see *Typical Operating Circuit*). This resistor and capacitor combination should be located within 0.5 inches of the MAX101A package. Any noise on these pins will directly affect the code uncertainty and degrade the ADC's effective-bits performance.

### CLK and DCLK

All input and output clock signals are differential. The input clocks, CLK and  $\overline{\text{CLK}}$ , are the primary timing signals for the MAX101A. CLK (pins 2, 62) and  $\overline{\text{CLK}}$  (pins 3, 61) are fed to the internal circuitry through an internal 50 $\Omega$  transmission line. One set of CLK,  $\overline{\text{CLK}}$  inputs should be driven and the other pair terminated by 50 $\Omega$  to -2V. Either set of inputs can be used as the driven inputs (input lines are balanced) for easy circuit connection. A minimum pulse width (tpwL) is required for CLK and  $\overline{\text{CLK}}$  (Figures 1–3).

For best performance and consistent results, use a lowphase-jitter clock source for CLK and CLK. Phase jitter larger than 2ps from the input clock source reduces the converter's effective bits performance and causes inconsistent results. The clock supplied to the MAX101A is internally divided by two, reshaped, and buffered. This divided clock becomes the internal signal used as strobes for the converters.

DCLK and DCLK are output clock signals derived from the input clocks and are used for external timing of the AData and BData outputs. (AData is valid after the rising edge of DCLK, and BData is valid after the falling edge.) They are fixed at one-half the rate of the input clocks in normal mode (Table 1). The MAX101A is characterized to work with 500MHz maximum input clock frequencies. See *Typical Operating Circuit*.

### **Output Mode Control (DIV10)**

When DIV10 is grounded, it enables the test mode, where the input incoming clock is divided by ten. This reduces the output data and clock rates by a factor of 5, allowing the output clock duty cycle to remain at 50%. The clock to output phasing remains the same and four out of every five sampled input values are discarded.

When left open, this input (DIV10) is pulled low by internal circuitry and the converter functions in its normal mode. **Layout, Grounding, and Power Supplies** A +5V ±5% supply as well as a -5.2V ±5% supply is needed for proper operation. Bypass the V<sub>EE</sub> and V<sub>CC</sub> supply pins to GND with high-quality 0.1µF and 0.001µF ceramic capacitors located as close to the package as possible. Connect all ground pins to a ground plane to optimize noise immunity and device accuracy. Turn on the fan before connecting the power supplies. See *Package Information* for the required airflow.

### Phase Adjust

MAX101A

This control pin affects the point in time that one-half of the converter samples the input signal relative to the other half. PH<sub>ADJ</sub> is normally connected to ground (0V), but can be adjusted over a  $\pm 1.25V$  range that typically provides a  $\pm 18ps$  adjustment between the "A" side T/H bridge strobe and the "B" side T/H bridge strobe.

### Interleaving (Input Clock Phasing)

To interleave two MAX101As it is necessary to know on which positive edge of the input clock data will change. At power-up, the clock edge from which AData and BData are synchronized is undetermined. The converter can work from a specific input clock edge, as described in the following paragraph.

TRK1 and TRK1 are differential inputs that are used in addition to the normal input clock (CLK) to set data phasing. A signal at one-half the input clock rate with the proper setup and hold times (setup and hold typically 300ps) is applied to these inputs. Choose AData by applying a logic "1" to TRK1 (\*0" to TRK1) before CLK's negative transition. Choose BData by applying a logic "0" to TRK1 before CLK's negative edge ("1" to TRK1). Voltages at the TRK1 input between ±50mV are interpreted as logic "1" and voltages between -350mV and -500mV are interpreted as logic "0".

MAX101A

500Msps, 8-Bit ADC with Track/Hold

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1996 Maxim Integrated Products Printed USA

16

is a registered trademark of Maxim Integrated Products.