#### SERIAL I/O REAL TIME CLOCK

#### ■ GENERAL DESCRIPTION

The NJU6355 series is a serial I/O Real Time Clock suitable for 4 bits microprocessor.

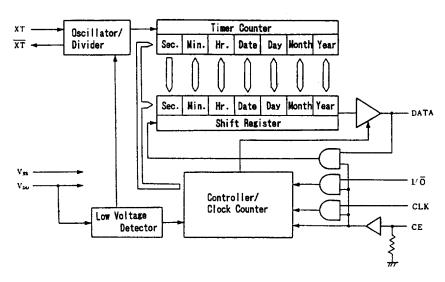

It contains quartz crystal oscillator, counter, shift register, voltage regulator, voltage detector and interface controller.

The NJU6355 required only 4-port of microprocessor for data transfer, and the microprocessor can receive the data at any time when the microprocessor requires.

The operating voltage is as wide as 2.0 V to 5.5 V, consequently, the NJU6355 can count accurate time data even if the back up period.

Furthermore, the long time back up is available as the current consumption during the back up period is less than  $3\mu$  A.

#### ■ PACKAGE OUTLINE

NJU6355XD

NJU6355xE

#### **■ FEATURES**

● Operating Voltage : 2.0 ~ 5.5V

• Low operating current : 3  $\mu$  A (Typ.) at 3.0V 4  $\mu$  A (Typ.) at 5.0V

BCD Counts of Seconds, Minutes, Hours, Date,

Days of Week, Month and Year

• Required only 4-port (DATA, CLK, CE and  $1/\overline{0}$ )

● Low Battery Detector (Low voltage alarm signal output)

- Automatic Leap Year Compensation

- Package Outline --- DIP 8/DMP 8

- C-MOS Technology

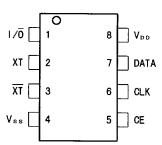

## ■ PIN CONFIGURATION

## LINE UP

| VERSION |          | 0    | U    | T | Р    | U T    | D A      | T A   |        |      | OSC. CAPACITOR                         |

|---------|----------|------|------|---|------|--------|----------|-------|--------|------|----------------------------------------|

| 6355 E  | Seconds, | Minu | tes, | Н | ours | , Days | of Week, | Date, | Month, | Year | C <sub>s</sub> /C <sub>d</sub> on chip |

| F       | Seconds, | Minu | tes, | H | ours | . Days | of Week  |       |        |      | C./C. on chip                          |

| G       | Seconds, | Minu | tes, | H | ours | , Days | of Week, | Date, | Month, | Year | C <sub>a</sub> on chip                 |

|         | Seconds, |      |      |   |      |        |          |       |        |      | C <sub>a</sub> on chip                 |

## BLOCK DIAGRAM

# TERMINAL DESCRIPTION

| NO. | SYMBOL | FU                                                                                                             | N C                                                                                                                                        | ΤI                 | 0             | N            |               |  |  |  |

|-----|--------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------|--------------|---------------|--|--|--|

| 1   | 1/0    | Input/Output Select Term "H": Input, "L": ( During the CE terminal i                                           | Output                                                                                                                                     |                    |               |              | impedance.    |  |  |  |

| 2   | XT     | Quartz Crystal Connectin                                                                                       | ng Termi                                                                                                                                   | nal (f=            | 32. 76        | 88kHz)       |               |  |  |  |

| 3   | ΧT     | Refer to the Line-Up Table for internal Cg, Cd value.                                                          |                                                                                                                                            |                    |               |              |               |  |  |  |

| 5   | CE     | Chip Enable Input Termin "H": Data Input/C "L": Data termina When the CE signal is whi should be fixed to "L". | Output i<br>al is hi                                                                                                                       | s avail<br>gh impe | able<br>dance | •            | ne CLK signal |  |  |  |

| 6   | CLK    |                                                                                                                | Clock Input Terminal The Data Input/Output is synchronized by this clock. When the CE terminal is "L" the data terminal is high impedance. |                    |               |              |               |  |  |  |

|     |        | Serial Timer Data<br>Input/Output                                                                              | 1/0                                                                                                                                        | CE                 | DA            | ATA Terminal |               |  |  |  |

|     |        | input/output                                                                                                   | Н                                                                                                                                          | Н                  |               | Input        | 1             |  |  |  |

| 7   | DATA   |                                                                                                                | L                                                                                                                                          | Н                  |               | Output       |               |  |  |  |

|     |        |                                                                                                                | H                                                                                                                                          | L                  | Hi            | gh-Impedance |               |  |  |  |

|     |        |                                                                                                                | L                                                                                                                                          | Ļ                  | Hi            | gh-Impedance |               |  |  |  |

|     |        |                                                                                                                |                                                                                                                                            |                    |               |              |               |  |  |  |

| 8   | VDD    | Power Supply (+5V)                                                                                             |                                                                                                                                            |                    |               |              |               |  |  |  |

#### FUNCTIONAL DESCRIPTION

#### 1. Timer Data structure

The NJU6355 using BCD code which consisting of 4 bits per 1 digit.

The calendar function including the last date of each month and the leap year calculation is executed automatically.

The unused bit for the timer data is "0".

< Timer Data Bit Map >

|         | MSB  |    |    |    |    |    |            | LSB | Range  |

|---------|------|----|----|----|----|----|------------|-----|--------|

| Second  | 0    | S6 | S5 | S4 | S3 | S2 | S1         | S0  | 0 - 59 |

| Minute  | 0    | m6 | m5 | m4 | m3 | m2 | m1         | m0  | 0 - 59 |

| Hour    | 0    | 0  | Н5 | H4 | Н3 | H2 | H1         | НО  | 0 - 23 |

| Days of | Week |    |    | 1  | 0  | W2 | W1         | WO  | 1 - 7  |

| Date    | 0    | 0  | D5 | D4 | D3 | D2 | D1         | D0  | 1 - 31 |

| Month   | 0    | 0  | 0  | M4 | МЗ | M2 | <b>M</b> 1 | MO  | 1 - 12 |

| Year    | Y7   | Y6 | Y5 | Y4 | Y3 | Y2 | Y1         | YO  | 0 - 99 |

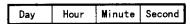

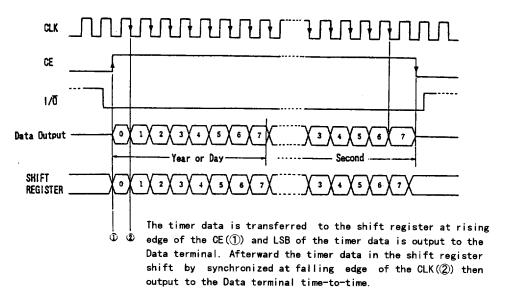

## 2. Timer Data Reading

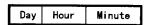

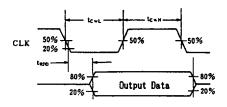

When the  $1/\overline{0}$  terminal is "L" and the CE terminal is "H", timer data can read out. The output is LSB first and the output data strings (depending on the version) is shown below.

The timer data is transferred from timer counter to shift register at rising edge of the chip enable on the CE terminal, and output the LSB of the timer data from the Data terminal.

Afterward the timer data in the shift register shift by synchronized at the falling edge of clock signal on CLK terminal and output from the DATA terminal.

If the timer data is updated in the data output, there are one second difference between timer data and output data.

## < E & G Version >

| Year | Month | Date | Day | Hour | Minute | Second |

|------|-------|------|-----|------|--------|--------|

The data is read out from LSB of Year, and first 52-bit is effective.

#### < F & H Version >

The data is read out from LSB of Days of Week, and first 28-bit is effective.

If the low voltage detector detect the low battery,  $(EE)_H$  is written into each digit of timer data and read out. The code of  $(EE)_H$  is a warning for the data broken.

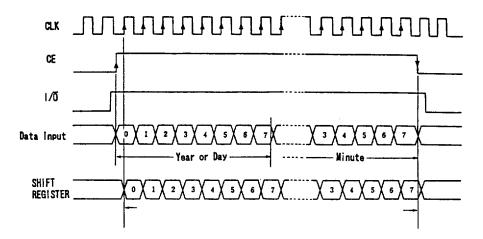

< Read-Out Timing >

note ) When the CE signal is which raising edge or falling edge, the CLK signal should be fixed to "L". And so, before the CE signal is raised, the  $1/\overline{0}$  signal should be fixed to "L".

## 3. Timer Data Writing

When both of  $1/\overline{0}$  terminal and CE terminal are "H", update is stopped, Oscillator divider is cleared, and the timer data can be written to the NJU6355. The timer data is written into the shift register from the Data terminal by synchronized with rising edge of the clock signal input from the CLK terminal, and the data is transferred from the shift register to the timer counter by synchronized with falling edge of the CE signal. In this time the second-counter is cleared to "0", and the oscillator divider start the operation. The input data strings are LSB first of each digit as shown below (the data format is depend on the version):

### < E & G Version >

| Year | Month | Date | Day | Hour | Minute |

|------|-------|------|-----|------|--------|

The data is written from LSB of Year and last 44-bit is effective.

## < F & H Version >

The data is written from LSB of Days of Week and last 20-bit is effective.

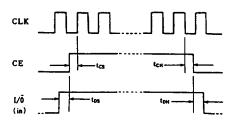

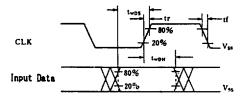

< Write-Down Timing >

The data is input into the shift register at rising edge of the CLK. The data in the shift register is transferred to the timer counter at this falling edge of the CE, then the oscillator divider start the operation.

note ) When the CE signal is which raising edge or falling edge, the CLK signal should be fixed to "L". And so, before the CE signal is raised, the  $1/\bar{0}$  signal should be fixed to "H".

#### 4. Low Voltage Detector

The NJU6355 series incorporate the low battery detector. If the supply voltage reduce to the detection level, (EE) H is written into each digit of the shift register as warning code for the CPU.

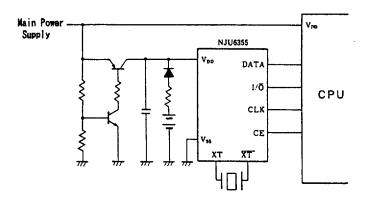

## 5. Data Access

The NJU6355 series can operate from 2.0V to 5.5V. However, it is not allow the data access out of the range of  $5V\pm10\%$ . It may be broken the data unless  $5V\pm10\%$ .

Thus, when the data access, CE terminal should be "H" after the power supply rise to  $500 \pm 10\%$ , then start the operation.

## M ABSOLUTE MAXIMUM RATINGS

( Ta=25°C )

| PARAMETER             | SYMBOL.         | RATINGS                                     | UNIT |

|-----------------------|-----------------|---------------------------------------------|------|

| Supply Voltage        | V <sub>DD</sub> | - 0.3 ~ + 6.0                               | ٧    |

| Input Voltage         | Vin             | V <sub>ss</sub> -0.3 ~ V <sub>DD</sub> +0.3 | V    |

| Power Dissipation     | P <sub>D</sub>  | 250 (DIP)<br>200 (DMP)                      | miN  |

| Operating Temperature | T.p.            | - 30 ~ + 80                                 | °C   |

| Storage Temperature   | Tets            | - 55 <b>~</b> +150                          | °C   |

## ■ ELECTRICAL CHARACTERISTICS

## DC Characteristics

( V<sub>DD</sub>=2. 0V, Ta=25°C )

| PARAMETER                    | SYMBOL          | CONDITIONS           | MIN  | TYP  | MAX  | UNIT |

|------------------------------|-----------------|----------------------|------|------|------|------|

| Operating Current            | I <sub>DD</sub> | XT=32. 768kHz, CE=0V |      | 3. 0 | 4. 0 | μА   |

| LowBattery Detect<br>Voltage | VDET            |                      | 1, 1 |      | 1. 7 | ٧    |

# DC Characteristics

(  $V_{DD}$ =5. 0V ± 10%, Ta=25°C )

| PARAMETER             | SYMBOL           | CONDITIONS                              | MIN                  | TYP  | MAX                   | UNIT     |

|-----------------------|------------------|-----------------------------------------|----------------------|------|-----------------------|----------|

| Operating Voltage     | V <sub>DD</sub>  |                                         | 4. 5                 |      | 5. 5                  | ٧        |

| Operating Current     | lop              | XT=32. 768kHz, CE=0V                    |                      | 4. 0 | 15                    | μА       |

| 3-st Leakage Current  | Itsl             | DATA Terminal (CE=OV)                   | -2.0                 |      | 2. 0                  | μА       |

| Input Leakage Current | Lic              | I/O, CLK Terminals                      | -1.0                 |      | 1. 0                  | μА       |

| Input Current         | lce              | CE Terminal (CE=V <sub>DD</sub> )       |                      |      | 20                    | μА       |

| Input Voltage         | V <sub>1 Н</sub> | I/O, CE, CLK, DATA Terminals            | V <sub>DD</sub> x0.8 |      | VDD                   | T        |

| Thiput Voltage        | ۷، د             | I/O, CE, CLK, DATA Terminals            | Vss                  |      | V <sub>DD</sub> х0. 2 | ٧        |

| Output Voltage        | Vон              | DATA Terminal (I <sub>OH</sub> =-0.4mA) | 4. 1                 |      |                       | <u> </u> |

| output voitage        | Vol              | DATA Terminal (IoL=1.0mA)               |                      |      | 0. 4                  | <b> </b> |

## AC CHARACTERISTICS

$(V_{DD}=5.0V\pm10\%, Ta=25^{\circ}C, C_{L}=50pF)$

| PARAMETER                            | SYMBOL           | CONDITIONS | MIN   | TYP | MAX  | UNIT |

|--------------------------------------|------------------|------------|-------|-----|------|------|

| CLK Pulse "H" Period                 | tcwH             |            | 0. 47 |     | 5000 | μs   |

| CLK Pulse "L" Period                 | towl             |            | 0. 47 |     | 5000 | μs   |

| CE Set-up Time Before<br>CLK Rising  | tcs              |            | 470   |     |      | ns   |

| CE Hold Time After<br>CLK Falling    | t <sub>сн</sub>  |            | 20    |     |      | ns   |

| I/O Set-up Time<br>Before CLK Rising | tos              |            | 60    |     |      | ns   |

| I/O Hold Time After<br>CLK Falling   | t <sub>вн</sub>  |            | 20    |     |      | ns   |

| Write-Down Data<br>Set-Up Time       | twos             |            | 100   |     |      | ns   |

| Write-Down Data<br>Hold Time         | twoн             |            | 20    |     |      | ns   |

| Data Delay Time<br>After CLK Falling | t <sub>RDD</sub> |            |       |     | 200  | ns   |

| Rise/Fall Time                       | t <sub>RF</sub>  |            |       |     | 50   | пѕ   |

## ■ APPLICATION CIRCUIT

12