# V-F/F-V CONVERTOR

## **■ GENERAL DESCRIPTION**

The NJM4151 provide a simple low-cost method of A/D conversion. They have all the inherent advantages of the voltage-to-frequency conversion technique. The Output of NJM4151 is a series of pulses of constant duration. The frequency of the pulses is proportional to the applied input voltage. These converters are designed for use in a wide range of data conversion and remote sensing applications.

## PACKAGE OUTLINE

N IM 4151 D

NJM 4151 M

#### **■ FEATURES**

Operating Voltage

$(8V\sim22V)$

• Frequency Operation from

(1.0Hz to 100kHz) DIP8, DMP8

Package OutlineBipolar Technology

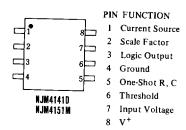

## ■ PIN CONFIGURATION

## **■ EQUIVALENT CIRCUIT**

## ■ ABSOLUTE MAXIMUM RATINGS

(Ta=25℃)

| PARAMETER                   | SYMBOL           | RATINGS           | UNIT |

|-----------------------------|------------------|-------------------|------|

| Supply Voltage              | V <sup>+</sup>   | 8~22              | V    |

| Output Sink Current         | Isink            | 20                | mA   |

| Power Dissipation           | Po               | (DIP8) 500        | mW   |

| •                           |                  | (DMP8) 300        | mW   |

| Input Voltage               | Vı               | $-0.2 \sim V^{+}$ | (V)  |

| Operating Temperature Range | Торг             | -20~+75           | r    |

| Storage Temperature Range   | T <sub>stg</sub> | -40~+125          | r    |

#### **■ ELECTRICAL CHARACTERISTICS**

$(V^+=+15V, Ta=+25^{\circ}C)$

| PARAMETER                                               | TEST CONDITION                                | MIN.      | TYP.      | MAX. | UNIT   |

|---------------------------------------------------------|-----------------------------------------------|-----------|-----------|------|--------|

|                                                         | 8V <v<sup>+&lt;15V</v<sup>                    | 2.0       | 3.5       | 6.0  | mA     |

| Operating Current                                       | 15V <v<sup>+&lt;22V</v<sup>                   | 2.0       | 4.5       | 7.5  | mA     |

| Conversion Accuracy<br>Scale Factor                     | $V_{IN} = 10V$ $R_S = 14.0 k\Omega$           | 0.90      | 1.00      | 1.10 | kHz/V  |

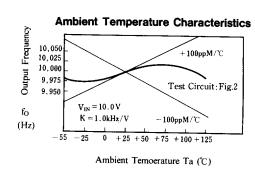

| Drift with Temperature                                  | $V_{IN} = 10V$                                | _         | ±100      |      | ppM/°C |

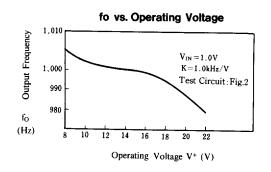

| Drift with V <sup>+</sup>                               | $V_{IN} = 1.0V$<br>8V <v<sup>+&lt;18V</v<sup> | _         | 0.2       | 1.0  | %/V    |

| Input Comparator Offset Voltage                         |                                               |           | 5         | 10   | mV     |

| Offset Current                                          |                                               | _         | ±50       | ±100 | пA     |

| Input Bias Current                                      |                                               | _         | -100      | -300 | пA     |

| Common Mode Range(Note 1)                               |                                               | 0 to V+-3 | 0 to V+-2 |      | v      |

| One-Shot Threshold Voltage, Pin 5                       |                                               | 0.63      | 0.66      | 0.70 | × V+   |

| Input Bias Current, Pin 5                               |                                               | _         | -100      | -500 | nA     |

| Reset V <sub>SAT</sub>                                  | Pin 5, I=2.2mA                                | _         | 0.15      | 0.50 | v      |

| Current Source Output Current ( $R_S$ =14.0k $\Omega$ ) | Pin 1, V*=0V                                  |           | 138.7     | _    | μΑ     |

| Change with Voltage                                     | Pin 1, $V^+ = 0V$ to $V^+ = 10V$              | _         | 1.0       | 2.5  | μΑ     |

| Off Leakage                                             | Pin 1, V <sup>+</sup> =0V                     | . –       | 1         | 50.0 | пA     |

| Reference Voltage                                       | Pin 2                                         | 1.70      | 1.90      | 2.08 | v      |

| Logic Output V <sub>SAT</sub>                           | Pin 3, I=3.0mA                                |           | 0.15      | 0.50 | v      |

| V <sub>SAT</sub>                                        | Pin 3, I=2.0mA                                | _         | 0.10      | 0.30 | v      |

| Off Leakage                                             |                                               | _         | 0.1       | 1.0  | μΑ     |

Note 1: Input Common Mode Range includes ground.

### **■ PRINCIPLE OF OPERATION**

### Single Supply Mode Voltage-to-Frequency Conversion

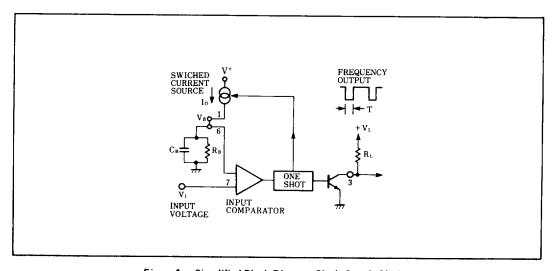

In this application the NJM4151 functions as a stand-alone voltage to frequency converter operating on a single positive power supply. Refer to Figure 1, the simplified block diagram. The NJM4151 contains a voltage comparator, a one-shot, and a precision switched current source. The voltage comparator compares a positive input voltage applied at pin 7 to the voltage at pin 6. If the input voltage is higher, the comparator will fire the one-shot. The output of the one-shot is connected to both the logic output and the precision switched current source. During the one-shot period, T, the logic output will go low and the current source will turn on with current I.

At the end of the one-shot period the logic output will go high and the current source will shut off. At this time the current source has injected an amount of charge  $Q=I_0T$  into the network  $R_B$ - $C_B$ . If this charge has not increased the voltage  $V_B$  such that  $V_B>V_I$ , the comparator again fires the one-shot and the current source injects another lump of charge, Q, into the  $R_B$ - $C_B$  network. This process continues until  $V_B>V_I$ .

When this condition is achieved the current source remains off and the voltage  $V_B$  decays until  $V_B$  is again equal to  $V_B$ . This completes one cycle. The VFC will now run in a steady state mode. The current source dumps lumps of charge into the capacitor  $C_B$  at rate fast enough to keep  $V_B \ge V_I$ . Since the discharge rate of capacitor  $C_B$  is proportional to  $V_B/R_B$ , the frequency at which the system runs will be proportional to the input voltage.

Figure 1. Simplified Block Diagram, Single Supply Mode

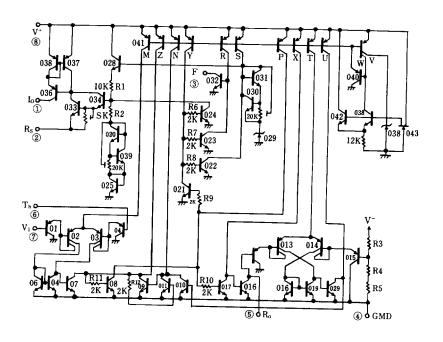

The 4151 VFC is easy to use and apply if you understand the operation of it through the block diagram, Figure 1. Many users, though, have expressed the desire to understand the workings of the internal circuitry. The circuit can be divided into five sections: the internal biasing network, input comparator, one-shot, voltage reference, and the output current source.

The internal biasing network is composed of Q39-Q43. The N-channel FET Q43 supplies the initial current for zener diode Q39. The NPN transistor Q38 senses the zener voltage to derive the current reference for the multiple collector current source Q41. This special PNP transistor provides active pull-up for all of the other sections of the 4151.

The input comparator section is composed of Q1-Q7. Lateral PNP transistors Q1-Q4 form the special ground-sensing input which is necessary for VFC operation at low input voltages. NPN transistors Q5 and Q6 convert the differential signal to drive the second gain stage Q7. If the voltage on input pin 7 is less than that on threshold pin 6, the comparator will be off and the collector of Q7 will be in the high state. As soon as the voltage on pin 7 exceeds the voltage on pin 6, the collector of Q7 will go low and trigger the one-shot.

The one-shot is made from a voltage comparator and an R-S latch. Transistors Q12-Q15 and Q18-Q20 form the comparator, while Q8-Q11 and Q16-Q17 make up the R-S latch. One latch output, open-collector reset transistor Q16, is connected to a comparator input and to the terminal, pin 5. Timing resistor  $R_0$  is tied externally from pin 5 to  $V^+$  and timing capacitor  $C_0$  is tied from pin 5 to ground. The other comparator input is tied to a voltage divider  $R_3$ - $R_5$  which sets the comparator threshold voltage at 0.667  $V^+$ . One-shot operation is initiated when the collector of Q7 goes low and sets the latch. This causes Q16 to turn off, releasing the voltage at pin 5 to charge exponentially towards  $V^+$  through  $R_0$ . As soon as this voltage reaches 0.667  $V^+$ , comparator output Q20 will go high causing Q10 to reset the latch. When the latch is reset, Q16 will discharge  $C_0$  to ground. The one-shot has now completed its function of creating a pulse of period T=1.1  $R_0C_0$  at the latch output, Q21. This pulse is buffered through Q23 to drive the open-collector logic circuit transistor Q32. During the one-shot period the logic output will be in the low state. The one-shot output is also used to switch the reference voltage by Q22 and Q24. The low T.C. reference voltage is derived from the combination of a 5.5V zener diode with resistor and diode level shift networks. A stable 1.89 volts is developed at pin 2, the emitter of Q33.

Connecting the external current-setting resistor  $R_S$ =14.0 $\Omega$  from pin 2 to ground gives 135 $\mu$ A from the collectors of Q33 and Q34. This current is reflected in the precision current mirror Q35-Q37 and produces the output current  $I_O$  at pin 1. When the R-S latch is reset, Q22 and Q24 will hold the reference voltage off, pin 2 will be at 0V, and the current will be off. During the one-shot period T, the latch will be set, the voltage of pin 2 will go to 1.89V, and the output current will be switched on.

#### **■ TYPICAL APPLICATION**

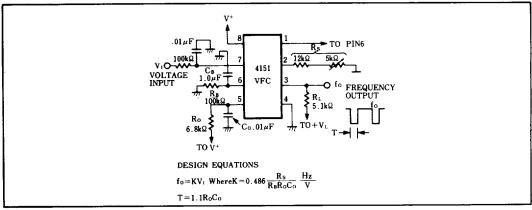

### 1. Single supply Voltage-to-Frequency Converter

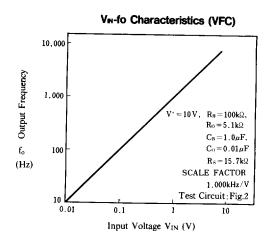

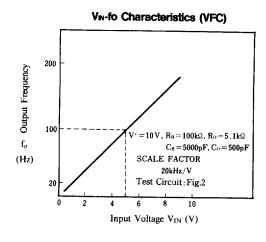

Figure 2 shows the simplest type of VFC that can be made with the 4151. Input voltage range is from 0 to  $\pm 10$ V, and output frequency is from 0 to  $\pm 10$ V. Full scale frequency can be tuned by adjusting  $\pm 10$ R, the output current set resistor. This circuit has the advantage of being simple and low in cost, but it suffers from inaccuracy due to a number of error sources. Linearity error is typically 1%. A frequency offset will also be introduced by the input comparator offset voltage. Also, response time for this circuit is limited by the passive integration network  $\pm 10$ R. For the component values shown in Figure 2, response time for a step change input from 0 to  $\pm 10$ V will be 135msec. For applications which require fast response time and high accuracy, use the circuits of Figure 3 and 4.

Figure 2. Single Supply Voltage-to-Frequency Converter

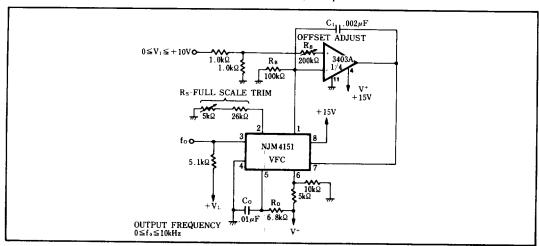

### 2. Precision VFC with Single Supply Voltage

For applications which require a VFC which will operate from a single positive supply with positive input voltage, the circuit of Figure 3 will give greatly improved linearity, frequency offset, and response time. Here, an active integrator using one section of the NJM3403A quad ground-sensing op-amp has replaced the R<sub>B</sub>-C<sub>B</sub> network in Figure 2. Linearity error for this circuit is due only to the 4151 current source output conductance. Frequency offset is due only to the op-amp input offset and can be nulled to zero by adjusting R<sub>B</sub>. This technique uses the op-amp bias current to develop the null voltage, so an op-amp with stable bias current, like the NJM3403A, is required.

Figure 3. Precision Voltage-to-Frequency Converter Single Supply

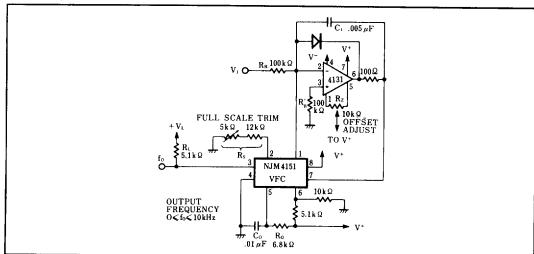

#### 3. Precision Voltage-to-Frequency Converter

In this application (Figure 4) the 4151 VFC is used with an operational amplifier integrator to provide typical linearity of 0.05% over the range of 0 to -10V. Offset is adjustable to zero. Unlike many VFC designs which lose linearity below 10mV, this circuit retains linearity over the full range of input voltage, all the way to 0V.

Trim the full scale adjust pot at  $V_1 = -10V$  for an output frequency of 10kHz. The offset adjust pot should be set for 10Hz with an input voltage of -10mV.

The 4131 operational amplifier integrator improves linearity of this circuit over that of Figure 2 by holding the output of the source, Pin 1, at a constant 0V. Therefore linearity error due to the current source output conductance is eliminated. The diode connected around the op-amp prevents the voltage at 4151 pin 7 from going below 0. Use a low-leakage diode here, since any leakage will degrade the accuracy. This circuit can be operated from a single positive supply if an NJM3403A ground-sensing op-amp is used for the integrator. In this case, the diode can be left out. Note that even though the circuit itself will operate from a single supply, the input voltage is necessarily negative. For operation above 10 kHz, bypass 4151 pin 6 with  $0.01 \mu\text{F}$ .

Figure 4. Precision Voltage-to-Frequency Converter

New Japan Radio Co., Ltd.

#### 4. Comparison of Voltage-to-Frequency Application Circuits

Table 1 compares the VFC applications circuits for typical linearity, frequency offset, response time for a step input from 0 to 10 volts, sign of input voltage, and whether the circuit will operate from a single positive supply or split supplies.

Table 1

|                  | Figure 2 | Figure 3 | Figure 4 |

|------------------|----------|----------|----------|

| Linearity        | 1%       | 0.2%     | 0.05%    |

| Frequency Offset | +10Hz    | 0        | 0        |

| Response Time    | 135msec  | 10msec   | 10msec   |

| Input Voltage    | +        | +        | _        |

| Single supply    | yes      | yes      | yes      |

| Split Supply     | _        | _        | yes      |

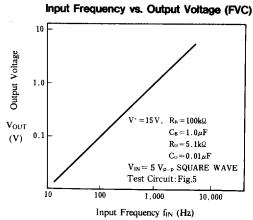

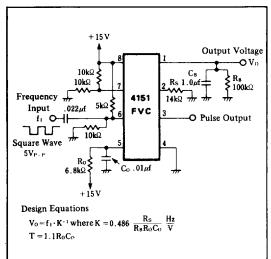

#### 5. Frequency-to-Voltage Conversion

The 4151 can be used as a frequency-to-voltage converter. Figure 5 shows the single-supply FVC configuration. With no signal applied, the resistor bias networks tied to pins 6 and 7 hold the input comparator in the off state. A negative going pulse applied to pin 6 (or positive pulse to pin 7) will cause the comparator to fire the one-shot. For proper operation, pulse width must be less than the period of the one-shot,  $T=1.1~R_{\rm o}C_{\rm o}$ . For a 5Vp-p square-wave input the differentiator network formed by the input coupling capacitor and the resistor bias network will provide pulses which correctly trigger the one-shot. An external voltage comparator such as the NJM311 or NJM2901 can be used to "square-up" sinusoidal input signals before they are applied to the 4151. Also, the component values for the input signal differentiator and bias network can be altered to accommodate square waves with different amplitudes and frequencies. The passive integrator network  $R_{\rm B}C_{\rm B}$  filters the current pulses from the pin 1 output. For less output ripple, increase the value of  $C_{\rm B}$ .

Figure 5. Single Supply Frequency-to-Voltage Converter

Figure 6. Precision Frequency-to-Voltage Converter

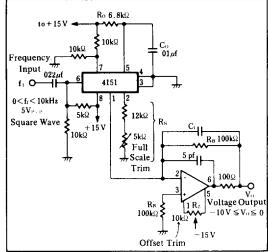

#### 6. Precision Frequency-to-Voltage Converter

For increased accuracy and linearity, use an operational amplifier integrator as shown in Figure 6, the precision FVC configuration. Trim the offset to give -10mV out with 10Hz in and trim the full scale adjust for -10V out with 10kHz in. Input signal conditioning for this circuit is necessary just as for the single supply mode, and scale factor can be programmed by the choice of component values. A tradeoff exists between output ripple and response time, through the choice of integration capacitor  $C_1$ . If  $C_1=0.1\mu\text{F}$  the ripple will be about 100mV. Response time constant  $\tau_R=R_B\cdot C_1$ . For  $R_B=100\text{k}\Omega$  and  $C_1=0.1\mu\text{F}$ ,  $\tau_R=10\text{ms}$

#### **■ PRECAUTIONS**

- The voltage applied to comparator input pins 6 and 7 should not be allowed to go below ground by more than 0.3 volt.

- Pins 3 and 5 are open-collector outputs. Shorts between these pins and V<sup>+</sup> can cause overheating and eventual destruction.

- 3. Reference voltage terminal pin 2 is connected to the emitter of an NPN transistor and is held at approximately 1.9 volts. This terminal should be protected from accidental shorts to ground or supply voltages. Permanent damage may occur if current in pin 2 exceeds 5mA.

- 4. Avoid stray coupling between 4151 pins 5 and 7, which could cause false triggering. For the circuit of Figure 2, bypass pin 7 to ground with at least 0.01μF. If false triggering is experienced with the precision mode circuits, bypass pin 6 to ground with at least 0.01μF. This is necessary for operation above 10kHz.

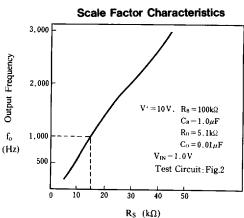

#### **■ PROGRMMING THE 4151**

The 4151 can be programmed to operate with a full scale frequency anywhere from 1.0Hz to 100kHz. In the case of the VFC configuration, nearly any full scale input voltage from 1.0V and up can be tolerated if proper scaling is employed. Here is how to determine component values for any desired full scale frequency.

- 1. Set  $Rs=14k\Omega$  or use a  $12k\Omega$  resistor and  $5k\Omega$  pot as shown in the figures. (The only exception to this is Figure 4.)

- 2 Set  $T=1.1R_0C_0=0.75[1/f_0]$  where  $f_0$  is the desired full scale frequency. For optimum performance make  $6.8k\Omega < R_0 < 680k\Omega$  and  $0.001\mu F < C_0 < 1.0\mu F$

- 3. a) For the circuit of Figure 2 make  $C_B = 10^{-2} [1/f_0]$  Farads.

Smaller values of  $C_B$  will give faster response time, but will also increase frequency offset and nonlinearity.

- b) For the active integrator circuits make  $C_1 = 5 \times 10^{-5} [1/f_0]$  Farads. The op-amp integrator must have a slew rate of at least  $135 \times 10^{-6} [1/C_1]$  volts per second where the value of  $C_1$  is again give in Frads.

- a) For the circuits of Figure 2 and 3 keep the values of R<sub>B</sub> and R<sub>B</sub>' as shown and use an input attenuator to give the desired full scale input voltage.

- b) For the precision mode circuit of Figure 4, set  $R_B = V_{10}/100\mu A$  where  $V_{10}$  is the full scale input voltage. Alternately the op-amp inverting input (summing node) can be used as a current input with full scale input current  $I_{10} = -100\mu A$ .

- 5. For the FVCs, pick the value of  $C_B$  or  $C_1$  to give the optimum tradeoff between response time and output ripple for the particular application.

#### ■ DESIGN EXAMPLE

- I. Design a precision VFC (from Figure 4) with  $f_0=100kHz$  and  $V_{10}=-10V$ .

- 1. Set Rs=14.0k $\Omega$ .

- 2.  $T=0.75 (1/10^5)=7.5\mu sec$  Let  $R_0=6.8k\Omega$  and  $C_0=0.001\mu F$

- 3.  $C_1 = 5 \times 1^{-5} (1/10^5) = 500$  pF Op-amp slew rate must be at lease SR= $135 \times 10^{-6} (1/500$  pF)=0.27 V/ $\mu$ sec

- 4.  $R_B = 10V/100\mu A = 100k\Omega$

- II. Design a precision VFC with  $f_0=1$ Hz and  $V_{10}=-10$ V,

- 1. Let  $Rs=14.0k\Omega$ .

- 2. T=0.75(1/1)=0.75sec Let  $R_0=680k\Omega$  and  $C_0=1.0\mu F$

- 3.  $C_1 = 5 \times 10^{-5} (1/1) \text{ F} = 50 \mu \text{F}$

- 4.  $R_B = 100k\Omega$

- III. Design a single supply FVC to operate with a supply voltage of 8V and full scale input frequency  $f_0$ =83.3Hz. The output voltage must reach at least 0.63 of its final value in 200msec. Determine the output ripple.

- 1. Set Rs= $14.0k\Omega$ .

- 2. T=0.75(1/83.3)=9msec Let  $R_0=82k\Omega$  and  $C_0=0.1\mu F$

- 3. Since this FVC must operate from 8.0V, we shall make the full scale output voltage at pin 6 equal to 5.0V.

- 4.  $R_B = 5V/100 \mu A = 50 k\Omega$

- 5. Output response time constant is  $\tau_R \le 20$ msec Therefore  $C_B \le \tau_R/R_B = 200 \times 10^{-3}/50 \times 10^3 = 4 \mu F$  Worst case ripple voltage is:  $V_R = 9$ mS $\times 135 \mu$ A $/4 \mu$ F= 304mV

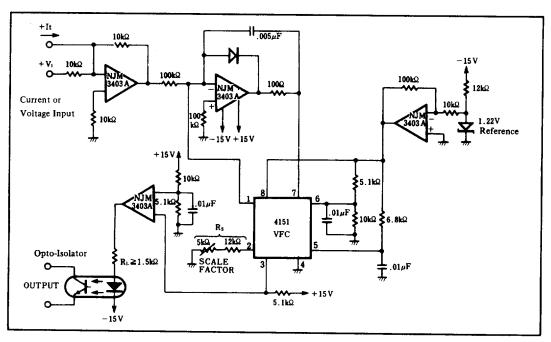

- IV. Design an opto-isolated V<sub>FC</sub> with high linearity which accepts a full scale input voltage of +10V. See Figure 7 for the final disign. This circuit uses the precision mode VFC configuration for maximum linearity. The NJM3403A quad op-amp provides the functions of inverter, integrator, regulator, and LED driver.

Figure 7. Opto-Isolated VFC

## **■ TYPICAL CHARACTERISTICS**