#### PRELIMINARY

# PARADĪGM®

# PDM4M3120

#### 3.3V, 1M x 32 CMOS Static RAM Module

#### Features

- $\Box$  High-density 3.3V, 4 megabyte Static RAM module

- □ Low profile 72-pin ZIP (Zig-zag In-line vertical Package) or 72-pin SIMM or Angled SIMM (Single In-line Memory Module)

- □ Fast access time: 12 ns (max.)

- □ Surface mounted plastic components on an epoxy laminate (FR-4) substrate.

- $\Box$  Single 3.3V (±10%) power supply

- □ Multiple V<sub>SS</sub> pins and decoupling capacitors for maximum noise immunity

- □ Inputs/outputs directly TTL compatible

#### Description

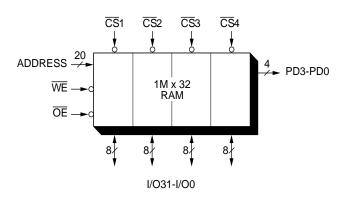

The PDM4M3120 is a 3.3V, 1M x 32 static RAM module constructed on an epoxy laminate (FR-4) substrate using eight 1M x 4 static RAMs in plastic SOJ packages. Availability of four chip select lines (one for each of four RAMs) provides byte access. The PDM4M3120 is available with access times as fast as 12 ns with minimal power consumption.

The PDM4M3120 is packaged in a 72-pin FR-4 ZIP (Zig-zag In-line vertical Package) or a 72-pin SIMM or Angled SIMM (Single In-line Memory Module). The ZIP configuration allows 72 pins to be placed on a package 3.950" long and 0.365" wide. At only 0.590" high, this low-profile package is ideal for systems with minimum board spacing. The SIMM configuration allows use of edge mounted sockets to secure the module.

All inputs and outputs of the PDM4M3120 are TTL compatible and operate from a single 3.3V supply. Full asynchronous circuitry requires no clock or refresh for operation and provides equal access and cycle times for ease of use.

Four identification pins (PD0, PD1, PD2, PD3) are provided for applications in which different density versions of the module are used. In this way, the target system can read the respective levels of PD0, PD1, PD2, PD3 to determine a 1M depth.

#### **Functional Block Diagram**

# Pin Configuration<sup>(1)</sup>

NOTE: 1. Pins 3, 4, 6, and 7 (PD0, PD1, PD02, and PD3 respectively) are read by the user to determine the density of the module. If PD0 reads  $V_{SS}$ , PD1 reads NC, PD2 reads  $V_{SS}$ , PD3 reads NC then the module has a 1M depth.

# **Pin Assignment**

| Pin             | Signal               |  |  |

|-----------------|----------------------|--|--|

| I/O31-I/O0      | Data Inputs/Outputs  |  |  |

| A19-A0          | Addresses            |  |  |

| CS4-CS1         | Chip Selects         |  |  |

| WE              | Write Enable         |  |  |

| ŌĒ              | Output Enable        |  |  |

| PD3-PD0         | Depth Identification |  |  |

| V <sub>CC</sub> | Power                |  |  |

| V <sub>SS</sub> | Ground               |  |  |

#### **Truth Table**

| Mode                    | CS | ŌĒ | WE | Output              | Power   |

|-------------------------|----|----|----|---------------------|---------|

| Deselect/<br>Power-down | Н  | Х  | Х  | High-Z              | Standby |

| Read                    | L  | L  | н  | DATA <sub>OUT</sub> | Active  |

| Write                   | L  | х  | L  | DATA <sub>IN</sub>  | Active  |

| Deselect                | L  | н  | н  | High-Z              | Active  |

# Absolute Maximum Ratings<sup>(1)</sup>

| Symbol            | Rating                                    | Com'l.       | Ind.         | Unit |

|-------------------|-------------------------------------------|--------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage with Respect to $V_{SS}$ | -0.5 to +4.6 | -0.5 to +4.6 | V    |

| T <sub>BIAS</sub> | Temperature Under Bias                    | -10 to +85   | -10 to +85   | °C   |

| T <sub>STG</sub>  | Storage Temperature                       | -55 to +125  | -65 to +150  | °C   |

| T <sub>A</sub>    | Operating Temperature                     | 0 to +70     | -40 to +85   | °C   |

| P <sub>T</sub>    | Power Dissipation                         | 1.0          | 1.0          | W    |

| I <sub>OUT</sub>  | DC Output Current                         | 50           | 50           | mA   |

NOTE: 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Recommended DC Operating Conditions**

| Symbol          | Parameter           | Min. | Тур. | Max. | Unit |

|-----------------|---------------------|------|------|------|------|

| V <sub>CC</sub> | Supply Voltage      | 3.0  | 3.3  | 3.6  | V    |

| V <sub>SS</sub> | Supply Voltage      | 0    | 0    | 0    | V    |

| Commercial      | Ambient Temperature | 0    | 25   | 70   | °C   |

| Industrial      | Ambient Temperature | -40  | 25   | 85   | °C   |

| Symbol          | Parameter                          | Test Conditions                                                                                                                    | Min.                | Max. | Unit |

|-----------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|

| I <sub>LI</sub> | Input Leakage Current<br>(Address) | $V_{CC}$ = Max., $V_{IN}$ = $V_{SS}$ to $V_{CC}$                                                                                   | _                   | 80   | μA   |

| ILI             | Input Leakage Current<br>(Data)    | $V_{CC}$ = Max., $V_{IN}$ = $V_{SS}$ to $V_{CC}$                                                                                   | _                   | 10   | μA   |

| I <sub>LO</sub> | Output Leakage Current             | $\label{eq:V_OUT} \begin{array}{l} V_{OUT} = V_{SS} \text{ to } V_{CC}, \ V_{CC} = \text{Max.}, \\ \hline CS = V_{IH} \end{array}$ | _                   | 10   | μA   |

| V <sub>OL</sub> | Output Low Voltage                 | I <sub>OL</sub> = 8 mA, V <sub>CC</sub> = Min.                                                                                     | _                   | 0.4  | V    |

| V <sub>OH</sub> | Output High Voltage                | $I_{OL} = -4 \text{ mA}, V_{CC} = \text{Min.}$                                                                                     | 2.4                 | _    | V    |

| V <sub>IH</sub> | Input High Voltage                 |                                                                                                                                    | 2.2                 | 6.0  | V    |

| V <sub>IL</sub> | Input Low Voltage                  |                                                                                                                                    | -0.5 <sup>(1)</sup> | 0.8  | V    |

# DC Electrical Characteristics (V\_{CC} = 3.3V $\pm$ 10%, T\_A = 0°C to 70°C)

NOTE 1.  $V_{IL}$  = -1.5V for pulse widths less than 10 ns, once per cycle.

## **Power Supply Characteristics**

| Symbol           | Parameter                                                                                                                                                                                                                 | Max <sup>(1)</sup> | Unit |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|

| I <sub>CC</sub>  | $\frac{\text{Operating Current}}{\text{CS}} = \text{V}_{\text{IL}}, \text{ V}_{\text{CC}} = \text{Max., f} = f_{\text{MAX}}, \text{ Outputs Open}$                                                                        | 900                | mA   |

| I <sub>SB</sub>  | $\frac{Standby Current}{CS} \ge V_{IH}, \ V_{CC} = Max., \ f = f_{MAX}, \ Outputs \ Open$                                                                                                                                 | 200                | mA   |

| I <sub>SB1</sub> | $ \begin{array}{l} \mbox{Full Standby Current} \overline{CS} \geq \ \mbox{V}_{CC} - 0.2 \mbox{V}, \\ \mbox{f} = 0, \ \mbox{V}_{IN} > \ \mbox{V}_{CC} - 0.2 \mbox{V or } < 0.2 \mbox{V}, \mbox{Outputs Open} \end{array} $ | 85                 | mA   |

NOTE 1. Preliminary specification only.

# **Capacitance**<sup>(1)</sup> ( $T_A = +25^{\circ}C$ , f = 1.0 MHz)

| Symbol             | Parameter                                                       | Max. | Unit |

|--------------------|-----------------------------------------------------------------|------|------|

| C <sub>I/O</sub>   | Data I/O Capacitance, V <sub>IN</sub> = 0V                      | 15   | pF   |

| C <sub>IN(1)</sub> | Input Capacitance, (Address) V <sub>IN</sub> = 0V               | 60   | pF   |

| C <sub>IN(2)</sub> | Input Capacitance, $(\overline{WE}, \overline{OE}) V_{IN} = 0V$ | 75   | pF   |

| C <sub>IN(3)</sub> | Input Capacitance, ( $\overline{CS}$ ), V <sub>IN</sub> = 0V    | 20   | pF   |

NOTE 1. This parameter is determined by device characteristics but is not production tested.

#### **AC Test Conditions**

| Input Pulse Levels            | V <sub>SS</sub> to 3.0V |

|-------------------------------|-------------------------|

| Input Rise/Fall Times         | 2.5 ns                  |

| Input Timing Reference Levels | 1.5V                    |

| Output Reference Levels       | 1.5V                    |

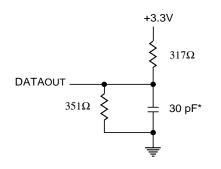

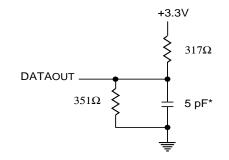

| Output Load                   | See Figures 1 and 2     |

\* Including scope and jig capacitances

Figure 1. Output Load

\* Including scope and jig capacitances

Figure 2. Output Load (for tOHZ, tCHZ, tOLZ, and tCLZ)

|                                 |                                    | PDN  | PDM4M3120SXXZ, PDM4M3120SXXM |        |      |        |      |      |

|---------------------------------|------------------------------------|------|------------------------------|--------|------|--------|------|------|

| Symbol                          | Parameter                          | -20  | ) ns                         | -15 ns |      | -12 ns |      |      |

|                                 |                                    | Min. | Max.                         | Min.   | Max. | Min.   | Max. | Unit |

| Read Cyc                        | le                                 | I    |                              |        |      |        |      |      |

| t <sub>RC</sub>                 | Read Cycle Time                    | 20   | _                            | 15     | —    | 12     | —    | ns   |

| t <sub>AA</sub>                 | Address Access Time                | —    | 20                           | —      | 15   | -      | 12   | ns   |

| t <sub>ACS</sub>                | Chip Select Access Time            | -    | 20                           | _      | 15   | -      | 12   | ns   |

| t <sub>CLZ</sub> <sup>(1)</sup> | Chip Select to Output inLow-Z      | 3    | -                            | 3      | _    | 3      | —    | ns   |

| t <sub>OE</sub>                 | Output Enable to Output Valid      | -    | 10                           | —      | 8    | -      | 7    | ns   |

| t <sub>OLZ</sub> <sup>(1)</sup> | Output Enable to Output in Low-Z   | 0    | -                            | 0      | —    | 0      | -    | ns   |

| t <sub>CHZ</sub> <sup>(1)</sup> | Chip Deselect to Output in High-Z  | -    | 7                            | _      | 7    | -      | 7    | ns   |

| t <sub>OHZ</sub> <sup>(1)</sup> | Output Disable to Output in High-Z | -    | 7                            | —      | 7    | -      | 7    | ns   |

| t <sub>OH</sub>                 | Output Hold from Address Change    | 3    | -                            | 3      | _    | 3      | -    | ns   |

| t <sub>PU</sub> <sup>(1)</sup>  | Chip Select to Power-Up Time       | 0    | -                            | 0      | _    | 0      | —    | ns   |

| t <sub>PD</sub> <sup>(1)</sup>  | Chip Deselect to Power-Down Time   | -    | 20                           | _      | 15   | -      | 12   | ns   |

| Write Cyc                       | le                                 |      |                              |        |      |        |      |      |

| t <sub>WC</sub>                 | Write Cycle Time                   | 20   | —                            | 15     | —    | 12     | —    | ns   |

| t <sub>CW</sub>                 | Chip Select to End of Write        | 12   | -                            | 10     | _    | 10     | —    | ns   |

| t <sub>AW</sub>                 | Address Valid to End of Write      | 12   | -                            | 10     | —    | 10     | —    | ns   |

| t <sub>AS</sub>                 | Address Setup Time                 | 0    | -                            | 0      | —    | 0      | —    | ns   |

| t <sub>WP</sub>                 | Write Pulse Width                  | 15   | -                            | 13     | —    | 12     | -    | ns   |

| t <sub>WR</sub>                 | Write Recovery Time                | 3    | -                            | 3      | —    | 3      | -    | ns   |

| t <sub>WHZ</sub> <sup>(1)</sup> | Write Enable to Output in High-Z   | -    | 7                            | _      | 7    | -      | 7    | ns   |

| t <sub>DW</sub>                 | Data to Write Time Overlap         | 12   | -                            | 10     | —    | 10     | —    | ns   |

| t <sub>DH</sub>                 | Data Hold from Write Time          | 0    | -                            | 0      | —    | 0      | -    | ns   |

| t <sub>OW</sub> <sup>(1)</sup>  | Output Active from End of Write    | 0    | -                            | 0      | _    | 0      | _    | ns   |

# AC Electrical Characteristics (Vcc = 3.3V $\pm$ 10%, $T_A$ = 0°C to +70°C)

NOTE 1. This parameter is determined by device characteristics but is not production tested.

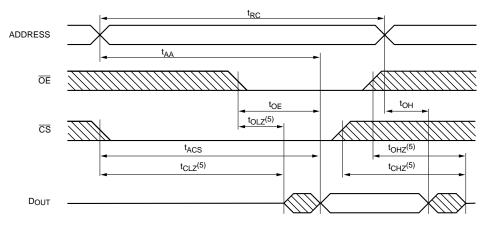

## Timing Waveforms of Read Cycle No.1<sup>(1)</sup>

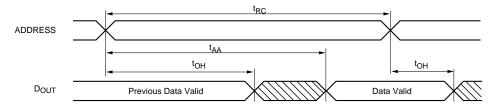

Timing Waveforms of Read Cycle No.2<sup>(1,2,4)</sup>

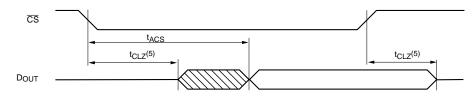

# Timing Waveforms of Read Cycle No.3<sup>(1,3,4)</sup>

- NOTES 1 WE is HIGH for Read Cycle.

2. Device is continuously selected. CS = V<sub>IL</sub>.

3. Address valid prior to or coincident with CS transition LOW.

- 4.  $\overline{OE} = V_{IL}$ .

- 5. Transition is measured  $\pm 200 \text{ mV}$  for steady state. This parameter is

- determined by device characteristics but is not production tested.

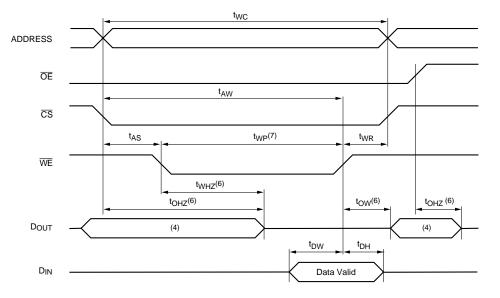

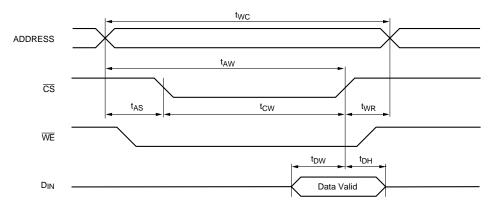

## Timing Waveforms of Write Cycle No.1 (WE Controlled)<sup>(1,2,3,7)</sup>

# Timing Waveforms of Write Cycle No.2 ( $\overline{CS}$ Controlled)<sup>(1,2,3,5)</sup>

NOTES 1  $\overline{WE}$  or  $\overline{CS}$  must be HIGH during all address transitions.

- A write occurs during the overlap (t<sub>WP</sub>) of a LOWCS and a LOWWE.

t<sub>WR</sub> is measured from the earlier of CS or WE going HIGH to end the write cycle.

- 4. During this period, I/O pins are in the output state, and input signals must be applied.

- 5. If the  $\overline{CS}$  LOW transition occurs simultaneously with or after the  $\overline{WE}$  LOW transition, the outputs remain in a high-impedance state.

- 6. Transition is measured ±200 mV for steady state with a 5 pF load (including scope and jig). This parameter is determined by device characteristics but is not production tested.

- 7. If  $\overline{\text{OE}}$  is LOW during a  $\overline{\text{WE}}$  controlled write cycle, the write pulse width must be the larger of t<sub>WP</sub> or  $(t_{WHZ} + t_{DW})$  to allow the I/O drivers to turn off and data to be placed on the bus for the required  $t_{DW}$ . If OE is HIGH during aWE controlled write cycle, this requirement does not apply and the write pulse width can be as short as the specified t<sub>WP</sub>

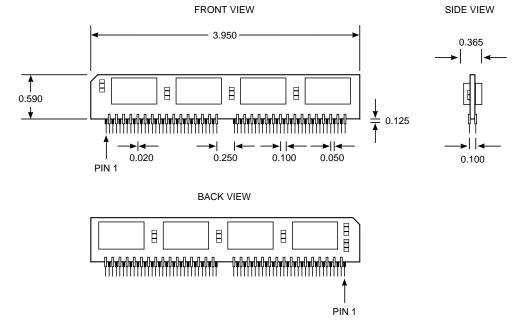

#### **Package Dimensions**

#### **ZIP Version**

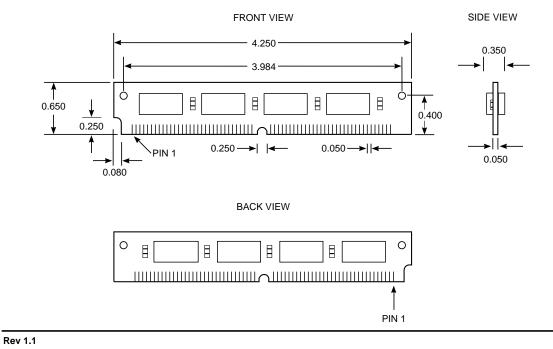

## **SIMM Version**

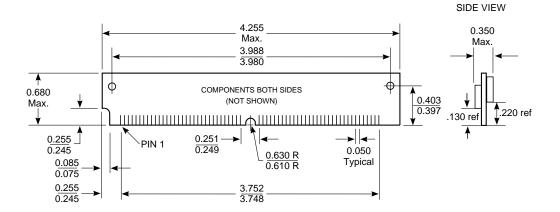

## **Angled SIMM Version**

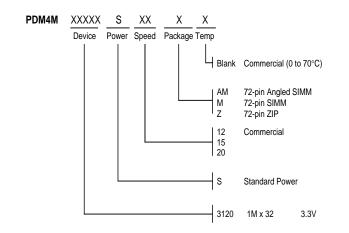

**Ordering Information**