# QUICKSWITCH® PRODUCTS HIGH-SPEED CMOS SYNCHRO-SWITCH™ DUAL 4:1 MUX/DEMUX WITH ACTIVE TERMINATORS

IDTQS3ST253

#### **FEATURES:**

- Enhanced N channel FET with no inherent diode to Vcc

- Bidirectional signal flow

- Flow-through pinout

- Zero propagation delay, zero ground bounce

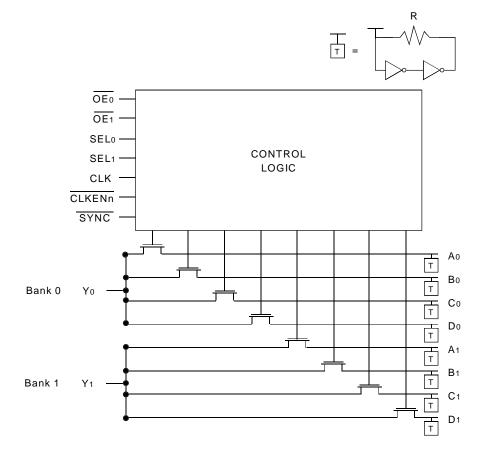

- 2 banks of 4:1 Mux/Demux

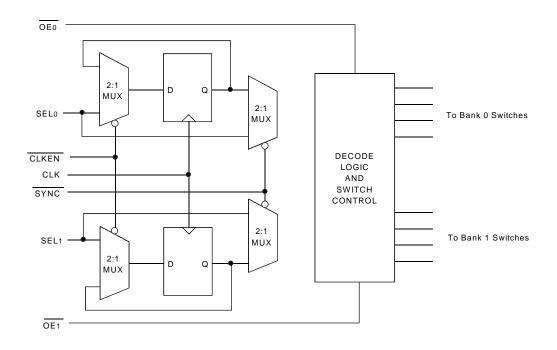

- Port select synchronous to the clock

- Undershoot clamp diodes on all switch and control pins

- Clock enable and Asynchronous enable

- "Bus-hold" terminators on the Demux side

- Asynchronous SEL option

- Break-before-make feature

- Available in QSOP Packages

- Bus-hold eliminates floating bus lines and reduces static power consumption

# DESCRIPTION:

The QS3ST253 is a high-speed CMOS dual 4:1 multiplexer/demultiplexer with active terminators (bus-hold circuits) on the demux side. Port selection and connection, controlled by SEL signals, can be either asynchronous or synchronous. In the synchronous mode, the A, B, C, or D port to Y port connection is updated on the rising edge of the input clock CLK. Once the port-to-port connection is made, data flow can be bi-directional with a typical 250ps propagation delay through the switch. Clock Enable, overriding Asynchronous Enable, and Asynchronous Select controls provide additional design flexibility.

The bus-hold circuits latch the last data driven on the demux side, providing infinite hold time and glitch-free signal transitions. Synchronous controls and bus-hold ease timing constraints in many high speed data mux/demux applications, such as bank interleaving.

The QS3ST253 is characterized for operation at -40°C to +85°C.

### **APPLICATIONS**

Video, audio, graphics switching, muxing

### **FUNCTIONAL BLOCK DIAGRAM**

#### INDUSTRIAL TEMPERATURE RANGE

**NOVEMBER 1999**

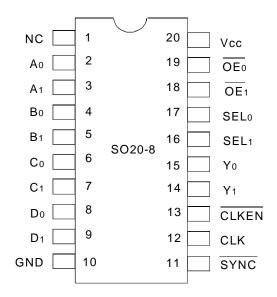

### **PIN CONFIGURATION**

QSOP TOP VIEW

# **ABSOLUTE MAXIMUM RATINGS (1)**

| Symbol               | Description                           | Max.         | Unit |

|----------------------|---------------------------------------|--------------|------|

| VTERM <sup>(2)</sup> | Supply Voltage to Ground              | - 0.5 to +7  | V    |

| VTERM <sup>(3)</sup> | DC Switch Voltage Vs                  | - 0.5 to +7  | V    |

| VTERM <sup>(3)</sup> | DC Input Voltage VIN                  | - 0.5 to +7  | V    |

| VAC                  | AC Input Voltage (pulse width ≤20ns)  | -3           | V    |

| Іоит                 | DC Output Current                     | 120          | mA   |

| Рмах                 | Maximum Power Dissipation (Ta = 85°C) | .82          | W    |

| Tstg                 | Storage Temperature                   | - 65 to +150 | °C   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Vcc Terminals.

- 3. All terminals except Vcc.

#### **CAPACITANCE**

$(TA = +25^{\circ}C, f = 1.0MHz, VIN = 0V, VOUT = 0V)$

| Pins                 |       | Тур. | Max. <sup>(1)</sup> | Unit |

|----------------------|-------|------|---------------------|------|

| Control Inputs       |       | 4    | 5                   | pF   |

| Quickswitch Channels | Demux | 5    | 7                   | pF   |

| (Switch OFF)         | Mux   | 13   | 14                  | pF   |

#### NOTE:

1. This parameter is guaranteed at characterization but not production tested.

### **PIN DESCRIPTION**

| Pin Names                         | 1/0 | Description        |

|-----------------------------------|-----|--------------------|

| A0 - D0                           | I/O | Bank 0 Demux Ports |

| A1 - D1                           | I/O | Bank 1 Demux Ports |

| Y0, Y1                            | I/O | Mux Port           |

| SEL0, SEL1                        | I   | Select Inputs      |

| CLK                               | I   | Clock              |

| CLKEN                             | I   | Clock Enable       |

| OE <sub>0</sub> , OE <sub>1</sub> | I   | Output Enable      |

| SYNC                              | l   | Synchronous Enable |

### **FUNCTION TABLE(1)**

| Control Inputs |                 |                 |          |       |                  | Port | Status                              |                                     |

|----------------|-----------------|-----------------|----------|-------|------------------|------|-------------------------------------|-------------------------------------|

| SYNC           | OE <sub>0</sub> | OE <sub>1</sub> | CLK      | CLKEN | SEL <sub>0</sub> | SEL1 | Yo                                  | <b>Y</b> 1                          |

| L              | L               | L               | <b>↑</b> | L     | L                | L    | A <sub>0</sub>                      | <b>A</b> 1                          |

| L              | Г               | L               | <b>↑</b> | L     | Н                | L    | Во                                  | B1                                  |

| L              | L               | L               | <b>↑</b> | L     | L                | Н    | Со                                  | C1                                  |

| L              | L               | L               | <b>↑</b> | L     | Н                | Н    | D <sub>0</sub>                      | D <sub>1</sub>                      |

| L              | Н               | Н               | <b>↑</b> | L     | Χ                | Χ    | Hold Previous Data (2) (Switch OFF) | Hold Previous Data (2) (Switch OFF) |

| L              | Г               | L               | 1        | Н     | Χ                | Χ    | Hold Previous Mux connection (3)    | Hold Previous Mux connection (3)    |

|                |                 |                 |          |       |                  |      | (Switch ON)                         | (Switch ON)                         |

| L              | Н               | Н               | 1        | Н     | Χ                | Χ    | Hold Previous Data (4) (Switch OFF) | Hold Previous Data (4) (Switch OFF) |

| Н              | L               | L               | Х        | Х     | L                | L    | Ao                                  | <b>A</b> 1                          |

| Н              | L               | L               | Х        | Χ     | Н                | L    | B0                                  | B1                                  |

| Н              | L               | L               | Х        | Х     | L                | Н    | Со                                  | C1                                  |

| Н              | L               | L               | Х        | Χ     | Н                | Н    | Do                                  | D1                                  |

| Н              | Н               | Н               | Х        | Χ     | Χ                | Χ    | Hold Previous Data (2) (Switch OFF) | Hold Previous Data (2) (Switch OFF) |

#### NOTES:

- 1. H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Don't Care

- ↑ = Low-to-High Transition

- 2. Mux switches are turned off and the terminators (last value latches) hold the previous data state. The port connections can be changed by the SEL input.

- 3. The contents of the "Mux select register" are unchanged and the previous Mux connection is unchanged. The output (Mux port) data state will depend on the present data state of the input (Demux port).

- 4. The contents of the "Mux select register" are unchanged and the last value latch holds the previous data state.

### **CONTROL LOGIC**

### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Industrial:  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 5.0V \pm 10\%$

| Symbol | Parameter                              | Te                     | Test Conditions                    |      | Typ. <sup>(1)</sup> | Max. | Unit |

|--------|----------------------------------------|------------------------|------------------------------------|------|---------------------|------|------|

| VIH    | Input HIGH Voltage                     | Guaranteed Logic HIG   | iH for Control Pins                | 2    | _                   | 1    | V    |

| VIL    | Input LOW Voltage                      | Guaranteed Logic LO    | W for Control Pins                 | _    | _                   | 0.8  | V    |

| lin    | Input Leakage Current (Control Inputs) | 0V ≤ VIN ≤ Vcc         |                                    | _    | 0.01                | ±1   | μΑ   |

| loz    | Off-State Current (Hi-Z)               | 0V ≤ Y ≤ Vcc           | 0V ≤ Y ≤ Vcc                       |      | 0.01                | ±1   | μΑ   |

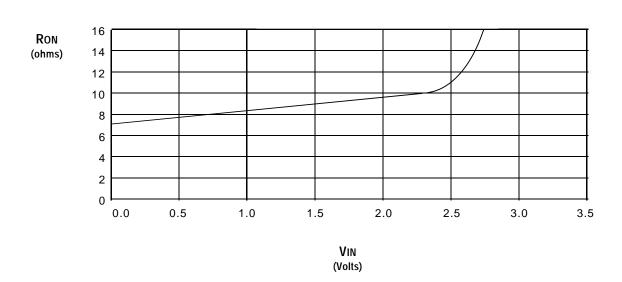

| Ron    | Switch On Resistance (2)               | Vcc = Min., VIN = 0V,  | Vcc = Min., Vin = 0V, Ion = 30mA   |      | 7                   | 9    | Ω    |

|        |                                        | Vcc = Min., VIN = 2.4V | Vcc = Min., VIN = 2.4V, ION = 15mA |      | 10                  | 13   |      |

| Івнь   | Input Hold Current (3,4)               | Vcc = Min.             | VIN = 0.8V                         | 60   | _                   | _    | μΑ   |

| Івнн   | (A, B, C, D)                           | Switch OFF             | VIN = 2V                           | - 60 | _                   | _    |      |

| Івн    | Input Current (5)                      | Vcc = Max.             | VIN = 0V or Vcc                    | _    | _                   | ±50  | μΑ   |

|        | (A, B, C, D)                           |                        | 0.8 < VIN < 2V                     | _    | _                   | ±500 |      |

#### NOTES:

- 1. Typical values are at VCC = 5.0V,  $TA = 25^{\circ}C$ .

- 2. Measured by voltage drop between A/B/C/D and Y pin at indicated current through the switch.

- 3. IBHL is the minimum sustaining "sink" current at the input for VIN = 0.8V. This parameter signifies the latching capability of the bus-hold circuit in logic LOW state.

- 4. IBHH is the minimum sustaining "source" current at the input for VIN = 2V. This parameter signifies the latching capability of the bus-hold circuit in logic HIGH state.

- 5. IBH is the magnitude of the input current specified under two conditions:

- a) Input voltage at GND or Vcc. This indicates the input current under steady-state condition.

- b) Input voltage between 0.8V and 2V (TTL input threshold range). This indicates the maximum input current during transient condition. The driver connected to the input must overcome this current requirement in order to switch the logic state of the bus-hold circuit.

### TYPICAL ON RESISTANCE vs Vin AT Vcc = 5V

#### POWER SUPPLY CHARACTERISTICS

| Symbol | Parameter                                           | Test Conditions <sup>(1)</sup>           | Max. | Unit   |

|--------|-----------------------------------------------------|------------------------------------------|------|--------|

| Icco   | Quiescent Power Supply Current                      | Vcc = Max., Vin = GND or Vcc, f = 0      | 3    | μΑ     |

| Δlcc   | Power Supply Current per Control Input HIGH (2)     | Vcc = Max., Vin = 3.4V, f = 0            | 1.5  | mA     |

| ICCD   | Dynamic Power Supply Current per MHz <sup>(3)</sup> | Vcc = Max., A/B/C/D and Y pins open      | 0.25 | mA/MHz |

|        |                                                     | Control Input Toggling at 50% Duty Cycle |      |        |

#### NOTES:

- 1. For conditions shown as Min. or Max., use the appropriate values specified under DC Electrical Characteristics.

- 2. Per TLL driven input (VIN = 3.4V, control inputs only). A/B/C/D and Y pins do not contribute to Δlcc.

- 3. This current applies to the control inputs only and represents the current required to switch internal capacitance at the specified frequency. The A/B/C/D and Y inputs generate no significant AC or DC currents as they transition. This parameter is guaranteed but not production tested.

#### **SWITCHING CHARACTERISTICS OVER OPERATING RANGE**

$T_A = -40^{\circ}C \text{ to } +85^{\circ}C. \text{ Vcc} = 5.0V \pm 10\%$

CLOAD = 50pF, RLOAD =  $500\Omega$  unless otherwise noted.

| Symbol | Parameter                                          | Min. | Тур. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|------|

| tplh   | Data Propagation Delays (1,2)                      | _    | 0.25 | _    |      |

| tphl   | A/B/C/D to Y, Y to A/B/C/D                         |      | 0.25 |      | ns   |

| tsec   | Clock Enable to Clock Setup Time                   | 3    | _    | _    | ns   |

| thec   | Clock Enable to Clock Hold Time                    | 0    | _    | _    | ns   |

| tcso   | Clock to Switch Turn-On Delay (3)                  | 0.5  | _    | 7    | ns   |

| taso   | Asynchronous Select to Switch Turn-On Delay (3)    | 0.5  | _    | 7    | ns   |

| tw     | Clock Pulse Width HIGH                             | 3    | _    | _    | ns   |

| tscs   | SEL to Clock Setup Time                            | 3    | _    | _    | ns   |

| tHCS   | SEL to Clock Hold Time                             | 0    | _    | _    | ns   |

| tpzl   | Asynchronous Enable to Switch Turn-On Delay (3)    | 1.5  | _    | 5.2  | ns   |

| tpzh   |                                                    |      |      |      |      |

| tplz   | Asynchronous Enable to Switch Turn-Off Delay (1,3) | 1.5  | _    | 4.8  | ns   |

| tphz   |                                                    |      |      |      |      |

#### NOTES:

- 1. This parameter is guaranteed but not production tested.

- 2. The bus switch contributes no propagation delay other than the RC delay of the ON resistance of the switch and the load capacitance. The time constant for the switch alone is of the order of 0.25ns for 50pF. Since this time constant is much smaller than the rise and fall times of typical driving signals, it adds very little propagation delay to the system. Propagation delay of the bus switch, when used in a system, is determined by the driving circuit on the driving side of the switch and its interaction with the load on the driven side.

- 3. Minimums guaranteed but not production tested.

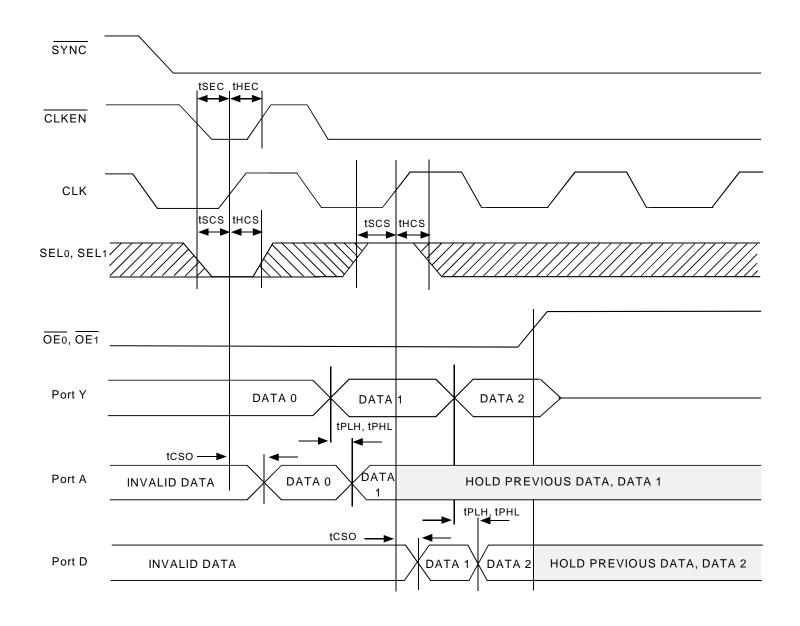

# TIMING WAVEFORMS - SYNCHRONOUS MODE, DEMUX FUNCTION

EXAMPLE: PORT A TO PORT D/PORT Y

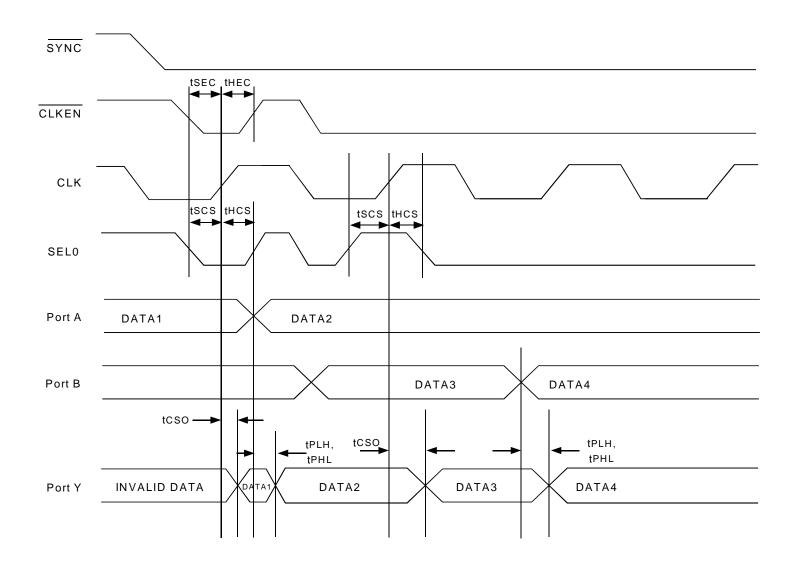

# **TIMING WAVEFORMS - SYNCHRONOUS MODE, MUX FUNCTION**

EXAMPLE: PORT A/PORT D TO PORT Y

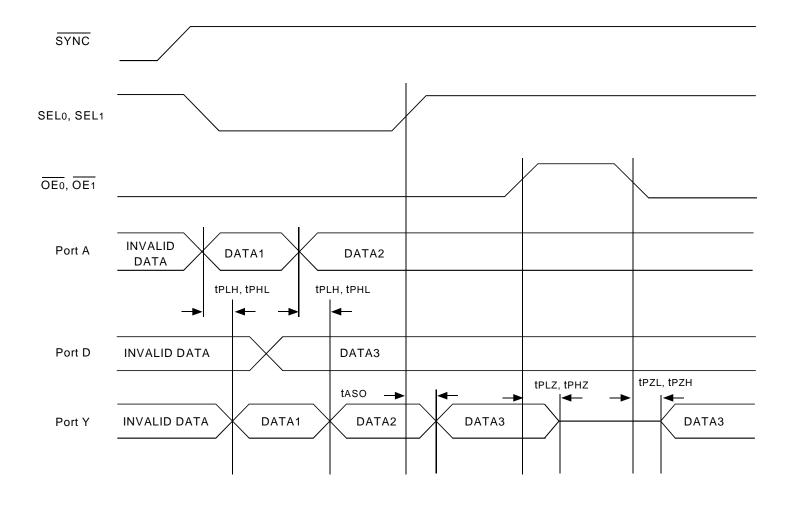

## **TIMING WAVEFORMS - ASYNCHRONOUS MODE, MUX FUNCTION**

EXAMPLE: PORT A/PORT DTO PORT Y

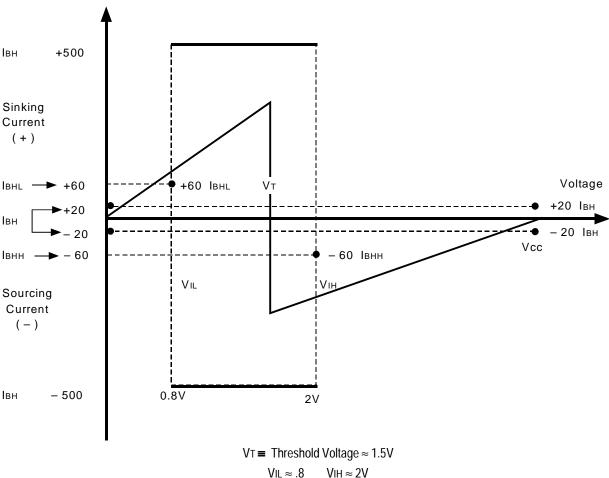

#### **ACTIVE TERMINATOR OR "BUS-HOLD" CIRCUIT**

The Active Terminator circuit, also known as the bus-hold circuit, is configured as a "weak latch" with positive feedback. When connected to a TTL or CMOS input port, the bus-hold circuit holds the last logic state at the input when the input is "disconnected" from the driver. When the output of a device connected to such an input attempts a logic level transition, it will overdrive the bus-hold circuit. The primary benefit of a bus-hold circuit is that it prevents CMOS inputs from floating, a situation which should be avoided to prevent spurious switching of inputs and unnecessary power dissipation. Bus-hold is a better solution than the traditional approach of using resistive termination to Vcc or GND to prevent bus floating, because the bus-hold circuit does not consume any static power.

#### V-I CHARACTERISTICS OF BUS-HOLD CIRCUIT

This figure shows the input V-I characteristics of a typical bus-hold implementation. The input characteristics resemble a resistor. As the input voltage is increased from 0 volts, the input "sink" current increases linearly. When the TTL threshold of the circuit is reached (typically 1.5 volts), the latch changes the logic state due to positive feedback and the direction of the current is reversed. As the input voltage is further increased towards Vcc, the input "source" current begins to decrease, reaching the lowest level at VIN = Vcc.

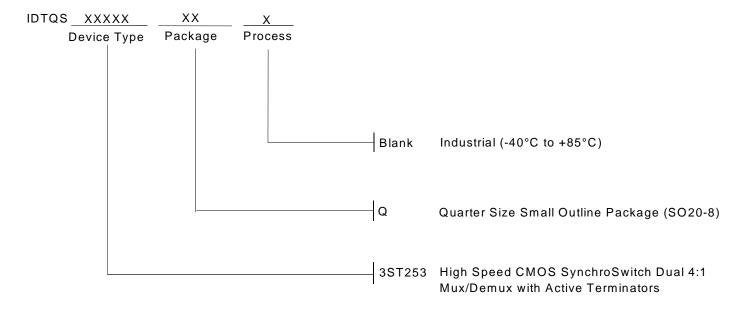

#### ORDERING INFORMATION

CORPORATE HEADQUARTERS 2975 Stender Way Santa Clara, CA 95054 for SALES: 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com\*