# 3.3V CMOS 12-BIT TO 24-BIT REGISTERED BUS EXCHANGER WITH 3-STATE OUTPUTS AND BUS-HOLD

# IDT74ALVCHR16270

# **FEATURES:**

- 0.5 MICRON CMOS Technology

- Typical tsk(0) (Output Skew) < 250ps

- ESD > 2000V per MIL-STD-883, Method 3015;

> 200V using machine model (C = 200pF, R = 0)

- 0.635mm pitch SSOP, 0.50mm pitch TSSOP, and 0.40mm pitch TVSOP packages

- Extended commercial range of 40°C to + 85°C

- $Vcc = 3.3V \pm 0.3V$ , Normal Range

- Vcc = 2.7V to 3.6V, Extended Range

- Vcc = 2.5V  $\pm$  0.2V

- CMOS power levels (0.4µW typ. static)

- Rail-to-Rail output swing for increased noise margin

### **Drive Features for ALVCHR16270:**

- Balanced Output Drivers: ±12mA

- Low switching noise

# **APPLICATIONS:**

- 3.3V High Speed Systems

- · 3.3V and lower voltage computing systems

### **DESCRIPTION:**

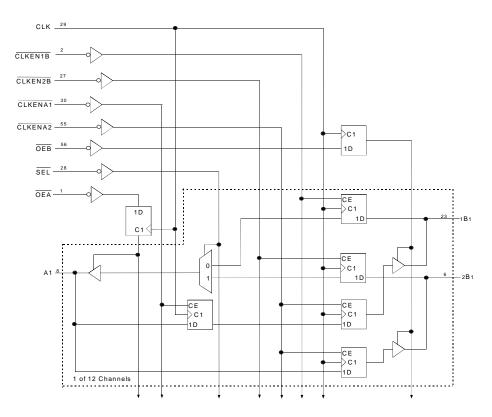

This registered bus exchanger is built using advanced dual metal

CMOS technology. The ALVCHR16270 is used in applications in which data must be transferred from a narrow high-speed bus to a wide lower-frequency bus.

This device provides synchronous data exchange between the two ports. Data is stored in the internal registers on the low-to-high transition of the clock (CLK) input when the appropriate clock-enable (CLKEN) inputs are low. The select (SEL) line selects 1B or 2B data for the A outputs. For data transfer in the A-to-B direction, a two-stage pipeline is provided in the A-to-1B path, with a single storage register in the A-to-2B path. Proper control of these inputs allows two sequential 12-bit words to be presented synchronously as a 24-bit word on the B-port. Data flow is controlled by the active-low output enables (OEA and OEB). The control terminals are registered to synchronize the bus-direction changes with CLK.

The ALVCHR16270 has series resistors in the device output structure which will significantly reduce line noise when used with light loads. This driver has been designed to drive  $\pm 12$ mA at the designated threshold levels.

The ALVCHR16270 has "bus-hold" which retains the inputs' last state whenever the input goes to a high impedance. This prevents floating inputs and eliminates the need for pull-up/down resistors.

### **FUNCTIONAL BLOCK DIAGRAM**

**EXTENDED COMMERCIAL TEMPERATURE RANGE**

**JUNE 1999**

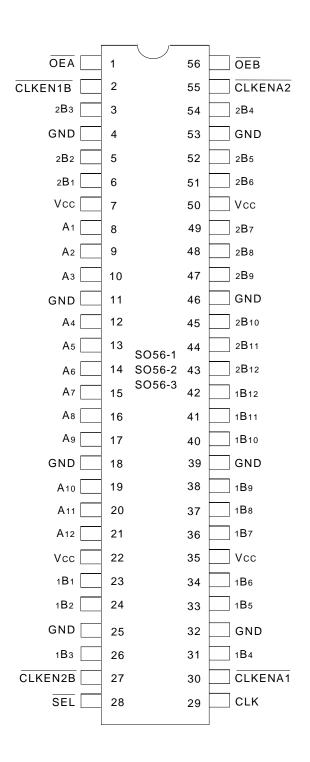

# PIN CONFIGURATION

SSOP/ TSSOP/TVSOP TOP VIEW

# FUNCTION TABLES (1) OUTPUT ENABLE

| Inputs |     |     | Outputs |          |  |

|--------|-----|-----|---------|----------|--|

| CLK    | OEA | OEB | Ax      | 1Bx, 2Bx |  |

| 1      | Н   | Н   | Z       | Z        |  |

| 1      | Н   | L   | Z       | Active   |  |

| 1      | L   | Н   | Active  | Z        |  |

| 1      | L   | L   | Active  | Active   |  |

# A-TO-B STORAGE ( $\overline{OEB} = L \text{ AND } \overline{OEA} = H$ )

|         | Inputs  |          |    |                    | puts               |

|---------|---------|----------|----|--------------------|--------------------|

| CLKENA1 | CLKENA2 | CLK      | Ах | 1Вх                | 2 <b>B</b> x       |

| L       | Н       | Χ        | Χ  | 1Bo <sup>(2)</sup> | 2Bo <sup>(2)</sup> |

| L       | Н       | Χ        | χ  | 1Bo <sup>(2)</sup> | 2Bo <sup>(2)</sup> |

| L       | L       | <b>↑</b> | L  | L <sup>(3)</sup>   | L                  |

| L       | L       | <b>↑</b> | Н  | H <sup>(3)</sup>   | Н                  |

| Н       | L       | <b>↑</b> | L  | 1Bo <sup>(2)</sup> | L                  |

| Н       | L       | <b>↑</b> | Н  | 1Bo <sup>(2)</sup> | Н                  |

| Н       | Н       | Χ        | Χ  | 1Bo <sup>(2)</sup> | 2Bo <sup>(2)</sup> |

# B-TO-A STORAGE ( $\overline{OEA} = L$ AND $\overline{OEB} = H$ )

|         | Inputs  |     |     |     |              |                   |  |  |

|---------|---------|-----|-----|-----|--------------|-------------------|--|--|

| CLKEN1B | CLKEN2B | CLK | SEL | 1Вх | 2 <b>B</b> x | Ах                |  |  |

| Н       | Χ       | Χ   | Н   | Χ   | Χ            | Ao <sup>(2)</sup> |  |  |

| Х       | Н       | Х   | L   | Χ   | Χ            | Ao <sup>(2)</sup> |  |  |

| L       | Х       | 1   | Н   | L   | Χ            | L                 |  |  |

| L       | Χ       | 1   | Н   | Н   | Χ            | Н                 |  |  |

| X       | L       | 1   | L   | Χ   | L            | L                 |  |  |

| Х       | L       | 1   | L   | Χ   | Н            | Н                 |  |  |

### NOTES:

- 1. H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Don't Care

- Z = High-Impedance

- ↑ = LOW-to-HIGH Transition

- 2. Output level before the indicated steady-state input conditions were established.

- 3. Two CLK edges are needed to propagate data.

# PIN DESCRIPTION

| Pin Names | I/O | Description                                                                                              |

|-----------|-----|----------------------------------------------------------------------------------------------------------|

| Ax(1:12)  | I/O | Bidirectional Data Port A. Usually connected to the CPU's Address/Data bus. <sup>(1)</sup>               |

| 1BX(1:12) | I/O | Bidirectional Data Port 1B. Usually connected to the even path or even bank of memory. (1)               |

| 2BX(1:12) | I/O | Bidirectional Data Port 2B. Usually connected to the odd path or odd bank of memory. (1)                 |

| CLK       |     | Clock Input                                                                                              |

| CLKENA1   | I   | Clock Enable Input for the A-1B Register. If CLKENA1 is LOW during the rising edge of CLK, data will be  |

|           |     | clocked into register A-1B (Active LOW).                                                                 |

| CLKENA2   | I   | Clock Enable Input for the A-2B Register. If CLKENA2 is LOW during the rising edge of CLK, data will be  |

|           |     | clocked into register A-2B (Active LOW).                                                                 |

| CLKEN1B   | I   | Clock Enable Input for the 1B-A Register. If CLKEN1B is LOW during the rising edge of CLK, data will be  |

|           |     | clocked into register 1B-A (Active LOW).                                                                 |

| CLKEN2B   | I   | Clock Enable Input for the 2B-A Register. If CLKEN2B is LOW during the rising edge of CLK, data will be  |

|           |     | clocked into register 2B-A (Active LOW).                                                                 |

| SEL       | I   | 1B or 2B Port Selection. When HIGH during the rising edge of CLK, SEL enables data transfer from 1B Port |

|           |     | to A Port. When LOW during the rising edge of CLK, SEL enables data transfer from 2B Port to A Port.     |

| OEA       | I   | Synchronous Output Enable for A Port (Active LOW)                                                        |

| OEB       | I   | Synchronous Output Enable for B Port (Active LOW)                                                        |

#### NOTE:

These pins have "Bus-Hold." All other pins are standard inputs, outputs, or I/Os.

# ABSOLUTE MAXIMUM RATING (1)

| Symbol                | Description                      | Max.           | Unit |

|-----------------------|----------------------------------|----------------|------|

| VTERM <sup>(2)</sup>  | Terminal Voltage                 | - 0.5 to + 4.6 | ٧    |

|                       | with Respect to GND              |                |      |

| V <sub>TERM</sub> (3) | Terminal Voltage                 | – 0.5 to       | ٧    |

|                       | with Respect to GND              | Vcc + 0.5      |      |

| Tstg                  | Storage Temperature              | - 65 to + 150  | °C   |

| lout                  | DC Output Current                | - 50 to + 50   | mA   |

| lik                   | Continuous Clamp Current,        | ± 50           | mA   |

|                       | VI < 0 or VI > VCC               |                |      |

| Іок                   | Continuous Clamp Current, Vo < 0 | - 50           | mA   |

| Icc                   | Continuous Current through       | ±100           | mA   |

| Iss                   | each Vcc or GND                  |                |      |

#### NOTES:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Vcc terminals.

3. All terminals except Vcc.

# **CAPACITANCE** (TA = $+25^{\circ}$ C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Тур. | Max. | Unit |

|--------|--------------------------|------------|------|------|------|

| CIN    | Input Capacitance        | VIN = 0V   | 5    | 7    | pF   |

| Соит   | Output<br>Capacitance    | Vout = 0V  | 7    | 9    | pF   |

| CI/O   | I/O Port<br>Capacitance  | VIN = 0V   | 7    | 9    | pF   |

NOTE:

1. As applicable to the device type.

NEW16linl

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA = - 40°C to +85°C

| Symbol      | Parameter                      | Test Co                    | onditions | Min. | Typ. <sup>(1)</sup> | Max.  | Unit |

|-------------|--------------------------------|----------------------------|-----------|------|---------------------|-------|------|

| <b>V</b> IH | Input HIGH Voltage Level       | Vcc = 2.3V to 2.7V         |           | 1.7  | _                   | _     | V    |

|             |                                | Vcc = 2.7V to 3.6V         |           | 2    | _                   | _     |      |

| VIL         | Input LOW Voltage Level        | Vcc = 2.3V to 2.7V         |           | _    | _                   | 0.7   | V    |

|             |                                | Vcc = 2.7V to 3.6V         |           | _    | _                   | 0.8   |      |

| IH          | Input HIGH Current             | Vcc = 3.6V                 | VI = VCC  | _    | _                   | ± 5   | μA   |

| IL          | Input LOW Current              | Vcc = 3.6V                 | VI = GND  | _    | _                   | ± 5   |      |

| OZH         | High Impedance Output Current  | Vcc = 3.6V                 | Vo = Vcc  | _    | _                   | ± 10  | μΑ   |

| OZL         | (3-State Output pins)          |                            | Vo = GND  | _    | _                   | ± 10  | μA   |

| /ıĸ         | Clamp Diode Voltage            | VCC = 2.3V, IIN = - 18mA   |           | _    | - 0.7               | - 1.2 | V    |

| <b>/</b> H  | Input Hysteresis               | Vcc = 3.3V                 |           | _    | 100                 | _     | mV   |

| CCL         | Quiescent Power Supply Current | Vcc = 3.6V                 |           | _    | 0.1                 | 40    | μΑ   |

| CCH         |                                | VIN = GND or VCC           |           |      |                     |       |      |

| CCZ         |                                |                            |           |      |                     |       |      |

| ∆lcc        | Quiescent Power Supply         | One input at Vcc - 0.6V,   |           | _    | _                   | 750   | μΑ   |

|             | Current Variation              | other inputs at Vcc or GND |           |      |                     |       |      |

#### NOTE:

1. Typical values are at Vcc = 3.3V, +25°C ambient.

# **BUS-HOLD CHARACTERISTICS**

| Symbol       | Parameter <sup>(1)</sup>         | Test Conditions |                       | Min. | Тур. <sup>(2)</sup> | Max.  | Unit |

|--------------|----------------------------------|-----------------|-----------------------|------|---------------------|-------|------|

| Івнн         | Bus-Hold Input Sustain Current   | Vcc = 3.0V      | VI = 2.0V             | - 75 | _                   | _     | μA   |

| IBHL         |                                  |                 | VI = 0.8V             | 75   | _                   | _     |      |

| Івнн         | Bus-Hold Input Sustain Current   | Vcc = 2.3V      | V <sub>I</sub> = 1.7V | - 45 | _                   | _     | μA   |

| <b>I</b> BHL |                                  |                 | VI = 0.7V             | 45   | _                   | _     |      |

| Івнно        | Bus-Hold Input Overdrive Current | Vcc = 3.6V      | VI = 0 to 3.6V        | _    | _                   | ± 500 | μA   |

| Івньо        |                                  |                 |                       |      |                     |       |      |

#### **NOTES**

1. Pins with Bus-hold are identified in the pin description.

2. Typical values are at Vcc = 3.3V, +25°C ambient.

# **OUTPUT DRIVE CHARACTERISTICS**

| Symbol | Parameter           | Test               | Conditions <sup>(1)</sup> | Min.      | Max. | Unit |

|--------|---------------------|--------------------|---------------------------|-----------|------|------|

| Vон    | Output HIGH Voltage | Vcc = 2.3V to 3.6V | IOH = - 0.1mA             | Vcc - 0.2 | _    | V    |

|        |                     | Vcc = 2.3V         | IOH = -4mA                | 1.9       | _    |      |

|        |                     |                    | IOH = -6mA                | 1.7       | _    |      |

|        |                     | Vcc = 2.7V         | IOH = -4mA                | 2.2       | _    | 1    |

|        |                     |                    | IOH = -8mA                | 2         | -    | 1    |

|        |                     | Vcc = 3.0V         | IOH = -6mA                | 2.4       | _    |      |

|        |                     |                    | Ioн = - 12mA              | 2         |      | 1    |

| Vol    | Output LOW Voltage  | Vcc = 2.3V to 3.6V | IoL = 0.1mA               | _         | 0.2  | V    |

|        |                     | Vcc = 2.3V         | IoL = 4mA                 | _         | 0.4  |      |

|        |                     |                    | IoL = 6mA                 | _         | 0.55 | 1    |

|        |                     | Vcc = 2.7V         | IoL = 4mA                 | _         | 0.4  | 1    |

|        |                     |                    | IoL = 8mA                 | _         | 0.6  |      |

|        |                     | Vcc = 3.0V         | IoL = 6mA                 | _         | 0.55 | 1    |

|        |                     |                    | IoL = 12mA                | _         | 0.8  | 1    |

#### NOTE:

1. V<sub>IH</sub> and V<sub>IL</sub> must be within the min. or max. range shown in the DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE table for the appropriate V<sub>CC</sub> range. T<sub>A</sub> = − 40°C to + 85°C.

# OPERATING CHARACTERISTICS, $T_A = 25^{\circ}C$

|        |                               |                                 | Vcc = 2.5V ± 0.2V | Vcc = 3.3V ± 0.3V |      |

|--------|-------------------------------|---------------------------------|-------------------|-------------------|------|

| Symbol | Parameter                     | Test Conditions                 | Typical           | Typical           | Unit |

| CPD    | Power Dissipation Capacitance | C <sub>L</sub> = 0pF, f = 10Mhz | _                 | _                 | pF   |

|        | Outputs enabled               |                                 |                   |                   | þΓ   |

| CPD    | Power Dissipation Capacitance |                                 | _                 | _                 |      |

|        | Outputs disabled              |                                 |                   |                   | pF   |

# **SWITCHING CHARACTERISTICS (1)**

|              |                                                          | Vcc = 2. | 5V ± 0.2V | Vcc = | : 2.7V | $Vcc = 3.3V \pm 0.3V$ |      |      |

|--------------|----------------------------------------------------------|----------|-----------|-------|--------|-----------------------|------|------|

| Symbol       | Parameter                                                | Min.     | Max.      | Min.  | Max.   | Min.                  | Max. | Unit |

| tplh         | Propagation Delay                                        | 2.5      | 6.9       | _     | 6.4    | 1.7                   | 5.6  | ns   |

| <b>t</b> PHL | CLK to xBx                                               |          |           |       |        |                       |      |      |

| tplh         | Propagation Delay                                        | 2.2      | 6.4       | _     | 6      | 1.6                   | 5.2  | ns   |

| tphl         | CLK to Ax                                                |          |           |       |        |                       |      |      |

| tplh         | Propagation Delay                                        | 2.4      | 7.2       | _     | 7      | 1.6                   | 6    | ns   |

| tphl         | SEL to Ax                                                |          |           |       |        |                       |      |      |

| tpzh         | Output Enable Time                                       | 2.1      | 7.9       | _     | 7.4    | 1.6                   | 6.5  | ns   |

| tpzl         | CLK to Ax or Bx                                          |          |           |       |        |                       |      |      |

| tphz         | Output Disable Time                                      | 3        | 7.8       | _     | 7.1    | 1.7                   | 6.2  | ns   |

| tplz         | CLK to Ax or Bx                                          |          |           |       |        |                       |      |      |

| tsu          | Setup Time, Ax data before CLK↑                          | 4.1      | _         | 3.8   | 1      | 3.1                   | _    | ns   |

| tsu          | Setup Time, Bx data before CLK↑                          | 0.9      | _         | 1.2   | I      | 0.9                   | _    | ns   |

| tsu          | Setup Time, CLKENA1 or CLKENA2 before CLK↑               | 3.5      | _         | 3.2   |        | 2.7                   | _    | ns   |

| tsu          | Setup Time, CLKEN1B or CLKEN2B before CLK↑               | 3.4      | _         | 3     | _      | 2.6                   | _    | ns   |

| tsu          | Setup Time, <del>OEB</del> or <del>OEA</del> before CLK↑ | 4.4      | _         | 3.9   | _      | 3.2                   | _    | ns   |

| tн           | Hold Time, Ax data after CLK↑                            | 0        | _         | 0     |        | 0.2                   | _    | ns   |

| tн           | Hold Time, Bx data after CLK↑                            | 1.4      | _         | 1     |        | 1.7                   | _    | ns   |

| tн           | Hold Time, CLKENA1 or CLKENA2 after CLK↑                 | 0        | _         | 0.1   | ı      | 0.3                   | _    | ns   |

| tн           | Hold Time, CLKEN1B or CLKEN2B after CLK↑                 | 0        | _         | 0     | _      | 0.6                   | _    | ns   |

| tн           | Hold Time, OEB or OEA after CLK↑                         | 0        |           | 0     | _      | 0.1                   | _    | ns   |

| tw           | Pulse Width, CLK HIGH or LOW                             | 3.3      | _         | 3.3   |        | 3.3                   | _    | ns   |

| tsk(o)       | Output Skew <sup>(2)</sup>                               | _        | _         | _     | _      | _                     | 500  | ps   |

### NOTES:

- 1. See test circuits and waveforms.  $TA = -40^{\circ}C$  to  $+85^{\circ}C$ .

- 2. Skew between any two outputs of the same package and switching in the same direction.

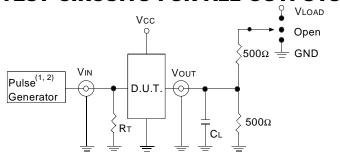

# **TEST CIRCUITS AND WAVEFORMS:**

### **TEST CONDITIONS**

| Symbol     | $Vcc^{(1)} = 3.3V \pm 0.3V$ | Vcc <sup>(1)</sup> = 2.7V | $Vcc^{(2)} = 2.5V \pm 0.2V$ | Unit      |

|------------|-----------------------------|---------------------------|-----------------------------|-----------|

| VLOAD      | 6                           | 6                         | 2 x Vcc                     | ٧         |

| VIH        | 2.7                         | 2.7                       | Vcc                         | ٧         |

| <b>V</b> T | 1.5                         | 1.5                       | Vcc / 2                     | ٧         |

| VLZ        | 300                         | 300                       | 150                         | mV        |

| VHZ        | 300                         | 300                       | 150                         | mV        |

| CL         | 50                          | 50                        | 30                          | pF        |

|            |                             |                           |                             | NEW16link |

# **TEST CIRCUITS FOR ALL OUTPUTS**

**DEFINITIONS:**

ALVC Link

CL= Load capacitance: includes jig and probe capacitance. RT= Termination resistance: should be equal to ZOUT of the Pulse

Generator.

#### NOTES:

- 1. Pulse Generator for All Pulses: Rate  $\leq$  10MHz; tF  $\leq$  2.5ns; tR  $\leq$  2.5ns.

- 2. Pulse Generator for All Pulses: Rate  $\leq$  10MHz; tF  $\leq$  2ns; tR  $\leq$  2ns.

### SWITCH POSITION

| Switch |

|--------|

| Vload  |

|        |

|        |

| GND    |

|        |

| Open   |

|        |

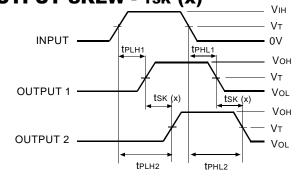

OUTPUT SKEW - TSK (x)

tsk(x) = |tplh2 - tplh1| or |tphl2 - tphl1|

ALVC Link

### NOTES:

- 1. For tsk(o) OUTPUT1 and OUTPUT2 are any two outputs.

- 2. For tsk(b) OUTPUT1 and OUTPUT2 are in the same bank.

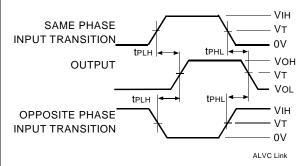

# PROPAGATION DELAY

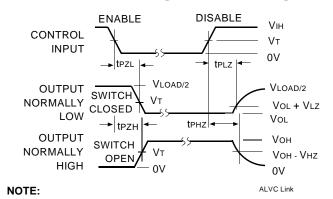

### **ENABLE AND DISABLE TIMES**

Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

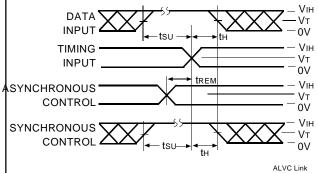

# SET-UP, HOLD, AND RELEASE TIMES

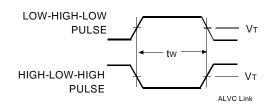

# **PULSE WIDTH**

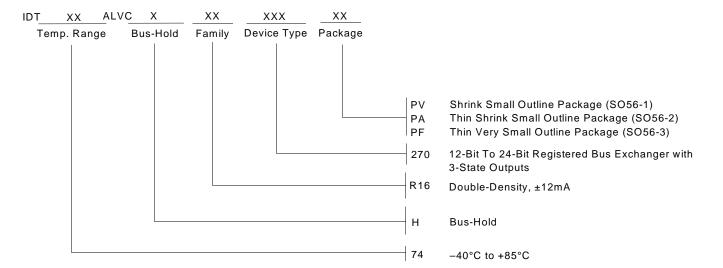

# ORDERING INFORMATION

CORPORATE HEADQUARTERS

2975 Stender Way Santa Clara, CA 95054 for SALES:

800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com\*

\*To search for sales office near you, please click the sales button found on our home page or dial the 800# above and press 2.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.