# A 42V Inverter/Rectifier for ISA using Discrete Semiconductor Components

Anthony F. J. Murray, Peter Wood, Neeraj Keskar, Jingdong Chen & Alberto Guerra – International Rectifier

As presented at Future Transportation Technology Conference, August 2001

**ABSTRACT:** A demonstration inverter has been built to illustrate the feasibility of implementing an ISA inverter in a 42V automotive powernet using discrete semiconductor switches. The component count is the same as a module solution and it is felt that with suitable heat-sinking etc, the discrete solution will be more cost effective and reliable than a module solution. For a 10kW inverter, the current carrying requirements of each switch is about 400A peak.

#### 1. Introduction.

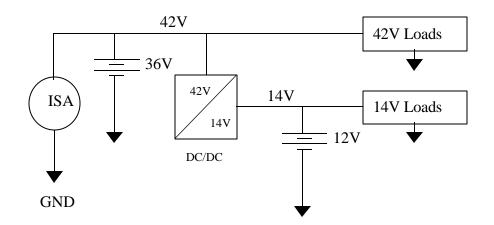

The advent of a 42V bus system for future automobile designs allows a key advantage over existing 14V systems – ease of integration of the starter motor and alternator into one machine. This has led to the development of an Integrated Starter Alternator (ISA) system, which will be primarily responsible for power management in the new 42V automobile. A principle component of the 42V ISA system will be a three-phase inverter/rectifier, responsible for supplying power to the 42V loads and charging the 36V battery (rectifier), and supplying power to the starter motor during starting (inverter). A possible topology is shown in figure 1. For a 10kW system, the current carrying capability of each switch in the inverter must be in the region of 400A peak.

Detailed calculations have shown that a module solution is possible using two die in parallel per switch (IRFC2907, 75V, 3.3m max,  $60mm^2$ ). This assumes adequate heat-sinking and wirebonds to carry the required current. In the case of a discrete solution using the same die, the current will be limited by the current carrying capability of the package (e.g. 95A for a TO-247), resulting in the requirement of more die in parallel per switch. The paper addresses this problem by implementing the inverter/rectifier using discrete components (2 per switch) in a new package developed specifically for high current applications [1, 2]. The paper demonstrates operation of the FETs up to 416A peak output current. A detailed model is used to predict operation at higher frequencies and the trade-offs in a more practical system are discussed.

Figure 1. Possible implementation of a 42V topology in an automotive system. The Inverter/Rectifier sits between the ISA machine and the 42V bus.

# International

### 2. System Design

2.1 Component and Package Selection.

Currently, auto systems manufacturers are still engaged in the design of ISA systems for the 42V vehicle, with first production releases ranging from the years 2003 to 2005. Although some manufacturers are designing higher power systems, 10kW is a reasonable estimate of the peak power requirements. This translates to about 400A peak current requirement for the inverter switches. A FET breakdown voltage of 75V was chosen to allow sufficient headroom above the nominal 42V bus during switching. Although the FET is rated under repetitive avalanche conditions up to the maximum junction temperature  $(T_{jmax} = 175^{\circ}C)$ , the 75V breakdown voltage will also minimize avalanche energy dissipation (the repetitive avalanche rating and it's effects are discussed separately in [3]). The FET chosen for the inverter was an IRFC2907 die  $(75V, 3.3m \text{ max}, 60mm^2)$  in a new high current package known as SuperTab<sup>TM</sup> [1, 2].

The new SuperTab<sup>TM</sup> package has a continuous current carrying capability of 300A. In this case, the rating exceeds the die rated current (209A continuous at room temperature). The die free package resistance is about 0.2m typical (as opposed to about 1m in a TO-247 package), resulting in a maximum  $R_{DS(on)}$  specification of about 3.5m for the packaged device. Hence, with careful layout and design, any additional parasitics over the module solution can be kept to a minimum. 2.2 Inverter Layout and Heatsink Design.

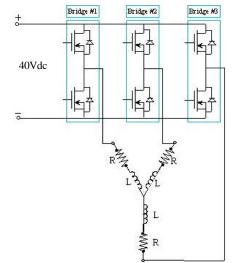

Figure 2a) shows a schematic of the inverter. The 40Vdc is supplied by a rectified three-phase 480Vac supply. Each switch in the schematic is implemented using two FETs in parallel. A passive R-L load was used since a low voltage motor with a suitable power rating was unavailable.

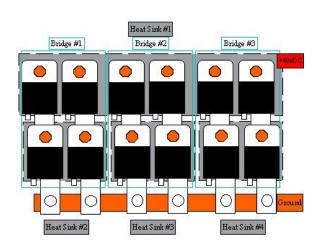

Figure 2b) shows the heatsink arrangement. The SuperTab<sup>TM</sup> package has been designed so that it can be bolted directly to a laminated copper bus bar. Hence, all six drains of the high side FETs are bolted directly to one heatsink, with a connection to the positive terminal of the DC link capacitors. Each phase is connected to a separate heatsink, containing two low side FETs as shown in figure 2b). The ground is completed by a copper bus bar connected to the source of the low side devices.

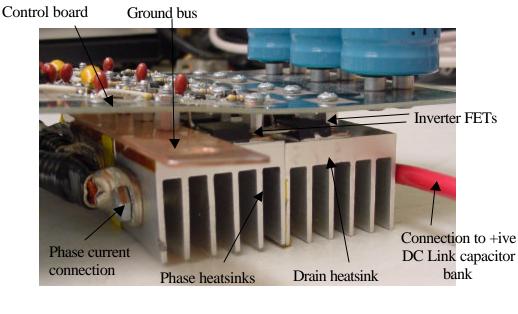

The FETs are driven by an IR2130 three-phase bridge driver, suitably buffered at the outputs. The inverter is controlled by a commercial PWM controller. Note that the drive circuitry sits on top of the heatsink arrangement and does not carry any high current. A photo of the inverter system is shown in figure 2c). The heatsink is cooled by forced air convection.

Figure 2a). Inverter schematic.

Figure 2b). FET arrangement on heatsinks.

# International

Figure 2c). Photo of inverter demo and SuperTab<sup>™</sup> FET.

## 3. Measured Results

The inverter was PWM controlled at a carrier frequency of 1.5kHz and modulating signal of 50Hz. The input power was measured for various currents and the output (real) power was calculated by integrating the voltage and current in one phase, namely,

$$P_A = \frac{3}{T} \int_0^T v_p(t) \cdot i_p(t) dt$$

[1]

The temperature of the heatsink is measured at each power level. Table 1 summarizes the results. Since the load was almost purely reactive, the real power delivered to the load was very small and losses are somewhat academic, with a power factor of about 0.17. However, the principle aim here was to demonstrate the current carrying capability of the FETs. Full characterization of real losses at various frequencies will be performed on a prototype system with a water-cooled heatsink and motor load.

| Input     | Phase Peak  | Phase RMS   | Real Output | Power    | Tsink ( <sup>°</sup> C ) | Tj ( <sup>°</sup> C ) |

|-----------|-------------|-------------|-------------|----------|--------------------------|-----------------------|

| Power (W) | Current (A) | Current (A) | Power (W)   | Loss (W) | . ,                      |                       |

| 48.36     | 72          | 45.76       | 30          | 18.36    | 26.5                     | 27.295                |

| 96.48     | 103.8       | 67.28       | 36          | 60.48    | 30                       | 32.56                 |

| 144       | 121.8       | 79.36       | 48          | 96       | 33                       | 37                    |

| 286.56    | 185         | 114         | 105         | 181.56   | 40                       | 47.695                |

| 475.2     | 227         | 145.4       | 165         | 310.2    | 52                       | 63.775                |

| 786       | 276.5       | 181.8       | 330         | 456      | 65                       | 82                    |

| 1520.96   | 416         | 271.4       | 420         | 1100.96  | 117                      | 162.62                |

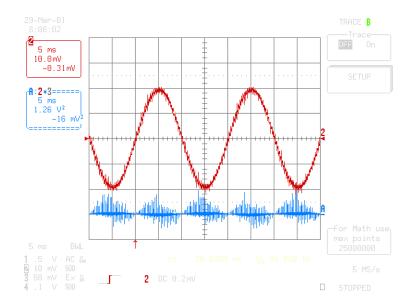

Figure 3 shows the instantaneous output power and corresponding phase current of 416A peak. The air flow through the heatsink was measured at about 1300ft/min. Using the values in Table 1, the sink-ambient thermal resistance is estimated to be  $0.5^{\circ}$ C/W. Hence, the estimated rise in junction temperature is also calculated and recorded in Table 1.

Figure 3. Output phase current (curve 2, 200A/div) and power (curve A, 200W/div).

#### 4. Modeling

The junction temperature and losses were estimated using a detailed inverter model described in [4]. MOSFET and diode parameters are obtained from extensive FET measurements. The model then accurately calculates both MOSFET and diode switching and conduction losses. The results in table 2 were estimated using the model.

| f (kHz) | I RMS phase<br>(A) | Total FET losses (W) |           | Total Diode Loss (W) |           | Total Losses<br>(W) | Tj (C ) |

|---------|--------------------|----------------------|-----------|----------------------|-----------|---------------------|---------|

|         | (,,)               | Conduction           | Switching | Conduction           | Switching | ()                  |         |

| 1.5     | 45.76              | 8.04                 | 3.96      | 46.26                | 0.06      | 58.32               | 32.3    |

| 1.5     | 67.28              | 17.64                | 5.76      | 74.52                | 0.06      | 97.98               | 37.25   |

| 1.5     | 79.36              | 25.08                | 6.78      | 92.58                | 0.06      | 124.5               | 40.56   |

| 1.5     | 114                | 66.12                | 10.26     | 168.12               | 0.12      | 244.62              | 55.58   |

| 1.5     | 145.4              | 110.7                | 12.66     | 228.66               | 0.12      | 352.14              | 69.02   |

| 1.5     | 181.8              | 189.36               | 15.36     | 310.56               | 0.18      | 515.46              | 89.44   |

| 1.5     | 271.4              | 717.12               | 23.16     | 602.64               | 0.24      | 1343.16             | 192.89  |

| 12      | 45.76              | 8.34                 | 32.1      | 46.26                | 0.36      | 87.06               | 35.88   |

| 12      | 67.28              | 18.54                | 46.14     | 74.52                | 0.54      | 139.74              | 42.47   |

| 12      | 79.36              | 26.52                | 54.24     | 92.58                | 0.6       | 173.94              | 46.75   |

| 12      | 114                | 71.52                | 82.32     | 168.12               | 0.96      | 322.92              | 65.37   |

| 12      | 145.4              | 121.02               | 101.04    | 228.66               | 1.14      | 451.86              | 81.49   |

| 12      | 181.8              | 209.16               | 123.06    | 310.56               | 1.44      | 644.22              | 105.53  |

| 12      | 271.4              | 804.78               | 185.16    | 602.64               | 2.16      | 1594.74             | 224.34  |

Table 2. Simulation results.

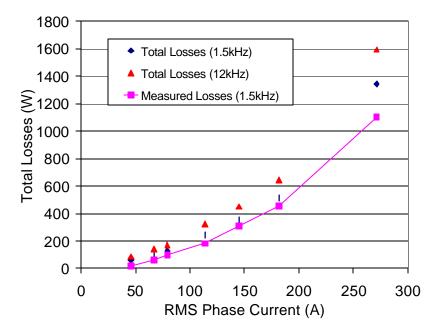

Figure 4 plots total losses versus RMS phase current. The analysis has also been extended to a higher frequency of 12kHz. We can see that diode switching losses are negligible and diode conduction losses are predicted to be extremely high. This is due to the low power factor. A higher power factor of say 0.9 would cause diode conduction losses to decrease significantly, but FET conduction losses would correspondingly rise, resulting in comparable total losses (within about 10%).

At 1.5kHz, conduction losses are larger than switching losses at all currents. At 12kHz, switching losses dominate at lower currents and conduction losses begin to dominate at higher currents. Also plotted in figure 4 are the measured losses at 1.5kHz. At higher currents, where conduction losses dominate, the model is accurate to about 15%. Larger inaccuracies are experienced at lower currents due to the increase in switching losses.

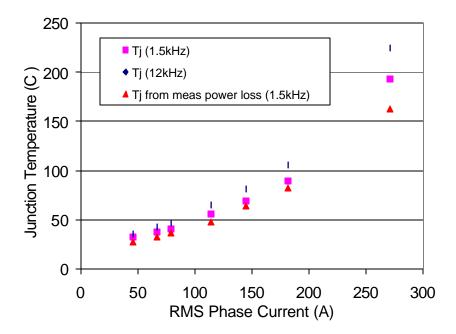

Figure 5 plots the model predicted junction temperature versus RMS phase current. Also plotted is the junction temperature rise predicted from the measured power loss at 1.5kHz (see table 1). At 1.5kHz, 271.4Arms, the model predicts the junction temperature to be about 193°C. The value calculated from the measured power loss is 163°C. The discrepancy is due to overestimation of the power losses in the model. We can clearly see that at 12kHz, even accounting for the inaccuracy of the model, it will not be possible to run at 271.4Arms on the existing heatsink. The additional increase in junction temperature is due primarily to the increased switching loss. Note that conduction losses also slightly increase due to the increased temperature effect on  $R_{DS(on)}$ .

Figure 4. Total losses versus RMS phase current.

Figure 5. Predicted junction temperature versus RMS phase current.

#### 5. Conclusions

A demonstration inverter for a 42V ISA system has been realized. The inverter FETs were shown to operate at 416A peak at 1.5kHz. Measurements are in reasonable agreement with an analytical model. The model was used to predict operation at higher frequencies. It is concluded that operation at higher frequencies will require a liquid cooled heatsink.

Feasibility to design an inverter/rectifier for a 42V ISA system with <u>discrete</u> semiconductor <u>components</u>, using the same number of components as a module solution, has been demonstrated. Even accounting for the incremental package cost, it is thought that the discrete solution will be more costeffective and reliable than the module solution.

## 6. Future Work

Characterization of the FETs over the full frequency range needs to be carried out using a real motor load and a liquid cooled heatsink. This will allow prediction of the optimum operating point in the real system.

# References.

P. Dugdale & A. Woodworth, "SuperTab<sup>™</sup>: A Novel High Current Semiconductor Switch Package," Proceedings PCIM, Chicago, Nov 1999.

P. Dugdale & A. Woodworth, "Current Handling and Thermal Considerations in a High Current Semiconductor Switch Package," Proceedings APEC, pp. 284-289, New Orleans, Feb 2000.

A. F. J. Murray, T. McDonald, H. Davis, J. Cao,& K. Spring, "Extremely Rugged MOSFET Technology with Ultra Low R<sub>DS(on)</sub> Specified for a

Broad Range of  $E_{AR}$  Conditions," Proceedings of Powersystems World 2000, pp. 105-114, Boston, Oct 2000.

[4] S. Clemente, B. Pelly, "An Algorithm for the Selection of the Optimum Power Device for the Electric Vehicle Propulsion," IEEE Workshop on Power Electronics in Transportation, Oct 1992.