DT 94-6AJ

INTERNATIONAL RECTIFIER · APPLICATION ENG · 233 KANSAS ST. · EL SEGUNDO, CA.90245 · TEL(310)322-3331 · FAX(310)322-3332

### IGBT の並列動作

By Donald A. Dapkus

訳 アイアールファーイースト株式会社

パワーMOSFETは正の温度係数をもつ事により並列で非常に良く機能します。IGBTはパワーMOSFETとBJTを組み合わせたものですが、温度係数が負だとも、また正だとも単純に言い表わすことはできません。温度係数はIGBTを設計する際に用いられる技術により異なり、また同じ技術でも電流密度により変化します。以下に簡単なガイドラインを示しますが、これは並列IGBTを設計する上で参考になると思います。

本 Design Tipには次のような目的があります。

- 1. IGBTの並列化についての一般的な検討を行う。

- 2. 電流、温度不平衡に対するサーマルカップリングの効果を検討する。

- 3. より良い共有を行うために、素子の選択方法を検討し、IR社の600V高速 IGBTの性能を比較する。

- 4. IR 社の 600V 超高速 IGBT の性能を比較する。

- 5. 複数(2以上)の並列 IGBT の設計を検討する。

IGBTの並列化についての予備知識は、参考[1]のセクション VIII にあります。

#### 1. 一般的考察

半導体の並列化は小さなことではありません。IGBTの並列化を成功させるために検討しなければならない事項には、ゲート回路、レイアウト、素子間における電流の不平衡、温度の不平衡があります。並列化により伝導損やケースへの接合熱抵抗を減らすことが出来ます。しかし、スイッチング損は同レベルか、また高くなる場合もあります。そうした損失が大きい場合、並列化により図れる改善はほんのわずかだけです。並列化は小さな素子が低価格であることの利点を活かそうとするものですが、技術的な問題点を十分に検討することなく行ってはなりません。また製造公差が極端な場合は、実験結果を入手しなければなりません。

ゲート回路

次ぎに示すものは、MOSゲートのパワートランジスタの設計における寄生振動の除去についてのアドバイスです。

- 1. IGBT または MOSFET のゲートが実質的なインピーダンスが小さな stiff (電圧) source を調べるよう にする。このアドバイスは同様に並列化した素子および単一素子の設計にも当てはまります。

- 2. 並列の各素子上では、少なくとも10オームのゲート絶縁抵抗を使用する。抵抗を物理的に素子の実際のゲートリード線の近くに置く。

- 3. ゲート駆動回路のツェナーダイオードは振動を起こすことがあります。ツェナーダイオードを直接エミッタ / ソースへのゲートに置きゲート過電圧を制御することは行わず、代わりに必要な場合は、ツェナーダイオードをゲート絶縁抵抗の駆動側に置く。

- 4. ゲート駆動回路のコンデンサーも振動を起こすことがあります。コンデンサーを直接エミッター/ソー スへのゲートに置きスイッチング時間を制御することは行わず、代わりにゲート絶縁抵抗を上げる。

- コンデンサーはスイッチングを遅らせるため、素子間のスイッチング不平衡が上昇します。

#### レイアウトについての考察

回路の物理的なレイアウトは、電流および周波数と共にその重要度が高まります。十分な努力を行い、漂遊インダクタンスを絶対的に最小にしなければなりません。レイアウトがきちんとしていないと、電圧のオーバーシュート、スイッチング性能および導通性能の低下のような問題が起きる可能性があります。レイアウトは、動作周波数および/あるいは電流が上昇するに従いできるだけ実際的に隙間が無く、コンパクトで対称的なものとし、キャパシタンスの分布を漂遊回路インダクタンスから切り離すようにしなければなりません。特に重要なのが、ゲート駆動リターンループにおける漂遊インダクタンスです。これにより IGBT ゲートには、予想以上の異なる電圧が出ることが分かります。40ページの参考[2]と参考[3]では、レイアウトがお粗末であったり、ゲート駆動が不適切である場合に起きる問題が幾つか述べられています。

### 不平衡電流対温度

パワー半導体を並列化する場合、最初に思い浮かぶ問題は合計電流をいかに共有するかということです。しかし、半導体は電流より温度に対しより敏感なため、真の問題はいかに接合温度近辺で整合させるかということと、素子の一つが定格接合温度に近づいているかどうかということです。接合温度は直接的に信頼性と相関しているため、設計者にとっては主たる関心事となっています。

### 電流の不平衡

二つの異なった IGBT があると、各電流レベルの VCE(on) は若干異なっています。この二つの IGBT が並列で動作している場合、両素子の VCE(on) は強制的に同じになります。このように、ある負荷電流に対し一つの IGBT がもう一つの IGBT よりも多く電流を通すと電流の不平衡が生じます。電流がデータシートで示された最大仕様以下である限り、電流の不平衡はそれ程重要ではありません。電流が低い場合、VCE(on) は75%から 100%にもな

ります。

#### 温度の不平衡

電圧は両方の IGBT に対し同じように降下するため、より多く電流を通している素子は接合温度が高く、最大 定格接合温度の150 を越えてしまうことがあります。このため信頼性の問題と共に、設計者は温度の不平衡に 特に注意を払う必要があります。

### 2. サーマルカップリングと他の平衡要因

サーマルカップリングには、温度の不平衡を減少させるための重要な役割があります。二つの素子の間のサーマルカップリングがしっかり固定されていると、温度差が著しくなることはありません。温度の不平衡を減少させる他の要因に電圧降下の温度係数があります。電圧降下の低いIGBTでは温度係数が低くなっています。電流と温度が上昇するに従い電圧降下は少なくなり、殆ど電流を通していなかったIGBTの電圧降下が著しい間は、電流および温度のギャップは無くなります。

三つ目の平衡保持メカニズムは、素子の動抵抗が持つ一つの特性に依っています。電圧降下の低い IGBT はダイナミック抵抗が高くなっているため、二つの電圧はより高い電流で有効範囲に降下します。

電流の不平衡は、サーマルカップリングにより著しく影響されることはありません。これは、分離および共通 ヒートシンクに実装した IGBT の電流の不平衡を示す次ぎのセクションの図でも示されています。しかし、基準 が一層重要になるに従い、温度の不平衡は著しい影響を受けるようになります。事実、次のセクションの図は、 150 の最大定格接合温度を越える熱い素子により最大電流が制限されることを示しています。さらに詳しい解 説は、セクション VIII.B.3 の参考[1]をご覧下さい。

### 3. IR の 600V 高速 IGBT 用素子の選択

素子の選択は、本質的に並列化と関連するディレーティングを減少させ、IGBTをデータシートの制限内で動作させるための効果的な方法です。選択の基準として、あるレベルの電流における各 IGBT の電圧が測定されていました。この測定方法はいわゆる「ダイオード・モード」(図1)で、ゲートがコレクターに結ばれており、電圧が複合ターミナルとエミッターに印加されています。希望する電流が IGBT を通して伝わるまで電圧は上昇します。この測定は自己加熱を防止するためパルスモードで行わなければなりません。この電流量に必要となる電圧は記録されています。この測定では、VCE(on)だけでなく、しきい値および gfs も考慮されています。この「ダイオードモード」電圧では、並列となる IGBT を結果的にうまく選択することが出来ます。 VCE(on)のみを整合させることは、スイッチモードで動作しない IGBT にはさらに適切です。以下の二つのセクションでは、異なった組み合わせの IGBT でシミュレーションを行い、IGBT の「ダイオード・モード」を使って測定した温度の不平衡および電流の不平衡に対する素子のばらつきを比較しました。

図 1 「ダイオード・モード」電圧 Vd i ode の測定の接続 Page3

この素子選択方法を使用し、我々は様々な組み合わせのIGBTが一般的なハーフブリッジでうまく並列動作をなすかを検証する方法を考えました。この目的のため、経験的なモデルがIGBTには使用され、それでは導通性およびスイッチング損がモデル化されています(参考[4]を参照)。

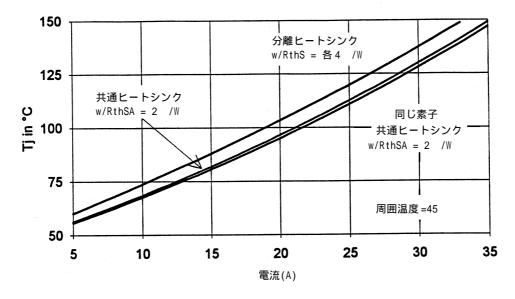

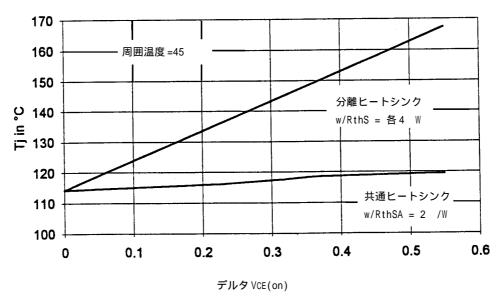

三つの各々のロットから取った5つの素子を調査し、導通電圧順にランク付けしました。このデータを使うと、並列動作でのIGBTの動作点がわかります。IGBTの様々な組み合わせでの性能を比較するため、パーセント電流不平衡に対する合計電流のグラフを作りました。このグラフでは、交流電流の不平衡が個々のIGBTの組み合わせである合計電流に対しどれ程になるかを示しています。分離したヒートシンクに装着された素子と共通のヒートシンクに装着された素子の二つの場合がプロットされています。また、二つの接合に対する合計電流の高い方の接合温度のグラフも作成しました。これらのグラフでは、次ぎの三つの曲線がプロットされています。1)不平衡の無い完璧に整合された素子、2)同じヒートシンクに装着され、Vdiodeの値により整合されていない素子、そして3)分離したヒートシンクに装着されVdiodeの値により整合されていない素子の三つの曲線です。

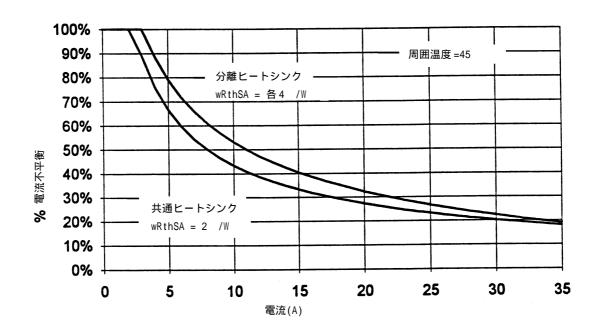

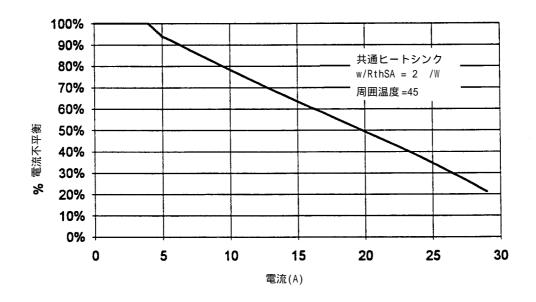

図 2 は、スペクトラムの両端での二つの IRGPC50F の異なったレベルの電流におけるパーセント電流不平衡を示しています。テストした素子のうち、一つは VCE(on)が低く、もう一つは VCE(on)が高くなっています。この組み合わせの IGBT の Vdiode は 0.69V でした。動作条件は、二つの素子が Rosa が 2 /W の共通のヒートシンクと、Rosa が 4 /W の分離したヒートシンクに装着され、周囲温度は 45 です。

図 2 Vdiode が 0.69V である IRGPC50F のパーセント電流不平衡に対する合計電流

図2に示すように、電流が低い場合ひとつのIGBTに電流が集中します。電流が上昇するに従い、低い曲線(同じヒートシンク、よってサーマルカップリングがしっかりと固定されている)について上で述べた三つの平衡保持メカニズムと、上の曲線の電流(分離したヒートシンク)に関連した二つの平衡保持メカニズムにより、不平衡は改善されます。

### **I⇔**R

### **DESIGN TIPS**

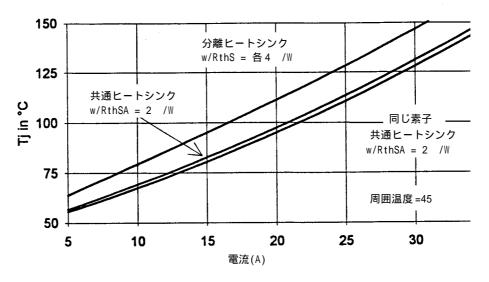

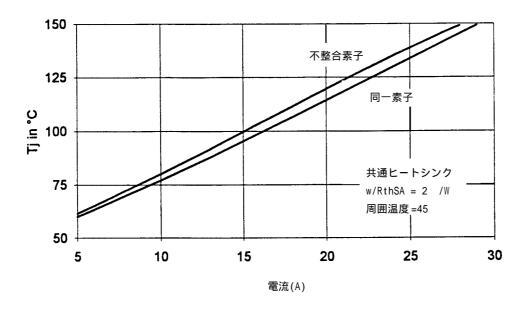

図3は、次の三つの場合についての並列の二つのIGBTの接合温度がより高くなっていることを示しています。 完全に整合された素子、同じヒートシンクに上記の二つの素子が実装されている、異なったヒートシンクに上記の二つの素子が装着されているの三つの場合です。この図は同じヒートシンクに分離した素子を置くことに対する最も強い支持を示しています。 20A を伝導しながら、二つの最も悪いの場合の IGBT の接合温度は完全に整合した IGBTの理想的な場合の2.5 以内にあります。しかし、分離したヒートシンクに装着された同じ二つの素子のうちの一つは、16 という上昇した接合温度で動作します。また、最大許容電流は35Aから31Aに低下しています。これは全て、分離したヒートシンクに装着されている素子が原因です。

図3 Vdiode が0.69Vである IRGPC50F の接合温度に対する合計電流

図 2 および図 3 の二つの素子は、テストした 15 の全ての素子の Volestim Volestim

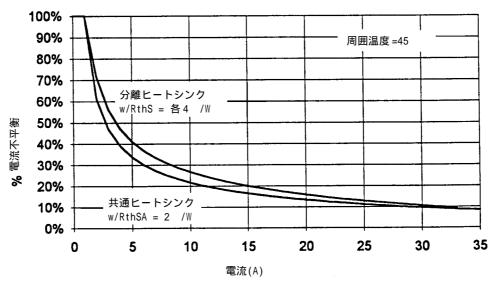

分離したヒートシンクに装着された素子は最大電流が33Aに制限され、共通のヒートシンクの素子は35Aまで動作可能です。20Aを伝導しながら、この二つのIGBTの接合温度は、共通のヒートシンクに実装され、完全に整合されたIGBTの理想的な場合の1.5 以内です。同じ二つの分離したヒートシンクに実装された素子は8.3 の上昇した接合温度で作動します。

図 4 Vdiode が 0.33V である IRGPC50F のパーセント電流不平衡に対する合計電流

図 5 Vdiode が 0.33V である IRGPC50F の接合温度に対する合計電流

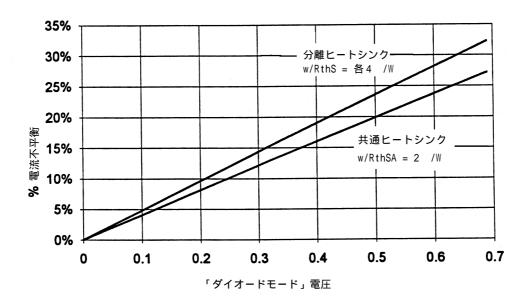

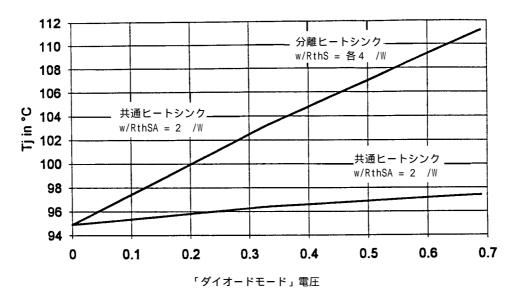

次ぎの二つのグラフは電流の不平衡および接合温度に対する Vdiode 測定の相関関係を示しています。この二つの図から、各々の「ダイオードモード」電圧が異なっている場合の並列の組み合わせの IGBT の動作を予測することが出来ます。図 7 は、素子を同じヒートシンクに実装することの重要性を強く示しています。

図6パーセント電流不平衡に対する Vdiode IRGPC50F

図7接合温度に対する Vdiode IRGPC50F

図8は、整合していないIGBT間の接合温度限度を原因とするハーフブリッジ回路に於ける出力の低下を示しています。この回路は前と同じ条件の元で作動していますが、電流の代わりに接合温度定価が125 に固定されています。どちらのIGBTも接合温度が125 を越えることはありません。グラフは最大出力電流に対するスイッチング周波数をプロットしています。通常の用途または状態ではデレーティングが殆ど、または全く必要ないことに注意して下さい。

図8 Vdiodeが0.00、0.33、0.69Vである3組みのIRGPC50Fについての電流に対する周波数グラフ

図8の曲線は、二つの素子が共通のヒートシンクに実装されていると仮定して計算したものです。分離したヒートシンクの場合は、前に述べた問題のため計していません。素子が異なったヒートシンクに実装さていると、出力電流は著しく減少します。

### 4. IR の 600V 超高速 IGBT 用の素子の選択

前のセクションで示した方法は、寿命キリング(lifetime killing)の量(参考[5]を参照)が素子の挙動に著しく影響する場合には不適切です。そうした素子には、単純なVCE(on)整合案が実行されてきました。次の各図は、並列化した高速IGBTの様々な組み合わせを使い達成した性能を示しています。

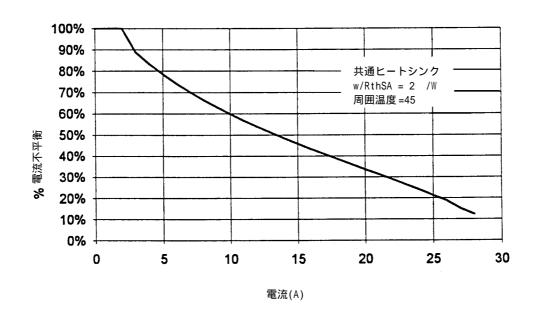

図9は、スペクトラムの両端での異なった電流レベルでの二つの IRGPC50U のパーセント電流不平衡、三つのロットの15の素子全ての最低および最大 VCE(on)を示しています。これらの VCE(on)は30 アンペアで 0.55 ボルトでした。動作条件は、ROSA が 2 /W の共通のヒートシンクに二つの素子を装着し、周囲温度は45 です。

図9 Vdiode が0.55V である IRGPC50U のパーセント電流不平衡に対する合計電流

### IOR

## **DESIGN TIPS**

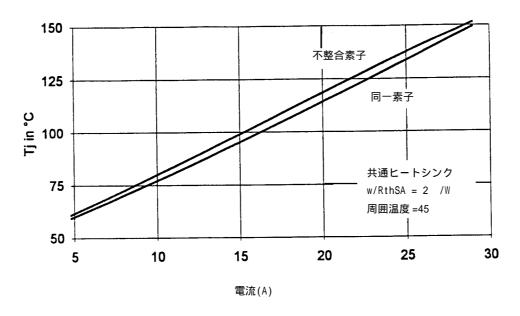

図9に示した電流の共有は、前のセクションで議論したように採用しがたいものですが、更に重要な要因は接合温度で、それを図10に示します。図10の上の曲線は図9の素子についてで、下の方の曲線は二つの同一のものについてです(例: VCE(on)がゼロ)。どのような電流でも、不整合素子の損失はほんの摂氏数度です。

図 10 Vdiode が 0.55V である IRGPC50U の接合温度に対する合計電流

整合した素子をさらに詳しく比較するため、30アンペアで測定した VCE(on)=0.36Vで二つの素子を使い上記の二つの図を繰り返しました。図11は、二つの不整合 IRGPC50Uの異なった電流レベルでのパーセント電流不平衡を示しています。動作条件は前の二つの図と同じです。

図 11 Vdiode が 0.55V である IRGPC50U のパーセント電流不平衡に対する合計電流

図12は接合温度に対する電流を示しています。図12の上の曲線は図11の素子で、下の曲線は二つの同一のものについてです(例: VCE(on)がゼロ)。

図 12 Vdiode が 0.36V である IRGPC50U の接合温度に対する合計電流

図13は、 VCE(on)が増大した IRGPC50Uの幾つかの異なったペアの並列での組み合わせの二つの接合温度の高い方を示しています。このグラフは並列化した素子は共通のヒートシンクに実装しなければならないことが何故重要なのかを示しています。

図 13 IRGPC50U の接合温度に対する VCE(on)

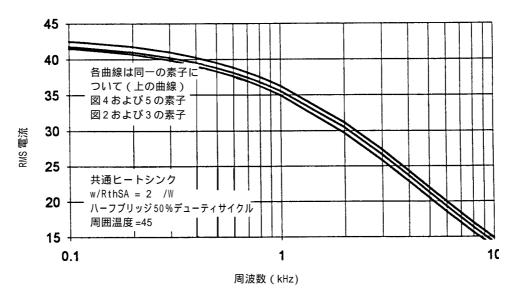

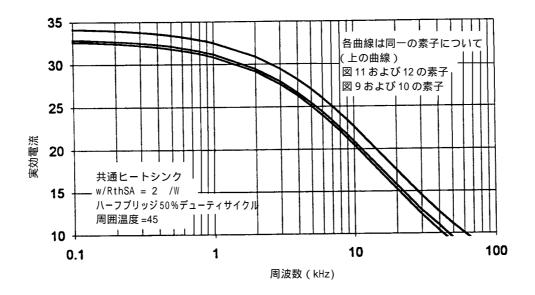

最後の図である図14は、デューティサイクルが50%に固定されている一般的なハーフブリッジ構成で動作する IRGPC50U の並列のペアの実効電流に対するスイッチング周波数を示しています。各素子は、温度抵抗が2 / Wで、周囲温度が45 で共通のヒートシンクに実装されています。どの IGBT も 125 の接合温度を越えることはありません。上の曲線は同一の素子で、次の曲線は図 11 および 12 で説明した素子の曲線で、下の曲線は図 9 および 10 で説明した素子のものです。

図 16 Vdiode が 0.00、0.36、0.55V である 3 組みの IRGPC50U についての電流に対する周波数グラフ

IRGPC50Fについて図 8 で示したように、サーマルカップリングがしっかりと固定されている共通のヒートシンクに装着されている場合にのみ、図 16 にプロットしたハーフブリッジの出力電流は二つの IGBT 間の VCE (on)の不整合により著しく減少することはありません。

### 5. マルチプル並列素子

これまでの議論は、簡単な分析ツールで取り扱うことが可能な二つの並列化した素子に限定していました。これにより結論が一般性に限定される訳ではありませんが、並列化した素子のグループでもあるように、二つのもので極端な電圧降下があります。セクションVIII.B.1の参考[1]で説明されているように、この二つの素子は極端なスイッチング特性を持ちやすい傾向にあります。このDesign Tipの考察、特に選択基準はこういった二つの極端な素子に適用され、他の全ての素子はその中間に入ることになります。

#### 結論

IGBTの並列化では、レイアウト、ゲート駆動、ヒートシンクへの事前の配慮が電流の分担よりもさらに重要となります。並列化されることとなる重要なパラメーターは接合温度です。これは素子の長期的な信頼性と直接関連しているからです。並列のIGBTが同じヒートシンクに実装されている場合、きっちりとした温度フィードバックがなされます。このフィードバックは、殆ど全ての用途で容認可能な温度不平衡をもたらします。スイッチモード動作を目的とした二つの素子の選択方法が示されていますが、これはディレーティングが殆どまたは全く無く、IGBTがその最大定格近辺で使用されているいない場合は一般的に必要ありません。

### 参考文献:

- $1. \quad IR Application Note AN-990 : Application Characterization of IGBTs.$

- 2. James B. Forsythe *Paralleling of Power MOSFETs for Higher Power Output*, Power Con'81.

- 3. HEXFETDesigner's Manua (HDM-1) 1992.

- 4. Clemente, S., Dapkus, D. Accurate Junction Temperature Calculation Optimizes I GBT Selection for Maximum Performance and Reliability, PCIM'92 Conference Proceedings.

- 5. IRApplicationNoteAN-983A: IGBT Characteristics.