ICL232

August 1997

# +5V Powered, Dual RS-232 Transmitter/Receiver

### **Features**

- Meets All RS-232C and V.28 Specifications

- Requires Only Single +5V Power Supply

- Onboard Voltage Doubler/Inverter

- Low Power Consumption

- 2 Drivers

- ±9V Output Swing for +5V Input

- 300 $\Omega$  Power-off Source Impedance

- Output Current Limiting

- TTL/CMOS Compatible

- 30V/μs Maximum Slew Rate

- 2 Receivers

- ±30V Input Voltage Range

- $3k\Omega$  to  $7k\Omega$  Input Impedance

- 0.5V Hysteresis to Improve Noise Rejection

- All Critical Parameters are Guaranteed Over the Entire Commercial, Industrial and Military Temperature Ranges

### **Applications**

- Any System Requiring RS-232 Communications Port

- Computer Portable and Mainframe

- Peripheral Printers and Terminals

- Portable Instrumentation

- Modems

- Dataloggers

# Description

The ICL232 is a dual RS-232 transmitter/receiver interface circuit that meets all EIA RS-232C and V.28 specifications. It requires a single +5V power supply, and features two onboard charge pump voltage converters which generate +10V and -10V supplies from the 5V supply.

The drivers feature true TTL/CMOS input compatibility, slew-rate-limited output, and  $300\Omega$  power-off source impedance. The receivers can handle up to +30V, and have a  $3k\Omega$  to  $7k\Omega$  input impedance. The receivers also have hysteresis to improve noise rejection.

# Ordering Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE      | PKG.<br>NO. |

|-------------|---------------------|--------------|-------------|

| ICL232CPE   | 0 to 70             | 16 Ld PDIP   | E16.3       |

| ICL232CBE   | 0 to 70             | 16 Ld SOIC   | M16.3       |

| ICL232IPE   | -40 to 85           | 16 Ld PDIP   | E16.3       |

| ICL232IJE   | -40 to 85           | 16 Ld CERDIP | F16.3       |

| ICL232IBE   | -40 to 85           | 16 Ld SOIC   | M16.3       |

| ICL232MJE   | -55 to 125          | 16 Ld CERDIP | F16.3       |

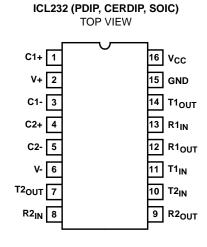

### **Pinout**

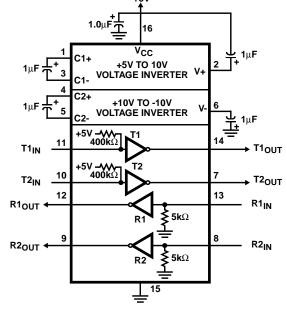

# Functional Diagram

# **Absolute Maximum Ratings**

| $V_{CC}$ to Ground                                                    |

|-----------------------------------------------------------------------|

| V- to Ground12V < V- < (GND +0.3V)                                    |

| Input Voltages                                                        |

| $T1_{IN}$ , $T2_{IN}$ (V0.3V) < $V_{IN}$ < (V+ +0.3V)                 |

| R1 <sub>IN</sub> , R2 <sub>IN</sub>                                   |

| Output Voltages                                                       |

| $T1_{OUT}$ , $T2_{OUT}$ (V0.3V) < $V_{TXOUT}$ < (V+ +0.3V)            |

| $R1_{OUT}$ , $R2_{OUT}$ (GND -0.3V) < $V_{RXOUT}$ < ( $V_{CC}$ +0.3V) |

| Short Circuit Duration                                                |

### **Thermal Information**

| Thermal Resistance (Typical, Note 1) CERDIP Package | θ <sub>JA</sub> ( <sup>o</sup> C/W)<br>80 | θ <sub>JC</sub> ( <sup>o</sup> C/W)<br>18 |

|-----------------------------------------------------|-------------------------------------------|-------------------------------------------|

| PDIP Package                                        | 100                                       | N/A                                       |

| SOIC Package                                        | 100                                       | N/A                                       |

| Maximum Junction Temperature                        |                                           |                                           |

| Plastic Packages                                    |                                           | 150 <sup>o</sup> C                        |

| Ceramic Package                                     |                                           | 175 <sup>0</sup> C                        |

| Maximum Storage Temperature Range                   | 65                                        | 5 <sup>o</sup> C to 150 <sup>o</sup> C    |

| Maximum Lead Temperature (Soldering 1               | 0s)                                       | 300°C                                     |

### **Operating Conditions**

Temperature Ranges

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

1.  $\theta_{\text{JA}}$  is measured with the component mounted on an evaluation PC board in free air.

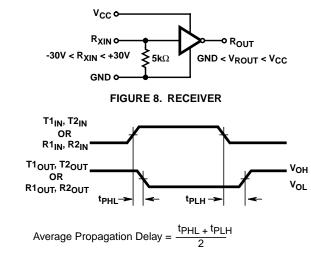

**Electrical Specifications** Test Conditions: V<sub>CC</sub> = +5V ±10%, T<sub>A</sub> = Operating Temperature Range. Test Circuit as in Figure 8 Unless Otherwise Specified

| PARAMETER                                              | TEST CONDITIONS                                                             | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|-------|

| Transmitter Output Voltage Swing, T <sub>OUT</sub>     | $T1_{OUT}$ and $T2_{OUT}$ Loaded with $3k\Omega$ to Ground                  | ±5  | ±9  | ±10 | V     |

| Power Supply Current, I <sub>CC</sub>                  | Outputs Unloaded, T <sub>A</sub> = 25°C                                     | =   | 5   | 10  | mA    |

| T <sub>IN</sub> , Input Logic Low, V <sub>IL</sub>     |                                                                             | -   | -   | 0.8 | V     |

| T <sub>IN</sub> , Input Logic High, V <sub>IH</sub>    |                                                                             | 2.0 | -   | -   | V     |

| Logic Pullup Current, I <sub>P</sub>                   | T1 <sub>IN</sub> , T2 <sub>IN</sub> = 0V                                    | =   | 15  | 200 | μΑ    |

| RS-232 Input Voltage Range, V <sub>IN</sub>            |                                                                             | -30 | -   | +30 | V     |

| Receiver Input Impedance, R <sub>IN</sub>              | V <sub>IN</sub> = ±3V                                                       | 3.0 | 5.0 | 7.0 | kΩ    |

| Receiver Input Low Threshold, V <sub>IN</sub> (H-L)    | $V_{CC} = 5V, T_A = 25^{\circ}C$                                            | 0.8 | 1.2 | -   | V     |

| Receiver Input High Threshold, V <sub>IN</sub> (L-H)   | $V_{CC} = 5V, T_A = 25^{\circ}C$                                            | -   | 1.7 | 2.4 | V     |

| Receiver Input Hysteresis, V <sub>HYST</sub>           |                                                                             | 0.2 | 0.5 | 1.0 | V     |

| TTL/CMOS Receiver Output Voltage Low, V <sub>OL</sub>  | I <sub>OUT</sub> = 3.2mA                                                    | =   | 0.1 | 0.4 | V     |

| TTL/CMOS Receiver Output Voltage High, V <sub>OH</sub> | I <sub>OUT</sub> = -1.0mA                                                   | 3.5 | 4.6 | -   | V     |

| Propagation Delay, t <sub>PD</sub>                     | RS-232 to TTL                                                               | -   | 0.5 | -   | μs    |

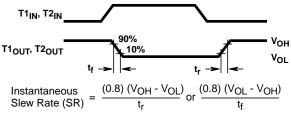

| Instantaneous Slew Rate, SR                            | $C_L = 10 pF, R_L = 3 k\Omega, T_A = 25^{\circ}C$<br>(Notes 2, 3)           | -   | -   | 30  | V/µs  |

| Transition Region Slew Rate, SR <sub>T</sub>           | $R_L$ = 3k $\Omega$ , $C_L$ = 2500pF Measured from +3V to -3V or -3V to +3V | -   | 3   | -   | V/μs  |

| Output Resistance, R <sub>OUT</sub>                    | V <sub>CC</sub> = V+ = V- = 0V, V <sub>OUT</sub> = ±2V                      | 300 | -   | -   | Ω     |

| RS-232 Output Short Circuit Current, I <sub>SC</sub>   | T1 <sub>OUT</sub> or T2 <sub>OUT</sub> Shorted to GND                       | -   | ±10 | -   | mA    |

### NOTES:

- 2. Guaranteed by design.

- 3. See Figure 4 for definition.

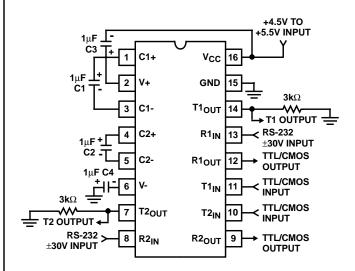

# **Test Circuits**

$V_{\text{IN}} = \pm 2V$

1 C1+

2

3 C1-

4 C2+

5 C2-

6

T2<sub>OUT</sub>

$R_{OUT} = V_{IN}/I$

R2<sub>IN</sub>

V<sub>CC</sub> 16

GND 15

T1<sub>OUT</sub> 14

R1<sub>IN</sub> 13

R1<sub>OUT</sub> 12

T1<sub>IN</sub>

T2<sub>IN</sub> 10

R2<sub>OUT</sub>

T2<sub>OUT</sub>

11

FIGURE 1. GENERAL TEST CIRCUIT

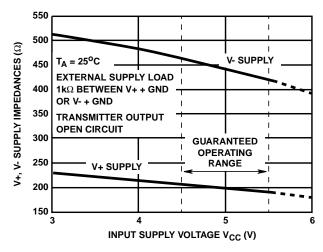

# **Typical Performance Curves**

FIGURE 3. V+, V- OUTPUT IMPEDANCES vs  $V_{CC}$

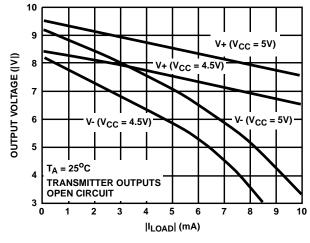

FIGURE 4. V+, V- OUTPUT VOLTAGES vs LOAD CURRENT

# Pin Descriptions

| PDIP, CERDIP | SOIC | PIN NAME          | DESCRIPTION                                                                           |

|--------------|------|-------------------|---------------------------------------------------------------------------------------|

| 1            | 1    | C1+               | External capacitor "+" for internal voltage doubler.                                  |

| 2            | 2    | V+                | Internally generated +10V (typical) supply.                                           |

| 3            | 3    | C1-               | External capacitor "-" for internal voltage doubler.                                  |

| 4            | 4    | C2+               | External capacitor "+" internal voltage inverter.                                     |

| 5            | 5    | C2-               | External capacitor "-" internal voltage inverter.                                     |

| 6            | 6    | V-                | Internally generated -10V (typical) supply.                                           |

| 7            | 7    | T2 <sub>OUT</sub> | RS-232 Transmitter 2 output ±10V (typical).                                           |

| 8            | 8    | R2 <sub>IN</sub>  | RS-232 Receiver 2 input, with internal 5K pulldown resistor to GND.                   |

| 9            | 9    | R2out             | Receiver 2 TTL/CMOS output.                                                           |

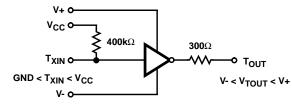

| 10           | 10   | T2 <sub>IN</sub>  | Transmitter 2 TTL/CMOS input, with internal 400K pullup resistor to V <sub>CC</sub> . |

| 11           | 11   | T1 <sub>IN</sub>  | Transmitter 1 TTL/CMOS input, with internal 400K pullup resistor to V <sub>CC</sub> . |

# Pin Descriptions (Continued)

| PDIP, CERDIP | SOIC | PIN NAME          | DESCRIPTION                                                         |

|--------------|------|-------------------|---------------------------------------------------------------------|

| 12           | 12   | R1 <sub>OUT</sub> | Receiver 1 TTL/CMOS output.                                         |

| 13           | 13   | R1 <sub>IN</sub>  | RS-232 Receiver 1 input, with internal 5K pulldown resistor to GND. |

| 14           | 14   | T1 <sub>OUT</sub> | RS-232 Transmitter 1 output ±10V (typical).                         |

| 15           | 15   | GND               | Supply Ground.                                                      |

| 16           | 16   | Vcc               | Positive Power Supply +5V ±10%                                      |

# **Detailed Description**

The ICL232 is a dual RS-232 transmitter/receiver powered by a single +5V power supply which meets all EIA RS232C specifications and features low power consumption. The functional diagram illustrates the major elements of the ICL232. The circuit is divided into three sections: a voltage doubler/inverter, dual transmitters, and dual receivers Voltage Converter.

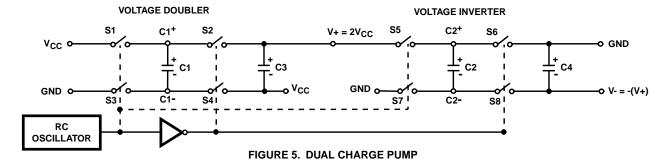

An equivalent circuit of the dual charge pump is illustrated in Figure 5.

The voltage quadrupler contains two charge pumps which use two phases of an internally generated clock to generate +10V and -10V. The nominal clock frequency is 16kHz. During phase one of the clock, capacitor C1 is charged to V<sub>CC</sub>. During phase two, the voltage on C1 is added to V<sub>CC</sub>, producing a signal across C2 equal to twice V<sub>CC</sub>. At the same time, C3 is also charged to 2V<sub>CC</sub>, and then during phase one, it is inverted with respect to ground to produce a signal across C4 equal to -2V<sub>CC</sub>. The voltage converter accepts input voltages up to 5.5V. The output impedance of the doubler (V+) is approximately  $200\Omega$ , and the output impedance of the inverter (V-) is approximately  $450\Omega$ . Typical graphs are presented which show the voltage converters output vs input voltage and output voltages vs load characteristics. The test circuit (Figure 3) uses 1µF capacitors for C1-C4, however, the value is not critical. Increasing the values of C1 and C2 will lower the output impedance of the voltage doubler and inverter, and increasing the values of the reservoir capacitors, C3 and C4, lowers the ripple on the V+ and V- supplies.

FIGURE 6. SLEW RATE DEFINITION

#### **Transmitters**

The transmitters are TTL/CMOS compatible inverters which translate the inputs to RS-232 outputs. The input logic threshold is about 26% of  $V_{CC}$ , or 1.3V for  $V_{CC}$  = 5V. A logic 1 at the input results in a voltage of between -5V and V- at the output, and a logic 0 results in a voltage between +5V and (V+ - 0.6V). Each transmitter input has an internal 400kΩ pullup resistor so any unused input can be left unconnected and its output remains in its low state. The output voltage swing meets the RS-232C specification of ±5V minimum with the worst case conditions of: both transmitters driving 3kΩ minimum load impedance,  $V_{CC}$  = 4.5V, and maximum allowable operating temperature. The transmitters have an internally limited output slew rate which is less than 30V/us. The outputs are short circuit protected and can be shorted to ground indefinitely. The powered down output impedance is a minimum of  $300\Omega$  with  $\pm 2V$  applied to the outputs and  $V_{CC} = 0V$ .

FIGURE 7. TRANSMITTER

### Receivers

The receiver inputs accept up to  $\pm 30$ V while presenting the required  $3k\Omega$  to  $7k\Omega$  input impedance even it the power is off (V<sub>CC</sub> = 0V). The receivers have a typical input threshold of 1.3V which is within the  $\pm 3$ V limits, known as the transition region, of the RS-232 specification. The receiver output is 0V to V<sub>CC</sub>. The output will be low whenever the input is greater than 2.4V and high whenever the input is floating or driven between +0.8V and -30V. The receivers feature 0.5V hysteresis to improve noise rejection.

FIGURE 9. PROPAGATION DELAY DEFINITION

# **Applications**

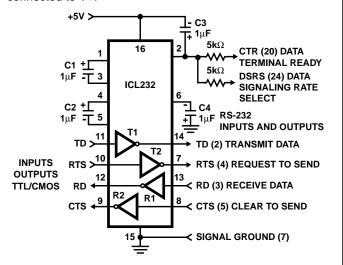

The ICL232 may be used for all RS-232 data terminal and communication links. It is particularly useful in applications where  $\pm 12V$  power supplies are not available for conventional RS-232 interface circuits. The applications presented represent typical interface configurations.

A simple duplex RS-232 port with CTS/RTS handshaking is illustrated in Figure 10. Fixed output signals such as DTR (data terminal ready) and DSRS (data signaling rate select)

is generated by driving them through a  $5 k\Omega$  resistor connected to V+.

FIGURE 10. SIMPLE DUPLEX RS-232 PORT WITH CTS/RTS HANDSHAKING

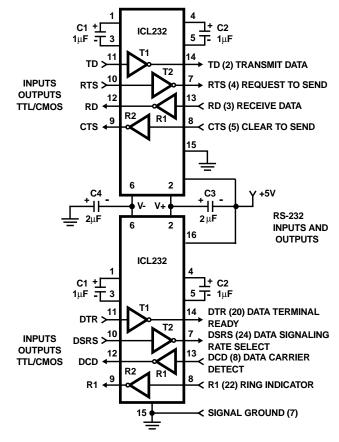

In applications requiring four RS-232 inputs and outputs (Figure 11), note that each circuit requires two charge pump capacitors (C1 and C2) but can share common reservoir capacitors (C3 and C4). The benefit of sharing common reservoir capacitors is the elimination of two capacitors and the reduction of the charge pump source impedance which effectively increases the output swing of the transmitters.

FIGURE 11. COMBINING TWO ICL232s FOR 4 PAIRS OF RS-232 INPUTS AND OUTPUTS