DS07-13606-1E

# 16-bit Proprietary Microcontroller

CMOS

# F<sup>2</sup>MC-16L MB90620A Series

# MB90622A/623A/P623A

### DESCRIPTION

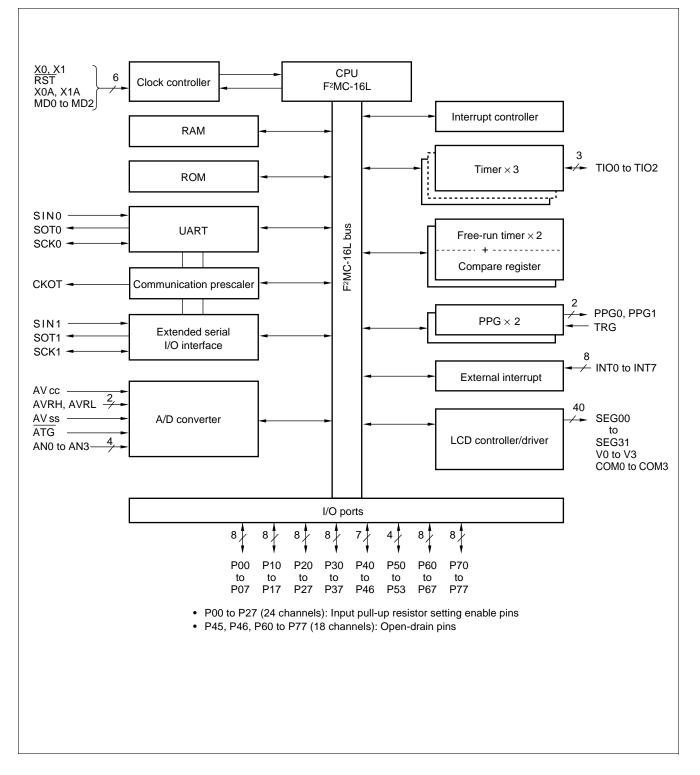

The MB90620A series is a line of general-purpose, 16-bit microcontrollers designed for those applications which require high-speed real-time processing, proving to be suitable for various industrial machines, camera and video devices, OA equipment, and for process control. The CPU used in this series is the F<sup>2</sup>MC\*-16L. The instruction set for the F<sup>2</sup>MC-16L CPU core is designed to be optimized for controller applications while inheriting the AT architecture of the F<sup>2</sup>MC-16/16H series, allowing a wide range of control tasks to be processed efficiently at high speed.

The peripheral resources integrated in the MB90620A series include: the UART (clock asynchronous/ synchronous transfer)  $\times$  1 channel, the extended serial I/O interface  $\times$  1 channel, the A/D converter (8/10-bit precision)  $\times$  4 channels, the 16-bit PPG timer (PWM/single-shot function)  $\times$  2 channels, the 16-bit reload timer  $\times$  3 channels, the 16-bit free-run timer (built-in compare register: 2 channels)  $\times$  2 channels, the external interrupt  $\times$  8 channels, the watch timer  $\times$  1 channel, LCD controller/driver 32 segments  $\times$  4 commons.

\*: F<sup>2</sup>MC stands for FUJITSU Flexible Microcontroller.

### ■ FEATURES

### F<sup>2</sup>MC-16L CPU

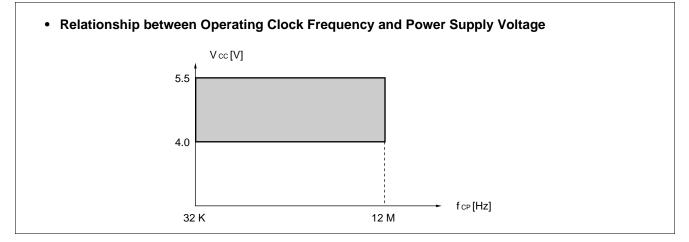

- Minimum execution time: 83.33 ns (at machine clock frequency of 12 MHz)

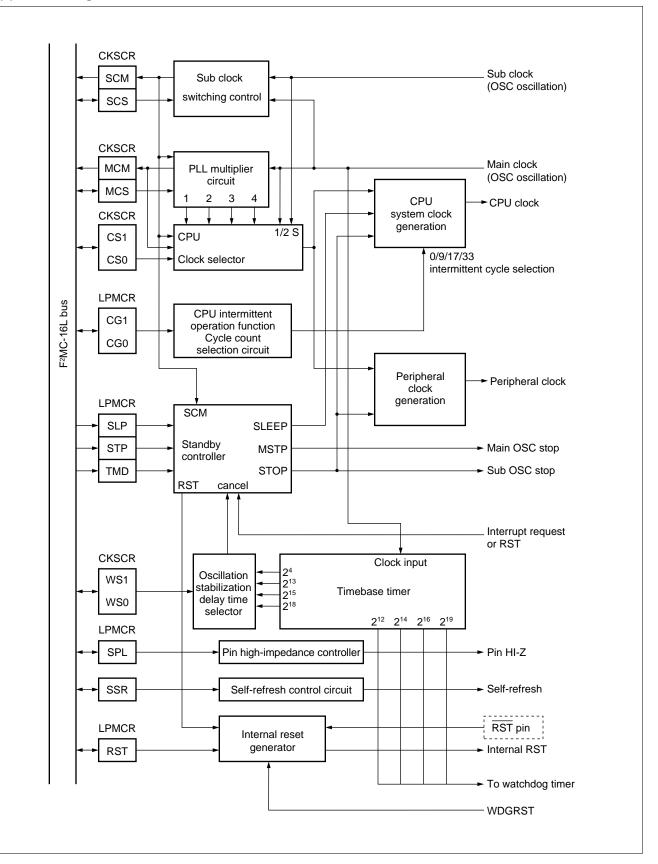

- Dual-clock control systems

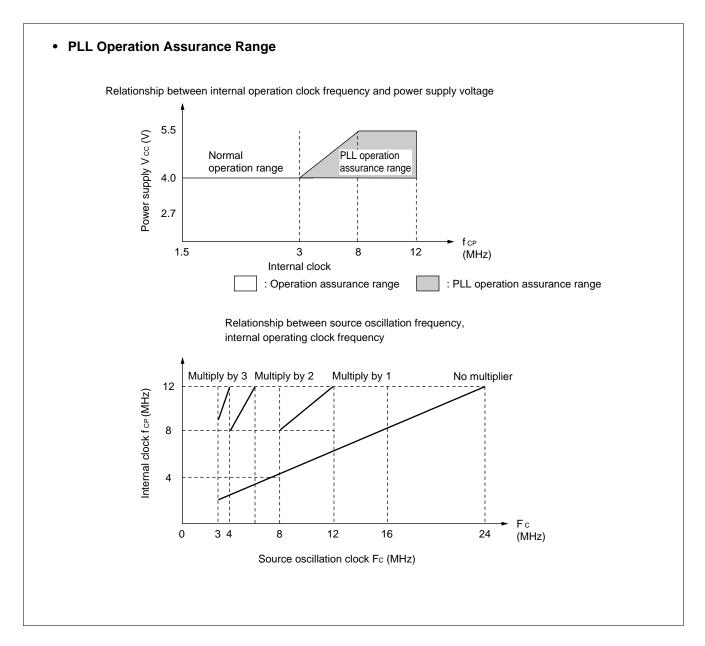

- PLL clock control

### (Continued)

- Instruction set optimized for controller applications Variety of data types: bit, byte, word, long-word Expanded addressing modes: 23 types High coding efficiency Improvement of high-precision arithmetic operations through use of 32-bit accumulator

- Instruction set supports high-level language (C language) and multitasking Inclusion of system stack pointer

Enhanced pointer-indirect instructions

Barrel shift instruction

- Improved execution speed: 4-byte instruction queue

- 8-level, 32-factor powerful interrupt service functions

- Automatic transfer function independent of CPU (EI<sup>2</sup>OS)

- General-purpose ports: max. 59 channels

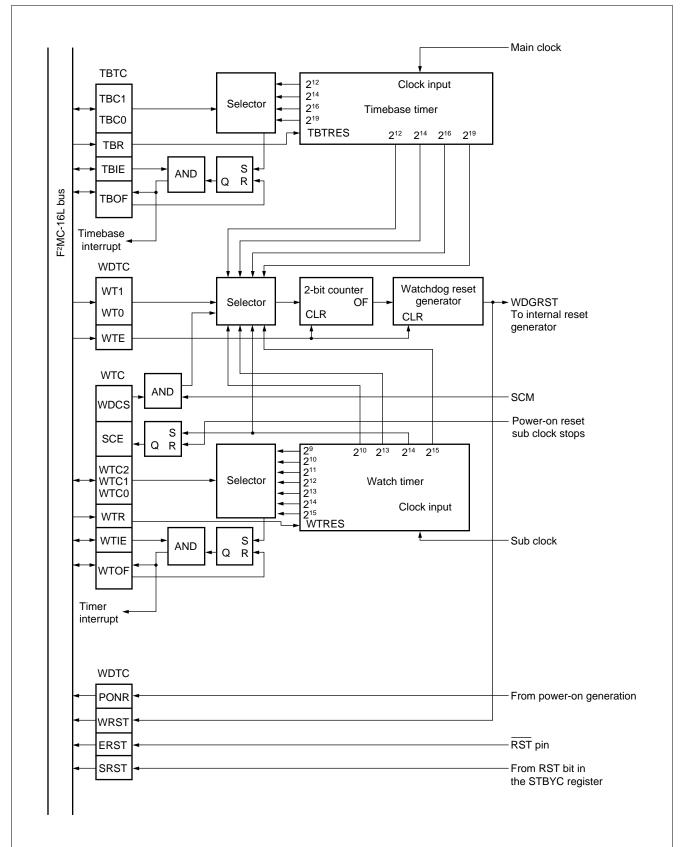

- 18-bit timebase timer/15-bit watch timer

- Watchdog timer function

- CPU intermittent operation function

- · Various standby modes

### **Peripheral blocks**

- ROM:32 Kbytes (MB90622A) 48 Kbytes (MB90623A)

- One-time PROM: 48 Kbytes (MB90P623A)

- RAM: 1.64 Kbytes (MB90622A)

2 Kbytes (MB90623A/P623A)

- General-purpose ports: max. 59 channels

- Dual-clock control system

- PLL clock multiplication control system

- UART: 1 channel

Can be used for either asynchronous transfer or synchronous transfer with clock

- Extended serial I/O interface: 1 channel Can be used for 8-bit synchronous transfer

- A/D converter (8/10-bit resolution): 4 channels

- PPG (Programable pulse generator): 2 channels

- 16-bit reload timer: 3 channels

- 16-bit free-run timer: 2 channels

- With compare register 2 channels

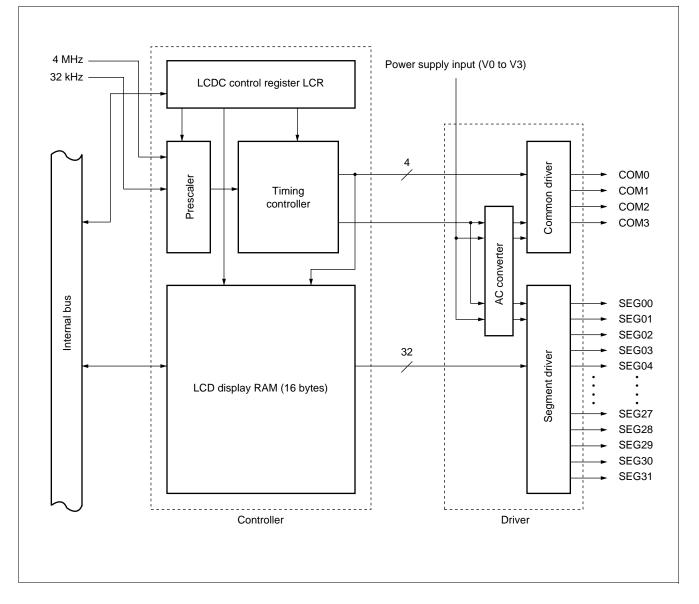

- LCD controller/driver

32 segments, 4 commons

- External interrupts: 8 channels

- 18-bit timebase timer

- 15-bit watch timer

- Watchdog timer function

- CPU intermittent operation function

- Standby mode Watch mode Sleep mode Stop mode

### ■ PRODUCT LINEUP

| Part number               | MB90622A                                                                                                                                                                                                                                                                                                                                  | MB90623A                                                                                                                                                                          | MB90P623A   |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| Parameter                 |                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                   |             |  |  |

| Classification            | Mass produc<br>(Mask ROM                                                                                                                                                                                                                                                                                                                  | One-time model                                                                                                                                                                    |             |  |  |

| ROM size                  | 32 Kbytes                                                                                                                                                                                                                                                                                                                                 | 48 Kbytes                                                                                                                                                                         | 48 Kbytes   |  |  |

| RAM size                  | 1.64 Kbytes                                                                                                                                                                                                                                                                                                                               | 2 Kbytes                                                                                                                                                                          | 2 Kbytes    |  |  |

| CPU functions             | Da                                                                                                                                                                                                                                                                                                                                        | Number of instructions: 340<br>nstruction bit length: 8 or 16 bits<br>Instruction length: 1 to 7 bytes<br>ita bit length: 1, 4, 8, 16, or 32 b<br>eccution time: 83.33 ns at 12 M | bits        |  |  |

| Oscillation circuit       | Dual-clo                                                                                                                                                                                                                                                                                                                                  | ock system of main clock and su                                                                                                                                                   | ub clock    |  |  |

| Ports                     | I/O ports (                                                                                                                                                                                                                                                                                                                               | Max. 59 channels<br>I/O ports (CMOS): 17<br>CMOS) with pull-up resistor ava<br>I/O ports (open drain): 18                                                                         | ailable: 24 |  |  |

| UART                      | Number of channels: 1<br>Clock synchronous communication (1202 to 9615 bps, full-duplex double buffering)<br>Clock asynchronous communication (62.5 K to 1 M bps, full-duplex double buffering)<br>Supports multiprocessor mode                                                                                                           |                                                                                                                                                                                   |             |  |  |

| Serial                    | Number of channels: 1<br>Internal or external clock mode<br>Clock synchronous transfer (62.5 kHz to 1 MHz, "LSB first" or "MSB first" transfer)                                                                                                                                                                                           |                                                                                                                                                                                   |             |  |  |

| A/D converter             | Resolution: 10 or 8 bits, Number of input channels: 4<br>Single-conversion mode (conversion for a specified input channel)<br>Scan conversion mode (continuous conversion for specified consecutive channels)<br>Continuous conversion mode (repeated conversion for a specified channel)<br>Stop conversion mode (periodical conversion) |                                                                                                                                                                                   |             |  |  |

| Timer                     | Number of channels: 3<br>16-bit reload timer operation (operation clock: SUB/2, \u00f6/2 <sup>3</sup> , \u00f6/2 <sup>5</sup> , external)                                                                                                                                                                                                 |                                                                                                                                                                                   |             |  |  |

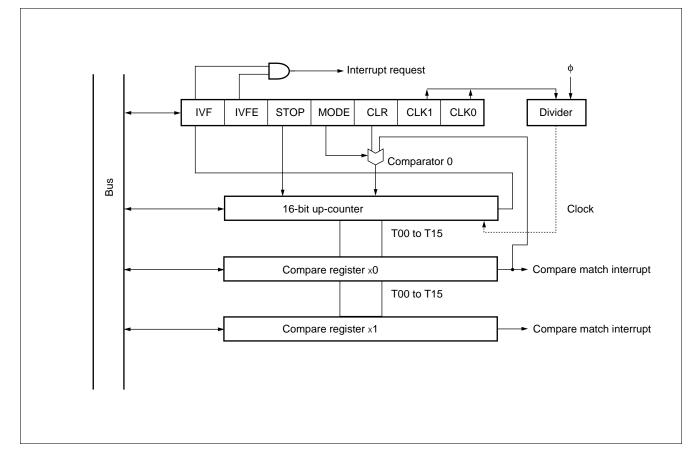

| Free-run timer            | Number of channels: 2<br>16-bit up-counter (four types of count clocks)<br>2 channels on each timer of the compare register (compare matching interrupt available)                                                                                                                                                                        |                                                                                                                                                                                   |             |  |  |

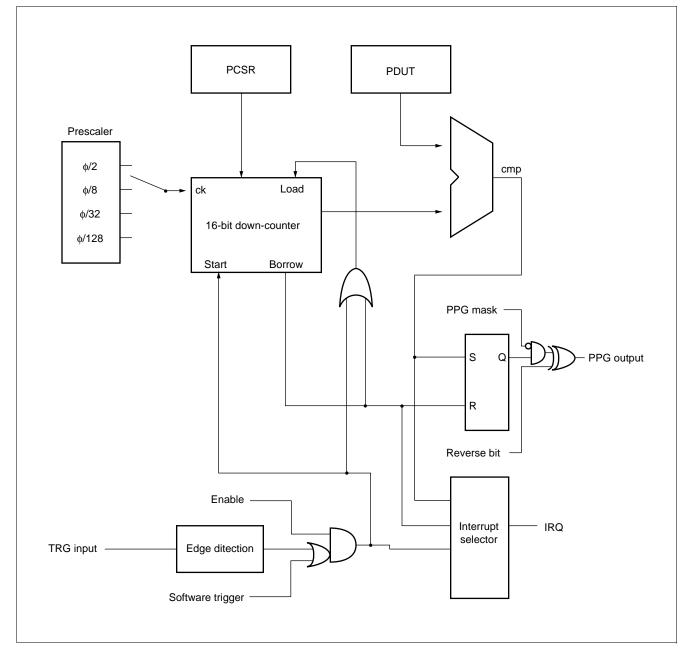

| PPG timer                 | Number of channels: 2<br>PWM function, single-shot function<br>With external trigger function                                                                                                                                                                                                                                             |                                                                                                                                                                                   |             |  |  |

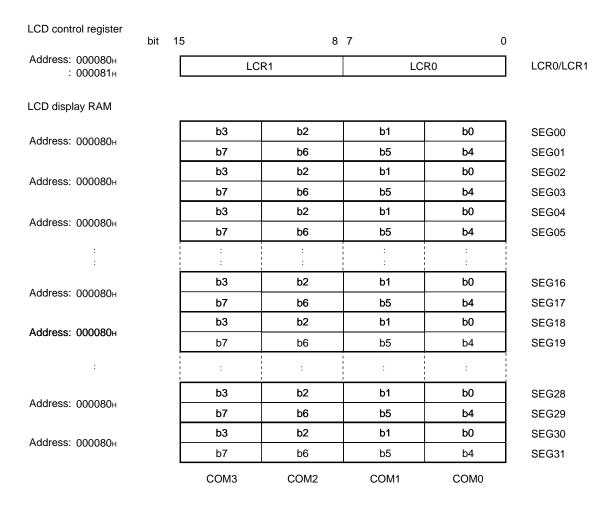

| LCD controller<br>/driver | Common output: 4 channels, Segment output: 32 channels<br>Direct driving of the LCD module<br>16 bytes of data memory for display<br>Operation clock source (main clock/sub clock selective)                                                                                                                                              |                                                                                                                                                                                   |             |  |  |

| Standby modes             | Stop                                                                                                                                                                                                                                                                                                                                      | mode, sleep mode, and watch                                                                                                                                                       | mode        |  |  |

| PLL functions             | Main clock multiplication ( $\times$ 1, $\times$ 2, $\times$ 3 and $\times$ 4)                                                                                                                                                                                                                                                            |                                                                                                                                                                                   |             |  |  |

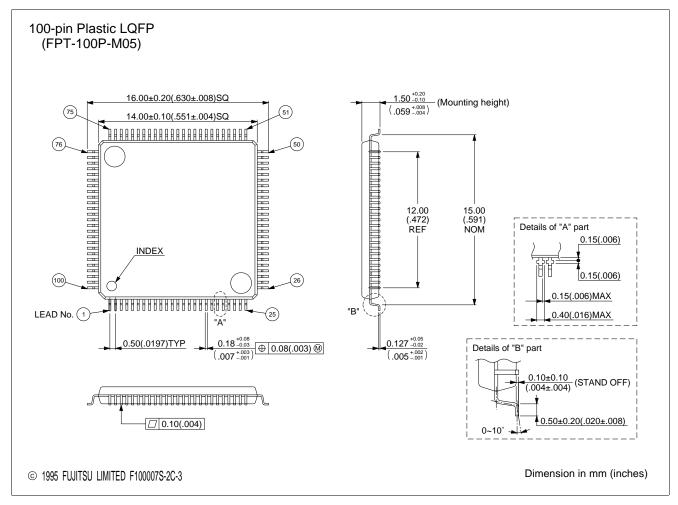

| Package                   | FPT-100P-M05                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                   |             |  |  |

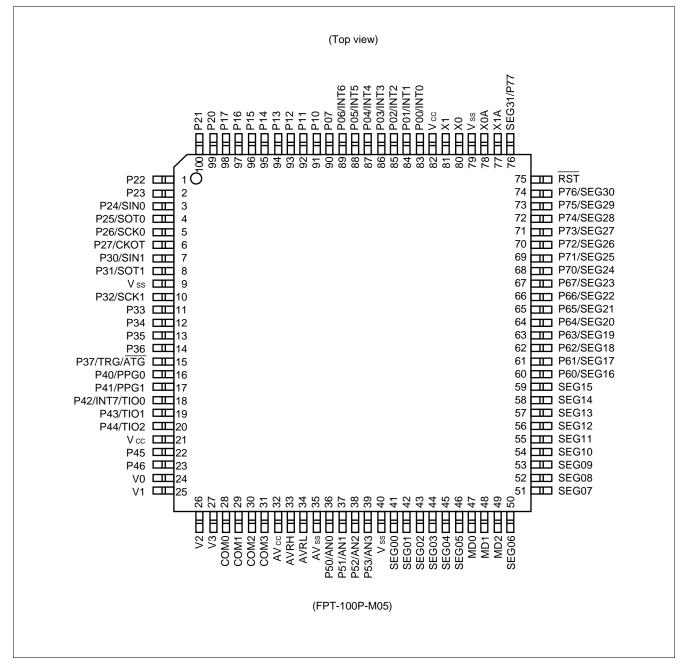

### ■ PIN ASSIGNMENT

### ■ PIN DESCRIPTION

| Pin no.         | Pin name     | Circuit type       | Function                                                                                                                                                                                                                                                                                               |  |

|-----------------|--------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 77<br>78        | X1A<br>X0A   | A<br>(Oscillation) | Crystal oscillator pins (32 kHz)                                                                                                                                                                                                                                                                       |  |

| 79              | Vss          | Power supply       | Digital circuit power supply (GND) pin                                                                                                                                                                                                                                                                 |  |

| 80<br>81        | X0<br>X1     | A<br>(Oscillation) | Crystal/FAR oscillator pins (4 MHz)                                                                                                                                                                                                                                                                    |  |

| 82              | Vcc          | Power supply       | Digital circuit power supply pin                                                                                                                                                                                                                                                                       |  |

| 83 to 89        | P00 to P06   | M<br>(CMOS/H)      | General-purpose I/O ports<br>At this pin, a pull-up resistor is added in the input mode depending<br>on the settings of the pull-up resistor setting register.                                                                                                                                         |  |

|                 | INT0 to INT6 |                    | External interrupt request input pins<br>When external interrupts are enabled, these inputs may be used at<br>any time; therefore, it is necessary to stop output by other functions<br>on these pins, except when using them for output deliberately.                                                 |  |

| 90              | P07          | G<br>(CMOS)        | General-purpose I/O port<br>At this pin, a pull-up resistor is added in the input mode depending<br>on the settings of the pull-up resistor setting register.                                                                                                                                          |  |

| 91 to 98        | P10 to P17   | G<br>(CMOS)        | General-purpose I/O ports<br>At this pin, a pull-up resistor is added in the input mode depending<br>on the settings of the pull-up resistor setting register.                                                                                                                                         |  |

| 99, 100<br>1, 2 | P20 to P23   | G<br>(CMOS)        | General-purpose I/O ports<br>At this pin, a pull-up resistor is added in the input mode depending<br>on the settings of the pull-up resistor setting register.                                                                                                                                         |  |

| 3               | P24          | F<br>(CMOS/H)      | General-purpose I/O port<br>At this pin, a pull-up resistor is added in the input mode depending<br>on the settings of the pull-up resistor setting register.                                                                                                                                          |  |

|                 | SINO         |                    | UART serial data input pin<br>During UART input operations, these inputs may be used at any<br>time; therefore, it is necessary to stop output by other functions on<br>these pins, except when using them for output deliberately.                                                                    |  |

| 4               | P25          | G<br>(CMOS)        | General-purpose I/O port<br>At this pin, a pull-up resistor is added in the input mode depending<br>on the settings of the pull-up resistor setting register.                                                                                                                                          |  |

|                 | SOT0         |                    | UART serial data output pin<br>This function is available when the UART serial data output is<br>enabled.                                                                                                                                                                                              |  |

| 5               | P26          | F<br>(CMOS/H)      | General-purpose I/O port<br>At this pin, a pull-up resistor is added in the input mode depending<br>on the settings of the pull-up resistor setting register.                                                                                                                                          |  |

|                 | SCK0         |                    | UART serial data I/O pin<br>This function is available when the UART clock output is enabled.<br>During UART input operations, these inputs may be used at any<br>time; therefore, it is necessary to stop output by other functions on<br>these pins, except when using them for output deliberately. |  |

| Pin no.  | Pin name   | Circuit type | Function                                                                                                                                                                                                                                                                                  |

|----------|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | P27        | G<br>(CMOS)  | General-purpose I/O port<br>At this pin, a pull-up resistor is added in the input mode depending<br>on the settings of the pull-up resistor setting register.                                                                                                                             |

|          | СКОТ       | _            | Clock output pin<br>This function is available when clock output is enabled.                                                                                                                                                                                                              |

| 7        | P30        | E            | General-purpose I/O port                                                                                                                                                                                                                                                                  |

|          | SIN1       | (CMOS/H)     | I/O extended serial data input pin<br>This pin, as required, is used for input during input operation, and it<br>is necessary to disable output for other functions from this pin<br>unless such output is made intentionally.                                                            |

| 8        | P31        | D            | General-purpose I/O port                                                                                                                                                                                                                                                                  |

|          | SOT1       | (CMOS)       | I/O extended serial data output pin<br>This function is available when serial data data output is enabled.                                                                                                                                                                                |

| 9        | Vss        | Power supply | Digital circuit power supply (GND) pin                                                                                                                                                                                                                                                    |

| 10       | P32        | E            | General-purpose I/O port                                                                                                                                                                                                                                                                  |

|          | SCK1       | - (CMOS/H)   | I/O extended serial clock I/O pins<br>This function is available when clock input is enabled.<br>This pin, as required, is used for input during input operation, and it<br>is necessary to disable output for other functions from this pin<br>unless such output is made intentionally. |

| 11 to 14 | P33 to P36 | D<br>(CMOS)  | General-purpose I/O ports                                                                                                                                                                                                                                                                 |

| 15       | P37        | E            | General-purpose I/O port                                                                                                                                                                                                                                                                  |

|          | TRG        | (CMOS/H)     | PPG0 and PPG1 external trigger input pin                                                                                                                                                                                                                                                  |

|          | ATG        | -            | A/D converter trigger input pin<br>During A/D converter input operations, these inputs may be used at<br>any time; therefore, it is necessary to stop output by other functions<br>on these pins, except when using them for output deliberately.                                         |

| 16       | P40        | D<br>(CMOS)  | General-purpose I/O port<br>This function is available when PPG timer 0 output is disabled.                                                                                                                                                                                               |

|          | PPG0       |              | PPG timer 0 output pin<br>This function is available when the PPG timer 0 waveform output is<br>enabled.                                                                                                                                                                                  |

| 17       | P41        | D<br>(CMOS)  | General-purpose I/O port<br>This function is available when PPG timer 1 output is disabled.                                                                                                                                                                                               |

|          | PPG1       |              | PPG timer 1 output pin<br>This function is available when the PPG timer 1 waveform output is<br>enabled.                                                                                                                                                                                  |

| Pin no.  | Pin name        | Circuit type  | Function                                                                                                                                                                                                                                              |  |

|----------|-----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 18       | P42             | L<br>(CMOS/H) | General-purpose I/O port<br>This function is available when the timer output from timer 0 is<br>disabled.                                                                                                                                             |  |

|          | INT7            |               | External interrupt request input pin<br>When external interrupts are enabled, these inputs may be used at<br>any time; therefore, it is necessary to stop output by other functions<br>on these pins, except when using them for output deliberately. |  |

|          | ΤΙΟΟ            |               | Timer input pin<br>The data on this pin is used as event count signal for timer 0.<br>Timer output pin<br>This function is available when the timer output from timer 0 is<br>enabled.                                                                |  |

| 19       | P43             | E<br>(CMOS/H) | General-purpose I/O port<br>This function is available when the timer output from timer 1 is<br>disabled.                                                                                                                                             |  |

|          | TIO1            |               | Timer input pin<br>The data on this pin is used as event count signal for timer 1.<br>Timer output pin<br>This function is available when the timer output from timer 1 is<br>enabled.                                                                |  |

| 20       | P44             | E<br>(CMOS/H) | General-purpose I/O port<br>This function is available when the timer output from timer 2 is<br>disabled.                                                                                                                                             |  |

|          | TIO2            |               | Timer input pin<br>The data on this pin is used as event count signal for timer 2.<br>Timer output pin<br>This function is available when the timer output from timer 2 is<br>enabled.                                                                |  |

| 21       | Vcc             | Power supply  | Digital circuit power supply pin                                                                                                                                                                                                                      |  |

| 22, 23   | P45, P46        | H<br>(CMOS)   | Open-drain I/O ports                                                                                                                                                                                                                                  |  |

| 24 to 27 | V0 to V3        | Power supply  | LCDC reference power supply pins                                                                                                                                                                                                                      |  |

| 28 to 31 | COM0 to<br>COM3 | К             | LCDC common pins                                                                                                                                                                                                                                      |  |

| 32       | AVcc            | Power supply  | Analog circuit power supply pin<br>This power supply must only be turned on or off when electric<br>potential of AVcc or greater is applied to Vcc.                                                                                                   |  |

| 33       | AVRH            | Power supply  | Analog circuit reference voltage input pin<br>This pin must only be turned on or off when electric potential of<br>AVRH or greater is applied to $AV_{CC}$ .                                                                                          |  |

| 34       | AVRL            | Power supply  | Analog circuit reference voltage input pin                                                                                                                                                                                                            |  |

| 35       | AVss            | Power supply  | Analog circuit power supply (GND) pin                                                                                                                                                                                                                 |  |

| Pin no.  | Pin name          | Circuit type  | Function                                                                                                                      |

|----------|-------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|

| 36 to 39 | P50 to P53        | l<br>(AD)     | General-purpose I/O ports<br>This function is available when "port" is specified in the analog input<br>enable register.      |

|          | AN0 to AN3        |               | A/D converter analog input pins<br>This function is available when the analog input enable register<br>specification is "AD." |

| 40       | Vss               | Power supply  | Digital circuit power supply (GND) pin                                                                                        |

| 41 to 46 | SEG00 to<br>SEG05 | К             | LCDC segment-only pins                                                                                                        |

| 47 to 49 | MD0 to MD2        | C<br>(CMOS)   | Operating mode selection input pins<br>Connect directly to Vcc or Vss.                                                        |

| 50 to 59 | SEG06 to<br>SEG15 | К             | LCDC segment-only pins                                                                                                        |

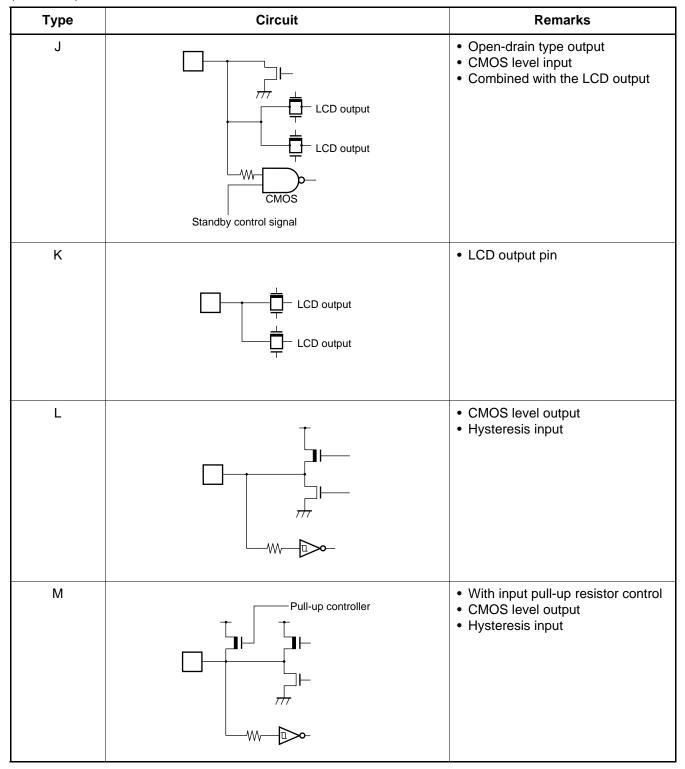

| 60 to 67 | P60 to P67        | J             | Open-drain I/O ports<br>This is available when enabled by the LCR2.                                                           |

|          | SEG16 to<br>SEG23 |               | LCDC segment pins                                                                                                             |

| 68 to 74 | P70 to P76        | J             | Open-drain I/O ports<br>This is available when enabled by the LCR2.                                                           |

|          | SEG24 to<br>SEG30 |               | LCDC segment pins                                                                                                             |

| 75       | RST               | B<br>(CMOS/H) | External reset request input pin                                                                                              |

| 76       | P77               | J             | Open-drain I/O port<br>This is available when enabled by the LCR2.                                                            |

|          | SEG31             |               | LCDC segment pin                                                                                                              |

To Top / Lineup / Index

### **MB90620A Series**

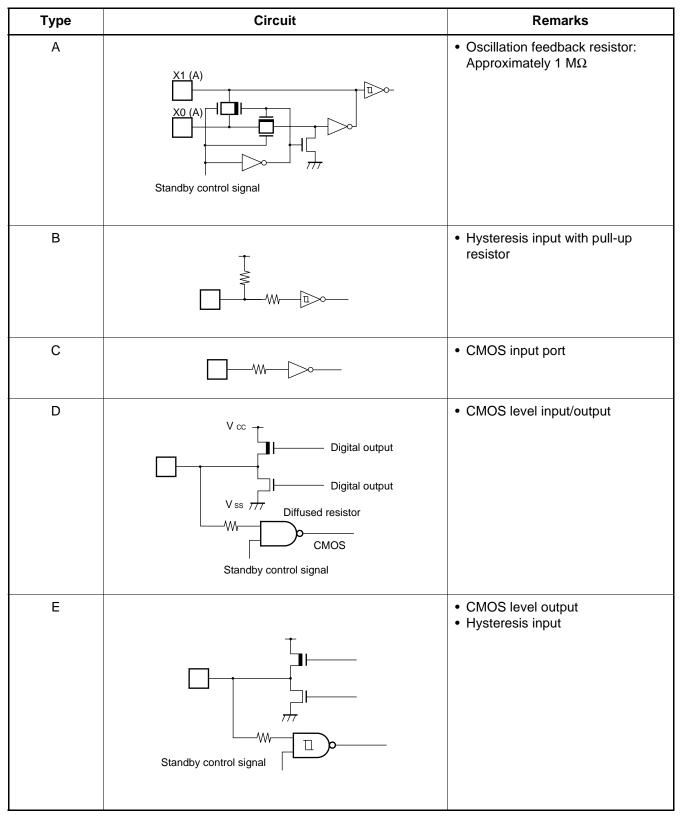

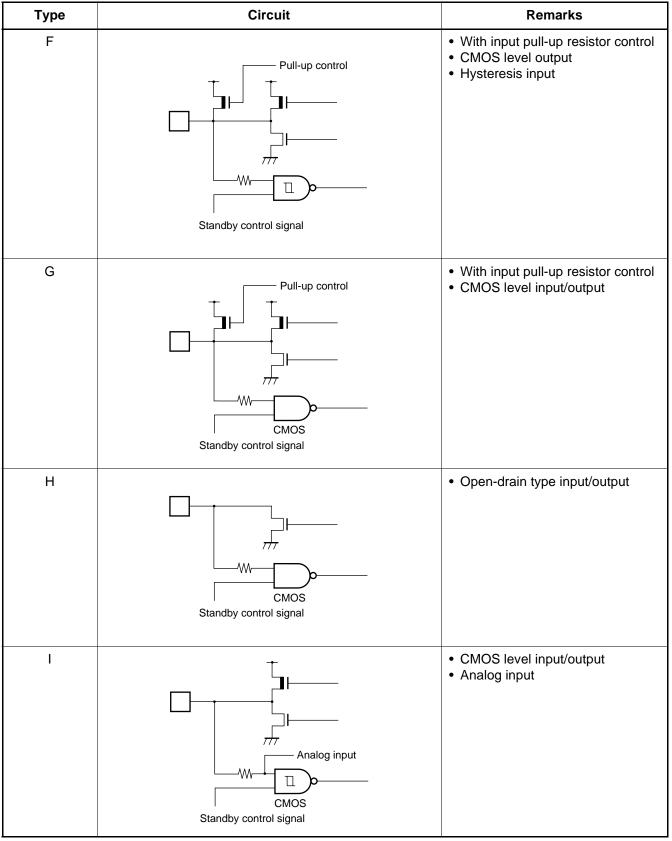

### ■ I/O CIRCUIT TYPE

| 1Can   | tinued) |

|--------|---------|

| 11,011 | muea    |

|        |         |

### ■ HANDLING DEVICES

#### 1. Preventing Latchup

Latchup may occur on CMOS ICs if voltage higher than Vcc or lower than Vss is applied to the input and output pins other than medium- and high voltage pins or if higher than the voltage is applied between Vcc and Vss.

When latchup occurs, power supply current increases rapidly and might thermally damage elements. When using, take great care not to exceed the absolute maximum ratings.

#### 2. Treatment of Unused Pins

Leaving unused input pins open could cause malfunctions. They should be connected to a pull-up or pull-down resistors.

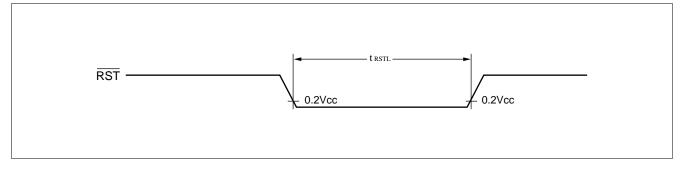

#### 3. External Reset Input

To reset the internal circuit by the Low-level input to the  $\overline{RST}$  pin, the Low-level input to the  $\overline{RST}$  pin must be maintained for at least five machine cycles. Pay attention to it if the chip uses external clock input.

#### 4. Vcc and Vss Pins

Apply equal potential to the Vcc and Vss pins.

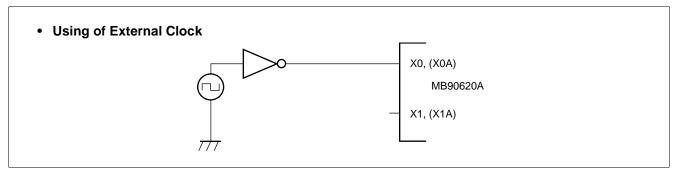

#### 5. Precautions when Using an External Clock

When an external clock is used, drive X0 pin.

### 6. Sequence for Applying A/D Converter Power Supply and Analog Inputs

Be sure to turn on the digital power supply (Vcc) before applying the A/D converter power supply (AVcc, AVRH, and AVRL) and the analog inputs (AN0 to AN15).

In addition, when the power is turned off, turn off the A/D converter power supply (AVcc, AVRH, and AVRL) and the analog inputs (AN0 to AN15) first, and then turn off the digital power supply (AVcc).

Whether applying or cutting off the power, be certain that AVRH does not exceed AVcc.

#### 7. Program Mode

In the MB90P623, all of the bits (48 K  $\times$  8 bits) are set to "1" when the IC is shipped from Fujitsu and after erasure. To input data, program the IC by selectively setting the desired bits to "0". Bits cannot be set to "1" electrically.

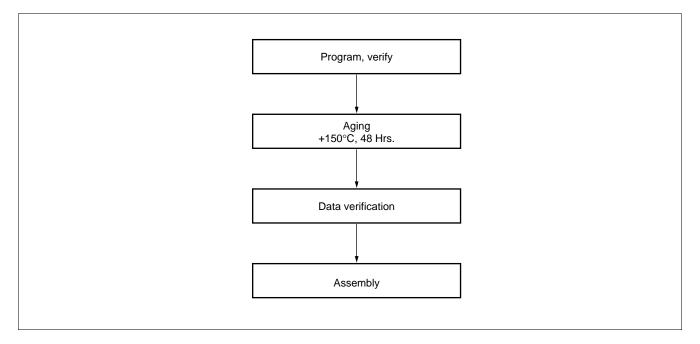

### 8. Recommended Screening Conditions

High-temperature aging is recommended as the pre-assembly screening procedure for a product with a blanked OTPROM width microcontroller program.

### 9. Programming Yield

All bit cannot be programmed at Fujitsu shipping test to a blanked OTPROM microcomputer, due to its nature. For this reason, a programming yield of 100% cannot be assured at all times.

### ■ PROGRAMMING TO THE EPROM ON THE MB90P623A

In EPROM mode, the MB90P623 EPROM functions equivalent to the MBM27C1000. This allows the PROM to be programmed with a general-purpose EPROM programmer by using the dedicated socket adapter.

#### 1. EPROM Mode Pin Assignments

#### • MBM27C1000 compatible pins

| MBM2    | MBM27C1000 |         | P623A     |

|---------|------------|---------|-----------|

| Pin no. | Pin name   | Pin no. | Pin name  |

| 1       | Vpp        | 49      | MD2 (Vpp) |

| 2       | OE*        | 10      | P32       |

| 3       | A15        | 98      | P17       |

| 4       | A12        | 95      | P14       |

| 5       | A07        | 6       | P27       |

| 6       | A06        | 5       | P26       |

| 7       | A05        | 4       | P25       |

| 8       | A04        | 3       | P24       |

| 9       | A03        | 2       | P23       |

| 10      | A02        | 1       | P22       |

| 11      | A01        | 100     | P21       |

| 12      | A00        | 99      | P20       |

| 13      | D00        | 83      | P00       |

| 14      | D01        | 84      | P01       |

| 15      | D02        | 85      | P02       |

| 16      | GND*       | —       | —         |

| MBM2    | 7C1000           | MB90 | P623A    |

|---------|------------------|------|----------|

| Pin no. | Pin no. Pin name |      | Pin name |

| 32      | Vcc              | —    | —        |

| 31      | PGM              | 11   | P33      |

| 30      | N.C.             | —    | —        |

| 29      | A14              | 97   | P16      |

| 28      | A13              | 96   | P15      |

| 27      | A08              | 91   | P10      |

| 26      | A09              | 92   | P11      |

| 25      | A11              | 94   | P13      |

| 24      | A16              | 7    | P30      |

| 23      | A10              | 93   | P12      |

| 22      | CE               | 8    | P31      |

| 21      | A07              | 90   | P07      |

| 20      | D06              | 89   | P06      |

| 19      | D05              | 88   | P05      |

| 18      | D04              | 87   | P04      |

| 17      | D03              | 86   | P03      |

\* : Connect a capacitance of 20 pF across OE (pin no.2) and GND (pin no.16) pins of the MBM27C1000.

### • Power supply, GND connection pins

| Classification | Pin no.                                           | Pin name                                                      |

|----------------|---------------------------------------------------|---------------------------------------------------------------|

| Power supply   | 21<br>82                                          | Vcc<br>Vcc                                                    |

| GND            | 9<br>34<br>35<br>40<br>75<br>79<br>12<br>13<br>14 | Vss<br>AVRL<br>AVss<br>Vss<br>RST<br>Vss<br>P34<br>P35<br>P36 |

| Pin no.                                                                          | Pin name                               | Treatment                                                     |

|----------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------|

| 47<br>48<br>80<br>78                                                             | MD0<br>MD1<br>X0<br>X0A                | Connect a pull-up resistor of 4.7 k $\Omega$                  |

| 81<br>77<br>28 to 31<br>41 to 46<br>50 to 59                                     |                                        | - OPEN                                                        |

| 15<br>16 to 20<br>22<br>23<br>24 to 27<br>32<br>33<br>36 to 39<br>60 to 74<br>76 | P45<br>P46<br>V0 to V3<br>AVcc<br>AVRH | Connect a pull-up<br>– resistor of about<br>1 MΩ to each pin. |

### Non-MBM27C1000 compatible pins

### 2. EPROM Programmer Socket Adapter

| Part no.     | Package  | Compatible socket adapter<br>Sun Hayato Co., Ltd. |

|--------------|----------|---------------------------------------------------|

| MB90P623APFV | SQFP-100 | ROM-100SQF-32DP-16L                               |

Inquiry: Sun Hayato Co., Ltd.: TEL (81)-3-3986-0403 FAX (81)-3-5396-9106

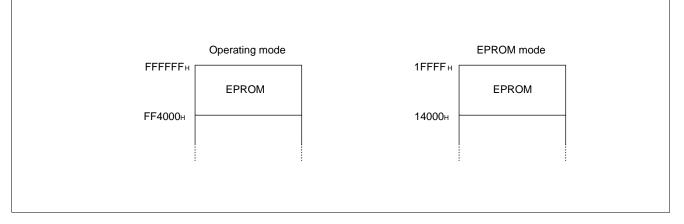

### 3. Programming Procedure

- (1) Set the EPROM programmer to the MBM27C1000.

- (2) Load the program data into the EPROM programmer at  $14000_{H}$  to  $1FFFF_{H}$ .

The ROM addresses from FF4000 $_{\text{H}}$  to FFFFF<sub>H</sub> in operating mode of MB90P623A series correspond to 14000 $_{\text{H}}$  to 1FFFF<sub>H</sub> in EPROM mode.

- (3) Insert the MB90P623A in the socket adapter, and mount the socket adapter on the EPROM programmer. Pay attention to the orientation of the device and of the socket adapter when doing so.

- (4) Activate the programming.

- (5) If programming cannot be performed successfully, connect a 0.1  $\mu$ F or similar capacitor between V<sub>cc</sub> and GND and between V<sub>PP</sub> and GND.

- Note: Because the mask ROM products (MB90623A) do not have an EPROM mode, they cannot read data from the EPROM programmer.

### BLOCK DIAGRAM

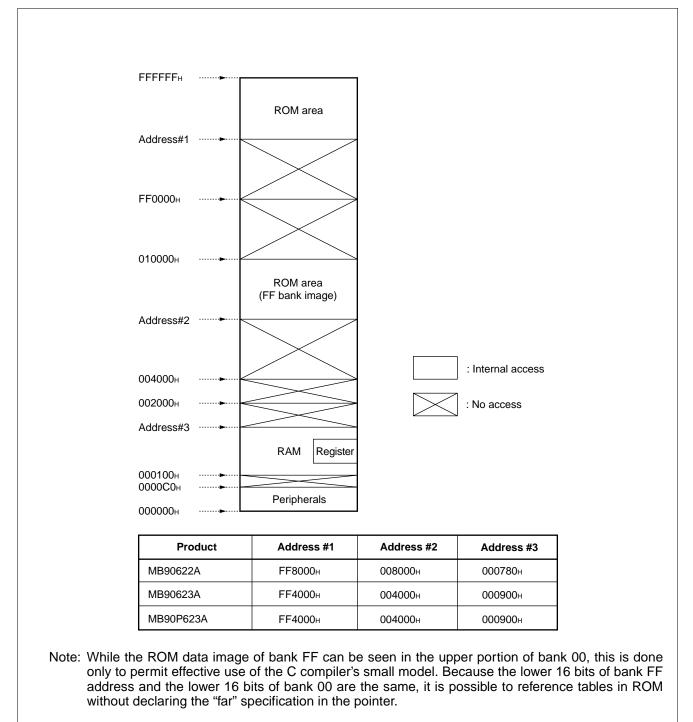

### MEMORY MAP

### ■ I/O MAP

| Address           | Register                                         | Register<br>name | Access | Resource<br>name                 | Initial value   |

|-------------------|--------------------------------------------------|------------------|--------|----------------------------------|-----------------|

| 00000н            | Port 0 data register                             | PDR0             | R/W    | Port 0                           | XXXXXXXX        |

| 000001н           | Port 1 data register                             | PDR1             | R/W    | Port 1                           | XXXXXXXX        |

| 000002н           | Port 2 data register                             | PDR2             | R/W    | Port 2                           | XXXXXXXX        |

| 00003н            | Port 3 data register                             | PDR3             | R/W    | Port 3                           | XXXXXXXX        |

| 000004н           | Port 4 data register                             | PDR4             | R/W    | Port 4                           | - X X X X X X X |

| 000005н           | Port 5 data register                             | PDR5             | R/W    | Port 5                           | XXX             |

| 00006н            | Port 6 data register                             | PDR6             | R/W    | Port 6                           | XXXXXXXX        |

| 000007н           | Port 7 data register                             | PDR7             | R/W    | Port 7                           | - X X X X X X X |

| 000008н<br>to 0Fн |                                                  | Vacanc           | у*     |                                  |                 |

| 000010н           | Port 0 direction register                        | DDR0             | R/W    | Port 0                           | 00000000        |

| 000011н           | Port 1 direction register                        | DDR1             | R/W    | Port 1                           | 00000000        |

| 000012н           | Port 2 direction register                        | DDR2             | R/W    | Port 2                           | 00000000        |

| 000013н           | Port 3 direction register                        | DDR3             | R/W    | Port 3                           | 00000000        |

| 000014н           | Port 4 direction register                        | DDR4             | R/W    | Port 4                           | -0000000        |

| 000015н           | Port 5 direction register                        | DDR5             | R/W    | Port 5                           | 0000            |

| 000016н           | Port 6 direction register                        | DDR6             | R/W    | Port 6                           | 00000000        |

| 000017н           | Port 7 direction register                        | DDR7             | R/W    | Port 7                           | 00000000        |

| 000018н<br>to 19н |                                                  | Vacanc           | У*     |                                  |                 |

| 00001Ан           | Port 0 pull-up resistor setting register         | RDR0             | R/W    | Port 0                           | 00000000        |

| 00001Вн           | Port 1 pull-up resistor setting register         | RDR1             | R/W    | Port 1                           | 00000000        |

| 00001Сн           | Port 2 pull-up resistor setting register         | RDR2             | R/W    | Port 2                           | 00000000        |

| 00001Dн           | Analog input enable register                     | ADER             | R/W    | A/D                              | 1111            |

| 00001Eн           | Clock output enable register                     | СКОТ             | R/W    | Clock output (CKOT)              | 0000            |

| 00001Fн           |                                                  | Vacanc           | у*     |                                  |                 |

| 000020н           | Serial mode register                             | SMR              | R/W    |                                  | 00000000        |

| 000021н           | Serial control register                          | SCR              | R/W    |                                  | 00000100        |

| 000022н           | Serial input register/<br>Serial output register | SIDR/<br>SODR    | R/W    | UART                             | xxxxxxxx        |

| 000023н           | Serial status register                           | SSR              | R/W    |                                  | 000100          |

| 000024н           | Sorial mode control status register              | SMCS             |        |                                  | 00000           |

| 000025н           | Serial mode control status register              | SMCS             | R/W    | Extended serial<br>I/O interface | 00000010        |

| 000026н           | Serial data register                             | SDR              | R/W    |                                  | XXXXXXXX        |

| Address            | Register                                 | Register<br>name | Access | Resource<br>name      | Initial value          |  |  |  |  |  |

|--------------------|------------------------------------------|------------------|--------|-----------------------|------------------------|--|--|--|--|--|

| 000027н            | Communication prescaler control register | CDCR             | R/W    | UART, I/O, serial     | 0 1 1 1 1              |  |  |  |  |  |

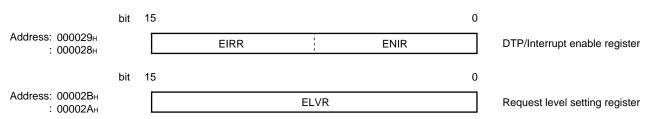

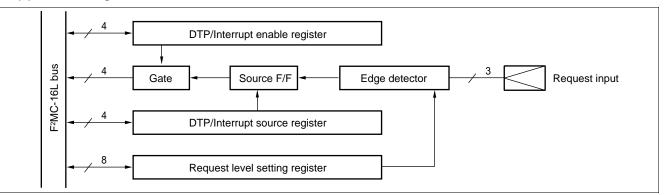

| 000028н            | DTP/Interrupt enable register            | ENIR             | R/W    |                       | 00000000               |  |  |  |  |  |

| 000029н            | DTP/Interrupt source register            |                  |        |                       |                        |  |  |  |  |  |

| 00002Ан            | Degreet level eatting to gister          |                  |        | interrupt             | 00000000               |  |  |  |  |  |

| 00002Вн            | Request level setting register           | ELVR             | R/W    |                       | 00000000               |  |  |  |  |  |

| 00002Сн            | A/D control status register              | ADCS0            |        |                       | 00000000               |  |  |  |  |  |

| 00002Dн            | A/D control status register              | ADCS1            | R/W    | 8/10-bit              | 00000000               |  |  |  |  |  |

| 00002Ен            | A/D data za sista z                      | ADCR0            |        | A/D converter         | XXXXXXXX               |  |  |  |  |  |

| 00002Fн            | A/D data register                        | ADCR1            | R/W    |                       | 0 0 0 0 0 0 X X        |  |  |  |  |  |

| 000030н            | DDC0 evels acting register               | DCSDO            | W      |                       | x x x x x x x x x      |  |  |  |  |  |

| 000031н            | PPG0 cycle setting register              | PCSR0            | VV     |                       | XXXXXXXX               |  |  |  |  |  |

| 000032н            | DDC0 duty factor acting register         | DDUTO            | 14/    | 16-bit                | XXXXXXXX               |  |  |  |  |  |

| 000033н            | PPG0 duty factor setting register        | PDUT0            | W      | PPG timer 0           | XXXXXXXX               |  |  |  |  |  |

| 000034н            | DDC0 control status register             | PCNL0            |        | _                     | 00000000               |  |  |  |  |  |

| 000035н            | PPG0 control status register             | PCNH0            | R/W    |                       | 000000-                |  |  |  |  |  |

| 000036н            |                                          | Vacanc           | y*     |                       |                        |  |  |  |  |  |

| to 37н             |                                          |                  |        |                       | xxxxxxx                |  |  |  |  |  |

| 000038н<br>000039н | PPG1 cycle setting register              | PCSR1            | W      |                       |                        |  |  |  |  |  |

|                    |                                          |                  |        | _                     | XXXXXXXXX<br>XXXXXXXXX |  |  |  |  |  |

| 00003Ан<br>00003Вн | PPG1 duty factor setting register        | PDUT1            | W      | 16-bit<br>PPG timer 1 | ×××××××××              |  |  |  |  |  |

| 00003Сн            |                                          | PCNL1            |        | -                     | 00000000               |  |  |  |  |  |

| 00003Cн<br>00003Dн | PPG1 control status register             | PCNL1<br>PCNH1   | R/W    |                       | 00000000               |  |  |  |  |  |

| 00003Ен,           |                                          | FONH             |        |                       | 0000000                |  |  |  |  |  |

| 00003Eн,<br>3Fн    |                                          | Vacanc           | у*     |                       |                        |  |  |  |  |  |

| 000040н            | Time on a sectoral attaction as sisters  | TMOODO           |        |                       | 00000000               |  |  |  |  |  |

| 000041н            | Timer control status register            | TMCSR0           | R/W    |                       | 0000                   |  |  |  |  |  |

| 000042н            | 16 bit timer register                    |                  |        | 16-bit                | xxxxxxxx               |  |  |  |  |  |

| 000043н            | 16-bit timer register                    | TMR0             | R/W    | reload timer 0        | XXXXXXXX               |  |  |  |  |  |

| 000044н            | 16 bit relead register                   |                  |        |                       | XXXXXXXX               |  |  |  |  |  |

| 000045н            | 16-bit reload register                   | TMRLR0           | R/W    |                       | XXXXXXXX               |  |  |  |  |  |

| Address           | Register                          | Register<br>name | Access  | Resource<br>name           | Initial value     |

|-------------------|-----------------------------------|------------------|---------|----------------------------|-------------------|

| 000046н           | Timor control status register 1   |                  | R/W     |                            | 00000000          |

| 000047н           | Timer control status register 1   | TMCSR1           | r./ v v |                            | 0000              |

| 000048н           | 16-bit timer register 1           | TMR1             | R/W     | 16-bit                     | XXXXXXXX          |

| 000049н           |                                   |                  | r/ vv   | reload timer 1             | XXXXXXXX          |

| 00004Ан           | 16-bit reload register 1          | TMRLR1           | R/W     | _                          | XXXXXXXX          |

| 00004Вн           | To-bit Teload Tegister T          |                  | Γ./ ٧ ٧ |                            | XXXXXXXX          |

| 00004Cн<br>to 4Fн |                                   | Vacanc           | у*      |                            |                   |

| 000050н           |                                   | TMOODO           | DAA     |                            | 00000000          |

| 000051н           | Timer control status register 2   | TMCSR2           | R/W     |                            | 0000              |

| 000052н           | 16 bit timer register 2           | тиро             |         | 16-bit                     | XXXXXXXX          |

| 000053н           | 16-bit timer register 2           | TMR2             | R/W     | reload timer 2             | XXXXXXXX          |

| 000054н           | 10 bit related register 2         |                  | R/W     | _                          | XXXXXXXX          |

| 000055н           | 16-bit reload register 2          | TMRLR2           | R/W     |                            | XXXXXXXX          |

| 000056н           | Timor data register 0             | TCDT0            | D       |                            | 00000000          |

| 000057н           | Timer data register 0             |                  | R       | 16-bit free-run<br>timer 0 | 00000000          |

| 000058н           | Timer control status register 0   | TCS0             | R/W     |                            | 00000000          |

| 000059н           | Compare control status register 0 | CCS0             | R/W     |                            | 000000            |

| 00005Ан           | Timer 0 compore register 0        | TCD00            |         |                            | X X X X X X X X X |

| 00005Вн           | Timer 0 compare register 0        | TCR00            | R/W     | Compare<br>register block  | X X X X X X X X X |

| 00005Сн           | Timer 0 compore register 1        | TCR01            | R/W     |                            | XXXXXXXX          |

| 00005Dн           | Timer 0 compare register 1        | ICRUI            | r./ v v |                            | X X X X X X X X X |

| 00005Eн,<br>5Fн   |                                   | Vacanc           | у*      |                            |                   |

| 000060н           | Timor data register 4             |                  | D       |                            | 00000000          |

| 000061н           | Timer data register 1             | TCDT1            | R       | 16-bit free-run<br>timer 1 | 00000000          |

| 000062н           | Timer control status register 1   | TCS1             | R/W     |                            | 00000000          |

| 000063н           | Compare control status register 1 | CCS1             | R/W     |                            | 000000            |

| 000064н           | Timer 1 compare register 0        |                  |         |                            | XXXXXXXX          |

| 000065н           | Timer 1 compare register 0        | TCR10            | R/W     | Compare<br>register block  | XXXXXXXX          |

| 000066н           | Timer 1 compare register 1        | TOD44            |         |                            | XXXXXXXX          |

| 000067н           | Timer 1 compare register 1        | TCR11            | R/W     |                            | XXXXXXXX          |

| Address           | Register                                                 | Register<br>name               | Access                   | Resource<br>name                    | Initial value   |  |  |  |  |  |

|-------------------|----------------------------------------------------------|--------------------------------|--------------------------|-------------------------------------|-----------------|--|--|--|--|--|

| 000068н<br>to 6Fн |                                                          | Vacanc                         | У*                       |                                     |                 |  |  |  |  |  |

| 000070н           | LCD display data RAM                                     | VRAM                           | R/W                      |                                     | XXXXXXXX        |  |  |  |  |  |

| to 7Fн            |                                                          | VICAIVI                        | Γ\/ ¥ ¥                  | LCD controller/                     | XXXXXXXX        |  |  |  |  |  |

| 000080н           | LCDC control register 0                                  | driver                         | 00010000                 |                                     |                 |  |  |  |  |  |

| 000081н           | LCDC control register 1                                  | DC control register 1 LCR1 R/W |                          |                                     |                 |  |  |  |  |  |

| 000082н<br>to 8Fн |                                                          | Vacanc                         | У*                       |                                     |                 |  |  |  |  |  |

| 000090н<br>to 9Eн | S                                                        | ystem reserv                   | ed area*                 |                                     |                 |  |  |  |  |  |

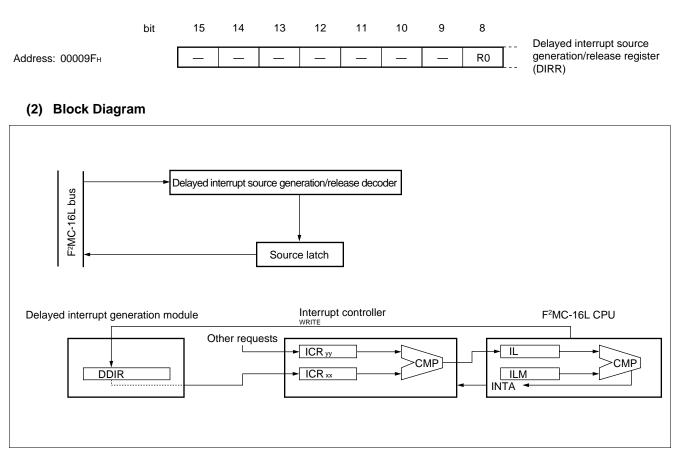

| 00009Fн           | Delayed interrupt source generation/<br>release register | DIRR                           | R/W                      | Delayed interrupt generation module | 0               |  |  |  |  |  |

| 0000А0н           | Low-power consumption mode control register              | LPMCR                          | Low-power<br>consumption | 00011000                            |                 |  |  |  |  |  |

| 0000A1н           | Clock selection register                                 | CKSCR                          | R/W                      | consumption                         | 1111100         |  |  |  |  |  |

| 0000А2н<br>to А7н |                                                          | Vacanc                         | У*                       |                                     |                 |  |  |  |  |  |

| 0000А8н           | Watchdog timer control register                          | WDTC                           | R/W                      | Watchdog timer                      | XXXXXXXX        |  |  |  |  |  |

| 0000А9н           | Timebase timer control register                          | TBTC                           | R/W                      | Timebase timer                      | 1 0 0 0 0 0     |  |  |  |  |  |

| 0000ААн           | Watch timer control register                             | WTC                            | R/W                      | Watch timer                         | 1 X - 0 0 0 0 0 |  |  |  |  |  |

| 0000ABн<br>to AFн |                                                          | Vacanc                         | У*                       |                                     |                 |  |  |  |  |  |

| 0000В0н           | Interrupt control register 00                            | ICR00                          | R/W                      |                                     | 00000111        |  |  |  |  |  |

| 0000В1н           | Interrupt control register 01                            | ICR01                          | R/W                      | _                                   | 00000111        |  |  |  |  |  |

| 0000В2н           | Interrupt control register 02                            | ICR02                          | R/W                      | _                                   | 00000111        |  |  |  |  |  |

| 0000ВЗн           | Interrupt control register 03                            | ICR03                          | R/W                      |                                     | 00000111        |  |  |  |  |  |

| 0000B4н           | Interrupt control register 04                            | ICR04                          | R/W                      |                                     | 00000111        |  |  |  |  |  |

| 0000B5н           | Interrupt control register 05                            | ICR05                          | R/W                      |                                     | 00000111        |  |  |  |  |  |

| 0000В6н           | Interrupt control register 06                            | ICR06                          | R/W                      | Interrupt                           | 00000111        |  |  |  |  |  |

| 0000 <b>В7</b> н  | Interrupt control register 07                            | ICR07                          | R/W                      | controller                          | 00000111        |  |  |  |  |  |

| 0000B8н           | Interrupt control register 08                            | ICR08                          | R/W                      |                                     | 00000111        |  |  |  |  |  |

| 0000В9н           | Interrupt control register 09                            | ICR09                          | R/W                      | _                                   | 00000111        |  |  |  |  |  |

| 0000ВАн           | Interrupt control register 10                            | ICR10                          | R/W                      |                                     | 00000111        |  |  |  |  |  |

| 0000ВВн           | Interrupt control register 11                            | ICR11                          | R/W                      |                                     | 00000111        |  |  |  |  |  |

| 0000BCH           | Interrupt control register 12                            | ICR12                          | R/W                      |                                     | 00000111        |  |  |  |  |  |

| 0000BDH           | Interrupt control register 13                            | ICR13                          | R/W                      |                                     | 00000111        |  |  |  |  |  |

(Continued)

| Address           | Register                      | Register<br>name | Access | Resource<br>name | Initial value |

|-------------------|-------------------------------|------------------|--------|------------------|---------------|

| 0000BEH           | Interrupt control register 14 | ICR14            | R/W    | Interrupt        | 00000111      |

| 0000BFH           | Interrupt control register 15 | ICR15            | R/W    | controller       | 00000111      |

| 0000C0н<br>to FFн |                               | Vacanc           | y*     |                  |               |

\* : Access prohibited.

Explanation of initial values

0: The initial value of this bit is "0".

1: The initial value of this bit is "1".

X: The initial value of this bit is undefined.

-: This bit is not used. No initial value is defined.

### ■ INTERRUPT SOURCES AND THEIR INTERRUPT VECTORS AND INTERRUPT CONTROL REGISTERS

| Interrupt source                                | l <sup>2</sup> OS | In  | terrupt     | vector              | Interru<br>reç | ot control<br>gister |

|-------------------------------------------------|-------------------|-----|-------------|---------------------|----------------|----------------------|

|                                                 | support           | N   | 0.          | Address             | ICR            | Address              |

| Reset                                           | ×                 | #08 | 08н         | <b>FFFFDC</b> H     | _              | _                    |

| INT9 instruction                                | ×                 | #09 | 09н         | FFFFD8H             | _              | —                    |

| Exception                                       | ×                 | #10 | 0Ан         | FFFFD4H             |                |                      |

| External interrupt #0                           | 0                 | #11 | 0Вн         | FFFFD0H             | ICR00          | 0000В0н              |

| External interrupt #1                           | 0                 | #12 | 0Сн         | <b>FFFFCC</b> H     | 101100         | UUUUBUH              |

| External interrupt #2                           | 0                 | #13 | 0Dн         | FFFFC8H             |                | 0000B1н              |

| External interrupt #3                           | 0                 | #14 | 0Ен         | FFFFC4 <sub>H</sub> | ICR01          |                      |

| External interrupt #4                           | 0                 | #15 | 0Fн         | FFFFC0H             |                | 0000000              |

| External interrupt #5                           | 0                 | #16 | 10н         | FFFFBCH             | ICR02          | 0000B2н              |

| External interrupt #6                           | 0                 | #17 | 11н         | FFFFB8H             |                | 0000000              |

| External interrupt #7                           | 0                 | #18 | 12н         | FFFFB4H             | ICR03          | 0000ВЗн              |

| Extended serial I/O interface                   | 0                 | #19 | 13н         | FFFFB0H             | ICR04          | 0000B4н              |

| Free-run timer 0 overflow                       | 0                 | #21 | <b>15</b> н | FFFFA8H             |                | 0000B5н              |

| Free-run timer 1 overflow                       | 0                 | #22 | <b>16</b> н | FFFFA4H             | ICR05          |                      |

| Free-run timer 0 and compare register 0 matched | 0                 | #23 | <b>17</b> н | FFFFA0H             | ICR06          | 0000В6н              |

| Free-run timer 0 and compare register 1 matched | 0                 | #24 | <b>18</b> н | FFFF9CH             |                |                      |

| Free-run timer 1 and compare register 0 matched | 0                 | #25 | <b>19</b> н | FFFF98H             |                | 000007               |

| Free-run timer 1 and compare register 1 matched | 0                 | #26 | 1Ан         | FFFF94H             | ICR07          | 0000 <b>B7</b> н     |

| PPG timer #0                                    | 0                 | #27 | 1Bн         | FFFF90H             |                | 0000000              |

| PPG timer #1                                    | 0                 | #28 | 1Cн         | FFFF8CH             | ICR08          | 0000B8н              |

| 16-bit reload timer #0                          | 0                 | #29 | 1Dн         | FFFF88H             |                | 0000000              |

| 16-bit reload timer #1                          | 0                 | #30 | <b>1Е</b> н | FFFF84 <sub>H</sub> | ICR09          | 0000В9н              |

| 16-bit reload timer #2                          | 0                 | #31 | 1Fн         | FFFF80H             | ICR10          | 0000ВАн              |

| A/D converter measurement complete              | 0                 | #33 | 21н         | FFFF78н             | ICR11          | 0000ВВн              |

| Watch prescaler                                 | ×                 | #35 | 23н         | FFFF70H             | ICR12          | 0000ВСн              |

| Timebase timer interval interrupt               | ×                 | #36 | 24н         | FFFF6CH             |                | UUUUDCH              |

| UART 0 transmission complete                    | 0                 | #37 | 25н         | FFFF68H             | ICR13          | 0000BDн              |

| UART 1 reception complete                       | 0                 | #39 | 27н         | FFFF60H             | ICR14          | 0000BEн              |

| Delayed interrupt generation module             | ×                 | #42 | 2Ан         | FFFF54H             | ICR15          | 0000BFн              |

○: The request flag is cleared by the I<sup>2</sup>OS interrupt clear signal (without stop requests).

©: The request flag is cleared by the I<sup>2</sup>OS interrupt clear signal (with stop requests).

$\times$ : The request flag is not cleared by the I<sup>2</sup>OS interrupt clear signal.

Note: Do not set I<sup>2</sup>OS startup in an ICR<sub>xx</sub> that does not support I<sup>2</sup>OS.

### ■ PERIPHERALS

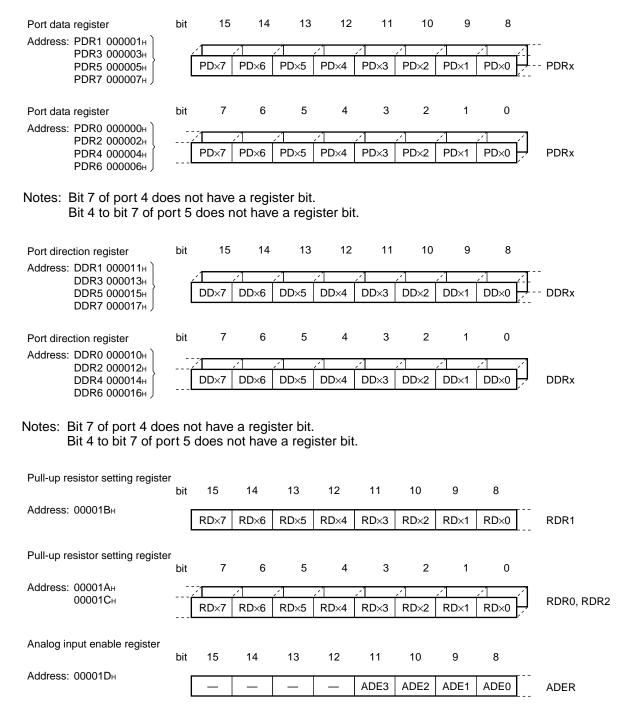

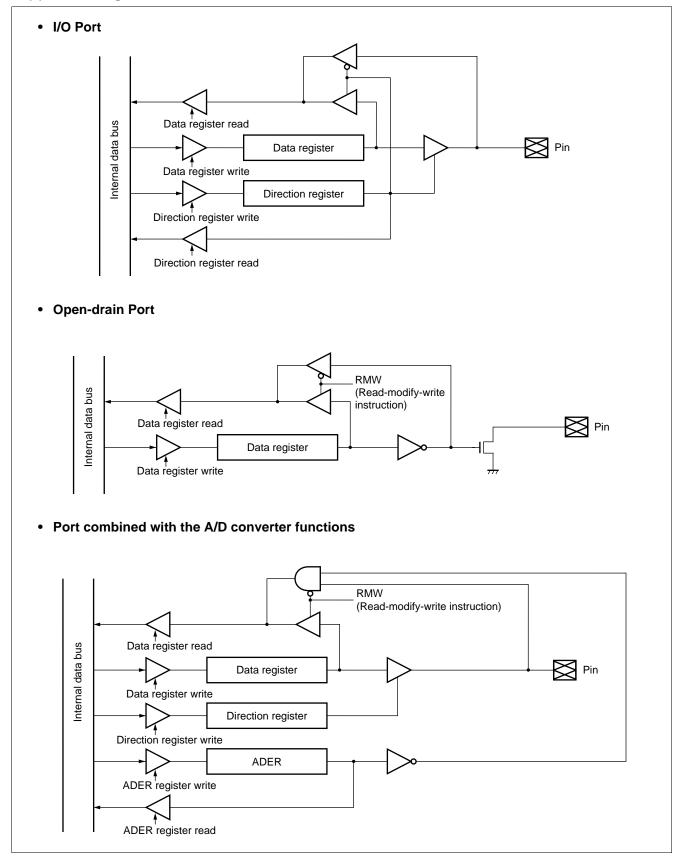

#### **1. Parallel Ports**

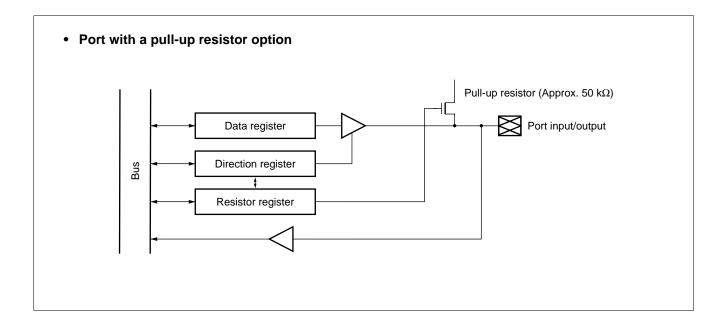

The MB90620A series has 59 input/output pins. In the twenty four input/output ports mapped on port 0 to 2, pull-up resistors are selectively added during input state operations depending on the settings in the resistor setting register. P45, P46, port 6 and port 7 are open-drain ports.

Port 6 and port 7 are combined with the LCD segment pin function.

#### (1) Register configuration

(2) Block Diagram

### 2. UART

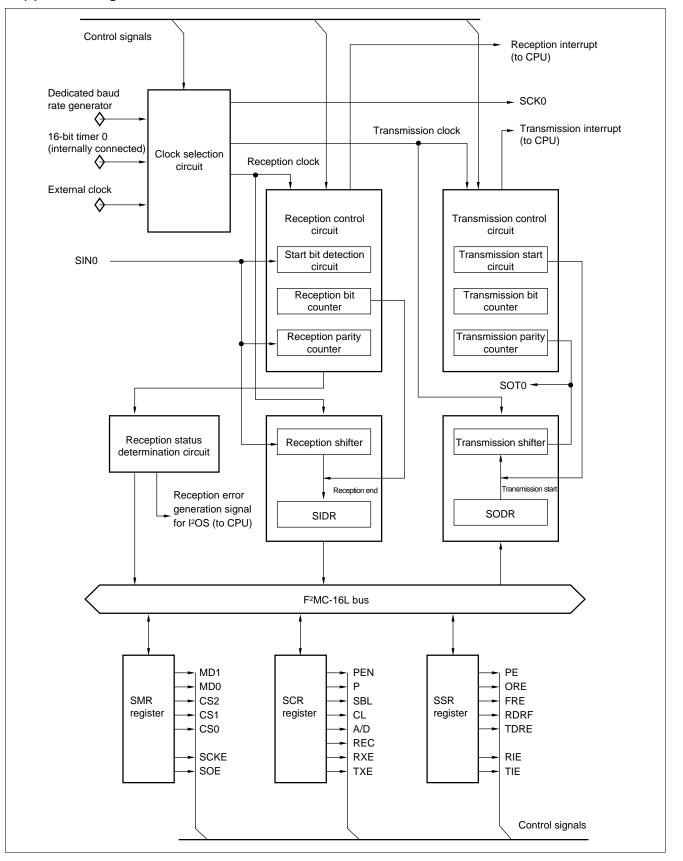

The UART is a serial I/O port for CLK asynchronous (start-stop synchronization) communications or for CLK synchronous communications. The features of this module are described below:

- Full-duplex double buffer

- CLK asynchronous (start-stop synchronization) communications and CLK synchronous communications capable

- Supports multiprocessor mode

- Built-in dedicated baud rate generator

$\begin{array}{c} {\sf CLK} \ {\sf asynchronous:} \ 9615, \ 31250, \ 4808, \ 2404, \ 1202 \ {\sf bps} \\ {\sf CLK} \ {\sf synchronous:} \ 1 \ {\sf M}, \ 500K, \ 250K, \ 125K, \ 62.5K \ {\sf bps} \end{array} \end{array} \right\} \ {\sf For} \ {\sf a} \ 6, \ 8, \ 10, \ 12, \ {\sf or} \ 16 \ {\sf MHz} \ {\sf clock}.$

- · Permits setting of any desired baud rate according to an external clock input

- Error detection function (parity errors, framing errors, and overrun errors)

- NRZ code as transfer signal

- Supports Intelligent I/O Service

#### (1) Register Configuration

|                              | bit | 7   | 6   | 5   | 4    | 3    | 2        | 1    | 0    |                                                           |

|------------------------------|-----|-----|-----|-----|------|------|----------|------|------|-----------------------------------------------------------|

| Address: 000020н             |     | MD1 | MD0 | CS2 | CS1  | CS0  | Reserved | SCKE | SOE  | Serial mode register<br>(SMR)                             |

|                              |     | 15  | 14  | 13  | 12   | 11   | 10       | 9    | 8    |                                                           |

| Address: 000021н             |     | PEN | Р   | SBL | CL   | A/D  | REC      | RXE  | TXE  | Serial control register (SCR)                             |

|                              | bit | 7   | 6   | 5   | 4    | 3    | 2        | 1    | 0    | Serial input register                                     |

| Address: 000022H             |     | D7  | D6  | D5  | D4   | D3   | D2       | D1   | D0   | Serial output register<br>(SIDR/SODR)                     |

| Address: 000023н             | bit | 15  | 14  | 13  | 12   | 11   | 10       | 9    | 8    |                                                           |

| Address: 000023H             |     | PE  | OPE | FRE | RDRF | TDRE | _        | RIE  | TIE  | <ul> <li>Serial status register</li> <li>(SSR)</li> </ul> |

| Address: 000027 <sub>H</sub> | bit | 15  | 14  | 13  | 12   | 11   | 10       | 9    | 8    | Communication prescaler                                   |

| , ddi 033. 000027 n          |     | MD  | _   | _   | _    | DIV3 | DIV2     | DIV1 | DIV0 | control register<br>(CDCR)                                |

#### (2) Block Diagram

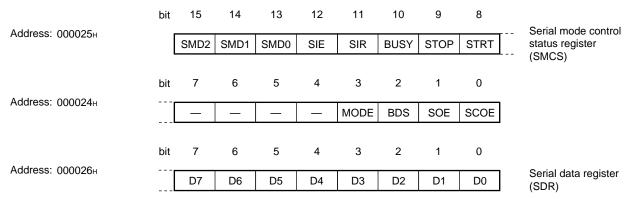

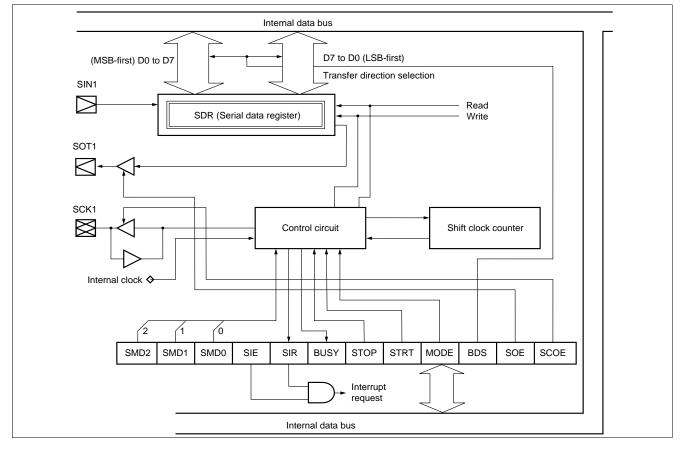

### 3. Extended Serial I/O Interface

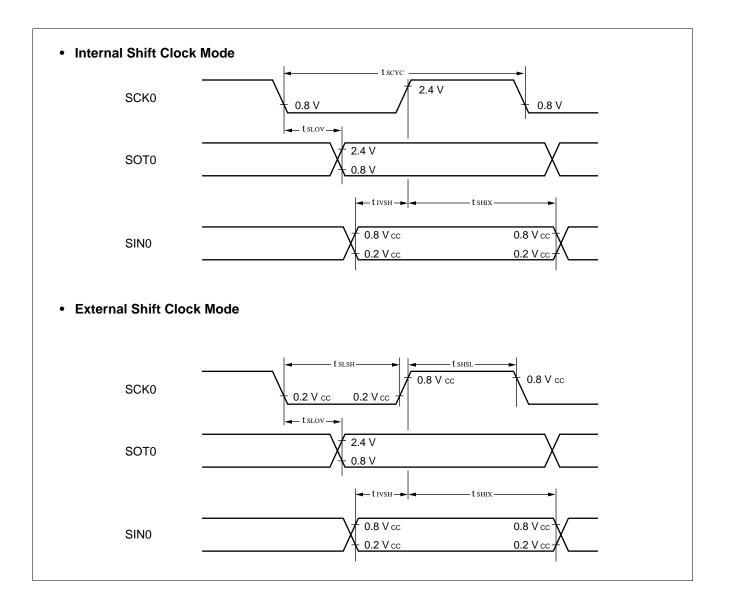

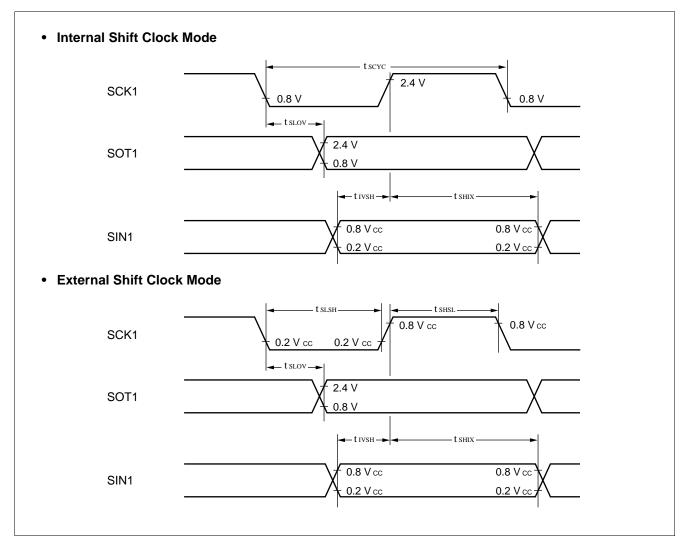

This block consists of an 8-bit serial I/O interface that can perform clock synchronous data transfer. Either LSBfirst or MSB-first data transfer can be selected. The serial I/O port to be used can also be selected. The following two serial I/O operation modes are available.

Internal shift clock mode: Data transfer is synchronization with the internal clock.

External shift clock mode: Data transfer is synchronization with the clock input from the external pin (SCK1). By manipulating the general-purpose port that shares the external pin (SCK1), this mode also enables the data transfer operation to be driven by CPU instructions.

#### (1) Register Configuration

#### (2) Block Diagram

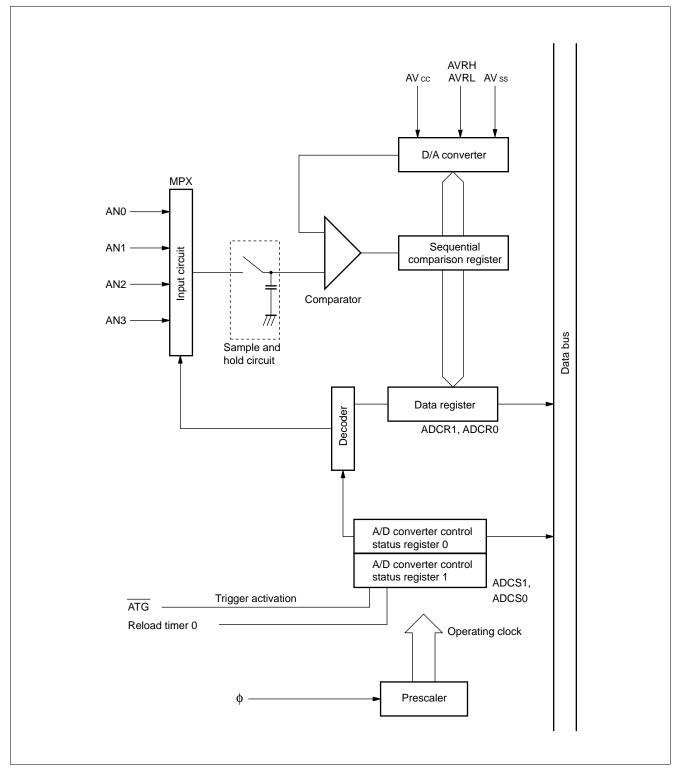

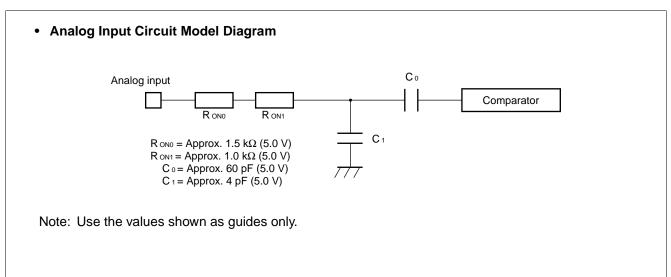

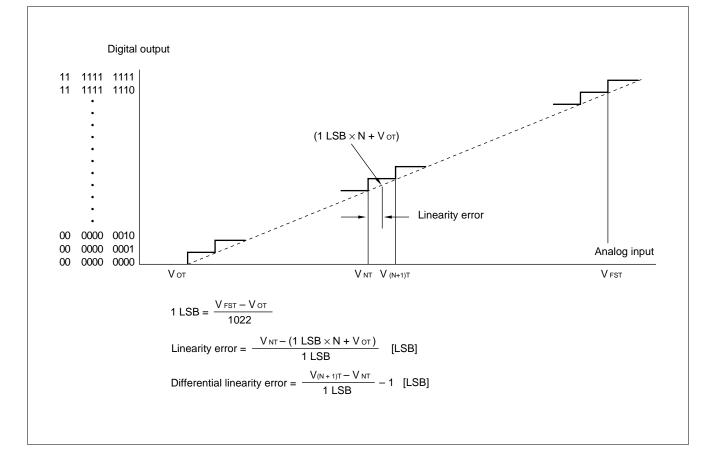

### 4. A/D Converter

The A/D converter converts the analog input voltage into a digital value. The features of this module are as follows:

- Conversion time: Minimum of 7 µs per channel (12 MHz machine clock)

- RC-type successive approximation conversion method with sample and hold circuit

- 8-bit/10-bit resolution

- · Analog input is selectable by software from among 4 channels

- A/D conversion mode selectable from the following three: One-shot conversion mode: Converts a specified channel once. Continuous conversion mode: Converts a specified channel repeatedly.

Stop conversion mode: Pauses after converting one channel and wait until the next activation (permits synchronization of start of conversion).

- Conversion mode: Single-conversion mode: Converts one channel (when the start and stop channels are the same).

Scan conversion mode: Converts several consecutive channels (when the start and stop channels are different).

- When A/D conversion is completed, an "A/D conversion complete" interrupt request can be issued to the CPU. Because generating this interrupt can be used to activate the I<sup>2</sup>OS and transfer the A/D conversion results to memory, this function is suitable for continuous processing.

- Activation sources can be selected from among software, an external trigger (falling edge), and timer (rising edge).

|                  | bit | 15   | 14  | 13       | 12   | 11   | 10       | 9    | 8        |                                   |

|------------------|-----|------|-----|----------|------|------|----------|------|----------|-----------------------------------|

| Address: 00002DH |     | BUSY | INT | INTE     | PAUS | STS1 | STS0     | STRT | Reserved |                                   |

| Address 00000    | bit | 7    | 6   | 5        | 4    | 3    | 2        | 1    | 0        | A/D converter control             |

| Address: 00002CH |     | MD1  | MD0 | Reserved | ANS1 | ANS0 | Reserved | ANE1 | ANE0     | status register<br>(ADCS1, ADCS0) |

| Address: 00002FH | bit | 15   | 14  | 13       | 12   | 11   | 10       | 9    | 8        | (ADC31, ADC30)                    |

| Address: 00002FH |     | 0    | 0   | 0        | 0    | 0    | 0        | D9   | D8       |                                   |

| Address: 00002EH | bit | 7    | 6   | 5        | 4    | 3    | 2        | 1    | 0        | A/D converter data registe        |

| Audiess. 00002EH |     | D7   | D6  | D5       | D4   | D3   | D2       | D1   | D0       | (ADCR1, ADCR0)                    |

#### (1) Register Configuration

(2) Block Diagram

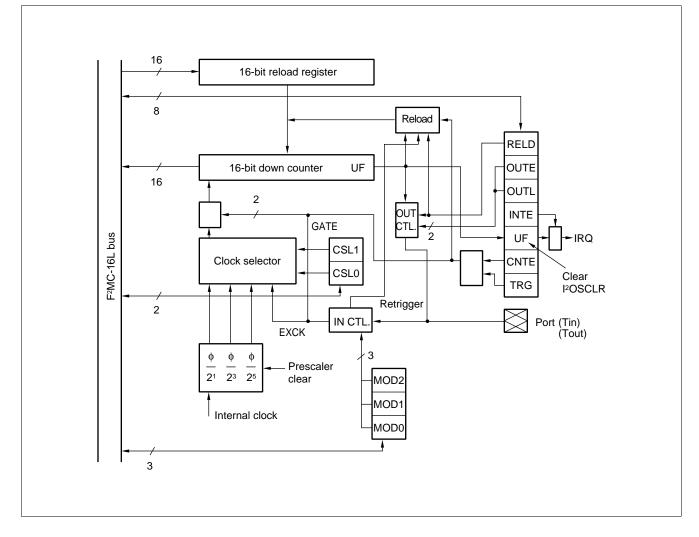

#### 5. 16-bit Timer (with Event Count Function)

The 16-bit timer consists of a 16-bit down counter, a 16-bit reload register, one input and output pin (TINx,TOTx), and a control register. Three internal clocks and an external clock can be selected for the input clock. When in reload mode, a toggled output waveform is output, while in one-shot mode a square wave indicating that the count is in progress is output pin (TOTx). The input pin (TINx) serves as an event input in event count mode, and can be used for trigger input or gate input in internal clock mode.

#### (1) Register Configuration

|                                            | bit              | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |   |                                                       |

|--------------------------------------------|------------------|------|------|------|------|------|------|------|------|---|-------------------------------------------------------|

| Address: 000040н<br>: 000046н<br>: 000050н |                  | MOD0 | OUTE | OUTL | RELD | INTE | UF   | CNTE | TRG  |   |                                                       |

| A                                          | bit              | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |   | Timer control status register                         |

| Address: 000041н<br>: 000047н<br>: 000051н |                  | _    | _    | —    | —    | CSL1 | CSL0 | MOD2 | MOD1 |   | 0 to 2<br>(TMCSR <sub>0</sub> to TMCSR <sub>2</sub> ) |

|                                            | bit <sup>2</sup> | 15   |      |      |      |      |      |      | 0    | ) |                                                       |

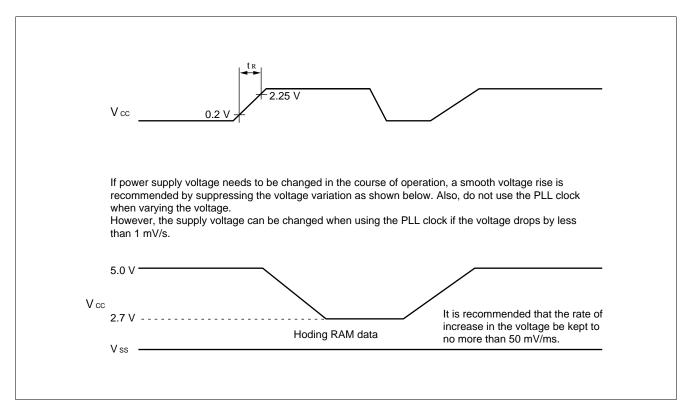

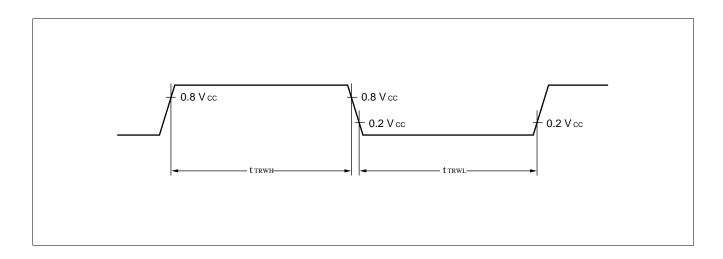

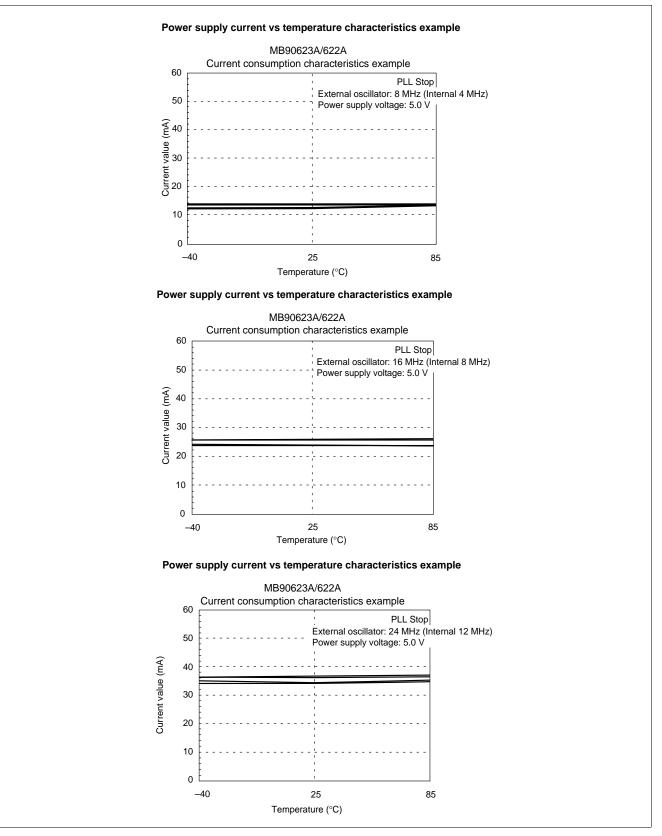

| Address: 000042н<br>: 000048н<br>: 000052н |                  |      |      |      |      |      |      |      |      |   | 16-bit timer register 0 to 2<br>(TMR₀ to TMR₂)        |