DS04-27405-1E

# ASSP For Power Supply Applications BIPOLAR

# Power Voltage Monitoring IC with Watchdog Timer

# MB3793-45

#### DESCRIPTION

The MB3793 is an integrated circuit to monitor power voltage; it incorporates a watchdog timer.

A reset signal is output when the power is cut or falls abruptly. When the power recovers normally after resetting, a power-on reset signal is output to microprocessor units (MPUs). An internal watchdog timer with two inputs for system operation diagnosis can provide a fall-safe function for various application systems.

There is also a mask option that can detect voltages of 4.9 to 2.4 V in 0.1-V steps.

The model number is MB3793-45 corresponding to the detected voltage. The model number and package code are as shown below.

| Model No. | Package code | Detection voltage |

|-----------|--------------|-------------------|

| MB3793-45 | 3793-7       | 4.5 V             |

#### **■ FEATURES**

- Precise detection of power voltage fall: ±2.5%

- · Detection voltage with hysteresis

- Low power dispersion:  $Icc = 31 \mu A$  (reference)

- Internal dual-input watchdog timer

- Watchdog-timer halt function (by inhibition pin)

- · Independently-set wacthdog and reset times

#### ■ PACKAGE

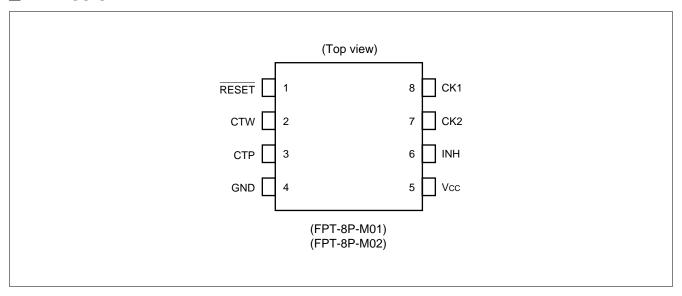

#### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| Pin no. | Symbol | Descriptions                            | Pin no. | Symbol | Descriptions       |

|---------|--------|-----------------------------------------|---------|--------|--------------------|

| 1       | RESET  | Outputs reset pin                       | 5       | Vcc    | Power supply pin   |

| 2       | CTW    | Watchdog timer monitor time setting pin | 6       | INH    | Inhibit pin        |

| 3       | СТР    | Power-on reset hold time setting pin    | 7       | CK2    | Inputs clock 2 pin |

| 4       | GND    | Ground pin                              | 8       | CK1    | Inputs clock 1 pin |

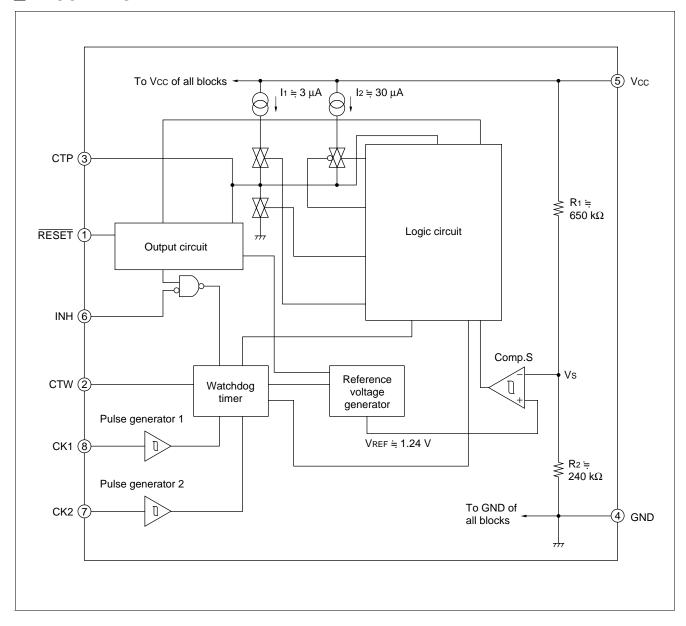

#### **■ BLOCK DIAGRAM**

#### **■ BLOCK DESCRIPTION**

#### 1. Comp. S

Comp. S is a comparator with hysteresis to compare the reference voltage with a voltage ( $V_s$ ) that is the result of dividing the power voltage ( $V_{cc}$ ) by resistors 1 and 2. When  $V_s$  falls below 1.24 V, a reset signal is output. This function enables the MB3793 to detect an abnormality within 1  $\mu$ s when the power is cut or falls abruptly.

#### 2. Output circuit

The output circuit contains a RESET output control comparator that compares the voltage at the CTP pin to the threshold voltage to release the RESET output if the CTP pin voltage exceeds the threshold value.

Since the reset (RESET) output buffer has CMOS organization, no pull-up resistor is needed.

#### 3. Pulse generator

The pulse generator generates pulses when the voltage at the CK1 and CK2 clock pins changes to High from Low level (positive-edge trigger) and exceeds the threshold voltage; it sends the clock signal to the watchdog timer.

#### 4. Watchdog timer

The watchdog timer can monitor two clock pulses. Short-circuit the CK1 and CK2 clock pins to monitor a single clock pulse.

#### 5. Inhibition pin

The inhibition (INH) pin forces the watchdog timer on/off. When this pin is High level, the watchdog timer is stopped.

#### 6. Logic circuit

The logic circuit contains flip-flops.

Flip-flop RSFF1 controls the charging and discharging of the power-on reset time setting capacitor (C<sub>TP</sub>).

Flip-flop RSFF2 turns on/off the circuit that accelerates charging of the power-on reset time setting capacitor (C<sub>TP</sub>) at a reset. The RSFF2 operates only at a reset; it does not operate at a power-on reset when the power is turned on.

#### ■ ABSOLUTE MAXIMUM RATINGS

$(Ta = +25^{\circ}C)$

| Parameter             |       | Symbol Conditions          |            | Rating      |      | Unit  |

|-----------------------|-------|----------------------------|------------|-------------|------|-------|

|                       |       |                            |            | Min.        | Max. | Offic |

| Power supply voltage* |       | Vcc                        | _          | -0.3        | +7   | V     |

|                       | CK1   | Vcк1                       | _          |             |      |       |

| Input voltage         | CK2   | Vск2                       | _          | -0.3        | +7   | V     |

|                       | INH   | linh                       | _          |             |      |       |

| Reset output current  | RESET | <b>І</b> оь<br><b>І</b> он | _          | -10         | +10  | mA    |

| Allowable loss        |       | Po                         | Ta ≤ +85°C | _           | 200  | mW    |

| Storage temperature   |       | Tstg                       | _          | <b>–</b> 55 | +125 | °C    |

<sup>\*:</sup> The power supply voltage is based on the ground voltage (0 V).

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                                       | Symbol     | Symbol Conditions |            | Unit |      |     |

|-------------------------------------------------|------------|-------------------|------------|------|------|-----|

| Farameter                                       | Symbol     |                   | Min.       | Тур. | Max. | Onn |

| Power supply voltage                            | Vcc        | _                 | 1.2        | _    | 6.0  | V   |

| Reset (RESET) output current                    | Iоь<br>Іон | _                 | <b>–</b> 5 | _    | +5   | mA  |

| Power-on reset hold time setting capacity       | Стр        | _                 | 0.001      | _    | 10   | μF  |

| Watchdog-timer monitoring time setting capacity | Стw        | _                 | 0.001      | _    | 1    | μF  |

| Operating temperature                           | Та         | _                 | -40        | _    | +85  | °C  |

<sup>\*:</sup> The watchdog timer monitor time range depends on the rating of the setting capacitor.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

#### **■ ELECTRICAL CHARACTERISTICS**

#### 1. DC Characteristics

$(Vcc = +5 V, Ta = +25^{\circ}C)$

| Parameter                               | Symbol                               |                 | Conditions                                   | Value   |      |         | Unit  |

|-----------------------------------------|--------------------------------------|-----------------|----------------------------------------------|---------|------|---------|-------|

| raiailletei                             | Syllibol                             | Conditions      |                                              | Min.    | Тур. | Max.    | Oiiit |

| Power supply current                    | Icc1                                 | After exit from | om reset                                     | _       | 31   | 45      | μΑ    |

|                                         | VsL                                  | Vcc falling     | Ta = +25°C                                   | 4.40    | 4.50 | 4.60    | V     |

| Detection voltage                       | V SL                                 | vcc raining     | $Ta = -40^{\circ}C \text{ to } +85^{\circ}C$ | (4.35)* | 4.50 | (4.65)* |       |

| Detection voltage                       | Vsh                                  | Vcc rising      | Ta = +25°C                                   | 4.50    | 4.60 | 4.70    | V     |

|                                         | VSH                                  | vcc rising      | $Ta = -40^{\circ}C \text{ to } +85^{\circ}C$ | (4.45)* | 4.60 | (4.75)* |       |

| Detection voltage hysteresis difference | Vshys                                | VsH - VsL       |                                              | 50      | 100  | 150     | mV    |

|                                         | Vсін                                 | CK rising       |                                              | (1.4)*  | 1.9  | 2.5     | V     |

| Clock-input threshold voltage           | VcIL                                 | CK falling      |                                              | 8.0     | 1.3  | (1.8)*  | V     |

| Clock-input hysteresis                  | Vchts                                | _               |                                              | (0.4)*  | 0.6  | (0.8)*  | V     |

| Inhibition-input voltage                | VIIH                                 | _               |                                              | 3.5     | _    | _       | V     |

| I III II DILIOII-III Put Voltage        | VIIL                                 | _               |                                              | _       | 0    | 0.8     | v     |

| Input current                           | Іін                                  | Vск = 5 V       |                                              | _       | 0    | 1.0     | μΑ    |

| (CK1, CK2, INH)                         | CK1, CK2, INH) $I_{IL} V_{CK} = 0 V$ |                 |                                              | -1.0    | 0    | _       | μΑ    |

| Poset output veltege                    | Vон                                  | IRESET = -5 mA  |                                              | 4.5     | 4.75 | _       | V     |

| Reset output voltage                    | Vol                                  | IRESET = +5 mA  |                                              | _       | 0.12 | 0.4     | V     |

| Reset-output minimum power voltage      | Vccl                                 | IRESET = +50    | μΑ                                           | _       | 0.8  | 1.2     | V     |

<sup>\*:</sup> The values enclosed in parentheses () are setting assurance values.

#### 2. AC Characteristics

$(Vcc = +5 V, Ta = +25^{\circ}C)$

| Parameter                       |         | Symbol Conditions |                                                 | Value |      |      | Unit |

|---------------------------------|---------|-------------------|-------------------------------------------------|-------|------|------|------|

|                                 |         | Symbol            | Conditions                                      | Min.  | Тур. | Max. | Unit |

| Power-on reset hold time        |         | <b>t</b> PR       | C <sub>TP</sub> = 0.1 μF                        | 80    | 130  | 180  | ms   |

| Watchdog timer reset time       |         | <b>t</b> wD       | $C_{TW} = 0.01 \ \mu F,$ $C_{TP} = 0.1 \ \mu F$ | 7.5   | 15   | 22.5 | ms   |

| Watchdog timer reset time       |         | twr               | C <sub>TP</sub> = 0.1 μF                        | 5     | 10   | 15   | ms   |

| Clock input pulse width         |         | <b>t</b> ckw      | _                                               | 500   | _    | _    | ns   |

| Clock input pulse cycle         |         | <b>t</b> cĸτ      | _                                               | 20    | _    | _    | μs   |

| Reset (RESET) output transition | Rising  | tr*               | C∟ = 50 pF                                      | _     | _    | 500  | ns   |

| time*                           | Falling | t <sub>f</sub> *  | C∟ = 50 pF                                      | _     | _    | 500  | ns   |

<sup>\*:</sup> The voltage range is 10% to 90% at testing the reset output transition time.

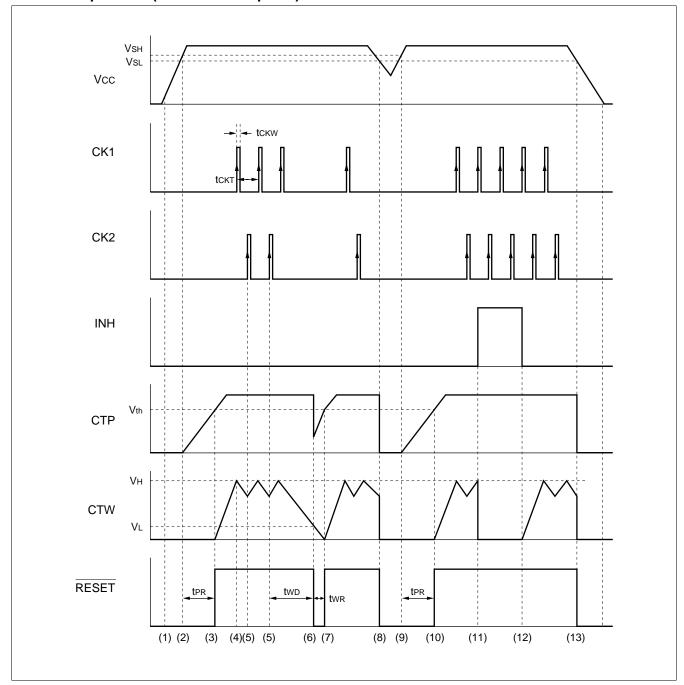

### **■ DIAGRAM**

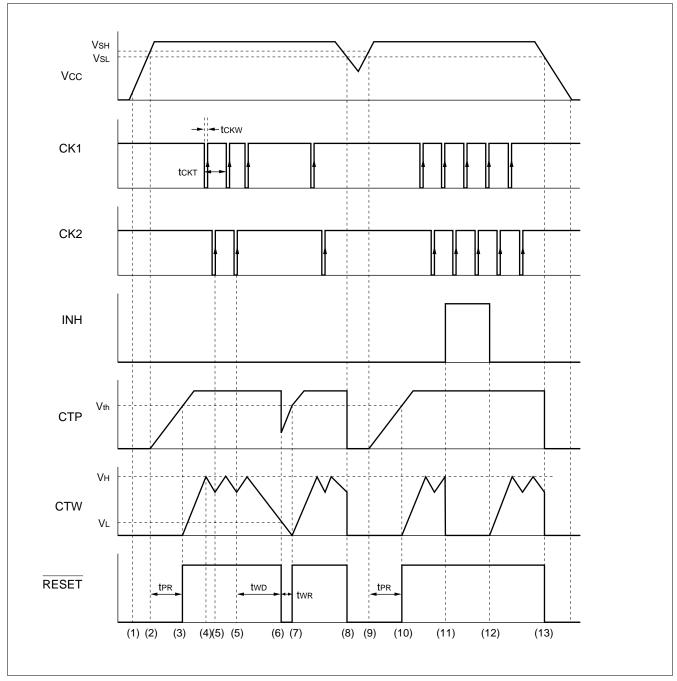

### 1. Basic operation (Positive clock pulse)

## 2. Basic operation (Negative clock pulse)

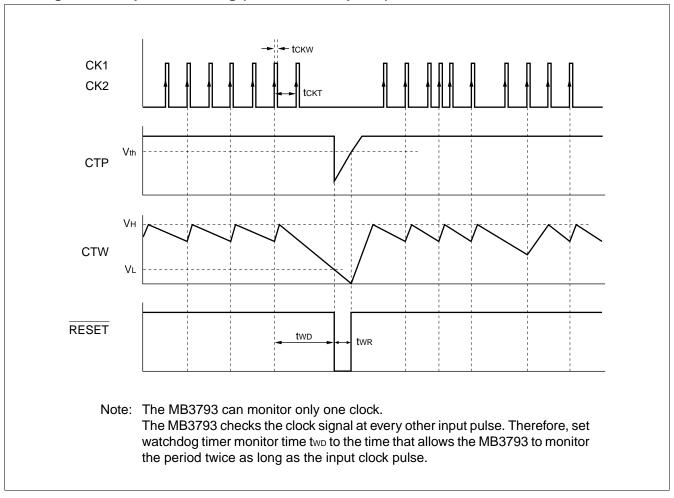

#### 3. Single-clock input monitoring (Positive clock pulse)

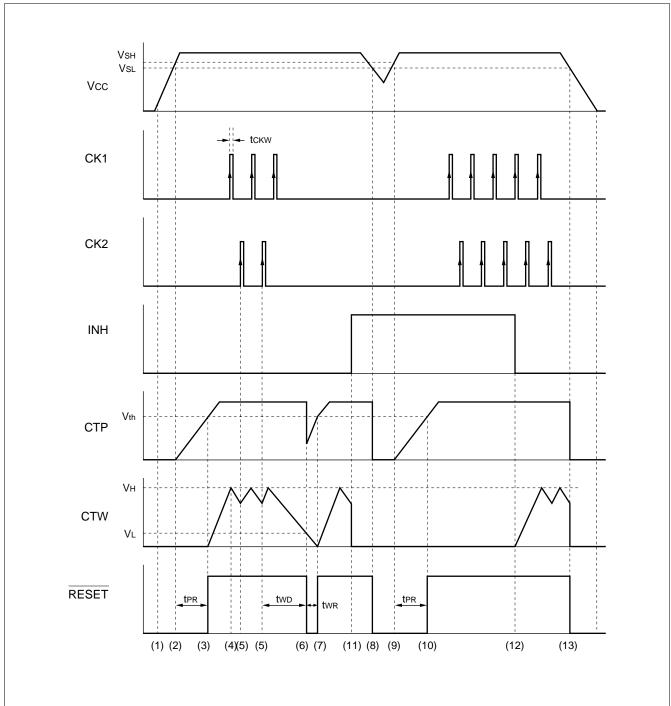

## 4. Inhibition operation (Positive clock pulse)

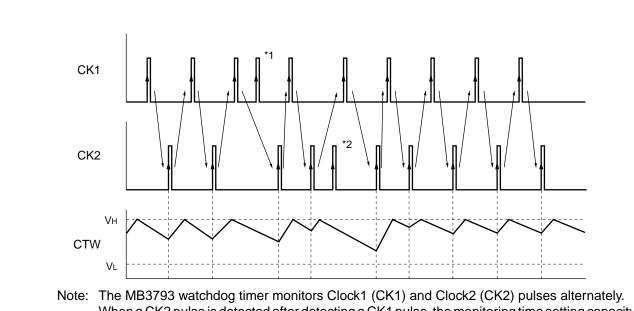

#### Clock pulse input supplementation (Positive clock pulse)

When a CK2 pulse is detected after detecting a CK1 pulse, the monitoring time setting capacity (C<sub>Tw</sub>) switches to charging from discharging.

When two consecutive pulses occur on one side of this alternation before switching, the second pulse is ignored.

In the above figure, pulse \*1 and \*2 are ignored.

#### **■** OPERATION SEQUENCE

#### 1. Positive clock pulse input

See "1. Basic operation (positive clock pulse)" under "■ DIAGRAM".

#### 2. Negative clock pulse input

See "2. Basic operation (negative clock pulse)" under "■ DIAGRAM".

The MB3793 operates in the same way whether it inputs positive or negative pulses.

#### 3. Clock monitoring

To use the MB3793 while monitoring only one clock, connect clock pins CK1 and CK2.

Although the MB3793 operates basically in the same way as when monitoring two clocks, it monitors the clock signal at every other input pulse.

See "3. Single-clock input monitoring (positive clock pulse)" under "■ DIAGRAM".

#### 4. Description of Operations

The numbers given to the following items correspond to numbers (1) to (13) used in "■ DIAGRAM".

- (1) The MB3793 outputs a reset signal when the supply voltage (Vcc) reaches about 0.8 V (Vccl)

- (2) If Vcc reaches or exceeds the rise-time detected voltage VsH, the MB3793 starts charging the power-on reset hold time setting capacitor C<sub>TP</sub>. At this time, the output remains in a reset state. The V<sub>SH</sub> value is about 4.60 V.

- (3) When C<sub>TP</sub> has been charged for a certain period of time T<sub>PR</sub> (until the CTP pin voltage exceeds the threshold voltage (V<sub>th</sub>) after the start of charging), the MB3793 cancels the reset (setting the RESET pin to "H" level from "L" level).

The  $V_{th}$  value is about 3.6 V with  $V_{CC} = 5.0 \text{ V}$

The power-on reset hold timer monitor time tpr is set with the following equation:

$t_{PR}$  (ms)  $= A \times C_{TP}$  ( $\mu F$ )

The value of A is about 1300 with Vcc = 5.0 V. The MB3793 also starts charging the watchdog timer monitor time setting capacitor ( $C_{Tw}$ ).

- (4) When the voltage at the watchdog timer monitor time setting pin  $C_{TW}$  reaches the "H" level threshold voltage  $V_H$ , the  $C_{TW}$  switches from the charge state to the discharge state.

- The value of V<sub>H</sub> is always about 1.24 V regardless of the detected voltage.

- (5) If the CK2 pin inputs a clock pulse (positive edge trigger) when the C<sub>TW</sub> is being discharged in the CK1-CK2 order or simultaneously, the C<sub>TW</sub> switches from the discharge state to the charge state.

The MB3793 repeats operations (4) and (5) as long as the CK1/CK2 pin inputs clock pulses with the system logic circuit operating normally.

- (6) If no clock pulse is fed to the CK1 or CK2 pin within the watchdog timer monitor time two due to some problem with the system logic circuit, the CTW pin is set to the "L" level threshold voltage V<sub>L</sub> or less and the MB3793 outputs a reset signal (setting the RESET pin to "L" level from "H" level). The value of V<sub>L</sub> is always about 0.24 V regardless of the detected voltage.

The watchdog timer monitor time two is set with the following equation:

two (ms) = B  $\times$  C<sub>TW</sub> ( $\mu$ F)

The value of B is hardly affected by the supply voltage; it is about 1500 with Vcc = 5.0 V.

(7) When a certain period of time twn has passed (until the CTP pin voltage reaches or exceeds Vth again after recharging the C<sub>TP</sub>), the MB3793 cancels the reset signal and starts operating the watchdog timer. The watchdog timer monitor reset time twn is set with the following equation:

twr (ms) = D x C<sub>TP</sub> ( $\mu$ F)

The value of D is about 100 with Vcc = 5.0 V.

The MB3793 repeats operations (4) and (5) as long as the CK1/CK2 pin inputs clock pulses. If no clock pulse is input, the MB3793 repeats operations (6) and (7).

- (8) If Vcc is lowered to the fall-time detected voltage (VsL) or less, the CTP pin voltage decreases and the MB3793 outputs a reset signal (setting the RESET pin to "L" level from "H" level). The value of VsL is 4.5 V

- (9) When Vcc reaches or exceeds VsH again, the MB3793 starts charging the CTP.

- (10) When the CTP pin voltage reaches or exceeds V<sub>th</sub>, the MB3793 cancels the reset and restarts operating the watchdog timer. It repeats operations (4) and (5) as long as the CK1/CK2 pin inputs clock pulses.

- (11) Making the inhibit pin active (setting the INH pin to "H" from "L") forces the watchdog timer to stop operation. This stops only the watchdog timer, leaving the MB3793 monitoring Vcc (operations (8) to (10)). The watchdog timer remains inactive unless the inhibit input is canceled.

- (12) Canceling the inhibit input (setting the INH pin to "L" from "H") restarts the watchdog timer.

- (13) The reset signal is output when the power supply is turned off to set Vcc to VsL or less.

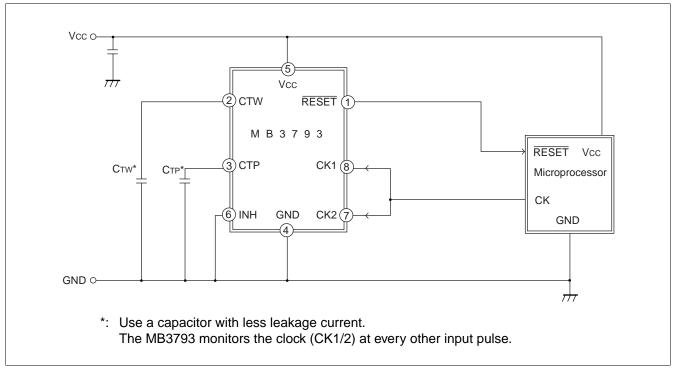

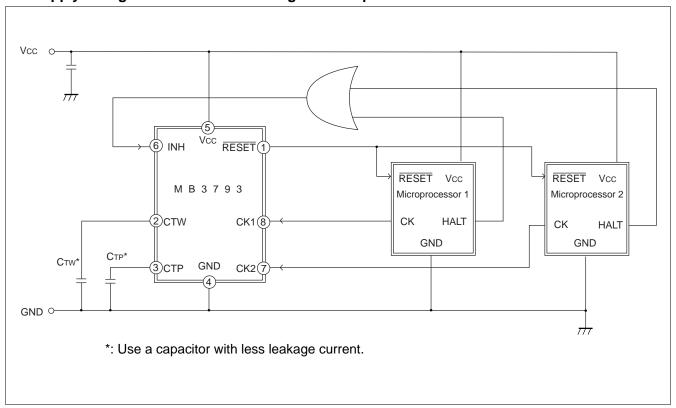

#### **■ APPLICATION EXAMPLE**

#### 1. Supply voltage monitor and watchdog timer (1-clock monitor)

#### 2. Supply voltage monitor and watchdog timer stop

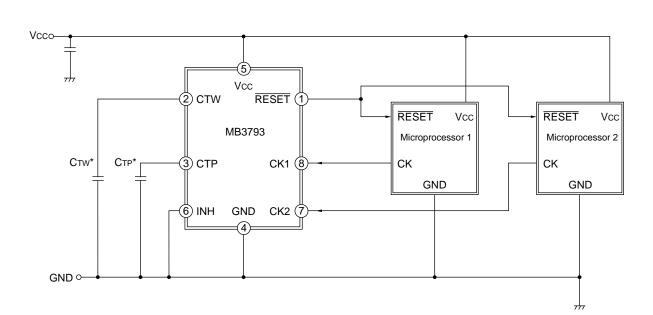

#### **■ TYPICAL APPLICATION**

<sup>\*:</sup> Use a capacitor with less leakage current.

#### 1. Equation of time-setting capacitances (CTP and CTW) and set time

$$\begin{split} \text{tpr} & \text{[ms]} \ \buildrel = \ A \times C_{\text{TP}} \, [\mu F] \\ \text{two} & \text{[ms]} \ \buildrel = \ B \times C_{\text{TW}} \, [\mu F] + C \times C_{\text{TP}} \, [\mu F] \\ & \text{However, when} \ \buildrel = \ C_{\text{TW}} \leq \text{about 10, two [ms]} \ \buildrel = \ B \times C_{\text{TW}} \, [\mu F] \\ \text{twr} & \text{[ms]} \ \buildrel = \ D \times C_{\text{TP}} \, [\mu F] \end{split}$$

Values of A, B, C, and D

| Α    | В    | С | D   | Remark      |

|------|------|---|-----|-------------|

| 1300 | 1500 | 3 | 100 | Vcc = 5.0 V |

#### 2. (Example) when C<sub>TP</sub> = 0.1 $\mu$ F and C<sub>TW</sub> = 0.01 $\mu$ F

|              | •           |       |

|--------------|-------------|-------|

| .,           | <b>t</b> pr | ≒ 130 |

| time<br>(ms) | <b>t</b> wD | ≒ 15  |

| (5)          | <b>t</b> wr | ≒ 10  |

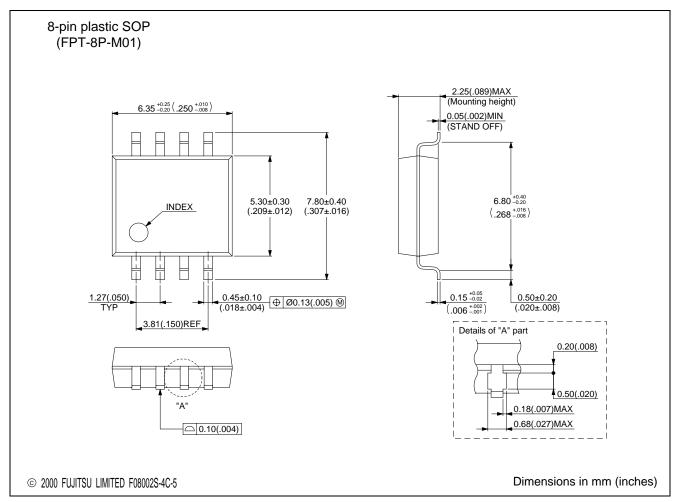

### **■** ORDERING INFORMATION

| Part number  | Package                           | Remarks |

|--------------|-----------------------------------|---------|

| MB3793-45PF  | 8-pin Plastic SOP<br>(FPT-8P-M01) |         |

| MB3793-45PNF | 8-pin Plastic SOL<br>(FPT-8P-M02) |         |

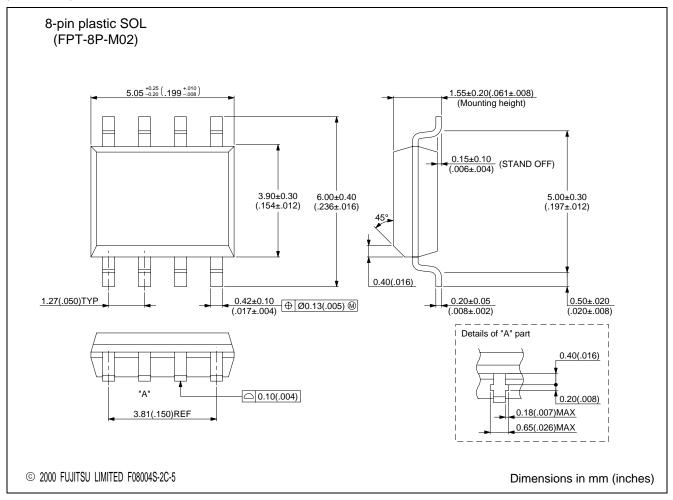

#### **■ PACKAGE DIMENSIONS**

(Continued)

#### (Continued)

# **FUJITSU LIMITED**

For further information please contact:

#### **Japan**

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices KAWASAKI PLANT, 4-1-1, Kamikodanaka, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8588, Japan

Tel: +81-44-754-3763 Fax: +81-44-754-3329 http://www.fujitsu.co.jp/

#### North and South America

FUJITSU MICROELECTRONICS, INC. 3545 North First Street, San Jose, CA 95134-1804, U.S.A.

Tel: +1-408-922-9000 Fax: +1-408-922-9179

Customer Response Center Mon. - Fri.: 7 am - 5 pm (PST)

Tel: +1-800-866-8608 Fax: +1-408-922-9179

http://www.fujitsumicro.com/

#### **Europe**

FUJITSU MICROELECTRONICS EUROPE GmbH Am Siebenstein 6-10,

D-63303 Dreieich-Buchschlag,

Germany

Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://www.fujitsu-fme.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LTD. #05-08, 151 Lorong Chuan, New Tech Park, Singapore 556741

Singapore 556741 Tel: +65-281-0770 Fax: +65-281-0220

http://www.fmap.com.sg/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 1702 KOSMO TOWER, 1002 Daechi-Dong, Kangnam-Gu, Seoul 135-280

Korea

Tel: +82-2-3484-7100 Fax: +82-2-3484-7111

F0007

© FUJITSU LIMITED Printed in Japan

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

The contents of this document may not be reproduced or copied without the permission of FUJITSU LIMITED.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipments, industrial, communications, and measurement equipments, personal or household devices, etc.).

#### CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.