DS04-13506-1E

# LINEAR IC

# R-2R TYPE 8-BIT D/A CONVERTER WITH OPERATIONAL AMPLIFIER OUTPUT BUFFERS

# **MB88347**

### ■ DESCRIPTION

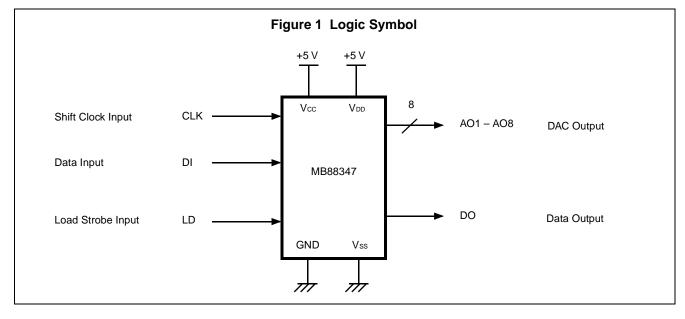

The Fujitsu MB88347 is an R-2R type 8-bit resolution digital-to-analog converter (DAC), designed for interface with a wide range of general 4-bit and 8-bit microcontrollers including Fujitsu's MB88200 family, MB8850 family, and MB88500 family 4-bit single-chip microcontrollers.

The MB88347 has an 8-bit  $\times$  8-channel D/A converter with operational amplifier output buffers. Digital data are input serially by individual channel units. The loaded digital data are converted into analog DC voltages by the D/A converter in 100  $\mu$ s settling time. Also, the MB88347 has operational amplifier output buffers. These operational amplifier output buffers are connected to each channel of the D/A converter, and provide high current drive capability. The MB88347 is suitable for electronic volumes and replacement for potentiometers for adjustment, in addition to normal D/A converter applications.

### **■ FEATURES**

- Conversion method: R-2R resistor ladder

- 8-bit × 8-channel D/A converter with operational amplifier output buffers

- Max. 2.5 MHz Serial data input

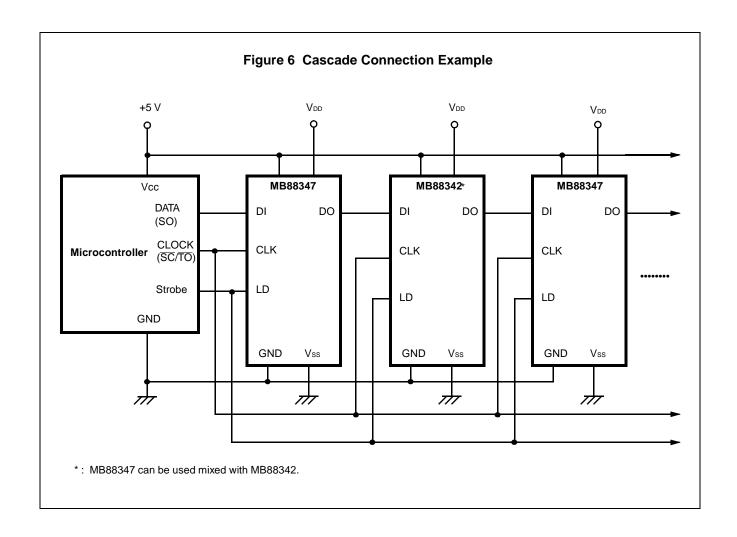

- Serial data output for cascade connection

- Max. 100 µs DAC output settling time

- Max. +1.0/-1.0 mA analog output sink/source current

- Two separate power supply/ground lines for MCU interface block/operational amplifier output buffer block and D/A converter block

(Continued)

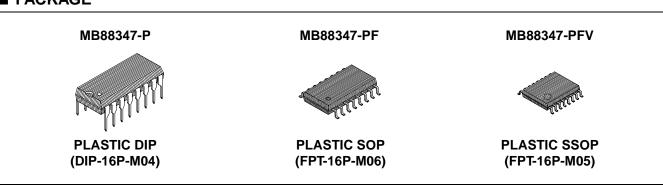

#### ■ PACKAGE

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

### (Continued)

- Pin compatible with MB88342

- Single +5 V power supply

- Wide operating temperature range: -20°C to +85°C

- Silicon-gate CMOS process

- Three package options :

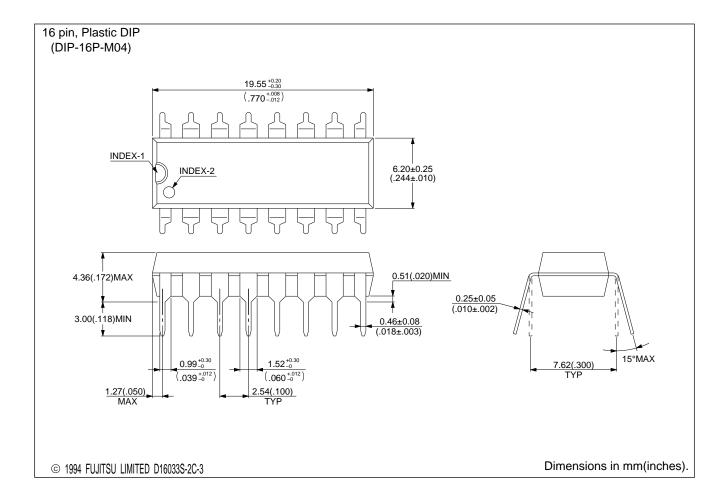

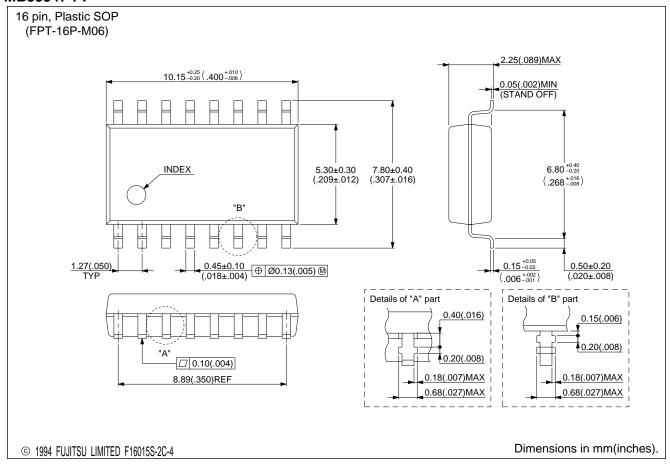

- 16-pin plastic DIP (Suffix : -P), 16-pin plastic SOP (Suffix : -PF), 16-pin plastic SSOP(Suffix : -PFV)

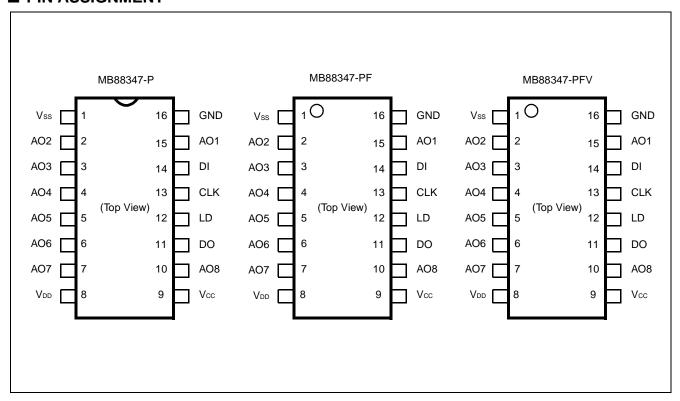

### **■ PIN ASSIGNMENT**

## **■ BLOCK DIAGRAM**

# **■ PIN DESCRIPTION**

PIN ASSIGNMENT and Table 1 show the pin assignment and pin description of the MB88347.

**Table 1 Pin Description**

| Symbol                                               | Pin No.                          | Туре | Name & Function                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------|----------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Sup                                            | ply                              | 1    |                                                                                                                                                                                                                                                                                                                                      |

| Vcc                                                  | 9                                | _    | +5 V DC power supply pin for the digital block (MCU interface) and operational amplifier output buffers.                                                                                                                                                                                                                             |

| GND                                                  | 16                               | _    | Ground pin for the digital block (MCU interface) and operational amplifier output buffers.                                                                                                                                                                                                                                           |

| V <sub>DD</sub>                                      | 8                                | _    | DC power supply pin for the analog block (D/A converter) except operational amplifier output buffers.                                                                                                                                                                                                                                |

| Vss                                                  | 1                                | _    | Ground pin for the analog block (D/A converter) except operational amplifier output buffers.                                                                                                                                                                                                                                         |

| Control Inp                                          | out                              |      |                                                                                                                                                                                                                                                                                                                                      |

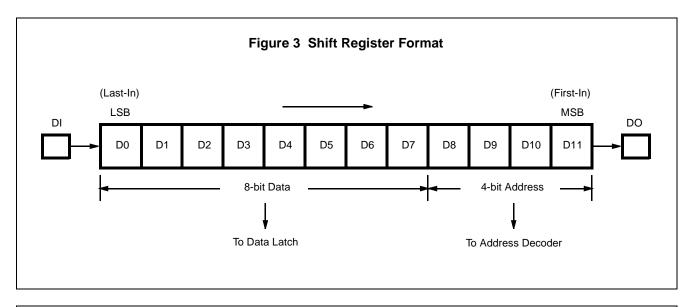

| CLK                                                  | 13                               | I    | Shift clock input to the internal 12-bit shift register: At the rising edge of CLK data on the DI pin is shifted into the LSB of the shift register and contents of the shift register are shifted right (to the MSB).                                                                                                               |

| LD                                                   | 12                               | I    | Load strobe input for a 12-bit address/data: A high level on the LD pin latches a 4-bit address (upper 4 bits: D11 to D8) of the internal 12-bit shift register into the internal address decoder, and writes 8-bit data (lower 8 bits: D7 to D0) of the shift register into an internal data latch selected by the latched address. |

| Data Input                                           | /Output                          |      |                                                                                                                                                                                                                                                                                                                                      |

| DI                                                   | 14                               | I    | Serial address/data input to the internal 12-bit shift register: The address/data format is that upper 4 bits (D11 to D8) indicate an address and lower 8 bits (D7 to D0) indicate data. The D11 (MSB) is the first-in bit and D0 (LSB) is the last-in bit.                                                                          |

| DO                                                   | 11                               | 0    | Serial address/data output from the internal 12-bit shift register: This is an output pin of the MSB bit data of the 12-bit shift register. This pin allows a cascade connection of the device.                                                                                                                                      |

| DAC Outpu                                            | ut                               |      |                                                                                                                                                                                                                                                                                                                                      |

| AO1<br>AO2<br>AO3<br>AO4<br>AO5<br>AO6<br>AO7<br>AO8 | 15<br>2<br>3<br>4<br>5<br>6<br>7 | 0    | 8-bit resolution D/A converter outputs : 8 channels (AO1 to AO8)  Each output channel has an operational amplifier output buffer for analog output data.                                                                                                                                                                             |

### **■ FUNCTIONAL DESCRIPTION**

### **OVERVIEW**

The MB88347 is a R-2R resistor ladder type, 8-bit resolution digital-to-analog converter (DAC) device. The MB88347 has 8 channels of D/A converters with operational amplifier output buffers. 8-bit digital data are loaded into internal data latches by individual DAC channel units. The loaded digital data are converted into analog DC voltages through the internal D/A converter in max. 100  $\mu$ s settling time. And the analog DC voltages source/sink the output current through the operational amplifier output buffers. For cascade connection, a serial data output is provided.

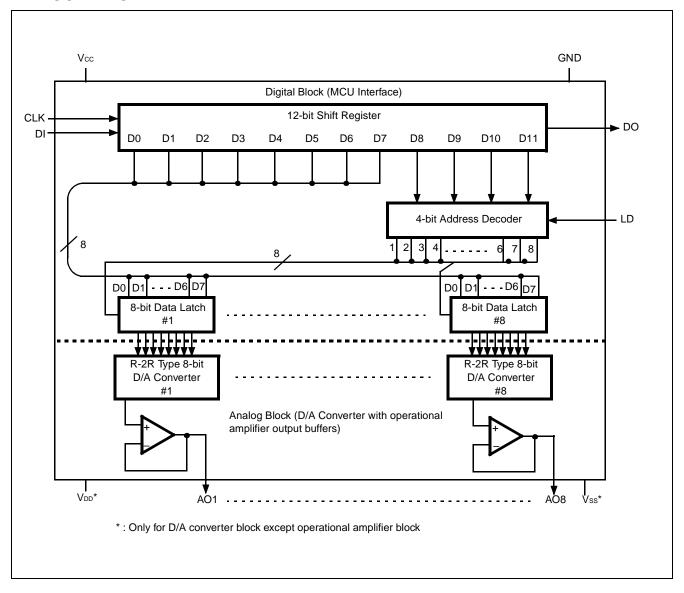

### **DEVICE CONFIGURATION**

As illustrated in BLOCK DIAGRAM, the MB88347 device is composed by the digital block (MCU interface) and analog block (D/A converter with operational amplifier output buffers). The digital block consists of a 12-bit shift register, a 4-bit address decoder, and 8-channels of 8-bit data latches. The analog block includes 8-channels of 8-bit D/A converters with operational amplifier output buffers connecting to the data latches. For electrically stable operation the power supply and ground lines are separate between the digital block (MCU interface) and operational amplifier output buffers, and analog block except operational amplifier output buffers.

### **DEVICE OPERATION**

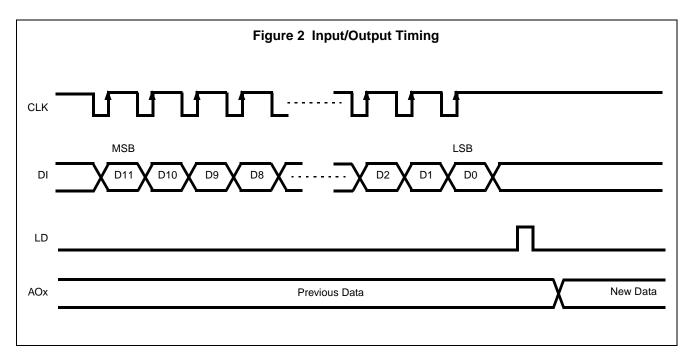

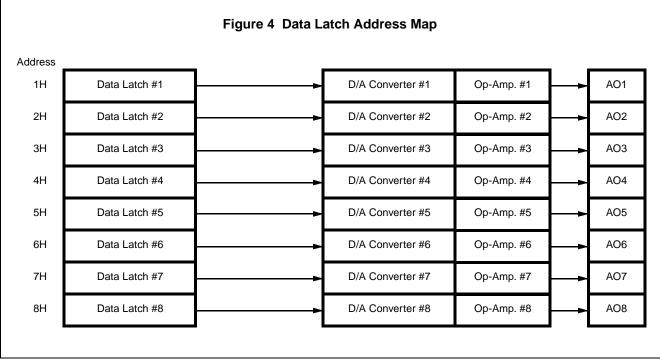

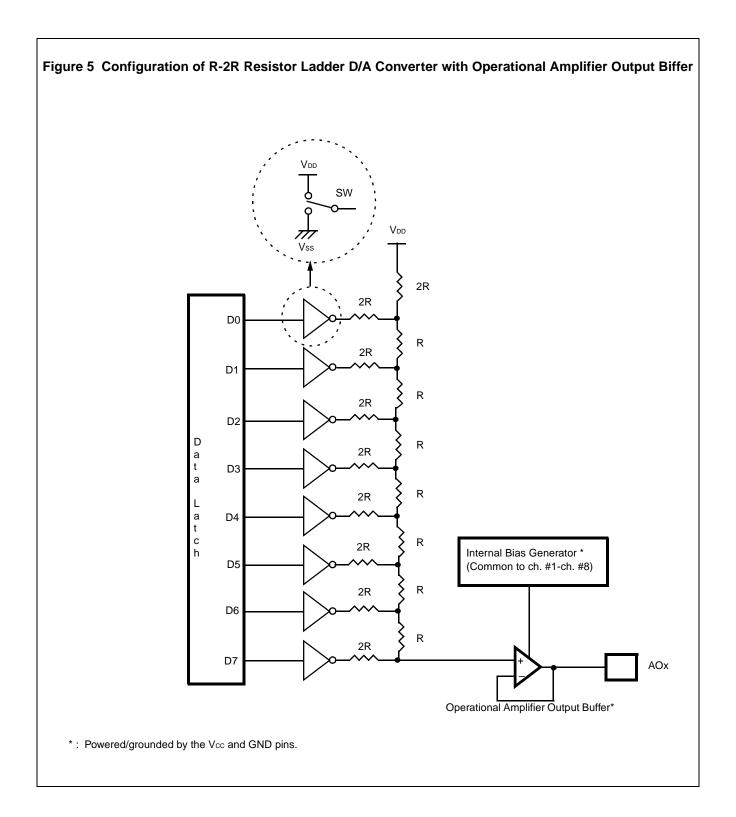

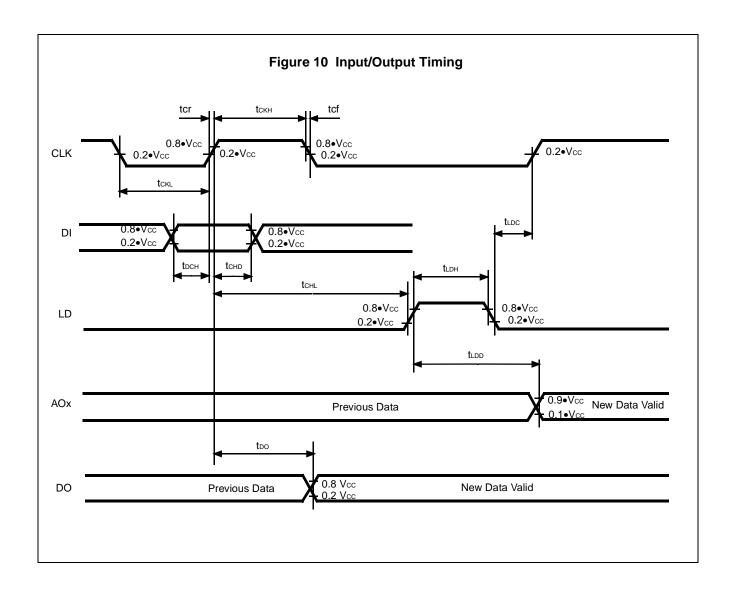

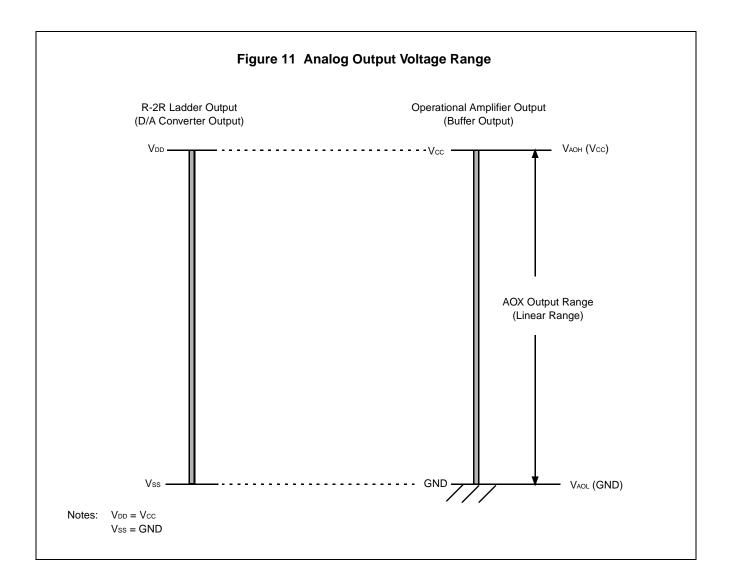

Figure 2 shows the input/output timing. A 12-bit address/data is serially input into the shift register through the DI pin synchronously with the rising edge of CLK. The format of the shift register is shown in Figure 3. The lower 8 bits (D7 to D0) are data bits to be converted, and the upper 4 bits are address bits (D11 to D8) to select a data latch to be written. A high level on the LD pin loads the address decoder with the 4-bit address to select a data latch, and writes the 8-bit data into a selected data latch. Figure 4 shows the data latch address map, and Table 2, address decoding. 8-bit data written into individual data latches are converted into analog DC voltages, dividing the supply voltage |VDD-VSS| through R-2R resistor ladders of D/A converters. The operational amplifier output buffers at individual D/A converter outputs can source up to 1.0 mA of the output current. Figure 5 shows a configuration of the R-2R resistor ladder D/A converter with operational amplifier, and Table 3 analog DC voltages corresponding to each digital data.

Table 2 Address Decoding

|    | Ado | iress | Data Latch Selected |               |

|----|-----|-------|---------------------|---------------|

| D8 | D9  | D10   | D11                 | MB88347       |

| 0  | 0   | 0     | 0                   | Deselected    |

| 0  | 0   | 0     | 1                   | Data Latch #1 |

| 0  | 0   | 1     | 0                   | Data Latch #2 |

| 0  | 0   | 1     | 1                   | Data Latch #3 |

| 0  | 1   | 0     | 0                   | Data Latch #4 |

| 0  | 1   | 0     | 1                   | Data Latch #5 |

| 0  | 1   | 1     | 0                   | Data Latch #6 |

| 0  | 1   | 1     | 1                   | Data Latch #7 |

| 1  | 0   | 0     | 0                   | Data Latch #8 |

| 1  | 0   | 0     | 1                   | Deselected    |

| 1  | 0   | 1     | 0                   | Deselected    |

| 1  | 0   | 1     | 1                   | Deselected    |

| 1  | 1   | 0     | 0                   | Deselected    |

| 1  | 1   | 0     | 1                   | Deselected    |

| 1  | 1   | 1     | 0                   | Deselected    |

| 1  | 1   | 1     | 1                   | Deselected    |

**Table 3 Data Conversion**

|    |    |    | DAC Output Level |    |    |    |    |                                                                  |

|----|----|----|------------------|----|----|----|----|------------------------------------------------------------------|

| D7 | D6 | D5 | D4               | D3 | D2 | D1 | D0 | AOx                                                              |

| 0  | 0  | 0  | 0                | 0  | 0  | 0  | 0  | ≈ Vss                                                            |

| 0  | 0  | 0  | 0                | 0  | 0  | 0  | 1  | ≈ (V <sub>DD</sub> – V <sub>SS</sub> ) × 1/255 + V <sub>SS</sub> |

| 0  | 0  | 0  | 0                | 0  | 0  | 1  | 0  | ≈ (V <sub>DD</sub> − V <sub>SS</sub> ) × 2/255 + V <sub>SS</sub> |

| 0  | 0  | 0  | 0                | 0  | 0  | 1  | 1  | ≈ (V <sub>DD</sub> – V <sub>SS</sub> ) × 3/255 + V <sub>SS</sub> |

| :  | :  | •  | •                | •  | •  | •  | :  | :                                                                |

| 1  | 1  | 1  | 1                | 1  | 1  | 1  | 0  | ≈ (V <sub>DD</sub> –Vss) × 254/255 + Vss                         |

| 1  | 1  | 1  | 1                | 1  | 1  | 1  | 1  | ≈ V <sub>DD</sub>                                                |

## **■ APPLICATION DESCRIPTION**

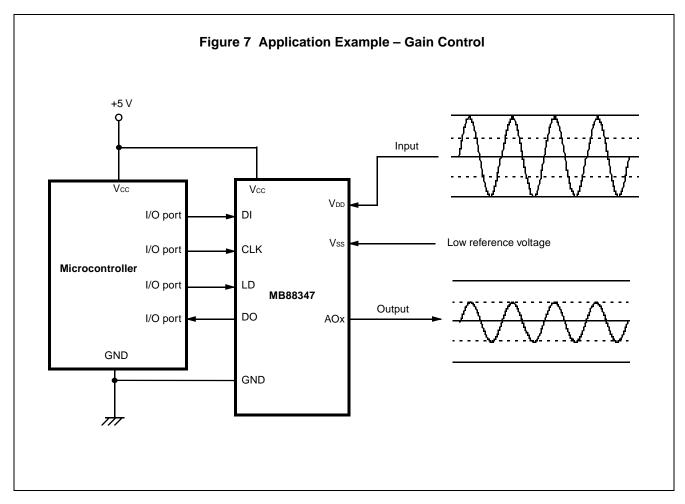

The MB88347 is suitable for electronic volumes and replacement for adjustment potentiometers, in addition to normal D/A converter applications. Figure 7 illustrates an application example for a gain control.

## **■ ELECTRICAL CHARACTERISTICS**

# **ABSOLUTE MAXIMUM RATINGS (See NOTE)**

| Parameter                        | Symbol          |             |         |           |      | Condition                                     |  |

|----------------------------------|-----------------|-------------|---------|-----------|------|-----------------------------------------------|--|

| Farameter                        | Syllibol        | Min         | Min Typ |           | Unit | Condition                                     |  |

| O and Malkana                    | Vcc             | -0.3        | _       | +7.0      | V    | Ta = +25°C                                    |  |

| Supply Voltage                   | V <sub>DD</sub> | -0.3        | _       | +7.0      | V    | $GND = 0 V$ $V_{DD} \le V_{CC},$              |  |

| Input Voltage                    | Vin             | -0.3        | _       | Vcc + 0.3 | V    | Ta = 25°C                                     |  |

| Output Voltage                   | Vоит            | -0.3        | _       | Vcc + 0.3 | V    | GND = 0 V<br>Should not exceed<br>Vcc + 0.3 V |  |

| Power Dissipation                | Po              | _           | _       | 250       | mW   |                                               |  |

| Operating Ambient<br>Temperature | Та              | -20         | _       | +85       | °C   |                                               |  |

| Storage Temperature              | Тѕтс            | <b>–</b> 55 | _       | +150      | °C   |                                               |  |

**NOTE:** Permanent device damage may occur if the above ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                                  | Symbol          |         |     |           |      | Condition                                       |

|------------------------------------------------------------|-----------------|---------|-----|-----------|------|-------------------------------------------------|

| Parameter                                                  | Syllibol        | Min Typ |     | Max       | Unit | Condition                                       |

| Supply Voltage                                             | Vcc             | 4.5     | 5.0 | 5.5       | V    |                                                 |

| (for MCU Interface/<br>OpAmp. Block)                       | GND             | _       | 0   | _         | V    | $V_{CC} \ge V_{DD}$ , $V_{DD} - V_{SS} \ge 2.0$ |

| Supply Voltage                                             | V <sub>DD</sub> | 2.0     | _   | Vcc       | V    | V                                               |

| (for Analog Block*)                                        | Vss             | GND     | _   | Vcc - 2.0 | V    |                                                 |

| Analog Output Source<br>Current                            | IAL             | _       | _   | +1.0      | mA   |                                                 |

| Analog Output Sink<br>Current                              | Іан             | _       | _   | +1.0      | mA   |                                                 |

| Analog Output Load<br>Capacitance for<br>oscillation limit | Соь             | _       | _   | 1.0       | μF   |                                                 |

| Operating Ambient<br>Temperature                           | Та              | -20     | _   | +85       | °C   |                                                 |

<sup>\*:</sup> Except operational amplifier output buffer block

### **■ DC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

## **Digital Block (MCU) Interface**

| Parameter                               | Symbol   |           | Value |           | Unit  | Condition                              |

|-----------------------------------------|----------|-----------|-------|-----------|-------|----------------------------------------|

| raiailletei                             | Syllibol | Min       | Тур   | Max       | Oilit | Condition                              |

| Supply Voltage (Vcc)                    | Vcc      | 4.5       | 5.0   | 5.5       | V     |                                        |

| Supply Current (Vcc) *                  | Icc      | _         | 0.8   | 1.8       | mA    | CLK = 1 MHz, No load                   |

| Input Leakage Current (CLK, DI, and LD) | lılk     | -10       | _     | +10       | μΑ    | V <sub>IN</sub> = 0 to V <sub>CC</sub> |

| Input Low Voltage (CLK, DI, and LD)     | VIL      | _         | _     | 0.2 • Vcc | V     |                                        |

| Input High Voltage (CLK, DI, and LD)    | ViH      | 0.5 • Vcc | _     | _         | V     |                                        |

| Output Low Voltage (DO)                 | Vol      | _         | _     | 0.4       | V     | loL = +2.5 mA                          |

| Output High Voltage (DO)                | Vон      | Vcc - 0.4 | _     | _         | V     | Іон = -400 μА                          |

<sup>\*:</sup> Including the supply current to the operational amplifier block

### **Analog Block (D/A Converters with Operational Amplifier Output Buffers)**

| Parameter                | Symbol          |      | Value |           | Unit  | Condition                                                                                                   |

|--------------------------|-----------------|------|-------|-----------|-------|-------------------------------------------------------------------------------------------------------------|

| raiailletei              | Symbol          | Min  | Тур   | Max       | Oilit | Condition                                                                                                   |

| Supply Current (VDD) **  | IDD             | _    | 1.0   | 1.5       | mA    | Unloaded                                                                                                    |

| Supply Voltage (VDD)     | V <sub>DD</sub> | 2.0  | _     | Vcc       | V     | Vpp - Vss > 2.0 V                                                                                           |

| Supply voltage (VDD)     | Vss             | GND  | _     | Vcc - 2.0 | V     | V SS ≥ 2.0 V                                                                                                |

| Resolution (AOx)         | Res             | _    | 8     | _         | bits  | Monotonicity                                                                                                |

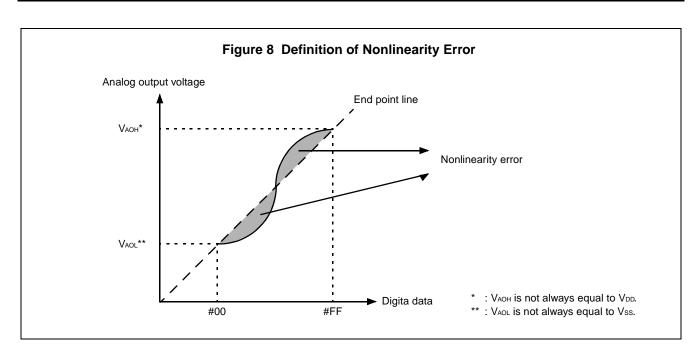

| Nonlinearity Error (AOx) | LE              | -1.5 | _     | +1.5      | LSB   | Unloaded,V <sub>DD</sub> ≤ V <sub>CC</sub> − 0.1 V, V <sub>SS</sub> ≥ 0.1 V<br>See note and Figure 8 below. |

| Differential Error (AOx) | DE              | -1.0 | 0     | +1.0      | LSB   | Unloaded, $V_{DD} \le V_{CC} - 0.1 \text{ V, } V_{SS} \ge 0.1 \text{ V}$<br>See note below.                 |

<sup>\*\* :</sup> Excluding the supply current to the operational amplifier block

#### NOTES

Nonlinearity Error: The difference between the input-output curve for the straight line (ideal line) that connects

the output voltage of the channel when #00 is set, and the output voltage when #FF is set.

Differential Error : The difference from the ideal increment value when the digital data is increased by 1 bit.

# **Analog Block (D/A Converters with Operational Amplifier Output Buffers)**

| Parameter                             | Symbol            | Value                 |                 |                       |      | Condition                                                                                                                                    |  |

|---------------------------------------|-------------------|-----------------------|-----------------|-----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                             | Symbol            | Min                   | Тур             | Max                   | Unit | Condition                                                                                                                                    |  |

| Min. Analog Output<br>Voltage 1 (AOx) | V <sub>AOL1</sub> | Vss                   | _               | Vss + 0.1             | V    | $V_{DD} = V_{CC}, \ V_{SS} = GND = 0 \ V,$ $I_{AL} = 0 \ \mu A, \ Digital \ Data = \#00$                                                     |  |

| Min. Analog Output<br>Voltage 2 (AOx) | V <sub>AOL2</sub> | Vss - 0.2             | Vss             | Vss + 0.2             | V    | $V_{DD} = V_{CC} = 5.0 \text{ V}, \text{ Vss} = \text{GND} = 0 \text{ V},$<br>$I_{AL} = +500 \mu\text{A}, \text{ Digital Data} = \#00$       |  |

| Min. Analog Output<br>Voltage 3 (AOx) | V <sub>AOL3</sub> | Vss                   | _               | Vss + 0.2             | V    | $V_{DD} = V_{CC} = 5.0 \text{ V}, \text{ Vss} = \text{GND} = 0 \text{ V}, \\ I_{AH} = +500 \ \mu\text{A}, \text{ Digital Data} = \#00$       |  |

| Min. Analog Output<br>Voltage 4 (AOx) | V <sub>AOL4</sub> | Vss - 0.3             | Vss             | Vss + 0.3             | V    | $V_{DD} = V_{CC} = 5.0 \text{ V}, \text{ Vss} = \text{GND} = 0 \text{ V},$<br>$I_{AL} = +1.0 \text{ mA}, \text{ Digital Data} = \#00$        |  |

| Min. Analog Output<br>Voltage 5 (AOx) | V <sub>AOL5</sub> | Vss                   | _               | Vss + 0.3             | V    | $V_{DD} = V_{CC} = 5.0 \text{ V}, \text{ Vss} = \text{GND} = 0 \text{ V},$<br>$I_{AH} = +1.0 \text{ mA}, \text{ Digital Data} = \#00$        |  |

| Max. Analog Output<br>Voltage 1 (AOx) | V <sub>AOH1</sub> | V <sub>DD</sub> - 0.1 | _               | V <sub>DD</sub>       | V    | $V_{DD} = V_{CC}$ , $V_{SS} = GND = 0$ V, $I_{AL} = 0$ $\mu A$ , Digital Data = #FF                                                          |  |

| Max. Analog Output<br>Voltage 2 (AOx) | V <sub>AOH2</sub> | V <sub>DD</sub> - 0.2 | _               | V <sub>DD</sub>       | V    | $V_{DD} = V_{CC} = 5.0 \text{ V}, \text{ Vss} = \text{GND} = 0 \text{ V},$ $I_{AL} = +500 \mu\text{A}, \text{ Digital Data} = \#\text{FF}$   |  |

| Max. Analog Output<br>Voltage 3 (AOx) | V <sub>АОНЗ</sub> | V <sub>DD</sub> - 0.2 | V <sub>DD</sub> | V <sub>DD</sub> + 0.2 | V    | $V_{DD} = V_{CC} = 5.0 \text{ V}, \text{ Vss} = \text{GND} = 0 \text{ V}, \\ I_{AH} = +500 \ \mu\text{A}, \text{ Digital Data} = \#FF$       |  |

| Max. Analog Output<br>Voltage 4 (AOx) | <b>V</b> AOH4     | V <sub>DD</sub> - 0.3 | _               | V <sub>DD</sub>       | V    | $V_{DD} = V_{CC} = 5.0 \text{ V}, \text{ Vss} = \text{GND} = 0 \text{ V},$<br>$I_{AL} = +1.0 \text{ mA}, \text{ Digital Data} = \#\text{FF}$ |  |

| Max. Analog Output<br>Voltage 5 (AOx) | V <sub>AOH5</sub> | V <sub>DD</sub> - 0.3 | V <sub>DD</sub> | V <sub>DD</sub> + 0.3 | V    | $V_{DD} = V_{CC} = 5.0 \text{ V}, \text{ Vss} = \text{GND} = 0 \text{ V},$<br>$I_{AH} = +1.0 \text{ mA}, \text{ Digital Data} = \#FF$        |  |

# **■ AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

| Parameter                | Symbol       | Va  | lue | Unit | Condition                                         |

|--------------------------|--------------|-----|-----|------|---------------------------------------------------|

| Parameter                | Symbol       | Min | Max | Unit | Condition                                         |

| Clock Low Time           | <b>t</b> ckL | 200 | _   | ns   |                                                   |

| Clock High Time          | <b>t</b> cкн | 200 | _   | ns   |                                                   |

| Clock Rise Time          | <b>t</b> Cr  | _   | 200 | ns   |                                                   |

| Clock Fall Time          | <b>t</b> Cf  | _   | 200 | ns   |                                                   |

| Data Setup Time          | <b>t</b> DCH | 30  | _   | ns   |                                                   |

| Data Hold Time           | <b>t</b> chd | 60  | _   | ns   |                                                   |

| Load Strobe High Time    | <b>t</b> ldh | 100 | _   | ns   |                                                   |

| Load Strobe Setup Time   | <b>t</b> chL | 200 | _   | ns   |                                                   |

| Load Strobe Hold Time    | <b>t</b> LDC | 100 | _   | ns   |                                                   |

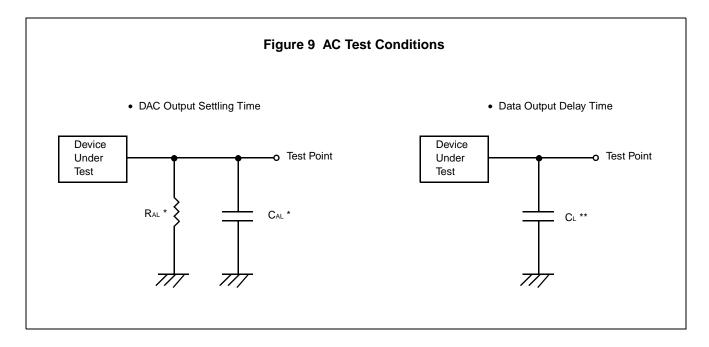

| DAC Output Settling Time | <b>t</b> LDD | _   | 100 | μs   | *R <sub>AL</sub> = 10 kΩ, C <sub>AL</sub> = 50 pF |

| Data Output Delay Time   | <b>t</b> DO  | 70  | 350 | ns   | **C <sub>L</sub> = 20 pF (Min.), 100 pF (Max.)    |

# **■ PACKAGE DIMENSIONS**

# MB88347-PF

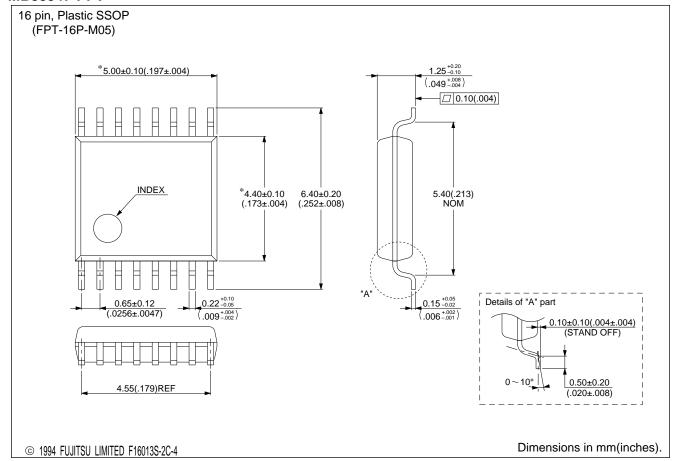

## MB88347-PFV

# **FUJITSU LIMITED**

For further information please contact:

### Japan

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices KAWASAKI PLANT, 4-1-1, Kamikodanaka Nakahara-ku, Kawasaki-shi Kanagawa 211-88, Japan

Tel: (044) 754-3763 Fax: (044) 754-3329

#### **North and South America**

FUJITSU MICROELECTRONICS, INC. Semiconductor Division 3545 North First Street San Jose, CA 95134-1804, U.S.A.

Tel: (408) 922-9000 Fax: (408) 432-9044/9045

#### **Europe**

FUJITSU MIKROELEKTRONIK GmbH Am Siebenstein 6-10 63303 Dreieich-Buchschlag Germany

Tel: (06103) 690-0 Fax: (06103) 690-122

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LIMITED #05-08, 151 Lorong Chuan New Tech Park Singapore 556741

Tel: (65) 281-0770 Fax: (65) 281-0220

### All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.

### F9703

© FUJITSU LIMITED Printed in Japan