# PRELIMINARY

# Clock Generator for DVD Players

### Produ

- Two Reference outputs (27.00 MHz)

- Two 33.8688-MHz outputs

- Two 512fs outputs (22.5792 MHz or 24.576 MHz)

- 27.00-MHz Clock or crystal input

- 3.3V operation (2.5V functional)

- High-drive outputs

Product Features

- 0 PPM application frequency synthesis error

- 16-pin TSSOP package

#### Table 1.

## **Product Description**

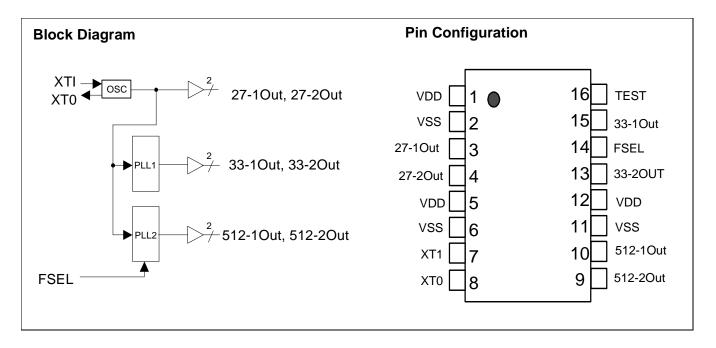

The CY24233 is a clock generator solution that supports DVD digital disk players. It produces a complete set of clocks needed to support the entire system. All output clocks are synthesized from a single 27.00MHz fundamental cut crystal or input reference clock. The output clocks are precisely synthesized to meet the systems low PPM error requirements.

| Test | FSEL | 27-1Out<br>27-2Out | 33-1Out<br>33-2Out | 512-10ut<br>512-20ut |

|------|------|--------------------|--------------------|----------------------|

| 0    | 0    | 27.00 MHz          | 2.700 MHz          | 1.800 MHz            |

| 0    | 1    | 27.00 MHz          | 2.700 MHz          | 3.000 MHz            |

| 1    | 0    | 27.00 MHz          | 33.8688 MHz        | 22.5792 MHz          |

| 1    | 1    | 27.00 MHz          | 33.8688 MHz        | 24.576 MHz           |

reet • San Jose

### Pin Description<sup>[1]</sup>

| Pin #    | Name                 | I/O | Description                                                                                                                                                                                                                                            |

|----------|----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3,4      | 27-1Out<br>27-2Out   | 0   | 3.3V fixed-frequency 27.00-MHz clock outputs. See <i>Table 1</i> on page 1 for frequency selection for test mode functionality.                                                                                                                        |

| 9,10     | 512-1Out<br>512-2Out | 0   | 3.3V fixed frequency clock outputs. See <i>Table 1</i> on page 1 for frequency selection.                                                                                                                                                              |

| 13,15    | 33-1Out<br>33-2Out   | 0   | 3.3V fixed frequency 33.8688-MHz clock outputs. See <i>Table 1</i> on page 1 for fre-<br>quency selection for test mode functionality.                                                                                                                 |

| 14*      | FSEL                 | I   | Frequency selection input. This pin controls the frequency that is present on two 512 output clock pins.                                                                                                                                               |

| 8        | хто                  | 0   | On-chip reference oscillator pin. Drives an external crystal. When an externally generated reference signal is used at XTI, this pin remains unconnected. Bypass with a proper capacitance to ground to match the external crystal's load capacitance. |

| 7        | ХТІ                  | I   | On-chip reference oscillator input pin. Requires either an external crystal (nominally 27 MHz) or externally generated reference signal. Bypass with a proper capacitance to ground to match the external crystal's load capacitance.                  |

| 1, 5, 12 | VDD                  | PWR | 3.3V Power supply.                                                                                                                                                                                                                                     |

| 2,6,11   | VSS                  | PWR | Device ground for all circuitry                                                                                                                                                                                                                        |

| 16       | TEST                 | I   | Internal pull up. If this input pin is asserted low, it will set this device into a test mode.<br>See <i>Table 1</i> on page 1.                                                                                                                        |

Note:

1. **Table Nomenclature:** All pin numbers with an asterisks (\*) immediately after them indicates that they have an internal pull-up resistor to ensure that they will be sensed as a logic HIGH even if no external circuitry is attached to them. I = Input pins, O = Output pins and PWR = Power connection pins.

#### Table 2. Maximum Lumped Capacitative Output Loads

| Clock                                 | Max Load | Units |

|---------------------------------------|----------|-------|

| 27-1Out                               | 40       | pF    |

| 27-20ut                               | 25       | pF    |

| 33-10ut,33-20ut,<br>512-10ut,512-20ut | 15       | pF    |

### **FSEL Switching Synchronization**

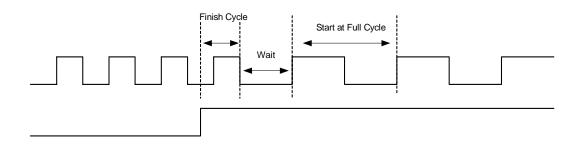

The FSEL input is used to select the frequency of the clocks on the 512-1Out and 512-2Out pins. The device contains internal clock edge synchronization to insure that when the state of this pin is changed while the clocks are running no short (runt) or long (stretched) clocks will occur in the output streams. This is to say that the transitions will be made at a naturally occurring clock edge of the former clocks period and the cycle immediately after the change will be of a full newly selected clocks period and duty cycle.

### **Maximum Ratings**

| Maximum Input Voltage Relative to $V_{SS}$ : $V_{SS}$ – 0.3V |

|--------------------------------------------------------------|

| Maximum Input Voltage Relative to $V_{DD}$ : $V_{DD}$ + 0.3V |

| Storage Temperature:65°C to +150°C                           |

| Operating Temperature:10°C to +75°C                          |

| Maximum ESD protection 2KV                                   |

| Maximum Power Supply:5.5V                                    |

| Operating Voltage:                                           |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation,  $V_{\text{in}}$  and  $V_{\text{out}}$  should be constrained to the range:

$V_{SS} < (V_{in} \text{ or } V_{out}) < V_{DD}$

Unused inputs must always be tied to an appropriate logic voltage level (either  $V_{SS}$  or  $V_{DD}$ ).

#### **DC Parameters** ( $V_{DD} = 3.3V \pm 10\%$ , $T_A = -10^{\circ}C$ to +75°C)

| Parameter           | Description             | Conditions                                                                                                                      | Min. | Тур. | Max. | Unit |

|---------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>IL</sub>     | Input Low Voltage       | Note 2                                                                                                                          | -    | -    | 0.8  | Vdc  |

| V <sub>IH</sub>     | Input High Voltage      |                                                                                                                                 | 2.0  | -    | -    | Vdc  |

| I <sub>IL</sub>     | Input Low Current       | For internal Pull-up resistors, Notes 2 & 3<br>$I_{IL}$ measured at $V_{IN}$ = GND, $I_{IH}$ measured<br>at $V_{IN}$ = $V_{DD}$ |      | -8   | -3.5 | μΑ   |

| IIH                 | Input High Current      |                                                                                                                                 | -    | -    | 5    | μA   |

| V <sub>HYS</sub>    | Input Hysteriss         | Note 2                                                                                                                          | 250  | 410  | 750  | mV   |

| I <sub>dd3.3V</sub> | Dynamic Supply Current  | Test = 1, FSEL=1, Note 4                                                                                                        | -    | 48   | 60   | mA   |

| V <sub>OL</sub>     | Output Low Voltage      | I <sub>OL</sub> = 4.0 mA                                                                                                        | -    | -    | 0.4  | V    |

| V <sub>OH</sub>     | Output High Voltage     | I <sub>OH</sub> = 4.0 mA                                                                                                        | 2.4  | -    | -    | V    |

| C <sub>in</sub>     | Input Pin Capacitance   |                                                                                                                                 | -    | -    | 5    | pF   |

| C <sub>out</sub>    | Output Pin Capacitance  |                                                                                                                                 | -    | -    | 6    | pF   |

| L <sub>pin</sub>    | Pin Inductance          |                                                                                                                                 | -    | -    | 7    | nH   |

| C <sub>xtal</sub>   | Crystal Pin Capacitance |                                                                                                                                 | -    | 5    | -    | pF   |

### AC Parameters <sup>[5]</sup>

| Parameter        | Description                             | Description Conditions                   |    | Тур. | Max. | Units |

|------------------|-----------------------------------------|------------------------------------------|----|------|------|-------|

| F <sub>ERR</sub> | Frequency Error, all outputs            | XTI = 27.00 MHz                          | -  | -    | 0    | ppm   |

| Τ <sub>R</sub>   | Rise Time                               | All clocks at rated load, Note 6         | -  | 2    | 5    | ns    |

| T <sub>F</sub>   | Fall Time                               | All clocks at rated load, Note 6         | -  | 2    | 5    | ns    |

| T <sub>PU</sub>  | Power up to Stable Output               | All Output Clocks, Note 7                | -  | -    | 3    | ms    |

| T <sub>DC1</sub> | Clock Duty Cycle<br>(all output clocks) | All clocks at rated load, Note 7         | 45 | 50   | 55   | %     |

| T <sub>j2</sub>  | Clock Jitter<br>(33-1Out,33-2Out)       | Cycle to cycle jitter<br>(Peak -maximum) | -  | 150  | 200  | ps    |

| T <sub>j2</sub>  | Clock Jitter<br>(512-10ut,512-20ut)     | All clocks at rated load<br>Note 7       | -  | 150  | 200  | ps    |

| T <sub>j3</sub>  | Clock Jitter<br>(27-1Out,27-2Out)       | ]                                        | -  | -    | 350  | ps    |

| T <sub>XS</sub>  | Crystal Oscillator Start-up Time        |                                          | -  | -    | 40   | μs    |

#### Notes:

2. 3.

4. 5. 6.

7. Trigerring is done at 1.5V.

Applicable to input signal: FSEL and Test pins. Although internal pull-up resistors have a typical value of 400K, this value may vary between 200K and 800K. All outputs loaded as per*Table 2* on page 2. Parameters are guaranteed by design and characterization. Not 100% tested in production. All parameters specified with fully loaded outputs. Measured between 0.2\* V<sub>DD</sub> and 0.8\*Volts.

### **Ordering Information**

| Part Number | Package Type | Product Flow             |  |  |

|-------------|--------------|--------------------------|--|--|

| CY24233ZC   | 16-Pin TSSOP | Commercial, -10° to 75°C |  |  |

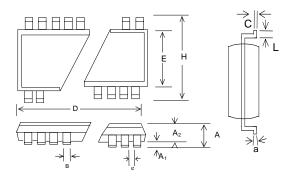

### **Package Drawing and Dimensions**

### **16 Pin TSSOP Outline Dimensions**

|                | Inches    |       |       | Mil      | rs   |      |

|----------------|-----------|-------|-------|----------|------|------|

| Symbol         | Min.      | Nom.  | Max.  | Min.     | Nom. | Max. |

| А              | -         | -     | 0.047 | -        | -    | 1.20 |

| A <sub>1</sub> | 0.002     | -     | 0.006 | 0.05     | -    | 0.15 |

| A2             | 0.031     | 0.039 | 0.041 | 0.80     | 1.00 | 1.05 |

| В              | 0.007     | -     | 0.012 | 0.19     | -    | 0.30 |

| С              | 0.004     | -     | 0.008 | 0.09     | -    | 0.20 |

| D              | 0.193     | 0.197 | 0.201 | 4.90     | 5.00 | 5.10 |

| E              | 0.169     | 0.173 | 0.177 | 4.30     | 4.40 | 4.50 |

| е              | 0.026 BSC |       |       | 0.65 BSC |      |      |

| Н              | 0.244     | 0.252 | 0.260 | 6.20     | 6.40 | 6.60 |

| L              | 0.018     | 0.024 | 0.030 | 0.45     | 0.60 | 0.75 |

| а              | 0°        | -     | 8°    | 0°       | -    | 8°   |

© Cypress Semiconductor Corporation, 2001. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

# **Revision History**

|                                                                                                     | Document Title: CY24233 Clock Generator for DVD Players<br>Document Number: 38-07132 |          |     |                |  |  |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------|-----|----------------|--|--|

| REV.         ECN NO.         Issue<br>Date         Orig. of<br>Change         Description of Change |                                                                                      |          |     |                |  |  |

| **                                                                                                  | 110596                                                                               | 11/29/01 | DMG | New data sheet |  |  |