# 133-MHz Spread Spectrum Clock Synthesizer/Driver with Differential CPU Outputs

| Features                                                                                           | Benefits                                                                           |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Compliant to Intel® CK00 Clock Synthesizer/Driver<br>Specifications                                | Supports next generation Pentium® processors using dif-<br>ferential clock drivers |

| Multiple output clocks at different frequencies                                                    | Motherboard clock generator                                                        |

| — Two pairs of differential CPU outputs, up to 133 MHz                                             | — Optimized for single-CPU design                                                  |

| — Ten synchronous PCI clocks                                                                       | — Support for PCI slots and chipset                                                |

| — Two MRef clocks, 180 degrees out of phase                                                        | — Drives up to two Direct Rambus™ Clock Generators                                 |

| — Three AGP and Hub Link clocks at 66 MHz                                                          | (DRCG)                                                                             |

| — Two 48-MHz clocks                                                                                | — Supports USB host controller and SuperI/O chip                                   |

| — Two reference clocks at 14.318 MHz                                                               | — Supports ISA slots and I/O chip                                                  |

| Spread Spectrum clocking                                                                           | Enables reduction of EMI and overall system cost                                   |

| — 31 kHz modulation frequency                                                                      |                                                                                    |

| — EPROM programmable percentage of spreading. De-<br>fault is –0.6%, which is recommended by Intel |                                                                                    |

| Power-down features                                                                                | Enables ACPI compliant designs                                                     |

| Three Select inputs                                                                                | Supports up to eight CPU clock frequencies                                         |

| Low-skew and low-jitter outputs                                                                    | Meets tight system timing requirements at high frequency                           |

| OE and Test Mode support                                                                           | Enables ATE and "bed of nails" testing                                             |

| 48-pin SSOP package                                                                                | Widely available, standard package enables lower cost                              |

Intel and Pentium are registered trademarks of Intel Corporation. Direct Rambus is a trademark of Rambus, Inc.

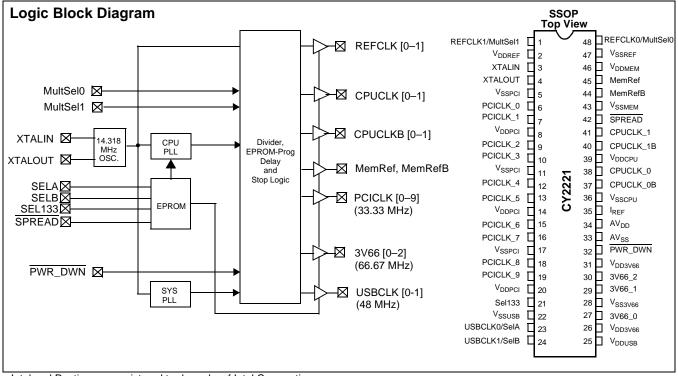

### **Pin Summary**

| Name                     | Pins                                   | Description                                                                                                                |

|--------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| V <sub>SSREF</sub>       | 47                                     | 3.3V Reference ground                                                                                                      |

| V <sub>DDREF</sub>       | 2                                      | 3.3V Reference voltage supply                                                                                              |

| V <sub>SSPCI</sub>       | 5, 11, 17                              | 3.3V PCI ground                                                                                                            |

| V <sub>DDPCI</sub>       | 8, 14, 20                              | 3.3V PCI voltage supply                                                                                                    |

| V <sub>SS3V66</sub>      | 28                                     | 3.3V AGP and Hub Link ground                                                                                               |

| V <sub>DD3V66</sub>      | 26, 31                                 | 3.3V AGP and Hub Link voltage supply                                                                                       |

| V <sub>SSUSB</sub>       | 22                                     | 3.3V USB ground                                                                                                            |

| V <sub>DDUSB</sub>       | 25                                     | 3.3V USB voltage supply                                                                                                    |

| V <sub>SSCPU</sub>       | 36                                     | 3.3V CPU ground                                                                                                            |

| V <sub>DDCPU</sub>       | 39                                     | 3.3V CPU voltage supply                                                                                                    |

| V <sub>SSMEM</sub>       | 43                                     | 3.3V Memory ground                                                                                                         |

| V <sub>DDMEM</sub>       | 46                                     | 3.3V Memory voltage supply                                                                                                 |

| AV <sub>SS</sub>         | 33                                     | Analog ground for PLL and Core                                                                                             |

| AV <sub>DD</sub>         | 34                                     | Analog voltage supply to PLL and Core                                                                                      |

| I <sub>REF</sub>         | 35                                     | Reference current for external biasing                                                                                     |

| XTALIN <sup>[1]</sup>    | 3                                      | Reference crystal input                                                                                                    |

| XTALOUT <sup>[1]</sup>   | 4                                      | Reference crystal feedback                                                                                                 |

| CPUCLK [0-1]             | 38, 41                                 | CPU clock outputs                                                                                                          |

| CPUCLK [0–1]B            | 37, 40                                 | Inverse CPU clock outputs                                                                                                  |

| PCICLK [0–9]             | 6, 7, 9, 10, 12, 13, 15, 16,<br>18, 19 | PCI clock outputs, synchronously running at 33.33 MHz                                                                      |

| MemRef                   | 45                                     | MemRef clock output, drives memory clock generator                                                                         |

| MemRefB                  | 44                                     | MemRefB clock output 180 degrees out of phase with MemRef                                                                  |

| 3V66_[0-2]               | 27, 29, 30                             | AGP and Hub Link clock outputs, running at 66 MHz                                                                          |

| USBCLK [0–1]/Sel[A–B]    | 23, 24                                 | Sel [A–B] inputs are sensed then internally latched on power-up be-<br>fore the pins are used for 48-MHz USB clock outputs |

| REFCLK[0-1]/MultSel[0-1] | 1, 48                                  | MultSel[0–1] inputs are sensed then internally latched on power-up before the pins are Reference clock outputs, 14.318 MHz |

| PWR_DWN                  | 32                                     | Active LOW input, powers down part when asserted                                                                           |

| SPREAD <sup>[2]</sup>    | 42                                     | Active LOW input, enables spread spectrum when asserted                                                                    |

| SEL133                   | 21                                     | CPU frequency select input (See Function Table)                                                                            |

Notes:

1. For best accuracy, use a parallel-resonant crystal, C<sub>LOAD</sub> = 18 pF. For crystals with different C<sub>LOAD</sub>, please refer to the application note, "Crystal Oscillator

Topics." 2. After Crystal Oscillator starts and during low period of Xin, if three pulses come on SPREAD part will go into internal test mode.

# Function Table<sup>[3]</sup>

| SEL133 | SELA | SELB | CPUCLK<br>(MHz) | MemRef<br>(MHz) | 3V66CLK<br>(MHz) | PCICLK<br>(MHz) | USBCLK<br>(MHz) | REFCLK<br>(MHz) | Notes: |

|--------|------|------|-----------------|-----------------|------------------|-----------------|-----------------|-----------------|--------|

| 0      | 0    | 0    | 100             | 50              | 66               | 33              | 48              | 14.318          |        |

| 0      | 0    | 1    | N/A             | N/A             | N/A              | N/A             | N/A             | N/A             |        |

| 0      | 1    | 0    | N/A             | N/A             | N/A              | N/A             | N/A             | N/A             |        |

| 0      | 1    | 1    | Hi-Z            | Hi-Z            | Hi-Z             | Hi-Z            | Hi-Z            | Hi-Z            |        |

| 1      | 0    | 0    | 133             | 66              | 66               | 33              | 48              | 14.318          |        |

| 1      | 0    | 1    | N/A             | N/A             | N/A              | N/A             | N/A             | N/A             |        |

| 1      | 1    | 0    | N/A             | N/A             | N/A              | N/A             | N/A             | N/A             |        |

| 1      | 1    | 1    | TCLK/2          | TCLK/4          | TCLK/4           | TCLK/8          | TCLK/2          | TCLK            |        |

Note: 3. TCLK is a test clock driven in on the XTALIN input in test mode.

### **Actual Clock Frequency Values**

| Clock Output | Target<br>Frequency<br>(MHz) | Actual<br>Frequency<br>(MHz) | РРМ |

|--------------|------------------------------|------------------------------|-----|

| CPUCLK       | 100                          | TBD                          | TBD |

| CPUCLK       | 133                          | TBD                          | TBD |

| USBCLK       | 48                           | 48.008                       | 167 |

### **Swing Select Functions**

| MultSel0 | MultSel1 | Board Target | Reference R, I <sub>REF =</sub>        | Output<br>Current        | V <sub>OH</sub> @ Z,<br>Iref = 2.32mA |

|----------|----------|--------------|----------------------------------------|--------------------------|---------------------------------------|

| 0        | 0        | 60Ω          | Rr = 475 <u>+</u> 1%,<br>Iref = 2.32mA | I <sub>OH</sub> = 5*Iref | 0.71 @ 60                             |

| 0        | 0        | 50Ω          | Rr = 475 <u>+</u> 1%,<br>Iref = 2.32mA | I <sub>OH</sub> = 5*Iref | 0.59 @ 50                             |

| 0        | 1        | 60Ω          | Rr = 475 <u>+</u> 1%,<br>Iref = 2.32mA | I <sub>OH</sub> = 6*Iref | 0.85 @ 60                             |

| 0        | 1        | 50Ω          | Rr = 475 <u>+</u> 1%,<br>Iref = 2.32mA | I <sub>OH</sub> = 6*Iref | 0.71 @ 50                             |

| 1        | 0        | 60Ω          | Rr = 475 <u>+</u> 1%,<br>Iref = 2.32mA | I <sub>OH</sub> = 4*Iref | 0.56 @ 60                             |

| 1        | 0        | 50Ω          | Rr = 475 <u>+</u> 1%,<br>Iref = 2.32mA | I <sub>OH</sub> = 4*Iref | 0.47 @ 50                             |

| 1        | 1        | 60Ω          | Rr = 475 <u>+</u> 1%,<br>Iref = 2.32mA | I <sub>OH</sub> = 7*Iref | 0.99 @ 60                             |

| 1        | 1        | 50Ω          | Rr = 475 <u>+</u> 1%,<br>Iref = 2.32mA | I <sub>OH</sub> = 7*Iref | 0.82 @ 50                             |

# **Clock Driver Impedances**

|                 |                       |             | Impedance    |                     |                 |

|-----------------|-----------------------|-------------|--------------|---------------------|-----------------|

| Buffer Name     | V <sub>DD</sub> Range | Buffer Type | Minimum<br>Ω | <b>Typical</b><br>Ω | $\max_{\Omega}$ |

| CPUCLK, CPUCLKB |                       | Type X1     |              |                     |                 |

| USB, REF        | 3.135–3.465           | Туре 3      | 20           | 40                  | 60              |

| PCI, 3V66       | 3.135–3.465           | Туре 5      | 12           | 30                  | 55              |

| MemRef, MemRefB | 3.135–3.465           | Туре 5      | 12           | 30                  | 55              |

# **Maximum Ratings**

| (Above which the useful life may be impaired. For lines, not tested.) | or user guide-            |

|-----------------------------------------------------------------------|---------------------------|

| Supply Voltage                                                        | 0.5 to +7.0V              |

| Input Voltage                                                         | / to V <sub>DD</sub> +0.5 |

| Storage Temperature (Non-Condensing)65°C to +               | -150°C |

|-------------------------------------------------------------|--------|

| Max. Soldering Temperature (10 sec) +                       | -260°C |

| Junction Temperature +                                      | -150°C |

| Package Power Dissipation                                   | 1W     |

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015)> | 2000V  |

### **Operating Conditions** Over which Electrical Parameters are Guaranteed

| Parameter                                                                                                                                             | Description                                                    | Min.   | Max.     | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------|----------|------|

| V <sub>DDREF</sub> , V <sub>DDPCI</sub> , AV <sub>DD</sub> ,<br>V <sub>DD3V66</sub> , V <sub>DDUSB</sub> , V <sub>DDCPU</sub> ,<br>V <sub>DDMEM</sub> | 3.3V Supply Voltages                                           | 3.135  | 3.465    | V    |

| T <sub>A</sub>                                                                                                                                        | Operating Temperature, Ambient                                 | 0      | 70       | °C   |

| C <sub>in</sub>                                                                                                                                       | Input Pin Capacitance                                          |        | 5        | pF   |

| C <sub>XTAL</sub>                                                                                                                                     | XTAL Pin Capacitance                                           |        | 22.5     | pF   |

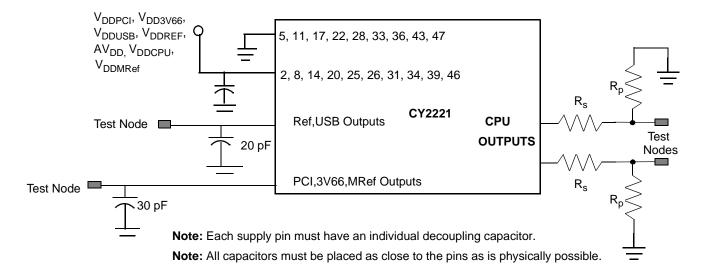

| CL                                                                                                                                                    | Max. Capacitive Load on<br>MemRef, USBCLK, REF<br>PCICLK, 3V66 |        | 20<br>30 | pF   |

| f <sub>(REF)</sub>                                                                                                                                    | Reference Frequency, Oscillator Nominal Value                  | 14.318 | 14.318   | MHz  |

### Electrical Characteristics Over the Operating Range

| Parameter          | Description               | Test Conditions                                                                                      |                                  |      | Max. | Unit |

|--------------------|---------------------------|------------------------------------------------------------------------------------------------------|----------------------------------|------|------|------|

| V <sub>IH</sub>    | High-level Input Voltage  | Except Crystal Pads. Threshold voltage for crystal pads = $V_{DD}/2$                                 |                                  | 2.0  |      | V    |

| V <sub>IL</sub>    | Low-level Input Voltage   | Except Crystal Pads                                                                                  |                                  |      | 0.8  | V    |

| V <sub>OH</sub>    | High-level Output Voltage | MemRef, USB, REF, 3V66                                                                               | I <sub>OH</sub> = -1 mA          | 2.4  |      | V    |

|                    |                           | PCI                                                                                                  | I <sub>OH</sub> = -1 mA          | 2.4  |      | V    |

| V <sub>OL</sub>    | Low-level Output Voltage  | MemRef, USB, REF, 3V66                                                                               | I <sub>OL</sub> = 1 mA           |      | 0.4  | V    |

|                    |                           | PCI                                                                                                  | I <sub>OL</sub> = 1 mA           |      | 0.55 | V    |

| I <sub>IH</sub>    | Input High Current        | $0 \le V_{IN} \le V_{DD}$                                                                            |                                  | -5   | 5    | μΑ   |

| IIL                | Input Low Current         | $0 \le V_{IN} \le V_{DD}$                                                                            |                                  | -5   | 5    | μΑ   |

| I <sub>OH</sub>    | High-level Output Current | CPU                                                                                                  | Type X1, V <sub>OH</sub> = 0.65V | 12.9 |      | mA   |

|                    |                           | For I <sub>OH</sub> =6*IRef Configuration                                                            | Type X1, V <sub>OH</sub> = 0.74V |      | 14.9 |      |

|                    |                           | USB, REF                                                                                             | Type 3, V <sub>OH</sub> = 1.00V  | -29  |      |      |

|                    |                           |                                                                                                      | Type 3, V <sub>OH</sub> = 3.135V |      | -23  |      |

|                    |                           | 3V66, PCI, MemRef, MemRefB                                                                           | Type 5, V <sub>OH</sub> = 1.00V  | -33  |      |      |

|                    |                           |                                                                                                      | Type 5, V <sub>OH</sub> = 3.135V |      | -33  |      |

| I <sub>OL</sub>    | Low-level Output Current  |                                                                                                      |                                  |      |      | mA   |

|                    |                           | USB, REF                                                                                             | Type 3, V <sub>OL</sub> = 1.95V  | 29   |      |      |

|                    |                           |                                                                                                      | Type 3, V <sub>OL</sub> = 0.4V   |      | 27   |      |

|                    |                           | 3V66, PCI, MemRef, MemRefB                                                                           | Type 5, V <sub>OL</sub> =1.95 V  | 30   |      |      |

|                    |                           |                                                                                                      | Type 5, V <sub>OL</sub> = 0.4V   |      | 38   |      |

| I <sub>OZ</sub>    | Output Leakage Current    | Three-state                                                                                          |                                  |      | 10   | μA   |

| I <sub>DD3</sub>   | 3.3V Power Supply Current | AV <sub>DD</sub> /V <sub>DD33</sub> = 3.465V, V <sub>DD25</sub> = 2.625V, F <sub>CPU</sub> = 133 MHz |                                  |      | 250  | mA   |

| I <sub>DDPD3</sub> | 3.3V Shutdown Current     | AV <sub>DD</sub> /V <sub>DDQ3</sub> = 3.465V, V <sub>DD25</sub> = 2.62                               | 5V                               |      | 20   | mA   |

# Switching Characteristics<sup>[4]</sup> Over the Operating Range

| Parameter              | Output               | Description                      | Test Conditions                                                           | Min.              | Max.                     | Unit |

|------------------------|----------------------|----------------------------------|---------------------------------------------------------------------------|-------------------|--------------------------|------|

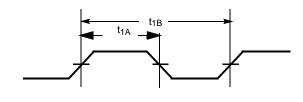

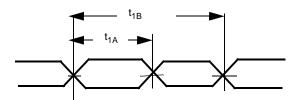

| t <sub>1</sub>         | All                  | Output Duty Cycle <sup>[5]</sup> | t <sub>1A</sub> /(t <sub>1B</sub> )                                       | 45                | 55                       | %    |

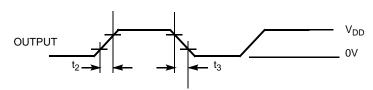

| t <sub>2</sub>         | CPU                  | Rise Time                        | Measured at 20% to 80% of V <sub>oh</sub>                                 | 175               | 700                      | ps   |

| t <sub>2</sub>         | USB, REF             | Rising Edge Rate                 | Between 0.4V and 2.4V                                                     | 0.5               | 2.0                      | V/ns |

| t <sub>2</sub>         | PCI, 3V66,<br>MemRef | Rising Edge Rate                 | Between 0.4V and 2.4V                                                     | 1.0               | 4.0                      | V/ns |

| t <sub>3</sub>         | CPU                  | Fall Time                        | Measured at 80% to 20% of $V_{oh}$                                        | 175               | 700                      | ps   |

| t <sub>3</sub>         | USB, REF             | Falling Edge Rate                | Between 2.4V and 0.4V                                                     | 0.5               | 2.0                      | V/ns |

| t <sub>3</sub>         | PCI, 3V66,<br>MemRef | Falling Edge Rate                | Between 2.4V and 0.4V                                                     | 1.0               | 4.0                      | V/ns |

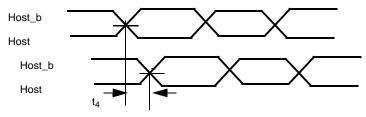

| t <sub>4</sub>         | CPU                  | CPU-CPU Skew                     | Measured at Crossover                                                     |                   | 150                      | ps   |

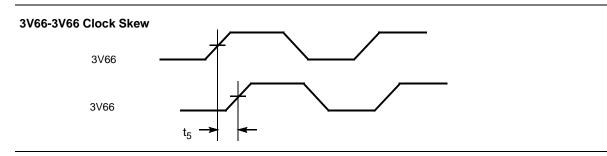

| t <sub>5</sub>         | 3V66                 | 3V66-3V66 Skew                   | Measured at 1.5V                                                          |                   | 250                      | ps   |

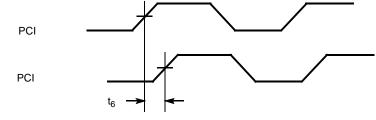

| t <sub>6</sub>         | PCI                  | PCI-PCI Skew                     | Measured at 1.5V                                                          |                   | 500                      | ps   |

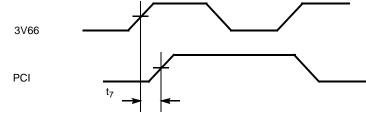

| t <sub>7</sub>         | 3V66,PCI             | 3V66-PCI Clock Skew              | 3V66 leads. Measured at 1.5V                                              | 1.5               | 3.5                      | ns   |

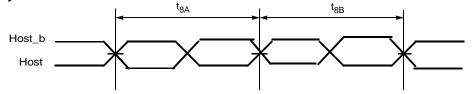

| t <sub>8</sub>         | CPU                  | Cycle-Cycle Clock Jitter         | Measured at Crossover $t_8 = t_{8A} - t_{8B}$<br>With all outputs running |                   | 200                      | ps   |

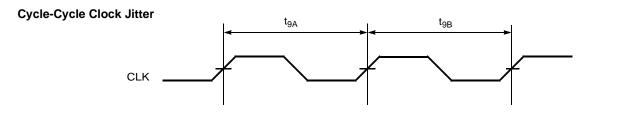

| t <sub>9</sub>         | Mref                 | Cycle-Cycle Clock Jitter         | Measured at 1.5V $t_{9} = t_{9A} - t_{9B}$                                |                   | 250                      | ps   |

| t <sub>9</sub>         | 3V66                 | Cycle-Cycle Clock Jitter         | Measured at 1.5V $t_{9} = t_{9A} - t_{9B}$                                |                   | 300                      | ps   |

| t <sub>9</sub>         | USB                  | Cycle-Cycle Clock Jitter         | Measured at 1.5V $t_{9} = t_{9A} - t_{9B}$                                |                   | 350                      | ps   |

| t <sub>9</sub>         | PCI                  | Cycle-Cycle Clock Jitter         | Measured at 1.5V $t_{9} = t_{9A} - t_{9B}$                                |                   | 500                      | ps   |

| t <sub>9</sub>         | REF                  | Cycle-Cycle Clock Jitter         | Measured at 1.5V $t_{9} = t_{9A} - t_{9B}$                                |                   | 1000                     | ps   |

|                        | CPU, PCI             | Settle Time                      | CPU and PCI clock stabilization from power-up                             |                   | 3                        | ms   |

|                        | CPU                  | Rise/Fall Matching               | Measured with test loads <sup>[6, 7]</sup>                                |                   | 20%                      |      |

|                        | CPU                  | Overshoot                        | Measured with test loads <sup>[7]</sup>                                   |                   | V <sub>oh</sub> +<br>0.2 | V    |

|                        | CPU                  | Undershoot                       | Measured with test loads <sup>[7]</sup>                                   | -0.2              |                          | V    |

| V <sub>oh</sub>        | CPU                  | High-level Output Voltage        | Measured with test loads <sup>[7]</sup>                                   | 0.65              | 0.74                     | V    |

| V <sub>ol</sub>        | CPU                  | Low-level Output Voltage         | Measured with test loads <sup>[7]</sup>                                   | 0.0               | 0.05                     | V    |

| V <sub>crossover</sub> | CPU                  | Crossover Voltage                | Measured with test loads <sup>[7]</sup>                                   | 45%<br>of<br>0.65 | 55%<br>of<br>0.74        | V    |

Notes:

All parameters specified with loaded outputs.

Duty cycle is measured at 1.5V when V<sub>DD</sub> = 3.3V. When V<sub>DD</sub> = 2.5V, duty cycle is measured at 1.25V.

Determined as a fraction of 2\*(Trp –Trn)/(Trp +Trn) Where Trp is a rising edge and Trp is an intersecting falling edge.

The test load is R<sub>s</sub> = 33.2Ω, R<sub>p</sub> = 49.9Ω in test circuit.

### **Switching Waveforms**

Duty Cycle Timing (Single Ended Output)

### Duty Cycle Timing (CPU Differential Output)

#### All Outputs Rise/Fall Time

#### **CPU-CPU Clock Skew**

### Switching Waveforms (continued)

#### **PCI-PCI Clock Skew**

#### 3V66-PCI Clock Skew

#### **CPU Clock Cycle-Cycle Jitter**

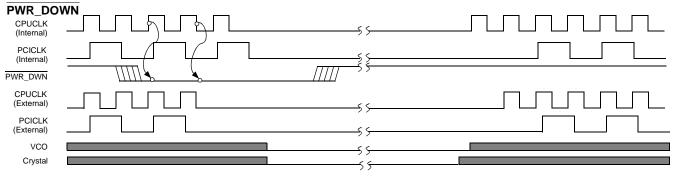

Shaded section on the VCO and Crystal waveforms indicates that the VCO and crystal oscillator are active, and there is a valid clock.

### **Test Circuit**

#### **Ordering Information**

| Ordering Code | Package<br>Name | Package Type | Operating<br>Range |

|---------------|-----------------|--------------|--------------------|

| CY2221PVC-1   | O48             | 48-Pin SSOP  | Commercial         |

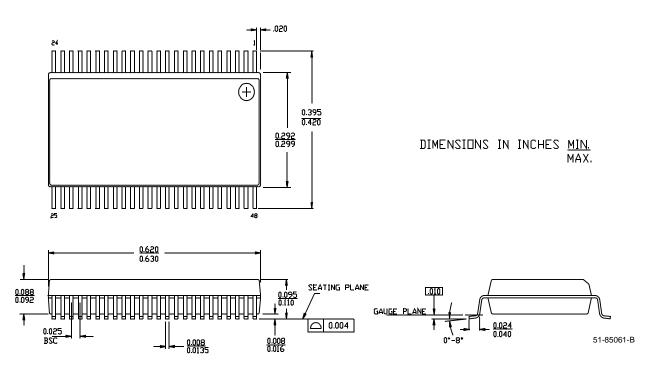

#### Package Diagram

#### 48-Lead Shrunk Small Outline Package O48

#### Document #: 38-07212 Rev. \*\*

#### Page 8 of 9

© Cypress Semiconductor Corporation, 2001. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

| Document Title: CY2221 133-Mhz Spread Spectrum Clock Synthesizer/Driver with Differential CPU Outputs<br>Document Number: 38-07212 |         |               |                    |                                               |

|------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|--------------------|-----------------------------------------------|

| REV.                                                                                                                               | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change                         |

| **                                                                                                                                 | 110345  | 10/28/01      | SZV                | Change from Spec number: 38-00814 to 38-07212 |