# 3.3V, 160-MHz, 1:12 Clock Distribution Buffer

#### **Product Features**

- 160-MHz Clock Support

- LVPECL or LVCMOS/LVTTL Clock Input

- LVCMOS/LVTTL Compatible Inputs

- 12 Clock Outputs: Drive up to 24 Clock Lines

- Synchronous Output Enable

- Output Three-state Control

- 350-ps Maximum Output-to-Output Skew

- Pin Compatible with MPC948

- Industrial Temp. Range: -40°C to +85°C

- 32-Pin TQFP Package

#### Description

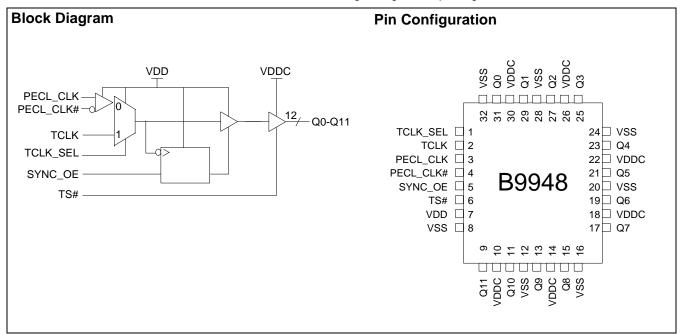

The B9948 is a low-voltage clock distribution buffer with the capability to select either a differential LVPECL or a LVC-MOS/LVTTL compatible input clock. The two clock sources can be used to provide for a test clock as well as the primary system clock. All other control inputs are LVCMOS/LVTTL compatible. The twelve outputs are 3.3V LVCMOS or LVTTL compatible and can drive two series terminated 50 $\Omega$  transmission lines. With this capability the B9948 has an effective fan-out of 1:24. The outputs can also be three-stated via the three-state input TS#. Low output-to-output skews make the B9948 an ideal clock distribution buffer for nested clock trees in the most demanding of synchronous systems.

The B9948 also provides a synchronous output enable input for enabling or disabling the output clocks. Since this input is internally synchronized to the input clock, potential output glitching or runt pulse generation is eliminated.

# **Pin Description**<sup>[1]</sup>

| Pin                                                 | Name      | PWR  | I/O   | Description                                                                                                                       |

|-----------------------------------------------------|-----------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| 3                                                   | PECL_CLK  |      | I, PU | PECL Input Clock                                                                                                                  |

| 4                                                   | PECL_CLK# |      | I, PD | PECL Input Clock                                                                                                                  |

| 2                                                   | TCLK      |      | I, PU | External Reference/Test Clock Input                                                                                               |

| 9, 11, 13, 15, 17,<br>19, 21, 23, 25, 27,<br>29, 31 | Q(11:0)   | VDDC | 0     | Clock Outputs                                                                                                                     |

| 1                                                   | TCLK_SEL  |      | I, PU | Clock Select Input. When LOW, PECL clock is selected and when HIGH TCLK is selected.                                              |

| 5                                                   | SYNC_OE   |      | I, PU | Output Enable Input. When asserted HIGH, the outputs are enabled and when set LOW the outputs are disabled in a LOW state.        |

| 6                                                   | TS#       |      | I, PU | Three-state Control Input. When asserted LOW, the output buffers are three-stated. When set HIGH, the output buffers are enabled. |

| 10, 14, 18, 22, 26,<br>30                           | VDDC      |      |       | 3.3V Power Supply for Output Clock Buffers                                                                                        |

| 7                                                   | VDD       |      |       | 3.3V Power Supply                                                                                                                 |

| 8, 12, 16, 20, 24,<br>28, 32                        | VSS       |      |       | Common Ground                                                                                                                     |

Note:

1. PD = Internal Pull-Down, PU = Internal Pull-Up.

### **Output Enable/ Disable**

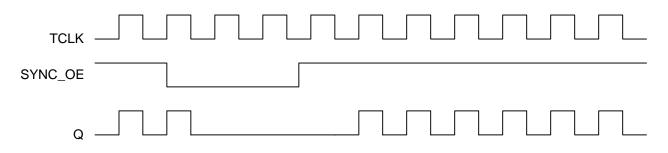

The B9948 features a control input to enable or disable the outputs. This data is latched on the falling edge of the input clock. When SYNC\_OE is asserted LOW, the outputs are disabled in a LOW state. When SYNC\_OE is set HIGH, the outputs are enabled as shown in *Figure 1*.

Figure 1. SYNC\_OE Timing Diagram

# **Maximum Ratings**

| Maximum Input Voltage Relative to V_{SS}: V_{SS} - 0.3V      |

|--------------------------------------------------------------|

| Maximum Input Voltage Relative to $V_{DD}$ : $V_{DD}$ + 0.3V |

| Storage Temperature:65°C to + 150°C                          |

| Operating Temperature:40°C to +85°C                          |

| Maximum ESD Protection 2 KV                                  |

| Maximum Power Supply:5.5V                                    |

| Maximum Input Current:±20 mA                                 |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation,  $V_{\text{in}}$  and  $V_{\text{out}}$  should be constrained to the range:

$V_{SS} < (V_{in} \text{ or } V_{out}) < V_{DD}$

Unused inputs must always be tied to an appropriate logic voltage level (either  $V_{SS}$  or  $V_{DD}$ ).

# **DC Parameters:** $V_{DDC} = 3.3V \pm 10\%$ , $V_{DD} = 3.3V \pm 10\%$ , $T_A = -40^{\circ}C$ to +85°C

| Parameter        | Description                                             | Conditions                                                         | Min.            | Тур. | Max.            | Unit |

|------------------|---------------------------------------------------------|--------------------------------------------------------------------|-----------------|------|-----------------|------|

| V <sub>IL</sub>  | Input Low Voltage                                       | PECL_CLK, Single Ended                                             | 1.49            |      | 1.825           | V    |

|                  |                                                         | All other inputs                                                   | V <sub>SS</sub> |      | 0.8             |      |

| V <sub>IH</sub>  | Input High Voltage                                      | PECL_CLK, Single Ended                                             | 2.135           |      | 2.42            | V    |

|                  |                                                         | All other inputs                                                   | 2.0             |      | V <sub>DD</sub> |      |

| IIL              | Input Low Current (@V <sub>IL</sub> = V <sub>SS</sub> ) | Note 2                                                             |                 |      | -100            | μA   |

| I <sub>IH</sub>  | Input High Current (@V <sub>IL</sub> =V <sub>DD</sub> ) |                                                                    |                 |      | 100             | μA   |

| V <sub>PP</sub>  | Peak-to-Peak Input Voltage<br>PECL_CLK                  | Note 3                                                             | 300             |      | 1000            | mV   |

| V <sub>CMR</sub> | Common Mode Range PECL_CLK                              |                                                                    | $V_{DD}-2.0$    |      | $V_{DD} - 0.6$  | V    |

| V <sub>OL</sub>  | Output Low Voltage                                      | I <sub>OL</sub> = 20 mA, Note 4                                    |                 |      | 0.4             | V    |

| V <sub>OH</sub>  | Output High Voltage                                     | $I_{OH} = -20 \text{ mA}, V_{DDC} = 3.3 \text{V}, \text{ Note } 4$ | 2.5             |      |                 | V    |

| I <sub>DD</sub>  | Quiescent Supply Current                                | All $V_{DDC}$ and $V_{DD}$                                         |                 | 1    | 2               | mA   |

| C <sub>in</sub>  | Input Capacitance                                       |                                                                    |                 |      | 4               | pF   |

2. 3.

Inputs have pull-up resistors that effect input current, PECL\_CLK# has a pull-down resistor. The V<sub>CMR</sub> is the difference from the most positive side of the differential input signal. Normal operation is obtained when the "High" input is within the V<sub>CMR</sub> range and the input lies within the V<sub>PP</sub> specification.

4. Driving series or parallel terminated 50 $\Omega$  (or 50 $\Omega$  to V<sub>DD</sub>/2) transmission lines.

# **AC Parameters**<sup>[5]</sup>: $V_{DDC} = 3.3V \pm 10\%$ , $V_{DD} = 3.3V \pm 10\%$ , $T_A = -40^{\circ}C$ to +85°C

| Parameter  | Description                                 | Conditions                      | Min.           | Тур. | Max.           | Unit |

|------------|---------------------------------------------|---------------------------------|----------------|------|----------------|------|

| Fmax       | Maximum Input Frequency <sup>[6]</sup>      |                                 | 160            |      |                | MHz  |

| Tpd        | PECL_CLK to Q Delay <sup>[6]</sup>          |                                 | 4.0            |      | 8.0            | ns   |

|            | TCLK to Q Delay <sup>[6]</sup>              |                                 | 4.4            |      | 8.9            |      |

| FoutDC     | Output Duty Cycle <sup>[6,7]</sup>          | Measured at V <sub>DDC</sub> /2 | TCYCLE/2 - 800 |      | TCYCLE/2 + 800 | ps   |

| tpZL, tpZH | Output enable time (all outputs)            |                                 | 2              |      | 10             | ns   |

| tpLZ, tpHZ | Output disable time (all outputs)           |                                 | 2              |      | 10             | ns   |

| Tskew      | Output-to-Output Skew <sup>[6,8]</sup>      |                                 |                |      | 350            | ps   |

| Tskew (pp) | Part-to-Part Skew <sup>[9]</sup>            | PECL_CLK to Q                   |                |      | 1.5            | ns   |

|            |                                             | TCLK to Q                       |                |      | 2.0            |      |

| Ts         | Set-up Time <sup>[6,10]</sup>               | SYNC_OE to PECL_CLK             | 1.0            |      |                | ns   |

|            |                                             | SYNC_OE to TCLK                 | 0.0            |      |                |      |

| Th         | Hold Time <sup>[6,10]</sup>                 | PECL_CLK to SYNC_OE             | 0.0            |      |                | ns   |

|            |                                             | TCLK to SYNC_OE                 | 1.0            |      |                |      |

| Tr/Tf      | Output Clocks Rise/Fall Time <sup>[8]</sup> | 0.8V to 2.0V                    | 0.2            |      | 1.0            | ns   |

Notes:

Parameters are guaranteed by design and characterization. Not 100% tested in production. All parameters specified with loaded outputs. Outputs driving  $50\Omega$  transmission lines. 50% input duty cycle.

5. 6. 7. 8. 9.

Soft inputs loaded with 30 pF each

Part-to-Part Skew at a given temperature and voltage

Set-up and Hold times are relative to the falling edge of the input clock

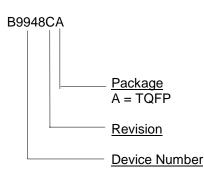

### **Ordering Information**

| Part Number         | Package Type | Production Flow            |  |  |

|---------------------|--------------|----------------------------|--|--|

| B9948CA 32-Pin TQFP |              | Industrial, –40°C to +85°C |  |  |

Note: The ordering part number is formed by a combination of device number, device revision, package style, and screening as shown below.

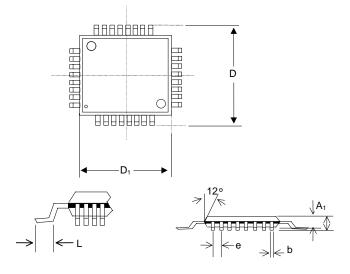

# **Package Drawing and Dimensions**

### **32-Pin TQFP Outline Dimensions**

|                |       | Inches  |       | М    | illimete | rs   |

|----------------|-------|---------|-------|------|----------|------|

| Symbol         | Min.  | Nom.    | Max.  | Min. | Nom.     | Max. |

| A              | -     | -       | 0.047 | -    | -        | 1.20 |

| A <sub>1</sub> | 0.002 | -       | 0.006 | 0.05 | -        | 0.15 |

| A2             | 0.037 | -       | 0.041 | 0.95 | -        | 1.05 |

| D              | -     | 0.354   | -     | -    | 9.00     | -    |

| D <sub>1</sub> | -     | 0.276   | -     | -    | 7.00     | -    |

| b              | 0.012 | -       | 0.018 | 0.30 | -        | 0.45 |

| е              | C     | .031 BS | С     | (    | ).80 BS0 | C    |

| L              | 0.018 | -       | 0.030 | 0.45 | -        | 0.75 |

© Cypress Semiconductor Corporation, 2002. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor product nor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

| Document Title: B9948 3.3V, 160 MHz, 1:12 Clock Distribution Buffer<br>Document Number: 38-07079 |         |               |                    |                                               |  |  |

|--------------------------------------------------------------------------------------------------|---------|---------------|--------------------|-----------------------------------------------|--|--|

| Rev.                                                                                             | ECN No. | Issue<br>Date | Orig. of<br>Change | Description of Change                         |  |  |

| **                                                                                               | 107115  | 06/06/01      | IKA                | Convert from IMI to Cypress                   |  |  |

| *A                                                                                               | 108060  | 07/03/01      | NDP                | Changed Commercial to Industrial (See page 6) |  |  |

| *В                                                                                               | 109805  | 01/31/02      | DSG                | Convert from Word to Frame (Cypress format)   |  |  |