INTEGRATED CIRCUITS

Product specification Supersedes data of August 1992 File under Integrated Circuits, IC02 1995 Feb 16

# **Philips Semiconductors**

### **TDA8446**

### FEATURES

- R, G, B clamped inputs

- Luminance and chrominance difference matrix

- Y-clamped inputs

- Fast switching between internal and external Y

- Chrominance input

- Amplifier with selectable gain

- 3-state switch for chrominance output.

### APPLICATIONS

- Digital TV systems

- Desktop video architecture.

### QUICK REFERENCE DATA

### DESCRIPTION

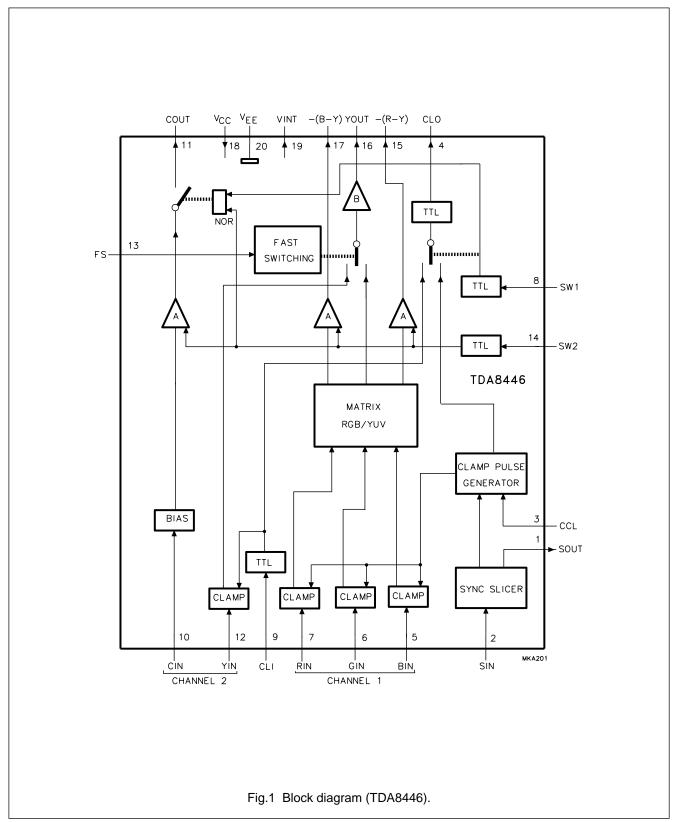

The TDA8446 is a video switch which has been designed for use in Digital Multistandard System Decoders (DMSD) in digital video system. The device is intended for matrixing incoming RGB signals and for switching between luminance signals. It generates a SYNC signal and TTL clamping pulses from any video signal with sync pulses.

| SYMBOL           | PARAMETER                     | MIN. | TYP. | MAX. | UNIT |

|------------------|-------------------------------|------|------|------|------|

| V <sub>CC</sub>  | supply voltage                | 10.8 | _    | 13.2 | V    |

| T <sub>amb</sub> | operating ambient temperature | 0    | -    | +70  | °C   |

### **ORDERING INFORMATION**

| TYPE NUMBER |                          | PACKAGE                                                    |          |

|-------------|--------------------------|------------------------------------------------------------|----------|

|             | NAME DESCRIPTION VERSION |                                                            | VERSION  |

| TDA8446     | DIP20                    | plastic dual in-line package; 20 leads; (300 mil)          | SOT146-1 |

| TDA8446T    | SO28                     | plastic small outline package; 28 leads; body width 7.5 mm | SOT136-1 |

### **BLOCK DIAGRAM**

TDA8446

# TDA8446

### PINNING

| PIN             |       | N    |                                                                                                                                                                                     |  |

|-----------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SYMBOL          | DIP20 | SO28 | DESCRIPTION                                                                                                                                                                         |  |

| SOUT            | 1     | 1    | synchronization signal output; this output provides the synchronization information extracted from the incoming signal at pin 2 (SIN).                                              |  |

| SIN             | 2     | 2    | synchronization signal input; CSYNC or CVBS signal from the peri-connector                                                                                                          |  |

| CCL             | 3     | 3    | clamping capacitor connection; the clamping pulse is generated by external circuitry connected to this pin, the generated pulse clamps the RGB inputs.                              |  |

| n.c.            | _     | 4    | not connected                                                                                                                                                                       |  |

| CLO             | 4     | 5    | amping pulse output                                                                                                                                                                 |  |

| n.c.            | _     | 6    | not connected                                                                                                                                                                       |  |

| BIN             | 5     | 7    | B-signal input                                                                                                                                                                      |  |

| GIN             | 6     | 8    | G-signal input                                                                                                                                                                      |  |

| RIN             | 7     | 9    | R-signal input                                                                                                                                                                      |  |

| SW1             | 8     | 10   | clamping control signal input; this TTL signal is used to select the clamp signal, a LOW level at this input forces the circuit to output the generated clamping pulse.             |  |

| n.c.            | _     | 11   | not connected                                                                                                                                                                       |  |

| CLI             | 9     | 12   | clamping pulse input; this TTL signal indicates the black level clamping period for the ncoming Y signal (active-HIGH).                                                             |  |

| CIN             | 10    | 13   | chrominance signal input                                                                                                                                                            |  |

| COUT            | 11    | 14   | chrominance signal output                                                                                                                                                           |  |

| YIN             | 12    | 15   | luminance signal input; this input also accepts the CVBS signal                                                                                                                     |  |

| FS              | 13    | 16   | fast switching signal input; this signal is used to control fast switching of the luminance signals, a HIGH level at this input forces the circuit to output the internal Y signal. |  |

| n.c.            | _     | 17   | not connected                                                                                                                                                                       |  |

| n.c.            | _     | 18   | not connected                                                                                                                                                                       |  |

| SW2             | 14    | 19   | gain control signal input; this TTL signal is used to set the gain of the chrominance amplifiers (A), a LOW level at this input forces the gain A to 6 dB (HIGH forces to 0 dB).    |  |

| n.c.            | —     | 20   | not connected                                                                                                                                                                       |  |

| –(R-Y)          | 15    | 21   | –(R–Y) signal output                                                                                                                                                                |  |

| YOUT            | 16    | 22   | luminance signal output                                                                                                                                                             |  |

| –(B–Y)          | 17    | 23   | –(B–Y) signal output                                                                                                                                                                |  |

| n.c.            | _     | 24   | not connected                                                                                                                                                                       |  |

| n.c.            | _     | 25   | not connected                                                                                                                                                                       |  |

| V <sub>CC</sub> | 18    | 26   | positive supply voltage (+12 V)                                                                                                                                                     |  |

| VINT            | 19    | 27   | internal decoupling                                                                                                                                                                 |  |

| V <sub>EE</sub> | 20    | 28   | ground                                                                                                                                                                              |  |

TDA8446

#### 28 V<sub>EE</sub> SOUT 1 27 VINT SIN 2 U SOUT 1 20 V<sub>EE</sub> CCL 3 26 V<sub>CC</sub> 19 VINT SIN 2 25 n.c. n.c. 4 CCL 3 18 V<sub>CC</sub> CLO 5 24 n.c. CLO 4 17 –(B–Y) 23 –(B-Y) n.c. 6 16 YOUT BIN 5 BIN 7 22 YOUT TDA8446T TDA8446 GIN 6 15 –(R–Y) 21 -(R-Y) GIN 8 RIN 7 14 SW2 RIN 9 20 n.c. SW1 8 13 FS SW1 10 19 SW2 CLI 9 12 YIN n.c. [11 18 n.c. CIN [10 11 COUT 17 n.c. CLI 12 CIN 13 16 FS MKA202 COUT 14 15 YIN МКА203 Fig.2 Pin configuration (DIP20). Fig.3 Pin configuration (SO28).

### Fast RGB/YC switch for digital decoding

### TDA8446

#### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL           | PARAMETER           |      | MAX.  | UNIT |

|------------------|---------------------|------|-------|------|

| V <sub>CC</sub>  | supply voltage      | -0.3 | +14   | V    |

| VI               | input voltage       |      | +12.3 | V    |

| T <sub>stg</sub> | storage temperature | -55  | +125  | °C   |

#### HANDLING

Each pin will withstand the ESD test in accordance with MIL-STD-883C class 2 (2000 V to 2999 V). Method 3015 (Human body model: R = 1500  $\Omega$ ; C = 100 pF) 3 pulses positive and 3 pulses negative on each pin as a function of ground. The IC will withstand 500 V in accordance with UZW-BO/FQ-B302 (Machine model: R = 0  $\Omega$ ; C = 200 pF; L = 2.5  $\mu$ H) 3 pulses positive and 3 pulses negative.

### **OPERATING CHARACTERISTICS**

| SYMBOL                                                                              | PARAMETER                           | MIN. | TYP. | MAX.            | UNIT |

|-------------------------------------------------------------------------------------|-------------------------------------|------|------|-----------------|------|

| Supply/tempe                                                                        | rature                              |      | ·    | ·               |      |

| V <sub>CC</sub>                                                                     | supply voltage                      | 10.8 | -    | 13.2            | V    |

| T <sub>amb</sub>                                                                    | operating ambient temperature       | 0    | _    | +70             | °C   |

| TTL inputs (S                                                                       | W1, SW2 and CLI)                    |      |      |                 |      |

| V <sub>IH</sub>                                                                     | HIGH level input voltage            | 2    | _    | V <sub>CC</sub> | V    |

| V <sub>IL</sub>                                                                     | LOW level input voltage             | -0.3 | _    | +0.8            | V    |

| SYNC signal (                                                                       | (SIN)                               |      |      |                 | 1    |

| V <sub>S(p-p)</sub>                                                                 | sync amplitude (peak-to-peak value) | 0.2  | -    | 2.5             | V    |

| Fast Switchin                                                                       | g input (FS)                        |      |      |                 |      |

| V <sub>IH</sub>                                                                     | HIGH level input voltage            | 1    | _    | 3               | V    |

| V <sub>IL</sub>                                                                     | LOW level input voltage             | 0    | -    | 0.4             | V    |

| Video inputs                                                                        | (RIN, GIN, BIN, CIN, YIN)           |      |      |                 |      |

| V <sub>i(p-p)</sub> video amplitude on RIN, GIN and BIN inputs (peak-to-peak value) |                                     | -    | 0.7  | 1               | V    |

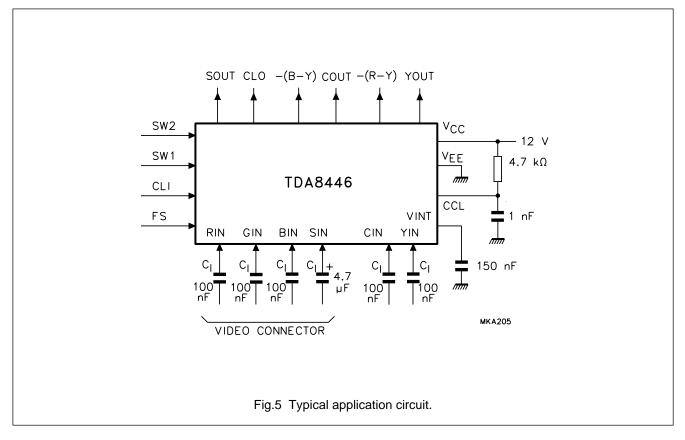

| Cl                                                                                  | C <sub>1</sub> input capacitance    |      | 100  | -               | nF   |

| Clamping puls                                                                       | se generator (CCL)                  | i    | -    |                 |      |

| R <sub>clamp</sub>                                                                  | clamping resistance                 | _    | 4.7  | -               | kΩ   |

| C <sub>clamp</sub>                                                                  | clamping capacitance                | -    | 1    | -               | nF   |

### TDA8446

### CHARACTERISTICS

$V_{CC}$  = 12 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| Supply<br>I <sub>CC</sub><br>SVRR<br>Y and R, G | supply current<br>supply voltage rejection ratio                                                                                              |                                                                     |      |      |      |    |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|------|------|----|

| SVRR                                            |                                                                                                                                               |                                                                     |      |      |      |    |

|                                                 | supply voltage rejection ratio                                                                                                                | supply current                                                      |      | -    | 75   | mA |

| Y and R, G                                      | cappiy voltage rejection rate                                                                                                                 | note 1                                                              | 30   | -    | _    | dB |

|                                                 | , B channels                                                                                                                                  |                                                                     |      |      |      |    |

| I <sub>CL</sub>                                 | input clamping current                                                                                                                        | V <sub>CC</sub> = 6 V; V <sub>I</sub> = 0 V                         | 0.3  | _    | -    | mA |

| l <sub>l</sub>                                  | input current                                                                                                                                 | V <sub>I</sub> = 9 V                                                | -1.5 | +0.5 | +1.5 | μA |

| G <sub>A</sub>                                  | gain of amplifier A                                                                                                                           | f <sub>i</sub> = 1 MHz; V <sub>SW2</sub> = 2 V                      | -1   | 0    | +1   | dB |

|                                                 |                                                                                                                                               | f <sub>i</sub> = 1 MHz; V <sub>SW2</sub> = 0.8 V                    | 5    | 6    | 7    | dB |

| G <sub>B</sub>                                  | gain of amplifier B                                                                                                                           | f <sub>i</sub> = 1 MHz                                              | -1   | 0    | +1   | dB |

|                                                 | RGB matrixed according to the following equations:   Y = $0.30R + 0.59G + 0.11B$ R-Y = $0.70R - 0.59G - 0.11B$ B-Y = $-0.30R - 0.59G + 0.89B$ |                                                                     |      |      |      |    |

| $\Delta G_{diff}$                               | relative gain difference                                                                                                                      | note 2                                                              | -    | 0    | 10   | %  |

| ΔG                                              | maximum gain variation                                                                                                                        | 100 kHz < f <sub>i</sub> < 8 MHz                                    | -    | 3    | _    | dB |

| R <sub>O</sub>                                  | output resistance                                                                                                                             |                                                                     | _    | 15   | _    | Ω  |

| Δt                                              | time difference at output                                                                                                                     | f <sub>i</sub> = 1 MHz; note 3                                      | _    | _    | 25   | ns |

| Vo                                              | DC output level                                                                                                                               | $V_{CCL} = 6 V$                                                     | _    | 4.2  | _    | V  |

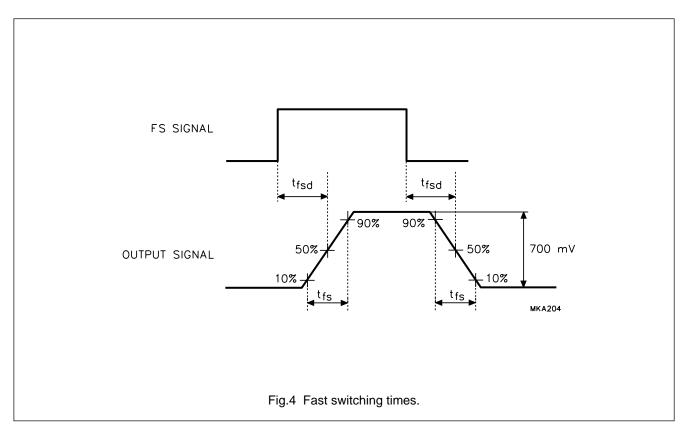

| t <sub>fsd</sub>                                | fast switching delay                                                                                                                          | see Fig.4                                                           | _    | 20   | _    | ns |

| t <sub>fs</sub>                                 | fast switching time                                                                                                                           | see Fig.4                                                           | _    | 10   | _    | ns |

| I <sub>IFS</sub>                                | input current on fast switching                                                                                                               | $V_{I} = 0.4 V$                                                     | -    | 0.7  | -    | μA |

| control (pin 13)                                |                                                                                                                                               | V <sub>I</sub> = 1 V                                                | _    | 0.5  | _    | μA |

| Chrominar                                       | nce channel (CIN, COUT)                                                                                                                       | -                                                                   | •    | •    |      | -  |

| R <sub>i</sub>                                  | internal input resistance                                                                                                                     |                                                                     | _    | 50   | -    | kΩ |

| Vo                                              | DC output level                                                                                                                               | $I_I = 0$                                                           | -    | 5    | _    | V  |

| G <sub>A</sub>                                  | gain of amplifier A                                                                                                                           | f <sub>i</sub> = 1 MHz; V <sub>SW1</sub> = V <sub>SW2</sub> = 2 V   | -1   | 0    | +1   | dB |

|                                                 |                                                                                                                                               | f <sub>i</sub> = 1 MHz; V <sub>SW2</sub> = 0.8 V                    | 5    | 6    | 7    | dB |

| ∆G                                              | maximum gain variation                                                                                                                        | 100 kHz < f <sub>i</sub> < 8 MHz                                    | -    | 3    | _    | dB |

| $\alpha_{off}$                                  | isolation (off state)                                                                                                                         | f <sub>i</sub> = 5 MHz; V <sub>SW1</sub> = V <sub>SW2</sub> = 0.8 V | _    | 60   | _    | dB |

| Zo                                              | output impedance                                                                                                                              | $V_{SW1} = V_{SW2} = 0.8 V$                                         | 100  | -    | _    | kΩ |

| Ro                                              | output resistance                                                                                                                             |                                                                     | -    | 7    | -    | Ω  |

| TTL inputs                                      | (SW1, SW2, CLI)                                                                                                                               |                                                                     |      |      |      | -  |

| IIH                                             | HIGH level input current                                                                                                                      | V <sub>IH</sub> = 2 V                                               | -    | -    | 10   | μA |

| IIL                                             | LOW level input current                                                                                                                       | V <sub>IL</sub> = 0.8 V                                             | _    | _    | -600 | μA |

### TDA8446

| SYMBOL                         | PARAMETER                                | CONDITIONS              | MIN. | TYP. | MAX. | UNIT |  |

|--------------------------------|------------------------------------------|-------------------------|------|------|------|------|--|

| Clamp outp                     | Clamp output (CLO)                       |                         |      |      |      |      |  |

| V <sub>OL</sub>                | LOW level output voltage                 | I <sub>OL</sub> = 2 mA  | -    | _    | 0.4  | V    |  |

| V <sub>OH</sub>                | HIGH level output voltage                | I <sub>OH</sub> = 10 μA | 2.4  | _    | _    | V    |  |

| Synchronization channel (SOUT) |                                          |                         |      |      |      |      |  |

| V <sub>o(p-p)</sub>            | output amplitude<br>(peak-to-peak value) |                         | 0.2  | -    | 1.5  | V    |  |

Notes

- 1. Supply voltage rejection ratio =  $20\log \frac{V_{R(CC)}}{V_{R(O)}}$

- 2. The relative gain difference is measured when only one input signal (R, G or B) is present.

- 3. The inputs RIN, GIN and BIN are interconnected; ∆t is the maximum time coincidence error between the luminance and the chrominance signals.

### APPLICATION INFORMATION

### TDA8446

OUTLINE

VERSION

SOT146-1

IEC

EIAJ

SC603

EUROPEAN PROJECTION

$\square$

ISSUE DATE

<del>92-11-17</del> 95-05-24

REFERENCES

JEDEC

# Fast RGB/YC switch for digital decoding

### PACKAGE OUTLINES

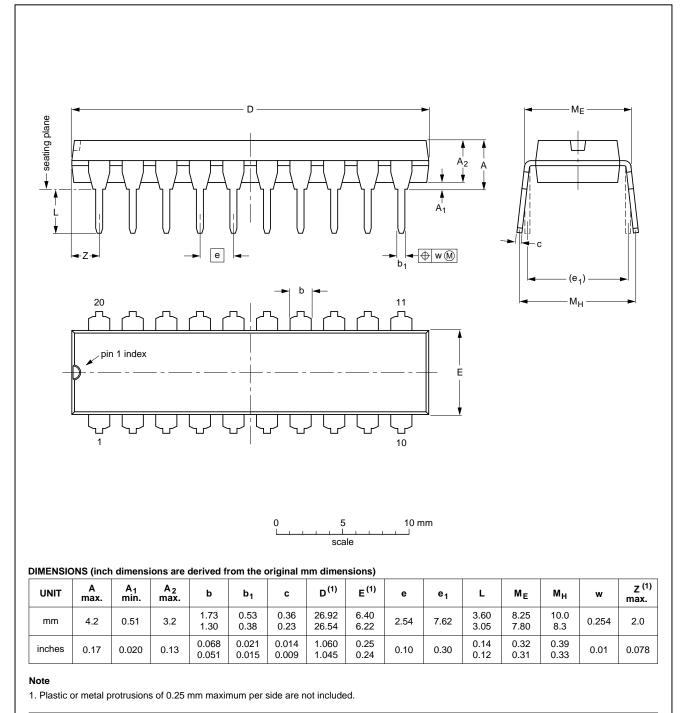

DIP20: plastic dual in-line package; 20 leads (300 mil)

**TDA8446**

SOT146-1

#### SO28: plastic small outline package; 28 leads; body width 7.5 mm SOT136-1 D Α X v = v 🕅 A HE Z 28 15 Q A<sub>2</sub> A.1 pin 1 index Π 14 Г detail X ⊕ w M e bp 0 5 10 mm scale DIMENSIONS (inch dimensions are derived from the original mm dimensions) Α z<sup>(1)</sup> D<sup>(1)</sup> E<sup>(1)</sup> UNIT A<sub>1</sub> $A_2$ A<sub>3</sub> bp С е ${\sf H}_{\sf E}$ L Lp Q ۷ w у θ max. 0.30 2.45 0.49 0.32 10.65 0.9 18.1 7.6 1.1 1.1 mm 2.65 0.25 0.25 0.25 1.27 1.4 0.1 2.25 7.4 0.4 0.10 0.36 0.23 17.7 10.00 0.4 1.0 8° 00 0.035 0.012 0.013 0.043 0.043 0.096 0.019 0.71 0.30 0.42 inches 0.10 0.055 0.01 0.01 0.004 0.01 0.050 0.39 0.016 0.016 0.004 0.089 0.014 0.009 0.69 0.29 0.039 Note 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included. REFERENCES EUROPEAN OUTLINE ISSUE DATE VERSION PROJECTION IEC JEDEC EIAJ 91-08-13 $\square$ SOT136-1 075E06 MS-013AE 95-01-24

TDA8446

### TDA8446

### SOLDERING

#### Plastic dual in-line packages

#### BY DIP OR WAVE

The maximum permissible temperature of the solder is 260 °C; this temperature must not be in contact with the joint for more than 5 s. The total contact time of successive solder waves must not exceed 5 s.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified storage maximum. If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### REPAIRING SOLDERED JOINTS

Apply a low voltage soldering iron below the seating plane (or not more than 2 mm above it). If its temperature is below 300 °C, it must not be in contact for more than 10 s; if between 300 and 400 °C, for not more than 5 s.

#### Plastic small outline packages

#### BY WAVE

During placement and before soldering, the component must be fixed with a droplet of adhesive. After curing the adhesive, the component can be soldered. The adhesive can be applied by screen printing, pin transfer or syringe dispensing.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder bath is 10 s, if allowed to cool to less than 150 °C within 6 s. Typical dwell time is 4 s at 250 °C.

A modified wave soldering technique is recommended using two solder waves (dual-wave), in which a turbulent wave with high upward pressure is followed by a smooth laminar wave. Using a mildly-activated flux eliminates the need for removal of corrosive residues in most applications.

#### BY SOLDER PASTE REFLOW

Reflow soldering requires the solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the substrate by screen printing, stencilling or pressure-syringe dispensing before device placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt, infrared, and vapour-phase reflow. Dwell times vary between 50 and 300 s according to method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 min at 45  $^\circ$ C.

REPAIRING SOLDERED JOINTS (BY HAND-HELD SOLDERING IRON OR PULSE-HEATED SOLDER TOOL)

Fix the component by first soldering two, diagonally opposite, end pins. Apply the heating tool to the flat part of the pin only. Contact time must be limited to 10 s at up to  $300 \,^{\circ}$ C. When using proper tools, all other pins can be soldered in one operation within 2 to 5 s at between 270 and 320  $^{\circ}$ C. (Pulse-heated soldering is not recommended for SO packages.)

For pulse-heated solder tool (resistance) soldering of VSO packages, solder is applied to the substrate by dipping or by an extra thick tin/lead plating before package placement.59+

### TDA8446

### DEFINITIONS

| Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                     |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|

| Objective specification                                                                                                                                                                                                                                                                                                                                                                                                                                   | ctive specification This data sheet contains target or goal specifications for product development. |  |  |  |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later.               |  |  |  |

| Product specification                                                                                                                                                                                                                                                                                                                                                                                                                                     | This data sheet contains final product specifications.                                              |  |  |  |

| Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                     |  |  |  |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. |                                                                                                     |  |  |  |

| Application information                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                     |  |  |  |

Where application information is given, it is advisory and does not form part of the specification.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.