INTEGRATED CIRCUITS

Product specification Supersedes data of 1995 Feb 01 File under Integrated Circuits, IC02 1996 Dec 12

### TDA8000; TDA8000T

#### FEATURES

- Two protected I/O lines

- V<sub>CC</sub> regulation (5 V ±4%, 100 mA max. with controlled rise and fall times)

- V<sub>PP</sub> generation (12.5, 15 or 21 V ±2.5%, 50 mA max. programmable by two bits, with controlled rise and fall times)

- Clock generation (up to 8 MHz)

- · Short-circuit, thermal and card extraction protections

- Two voltage supervisors (digital and analog supplies)

- Automatic activation and deactivation sequences via an independent internal clock

- Enhanced ESD protections on card connections (4 kV min.)

- ISO 7816 approval.

#### APPLICATIONS

- Pay TV

- Telematics

- · Cashless payment

- Multipurpose card-readers, etc.

#### **GENERAL DESCRIPTION**

The TDA8000 is a complete, low-cost analog interface which can be positioned between a smart card or a memory card (ISO 7816) and a microcontroller. It is approved for banking, telecom and pay TV applications.

The complete supply, protection and control functions are realized with only a few external components, which makes the TDA8000 very attractive for consumer applications. Application suggestions and support is available on request (see examples in Chapter "Application information").

| SYMBOL                             | PARAMETER                              | CONDITIONS                                         | MIN. | TYP. | MAX. | UNIT |

|------------------------------------|----------------------------------------|----------------------------------------------------|------|------|------|------|

| V <sub>DD</sub>                    | supply voltage                         |                                                    | 6.7  | -    | 18   | V    |

| I <sub>DD</sub>                    | supply current                         | idle mode; V <sub>DD</sub> = 12 V                  | -    | 25   | -    | mA   |

|                                    |                                        | active modes; unloaded                             | -    | 32   | -    | mA   |

| V <sub>th2</sub>                   | threshold voltage on V <sub>SUP</sub>  |                                                    | 4.5  | -    | 4.68 | V    |

| V <sub>CC</sub>                    | card supply voltage                    |                                                    | 4.8  | 5.0  | 5.2  | V    |

| I <sub>CC</sub>                    | card supply current                    |                                                    | -    | -    | -100 | mA   |

| V <sub>H</sub>                     | high voltage supply for $V_{PP}$       |                                                    | -    | -    | 30   | V    |

| I <sub>PP</sub>                    | programming current                    | read mode; V <sub>PP</sub> = 5 V                   | -    | -    | -50  | mA   |

|                                    |                                        | write mode; V <sub>PP</sub> > 5 V                  | -    | -    | -50  | mA   |

| t <sub>de</sub> , t <sub>act</sub> | deactivation/activation cycle duration |                                                    | -    | -    | 500  | μs   |

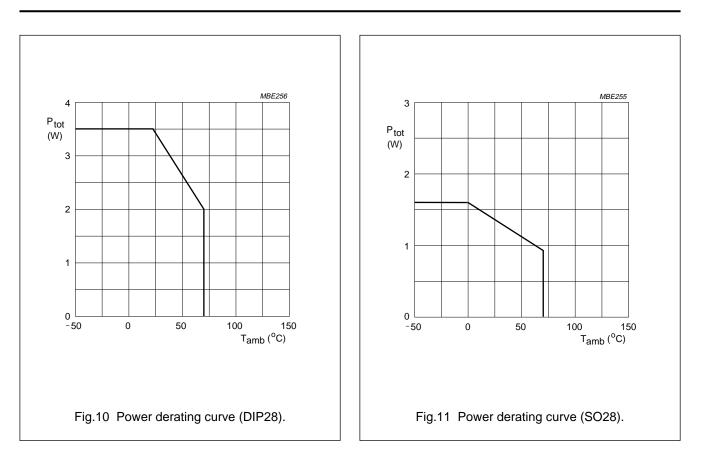

| P <sub>tot</sub>                   | continuous total power dissipation     | TDA8000; T <sub>amb</sub> = +70 °C;<br>see Fig.10  | _    | -    | 2    | W    |

|                                    |                                        | TDA8000T; T <sub>amb</sub> = +70 °C;<br>see Fig.11 | -    | -    | 0.92 | W    |

| T <sub>amb</sub>                   | operating ambient temperature          |                                                    | 0    | -    | +70  | °C   |

#### QUICK REFERENCE DATA

#### ORDERING INFORMATION

| TYPE        |       | PACKAGE                                                    |          |  |  |

|-------------|-------|------------------------------------------------------------|----------|--|--|

| NUMBER NAME |       | DESCRIPTION                                                | VERSION  |  |  |

| TDA8000     | DIP28 | plastic dual in-line package; 28 leads (600 mil)           | SOT117-1 |  |  |

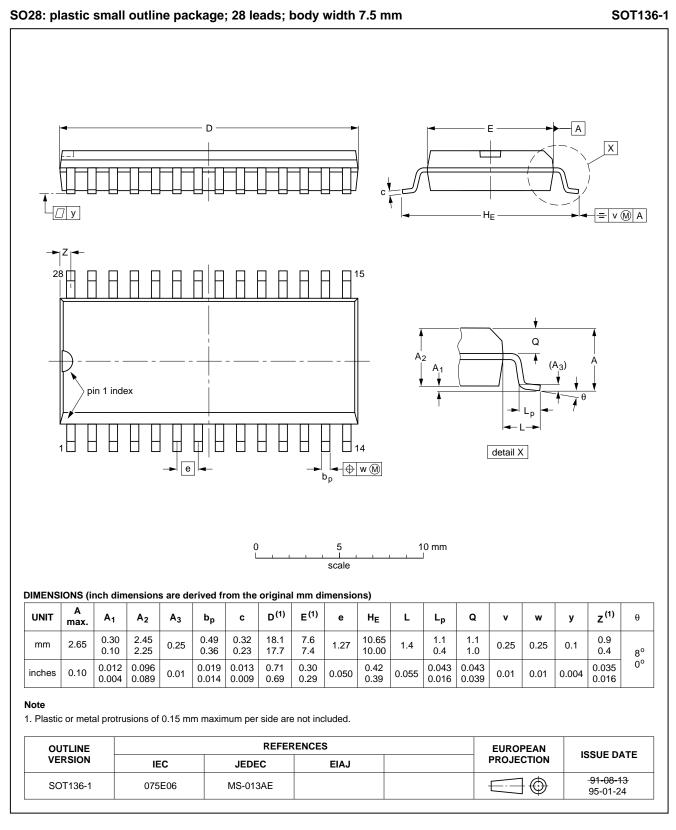

| TDA8000T    | SO28  | plastic small outline package; 28 leads; body width 7.5 mm | SOT136-1 |  |  |

# TDA8000; TDA8000T

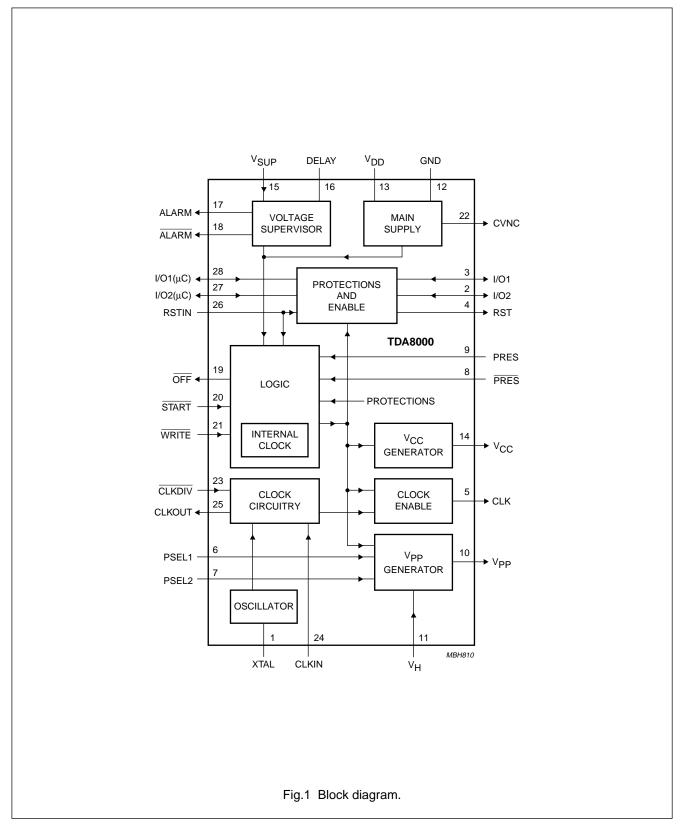

#### **BLOCK DIAGRAM**

TDA8000; TDA8000T

### Smart card interface

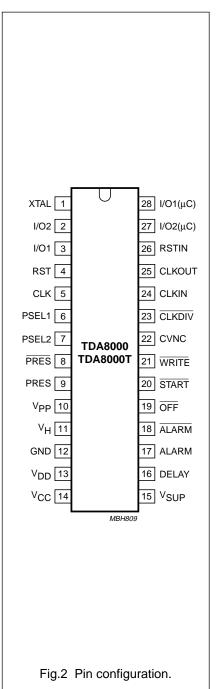

#### PINNING

| SYMBOL           | PIN | DESCRIPTION                                                                                                |

|------------------|-----|------------------------------------------------------------------------------------------------------------|

| XTAL             | 1   | crystal connection                                                                                         |

| I/O2             | 2   | data line to/from the card                                                                                 |

| I/O1             | 3   | data line to/from the card                                                                                 |

| RST              | 4   | card reset output                                                                                          |

| CLK              | 5   | clock output to the card                                                                                   |

| PSEL1            | 6   | programming voltage selection input (see Table 1)                                                          |

| PSEL2            | 7   | programming voltage selection input (see Table 1)                                                          |

| PRES             | 8   | card presence contact input (active LOW)                                                                   |

| PRES             | 9   | card presence contact input (active HIGH)                                                                  |

| V <sub>PP</sub>  | 10  | card programming voltage output                                                                            |

| V <sub>H</sub>   | 11  | high voltage supply for V <sub>PP</sub> generation                                                         |

| GND              | 12  | ground                                                                                                     |

| V <sub>DD</sub>  | 13  | positive supply voltage                                                                                    |

| V <sub>CC</sub>  | 14  | card supply output voltage                                                                                 |

| V <sub>SUP</sub> | 15  | voltage supervisor input                                                                                   |

| DELAY            | 16  | external capacitor connection for delayed reset timing                                                     |

| ALARM            | 17  | open-collector reset output for the microcontroller (active HIGH)                                          |

| ALARM            | 18  | open-collector reset output for the microcontroller (active LOW)                                           |

| OFF              | 19  | interrupt output to the microcontroller (active LOW)                                                       |

| START            | 20  | microcontroller input for starting session (active LOW)                                                    |

| WRITE            | 21  | control input for applying programming voltage to the card (active LOW)                                    |

| CVNC             | 22  | internally generated 5 V reference, present when V <sub>DD</sub> is on; to be decoupled externally (47 nF) |

| CLKDIV           | 23  | input for dividing/not dividing the CLKOUT frequency by two (active LOW)                                   |

| CLKIN            | 24  | external clock signal input                                                                                |

| CLKOUT           | 25  | clock output to the microcontroller, or another TDA8000                                                    |

| RSTIN            | 26  | card reset input from the microcontroller (active HIGH)                                                    |

| I/O2(μC)         | 27  | data line to/from the microcontroller; must not be left<br>open-circuit, tie to CVNC if not used           |

| I/O1(μC)         | 28  | data line to/from the microcontroller; must not be left open-circuit, tie to CVNC if not used              |

### TDA8000; TDA8000T

#### FUNCTIONAL DESCRIPTION

#### **Power supply**

The circuit operates within a supply voltage range of 6.7 to 18 V.  $V_{DD}$  and GND are the supply pins. All card contacts remain inactive during power-up or power-down, provided  $V_{DD}$  does not rise or fall too fast (0.5 V/ms typ.).

#### POWER-UP

The logic part is powered first and is in the reset condition until V<sub>DD</sub> reaches V<sub>th1</sub>. The sequencer is blocked until V<sub>DD</sub> reaches V<sub>th4</sub> + V<sub>hys4</sub>.

#### POWER-DOWN

When  $V_{DD}$  falls below  $V_{th4}$ , an automatic deactivation of the contacts is performed.

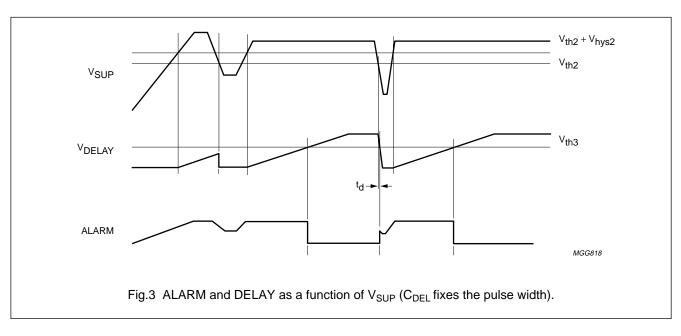

#### Voltage supervisor

This block surveys the 5 V supply of the microcontroller  $(V_{SUP})$  in order to deliver a defined reset pulse and to avoid any transients on card contacts during power-up or power-down of V<sub>SUP</sub>.

The voltage supervisor remains active even if  $V_{\text{DD}}\xspace$  is powered-down.

#### POWER-UP

As long as  $V_{SUP}$  is below  $V_{th2} + V_{hys2}$  the capacitor  $C_{DEL}$ , connected to the pin DELAY, will be discharged. When  $V_{SUP}$  rises to the threshold level,  $C_{DEL}$  will be recharged. ALARM and ALARM remain active, and the sequencer is blocked until the voltage on the pin DELAY reaches  $V_{th3}$ .

#### POWER-DOWN (see Fig.3)

If  $V_{\underline{SUP}}$  falls below  $V_{th2}$ ,  $C_{DEL}$  will be discharged, ALARM and ALARM become active, and an automatic deactivation of the contacts is performed.

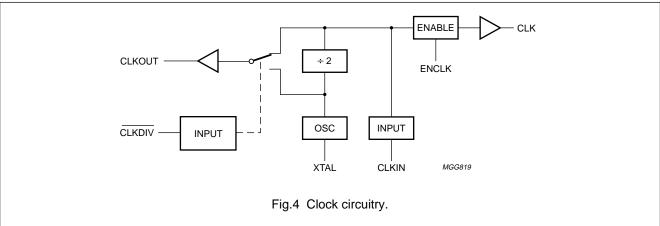

#### Clock circuitry (see Fig.4)

The clock signal (CLK) can be applied to the card by two different methods:

- Generation by a crystal oscillator: the crystal (3 to 11 MHz) is connected to pin XTAL. Its frequency is divided by two.

- 2. Use of a signal frequency already present in the system and connected to the pin CLKIN (up to 8 MHz). Pin XTAL has to be connected to GND via a 1 k $\Omega$  resistor. In this event, the CLKOUT signal remains LOW.

In both events the signal is buffered and enabled.

Pin CLKOUT may be used to clock a microcontroller. The signal ( $\frac{1}{2}f_{xtal}$  or  $f_{xtal}$  if CLKDIV is HIGH) is available when the circuit is powered up.

#### State diagram

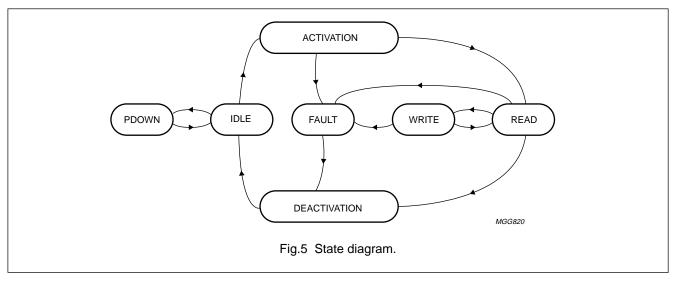

Once activated, the circuit has six possible modes of operation:

- Idle

- Activation

- Read

- Write

- Deactivation

- Fault.

Figure 5 shows how these modes are accessible.

#### IDLE MODE

After reset, the circuit enters the IDLE state. A minimum number of circuits are active while waiting for the microcontroller to start a session:

- All card contacts are inactive

- Voltage generators are stopped

- Oscillator is running, providing CLKOUT

- Voltage supervisor is active

- Pins I/O1( $\mu$ C) and I/O2( $\mu$ C) are high impedance.

The  $\overline{\text{OFF}}$  line is HIGH if a card is present (PRES and PRES active) and LOW if a card is not present.

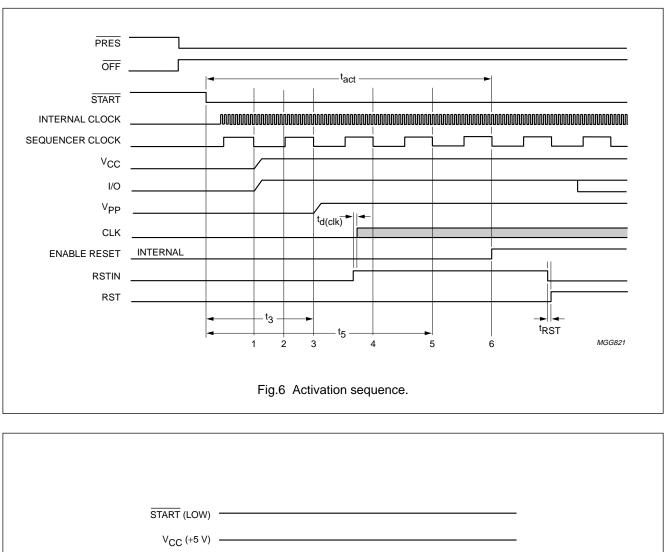

#### ACTIVATION SEQUENCE

From the IDLE mode, the circuit enters the ACTIVATION mode when the microcontroller sets the START line (active LOW). The I/O( $\mu$ C) signals must not be LOW. The internal circuitry is activated, the internal clock starts and the following ISO 7816 sequence is performed:

- 1.  $V_{CC}$  rises from 0 to 5 V

- 2. I/Os are enabled

- 3.  $V_{PP}$  rises from 0 to 5 V

- 4. No change

- 5. CLK is enabled

- 6. RST is enabled.

The typical time interval between two steps is  $32 \ \mu s$  for the first two steps and  $64 \ \mu s$  for the other three. Timing is derived from the internal clock (see Fig.6).

TDA8000; TDA8000T

Between steps 3 and 5, a HIGH level on pin RSTIN allows the CLK signal to be applied to the card. This feature facilitates a precise count of CLK periods while waiting for the card to respond to a reset.

After step 5, RSTIN has no further action on CLK.

After step 6, RST is set to the complementary value of RSTIN.

#### READ MODE

When the activation sequence is completed and, after the card has replied to its Answer-to-Reset, theTDA8000 enters the READ mode. Data is exchanged between the card and the microcontroller via the I/O lines.

When it is required to write to the internal memory of the card, the circuit is set to the WRITE mode by the microcontroller.

Cards with EPROM memory require a programming voltage (V<sub>PP</sub>).

#### V<sub>PP</sub> GENERATION

The circuit supports cards with  $V_{PP}$  of 12.5, 15 or 21 V. The selection of P is achieved by PSEL1 and PSEL2 according to Table 1.

| Table 1 | Card programming voltage selection |

|---------|------------------------------------|

|---------|------------------------------------|

| PSEL1 | PSEL2 | PROGRAMMING<br>VOLTAGE P |

|-------|-------|--------------------------|

| LOW   | LOW   | 5                        |

| LOW   | HIGH  | 12.5                     |

| HIGH  | LOW   | 15                       |

| HIGH  | HIGH  | 21                       |

In order to respect the ISO7816 slopes, the circuit generates V<sub>PP</sub> by charging and discharging an internal capacitor. The voltage on this capacitor is then amplified by a power stage gain of 5, powered via an external supply pin V<sub>H</sub> [30 V (max.)].

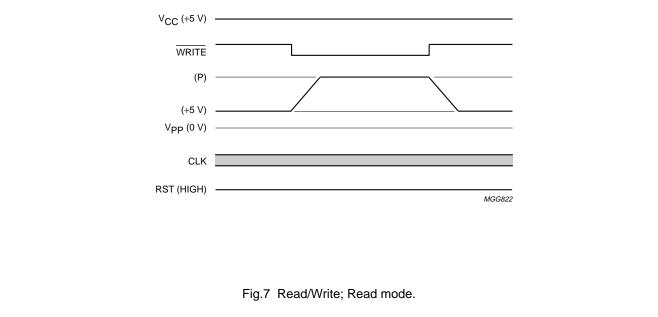

#### WRITE MODE (see Fig.7)

When the microcontroller sets the  $\overline{\text{WRITE}}$  line (active LOW), the circuit enters the WRITE mode. V<sub>PP</sub> rises from 5 V to the selected value with a typical slew rate of 1 V/µs. When the write operation is completed, the microcontroller returns the  $\overline{\text{WRITE}}$  line to its HIGH state, and V<sub>PP</sub> falls back to 5 V with the same slew rate.

WRITE has no action outside a session.

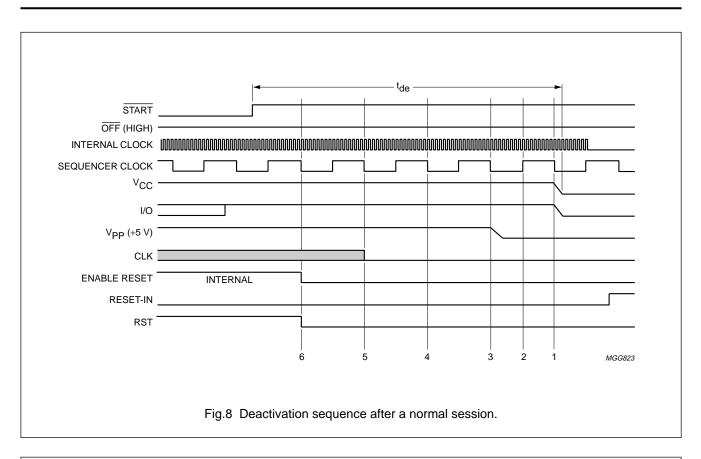

DEACTIVATION SEQUENCE (see Fig.8)

When the session is completed, the microcontroller sets the  $\overline{\text{START}}$  line to its HIGH state.

The circuit then executes an automatic deactivation sequence by counting back the sequencer:

- 1. Card reset (RST falls to LOW)

- 2. CLK is stopped

- 3. No change

- 4. V<sub>PP</sub> falls to 0 V

- 5. I/O1( $\mu$ C) and I/O2( $\mu$ C) become high impedance

- 6. V<sub>CC</sub> falls to 0 V.

The circuit returns to the IDLE mode on the next rising edge of the sequencer clock.

#### PROTECTIONS

Main fault conditions are monitored by the circuit:

- Short-circuit on V<sub>CC</sub>

- Short-circuit on V<sub>PP</sub>

- Over current on I/Os

- Card extraction during transaction

- Overheating problem.

When one of these fault conditions is detected, the circuit pulls the interrupt line  $\overline{\text{OFF}}$  to its active LOW state and returns to the FAULT mode.

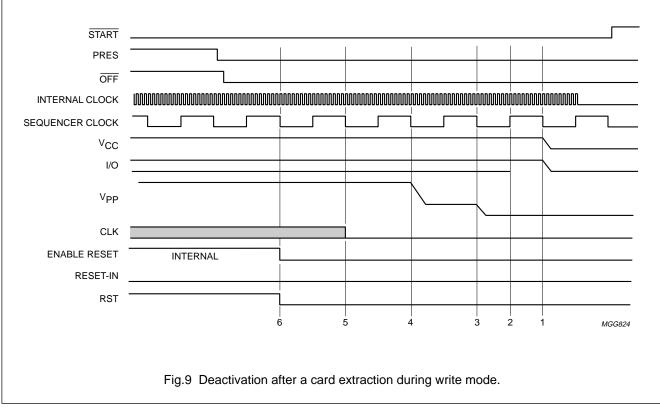

FAULT MODE (see Fig.9)

When a fault condition is written to the microcontroller via the  $\overline{\text{OFF}}$  line, the circuit initiates a deactivation sequence.

After the deactivation sequence has been completed, the  $\overline{OFF}$  line is reset to its HIGH state when the microcontroller has reset the  $\overline{START}$  line HIGH, except if the fault condition was due to a card extraction.

#### Note

The two other causes of emergency deactivation (Power failure detected on  $V_{DD}$  or  $V_{SUP}$ ) do not act upon  $\overline{OFF}$ .

### TDA8000; TDA8000T

#### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL           | PARAMETER                                                                                 | CONDITIONS                                                 | MIN. | MAX.             | UNIT |

|------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------|------|------------------|------|

| V <sub>DD</sub>  | supply voltage                                                                            |                                                            | -0.3 | +18              | V    |

| V <sub>x1</sub>  | voltage on pins PSEL1, PSEL2, PRES,<br>PRES, WRITE, START, OFF,<br>ALARM and RSTIN        |                                                            | -0.3 | V <sub>DD</sub>  | V    |

| V <sub>H</sub>   | voltage on pin V <sub>H</sub>                                                             |                                                            | -0.3 | +30              | V    |

| V <sub>PP</sub>  | voltage on pin V <sub>PP</sub>                                                            |                                                            | -0.3 | V <sub>H</sub>   | V    |

| V <sub>SUP</sub> | voltage on pin V <sub>SUP</sub>                                                           |                                                            | -0.3 | +12              | V    |

| V <sub>x2</sub>  | voltage on pins ALARM and DELAY                                                           |                                                            | -0.3 | V <sub>SUP</sub> | V    |

| V <sub>x3</sub>  | voltage on pins XTAL, I/O1(μC), I/O2(μC),<br>CLKIN, CLKOUT, CLKDIV and CVNC               |                                                            | -0.3 | +6.0             | V    |

| $V_{x4}$         | voltage on pins I/O1, I/O2, RST, CLK and $V_{CC}$                                         | duration < 1 ms                                            | -0.3 | +7.0             | V    |

| P <sub>tot</sub> | continuous total power dissipation                                                        | TDA8000; T <sub>amb</sub> = +70 °C;<br>note 1; see Fig.10  | _    | 2                | W    |

|                  |                                                                                           | TDA8000T; T <sub>amb</sub> = +70 °C;<br>note 1; see Fig.11 | _    | 0.92             | W    |

| T <sub>stg</sub> | storage temperature                                                                       |                                                            | -55  | +150             | °C   |

| V <sub>es</sub>  | electrostatic voltage on pins I/O1, I/O2, V <sub>CC</sub> , V <sub>PP</sub> , RST and CLK |                                                            | -4   | +4               | kV   |

|                  | electrostatic voltage on other pins                                                       |                                                            | -2   | +2               | kV   |

#### Note

1.  $P_{tot} = V_{DD} \times (I_{DD(unloaded)} + \Sigma I_{signals}) + I_{CC} \times (V_{DD} - V_{CC}) + max.\{(V_H - V_{PP}) \times I_{PP(read)} + (V_H - V_{PP}) \times I_{PP(write)}\} + V_H \times I_{H(unloaded)} + V_{SUP} \times I_{SUP} + (V_{DD} - CVNC) \times I_{CVNC}.$

Where 'signals' means all signal pins used, excluding the supply pins.

## TDA8000; TDA8000T

#### HANDLING

Each pin withstands the ESD test according to MIL-STD-883C class 3 for card contacts, class 2 for the remaining. Method 3015 (HBM 1500  $\Omega$ , 100 pF) 3 pulses positive and 3 pulses negative; on each pin referenced to ground.

#### THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER                                               | VALUE | UNIT |

|---------------------|---------------------------------------------------------|-------|------|

| R <sub>th j-a</sub> | thermal resistance from junction to ambient in free air |       |      |

|                     | SOT117-1                                                | 30    | K/W  |

|                     | SOT136-1                                                | 70    | K/W  |

# TDA8000; TDA8000T

### CHARACTERISTICS

$V_{DD} = 12 \text{ V}; \text{ } V_{H} = 25 \text{ V}; \text{ } V_{SUP} = 5 \text{ V}; \text{ } f_{xtal} = 7.16 \text{ MHz or } f_{CLKIN} = 3.58 \text{ MHz}; \text{ } T_{amb} = 25 \text{ }^{\circ}\text{C}; \text{ } \text{ unless otherwise specified}.$

| SYMBOL             | PARAMETER                                       | CONDITIONS                          | MIN.                 | TYP. | MAX. | UNIT |

|--------------------|-------------------------------------------------|-------------------------------------|----------------------|------|------|------|

| Supply             |                                                 |                                     |                      | -1   |      |      |

| V <sub>DD</sub>    | supply voltage                                  |                                     | 6.7                  | -    | 18   | V    |

| I <sub>DD</sub>    | supply current                                  | idle mode; V <sub>DD</sub> = 8 V    | 16                   | 22   | 30   | mA   |

|                    |                                                 | idle mode; V <sub>DD</sub> = 18 V   | 20                   | 28   | 36   | mA   |

|                    |                                                 | active mode; unloaded               | 26                   | 32   | 38   | mA   |

| V <sub>th1</sub>   | threshold voltage for power-on reset            |                                     | 1.5                  | 3.0  | 4.0  | V    |

| V <sub>th4</sub>   | threshold voltage on V <sub>DD</sub> (falling)  |                                     | 6.0                  | -    | 6.5  | V    |

| V <sub>hys4</sub>  | hysteresis on V <sub>th4</sub>                  |                                     | 50                   | -    | 200  | mV   |

| Voltage su         | upervisor                                       |                                     |                      | ·    | 1    |      |

| V <sub>SUP</sub>   | supply voltage for the supervisor               |                                     | -                    | 5    | -    | V    |

| I <sub>SUP</sub>   | input current on V <sub>SUP</sub>               |                                     | _                    | 1.6  | 2    | mA   |

| V <sub>th2</sub>   | threshold voltage on V <sub>SUP</sub> (falling) |                                     | 4.5                  | -    | 4.68 | V    |

| V <sub>hys2</sub>  | hysteresis on V <sub>th2</sub>                  |                                     | 10                   | -    | 80   | mV   |

| V <sub>th3</sub>   | threshold voltage on DELAY                      |                                     | 2.35                 | -    | 2.65 | V    |

| I <sub>DEL</sub>   | output current on DELAY                         | pin grounded (charge)               | -4                   | -    | -2.5 | μA   |

|                    |                                                 | V <sub>DEL</sub> = 4 V (discharge)  | 6                    | -    | _    | mA   |

| V <sub>DEL</sub>   | voltage on pin DELAY                            |                                     | _                    | _    | 3.5  | V    |

| ALARM, Ā           | LARM (open-collector outputs)                   |                                     |                      |      |      |      |

| I <sub>OH</sub>    | HIGH level output current on pin                | V <sub>OH</sub> = 5 V               | -                    | -    | 25   | μA   |

| V <sub>OL</sub>    | LOW level output voltage on pin                 | I <sub>OL</sub> = 2 mA              | _                    | -    | 0.4  | V    |

| I <sub>OL</sub>    | LOW level output current on pin<br>ALARM        | V <sub>OL</sub> = 0 V               | -                    | -    | -25  | μA   |

| V <sub>OH</sub>    | HIGH level output voltage on pin<br>ALARM       | $I_{OH} = -2 \text{ mA}$            | V <sub>SUP</sub> – 1 | -    | -    | V    |

| t <sub>d</sub>     | delay between V <sub>SUP</sub> and ALARM        | C <sub>DEL</sub> = 47 nF; see Fig.3 | -                    | _    | 10   | μs   |

| t <sub>pulse</sub> | ALARM pulse width                               | C <sub>DEL</sub> = 47 nF            | 30                   | -    | 65   | ms   |

| Interrupt I        | ine OFF (open-collector)                        |                                     |                      |      |      |      |

| I <sub>OH</sub>    | HIGH level output current                       | V <sub>OH</sub> = 5 V               | -                    | _    | 25   | μA   |

| V <sub>OL</sub>    | LOW level output voltage                        | I <sub>OL</sub> = 1 mA              | -                    | _    | 0.4  | V    |

| Logic inpu         | uts (RSTIN, START, WRITE, CLKDI                 | , PSEL1, PSEL2, PRES,               | PRES); note          | e 1  |      |      |

| V <sub>IL</sub>    | LOW level input voltage                         |                                     | -                    | _    | 0.8  | V    |

| V <sub>IH</sub>    | HIGH level input voltage                        |                                     | 1.5                  | _    | _    | V    |

| IIL                | LOW level input current                         | V <sub>IL</sub> = 0 V               | -                    | _    | -20  | μA   |

| I <sub>IH</sub>    | HIGH level input current                        | V <sub>IH</sub> = 5 V               | _                    | _    | 20   | μA   |

| SYMBOL           | PARAMETER                          | CONDITIONS                                              | MIN.                    | TYP.  | MAX.                    | UNIT |

|------------------|------------------------------------|---------------------------------------------------------|-------------------------|-------|-------------------------|------|

| Reset out        | put to the card (RST)              |                                                         | 1                       | Į     | 1                       | 1    |

| VIDLE            | output voltage in IDLE mode        |                                                         | _                       | _     | 0.4                     | V    |

| V <sub>OL</sub>  | LOW level output voltage           | I <sub>OL</sub> = 200 μA                                | _                       | _     | 0.45                    | V    |

| V <sub>OH</sub>  | HIGH level output voltage          | I <sub>OH</sub> = -200 μA                               | 4.0                     | _     | V <sub>CC</sub>         | V    |

|                  |                                    | I <sub>OH</sub> = -10 μA                                | V <sub>CC</sub> – 0.7   | _     | V <sub>CC</sub>         | V    |

| t <sub>RST</sub> | delay between RSTIN and RST        | RST enabled; see Fig.6                                  | _                       | _     | 2                       | μs   |

| t <sub>r</sub>   | rise time                          | C <sub>L</sub> = 330 pF                                 | -                       | -     | 1                       | μs   |

| t <sub>f</sub>   | fall time                          | C <sub>L</sub> = 330 pF                                 | _                       | _     | 1                       | μs   |

| Clock out        | put to card (CLK)                  |                                                         | ł                       |       |                         |      |

| VIDLE            | output voltage in IDLE mode        |                                                         | _                       | _     | 0.4                     | V    |

| V <sub>OL</sub>  | LOW level output voltage           | I <sub>OL</sub> = 200 μA                                | _                       | _     | 0.4                     | V    |

| V <sub>OH</sub>  | HIGH level output voltage          | I <sub>OH</sub> = -200 μA                               | 2.4                     | _     | V <sub>CC</sub> + 0.3   | V    |

|                  |                                    | I <sub>OH</sub> = -20 μA                                | 0.7V <sub>CC</sub>      | _     | V <sub>CC</sub> + 0.3   | V    |

|                  |                                    | I <sub>OH</sub> = -10 μA                                | V <sub>CC</sub> – 0.7   | _     | V <sub>CC</sub> + 0.3   | V    |

| t <sub>r</sub>   | rise time                          | C <sub>L</sub> = 30 pF; note 2                          | -                       | -     | 18                      | ns   |

| t <sub>f</sub>   | fall time                          | C <sub>L</sub> = 30 pF; note 2                          | -                       | _     | 18                      | ns   |

| δ                | duty factor                        | C <sub>L</sub> = 30 pF; (XTAL or<br>CLKIN used); note 2 | 45                      | -     | 55                      | %    |

| Δδ/Δθ            | thermal drift on duty factor       | DIP and SO packages                                     | _                       | -0.07 | -                       | %/K  |

| Card prog        | ramming voltage (V <sub>PP</sub> ) | 1                                                       |                         |       |                         | •    |

| Р                | selected voltage                   | see Table 1                                             |                         |       |                         |      |

| V <sub>PP</sub>  | output voltage                     | idle mode                                               | -                       | -     | 0.4                     | V    |

|                  |                                    | read mode                                               | V <sub>CC</sub> – 4%    | _     | V <sub>CC</sub> + 4%    | V    |

|                  |                                    | write mode; I <sub>PP</sub> < 50 mA                     | P - 2.5% <sup>(3)</sup> | -     | P + 2.5% <sup>(3)</sup> | V    |

| I <sub>PP</sub>  | output current                     | read mode                                               | -                       | -     | -50                     | mA   |

|                  |                                    | write mode                                              | -                       | -     | -50                     | mA   |

|                  |                                    | write mode; V <sub>PP</sub><br>short-circuited to GND   | -                       | -     | -400                    | mA   |

| SR               | slew rate                          | up or down                                              | 0.80                    | 1.0   | 1.20                    | V/µs |

| High-volta       | age input (V <sub>H</sub> )        |                                                         |                         |       |                         |      |

| V <sub>H</sub>   | input voltage                      |                                                         | -                       | -     | 30                      | V    |

| I <sub>H</sub>   | input current at V <sub>H</sub>    | idle mode                                               | 2                       | -     | 3                       | mA   |

|                  |                                    | active mode; unloaded;<br>WRITE = 0                     |                         |       |                         |      |

|                  |                                    | P = 5 V                                                 | 3                       | _     | 7                       | mA   |

|                  |                                    | P = 12.5 V                                              | 5                       | -     | 10                      | mA   |

|                  |                                    | P = 15 V                                                | 6                       | -     | 11                      | mA   |

|                  |                                    | P = 21 V                                                | 8                       | _     | 13                      | mA   |

| $V_{H} - V_{PP}$ | voltage drop                       |                                                         | -                       | _     | 2.2                     | V    |

| SYMBOL                          | PARAMETER                      | CONDITIONS                                                        | MIN. | TYP. | MAX. | UNIT |

|---------------------------------|--------------------------------|-------------------------------------------------------------------|------|------|------|------|

| Card supp                       | bly voltage (V <sub>CC</sub> ) |                                                                   | -    |      |      | ļ    |

| V <sub>CC</sub>                 | output voltage                 | idle mode                                                         | -    | -    | 0.4  | V    |

|                                 |                                | active mode;<br>I <sub>CC</sub> < 100 mA                          | 4.80 | -    | 5.20 | V    |

| I <sub>CC</sub>                 | output current                 |                                                                   | -    | _    | -100 | mA   |

|                                 |                                | $V_{CC}$ connected to GND                                         | -    | _    | -400 | mA   |

| SR                              | slew rate                      | up or down                                                        | 0.80 | 1.0  | 1.20 | V/µs |

| 5 V refere                      | nce output (CVNC)              |                                                                   |      |      |      |      |

| V <sub>CVNC</sub>               | output voltage at CVNC         | I <sub>CVNC</sub> < –15 mA                                        | 4.5  | 5.0  | 5.5  | V    |

| Crystal co                      | onnection (XTAL)               |                                                                   | •    | •    |      |      |

| R <sub>xtal(neg)</sub>          | negative resistance at crystal | 3 MHz < f <sub>i</sub> < 11 MHz;<br>note 4                        | -    | -    | -300 | Ω    |

| V <sub>xtal</sub>               | DC voltage at crystal          |                                                                   | 3    | _    | 4    | V    |

| f <sub>xtal</sub>               | crystal resonant frequency     |                                                                   | 3    | -    | 11   | MHz  |

| External c                      | lock input (CLKIN)             |                                                                   |      | •    |      |      |

| f <sub>ext</sub>                | frequency at CLKIN             | note 2                                                            | 0    | -    | 8    | MHz  |

| V <sub>IL</sub>                 | LOW level input voltage        |                                                                   | 0    | -    | 0.8  | V    |

| V <sub>IH</sub>                 | HIGH level input voltage       |                                                                   | 1.5  | _    | 5    | V    |

| IIL                             | LOW level input current        | V <sub>IL</sub> = 0 V                                             | -    | _    | -20  | μA   |

| I <sub>IH</sub>                 | HIGH level input current       | V <sub>IH</sub> = 2 V                                             | -    | _    | 20   | μA   |

| CI                              | input capacitance              |                                                                   | -    | _    | 5    | pF   |

| Clock out                       | put (CLKOUT)                   |                                                                   |      |      |      |      |

| f <sub>CLKOUT</sub>             | frequency on CLKOUT            |                                                                   | 1    | _    | 8    | MHz  |

| V <sub>OL</sub>                 | LOW level output voltage       | I <sub>OL</sub> = 1 mA                                            | -    | -    | 0.4  | V    |

| V <sub>OH</sub>                 | HIGH level output voltage      | V <sub>OH</sub> = -200 μA                                         | 3    | -    | _    | V    |

|                                 |                                | V <sub>OH</sub> = -10 μA                                          | 4    | _    | _    | V    |

| t <sub>r</sub> , t <sub>f</sub> | rise and fall times            | C <sub>L</sub> = 30 pF; note 2                                    | -    | _    | 25   | ns   |

| δ                               | duty factor                    | $\overline{\text{CLKDIV}} = 0;$<br>C <sub>L</sub> = 30 pF; note 2 | 45   | -    | 55   | %    |

|                                 |                                | $\overline{CLKDIV} = 1;$<br>C <sub>L</sub> = 30 pF; note 2        | 40   | -    | 60   | %    |

| Δδ/Δθ                           | thermal drift on duty factor   | DIP and SO packages                                               | -    | -0.1 | _    | %/C  |

| SYMBOL                          | PARAMETER                                            | CONDITIONS                                                                                                   | MIN. | TYP. | MAX.                   | UNIT |

|---------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------------------------|------|

| Data lines                      | [ <b>Ι/Ο1, Ι/Ο2, Ι/Ο1(μC), Ι/Ο2(μC)]</b> ; note      | e 5                                                                                                          | ł    |      |                        |      |

| V <sub>OH</sub>                 | HIGH level output voltage on I/O                     | $\begin{array}{l} 4.5 < V_{SUP} < 5.5; \\ 4.5 < V_{I/O(\mu C)} < 5.5; \\ I_{OH} = -20 \; \mu A \end{array}$  | 4    | -    | V <sub>CC</sub> + 0.2  | V    |

|                                 |                                                      | $\begin{array}{l} 4.5 < V_{SUP} < 5.5; \\ 4.5 < V_{I/O(\mu C)} < 5.5; \\ I_{OH} = -200 \; \mu A \end{array}$ | 2.4  | -    | -                      | V    |

| V <sub>OL</sub>                 | LOW level output voltage on I/O                      | $I_{I/O} = 1 \text{ mA};$<br>I/O(µC) grounded                                                                | -    | -    | 65                     | mV   |

| I <sub>IL</sub>                 | LOW level input current on I/O( $\mu$ C)             | $I/O(\mu C)$ grounded;<br>$I_{I/O} = 0$                                                                      | -    | -    | -500                   | μA   |

|                                 |                                                      | I/O(μC) grounded;<br>I/O connected to V <sub>CC</sub>                                                        | -    | -    | -5                     | mA   |

| V <sub>OH</sub>                 | HIGH level output voltage on I/O(μC)                 | $4.5 < V_{I/O} < 5.5$                                                                                        | 4    | -    | V <sub>SUP</sub> + 0.2 | V    |

| V <sub>OL</sub>                 | LOW level output voltage on $I/O(\mu C)$             | $I_{I/O(\mu C)} = 1 \text{ mA};$<br>I/O grounded                                                             | -    | -    | 70                     | mV   |

| IIL                             | LOW level input current on I/O                       | I/O grounded; $I_{I/O(\mu C)} = 0$                                                                           | -    | -    | -500                   | μA   |

|                                 |                                                      | I/O grounded; I/O( $\mu$ C) connected to V <sub>SUP</sub>                                                    | -    | -    | -5                     | mA   |

| V <sub>IDLE</sub>               | voltage on I/O outside a session                     |                                                                                                              | _    | _    | 0.4                    | V    |

| Z <sub>IDLE</sub>               | impedance on I/O( $\mu$ C) outside a session         |                                                                                                              | 10   | -    | -                      | MΩ   |

| R <sub>pu</sub>                 | internal pull-up resistance between I/O and $V_{CC}$ |                                                                                                              | 17   | 20   | 23                     | kΩ   |

| t <sub>r</sub> , t <sub>f</sub> | rise and fall times                                  | $C_{i} = C_{o} = 30 \text{ pF}$                                                                              | -    | _    | 1                      | μs   |

| Protection                      | IS                                                   |                                                                                                              |      |      |                        |      |

| T <sub>sd</sub>                 | shut-down local temperature                          |                                                                                                              | _    | 135  | -                      | °C   |

| I <sub>CC(sd)</sub>             | shut-down current at V <sub>CC</sub>                 |                                                                                                              | -175 | _    | -230                   | mA   |

| I <sub>PP(sd)</sub>             | shut-down current at V <sub>PP</sub>                 |                                                                                                              | -90  | -    | -140                   | mA   |

| I <sub>I/O(sd)</sub>            | shut-down current at I/O                             | from I/O to I/O(µC)                                                                                          | 3    | -    | 5                      | mA   |

| Timing                          |                                                      |                                                                                                              |      |      | •                      |      |

| t <sub>act</sub>                | activation sequence duration                         | see Fig.6                                                                                                    | 250  | -    | 500                    | μs   |

| t <sub>de</sub>                 | deactivation sequence duration                       | see Fig.8                                                                                                    | 250  | _    | 500                    | μs   |

| t <sub>3</sub>                  | start of the window for sending<br>CLK to the card   | see Fig.6                                                                                                    | -    | -    | 140                    | μs   |

## TDA8000; TDA8000T

| SYMBOL              | PARAMETER                                                  | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|---------------------|------------------------------------------------------------|------------|------|------|------|------|

| t <sub>5</sub>      | end of the window for sending CLK to the card              | see Fig.6  | 160  | -    | _    | μs   |

| t <sub>st</sub>     | maximum pulse width on START before $V_{CC}$ starts rising |            | -    | -    | 30   | μs   |

| t <sub>d(clk)</sub> | delay between RSTIN and CLK                                | see Fig.6  | -    | _    | 2    | μs   |

Notes

1. START, WRITE, CLKDIV and PRES are active LOW; RSTIN and PRES are active HIGH.

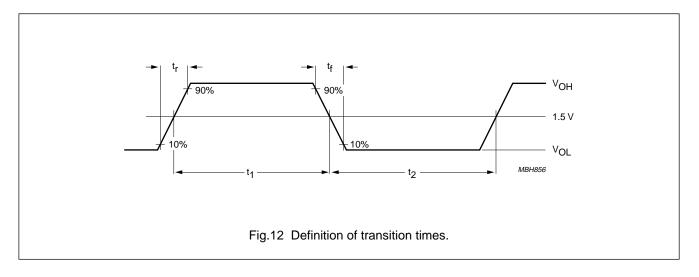

2. The transition time and duty factor definitions are shown in Fig.12;  $\delta = \frac{t_1}{t_1 + t_2}$ .

- 3. P is the card programming voltage set by pins PSEL1 and PSEL2.

- 4. This condition ensures correct start-up of the oscillator with crystals having series resistance up to 100  $\Omega$ .

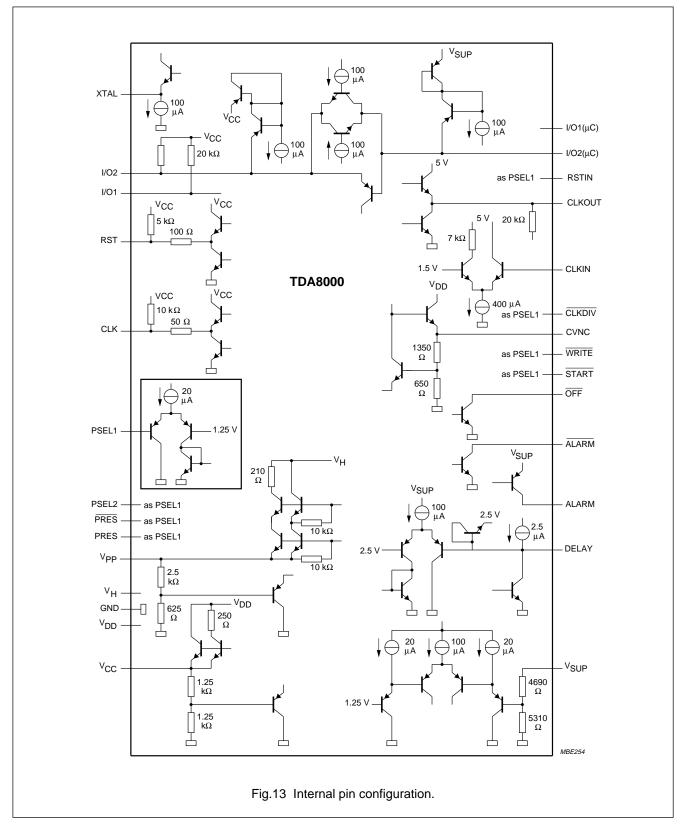

- 5. The path between I/O and I/O( $\mu$ C) is as follows (see Fig.13):

- a) Clamp to V<sub>CC</sub>.

- b) 20 k $\Omega$  pull-up resistor to V\_CC; thus V\_OH on I/O.

- c) Two opposite npn transistors with sensing pnp transistor.

- d) Clamp to  $V_{SUP};$  thus  $V_{OH}$  on I/O( $\mu C).$

- e) The base current of the npn transistor is decreasing when their collector current increases. This means the voltage drop is very low for small currents and becomes maximum for some mA. Thus V<sub>OL</sub> on I/O and I/O(μC), current limits, and high impedance feature. The output current from I/O and I/O(μC) when the line is open-circuit is the sum of the pull-up current and the base currents.

## TDA8000; TDA8000T

#### INTERNAL PIN CONFIGURATION

### TDA8000; TDA8000T

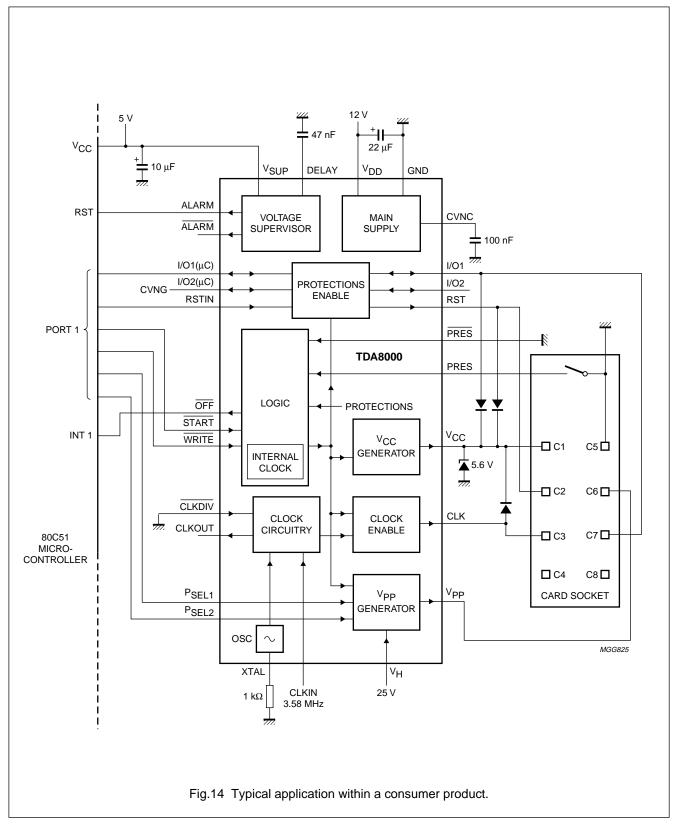

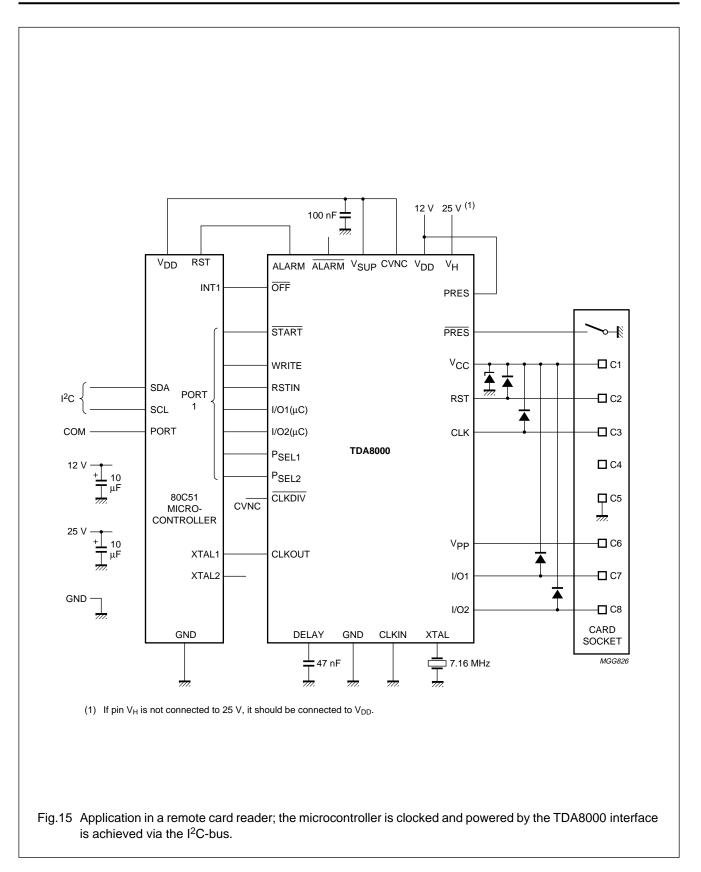

#### APPLICATION INFORMATION

TDA8000; TDA8000T

### Smart card interface

#### PACKAGE OUTLINES

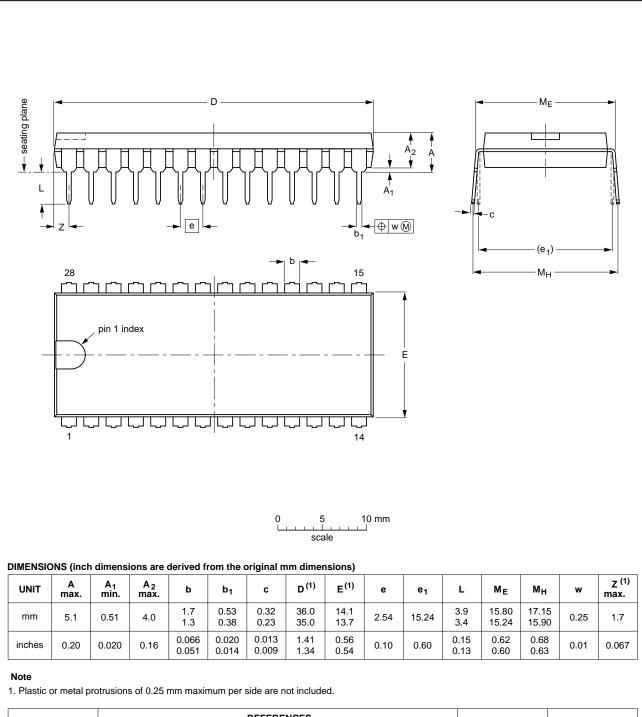

DIP28: plastic dual in-line package; 28 leads (600 mil)

| ουτ | OUTLINE<br>VERSION | REFERENCES |          |      |  | EUROPEAN       | ISSUE DATE                       |

|-----|--------------------|------------|----------|------|--|----------------|----------------------------------|

| VE  |                    | IEC        | JEDEC    | EIAJ |  | PROJECTION     | 1330E DATE                       |

| sc  | )T117-1            | 051G05     | MO-015AH |      |  | $= = \bigcirc$ | <del>-92-11-17</del><br>95-01-14 |

#### SOLDERING

#### Plastic dual in-line packages

#### BY DIP OR WAVE

The maximum permissible temperature of the solder is 260 °C; this temperature must not be in contact with the joint for more than 5 s. The total contact time of successive solder waves must not exceed 5 s.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified storage maximum. If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### REPAIRING SOLDERED JOINTS

Apply a low voltage soldering iron below the seating plane (or not more than 2 mm above it). If its temperature is below 300  $^{\circ}$ C, it must not be in contact for more than 10 s; if between 300 and 400  $^{\circ}$ C, for not more than 5 s.

#### Plastic small outline packages

#### BY WAVE

During placement and before soldering, the component must be fixed with a droplet of adhesive. After curing the adhesive, the component can be soldered. The adhesive can be applied by screen printing, pin transfer or syringe dispensing.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder bath is 10 s, if allowed to cool to less than 150 °C within 6 s. Typical dwell time is 4 s at 250 °C.

# TDA8000; TDA8000T

A modified wave soldering technique is recommended using two solder waves (dual-wave), in which a turbulent wave with high upward pressure is followed by a smooth laminar wave. Using a mildly-activated flux eliminates the need for removal of corrosive residues in most applications.

#### BY SOLDER PASTE REFLOW

Reflow soldering requires the solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the substrate by screen printing, stencilling or pressure-syringe dispensing before device placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt, infrared, and vapour-phase reflow. Dwell times vary between 50 and 300 s according to method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 min at 45  $^\circ$ C.

REPAIRING SOLDERED JOINTS (BY HAND-HELD SOLDERING IRON OR PULSE-HEATED SOLDER TOOL)

Fix the component by first soldering two, diagonally opposite, end pins. Apply the heating tool to the flat part of the pin only. Contact time must be limited to 10 s at up to  $300 \,^{\circ}$ C. When using proper tools, all other pins can be soldered in one operation within 2 to 5 s at between 270 and 320  $^{\circ}$ C. (Pulse-heated soldering is not recommended for SO packages.)

For pulse-heated solder tool (resistance) soldering of VSO packages, solder is applied to the substrate by dipping or by an extra thick tin/lead plating before package placement.

### TDA8000; TDA8000T

#### DEFINITIONS

| Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| Objective specification                                                                                                                                                                                                                                                                                                                                                                                                                                   | This data sheet contains target or goal specifications for product development.       |  |  |  |  |  |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later. |  |  |  |  |  |

| Product specification                                                                                                                                                                                                                                                                                                                                                                                                                                     | This data sheet contains final product specifications.                                |  |  |  |  |  |

| Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |  |  |  |  |  |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. |                                                                                       |  |  |  |  |  |

| Application information                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                       |  |  |  |  |  |

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.