# **SIEMENS**

### Nonvolatile Memory 1-Kbit E<sup>2</sup>PROM

**SDE 2506**

#### **Preliminary DataMOS IC**

#### **Features**

- Word-organized reprogrammable nonvolatile memory in n-channel floating-gate technology

- 128 x 8-bit organization

- 5 V supply voltage

- 3 lines processor interface for data transfer and chip control

- Data input (8 bits), address input (7 bits), control information input (1 bit) and data output are serial

- More than 10<sup>5</sup> reprogramming cycles per address

- Data retention longer than 10 years (operating temperature range)

- Unlimited number of read-out operations without refresh

- 5 ms erase/write cycle

- Extended temperature range from 40 to 110 °C

http://www.neonet.lv/autoradio E-mail:juris@mailbox.neonet.lv Email:juriss@parks.lv fax:+371 7184532 Riga , Latvia

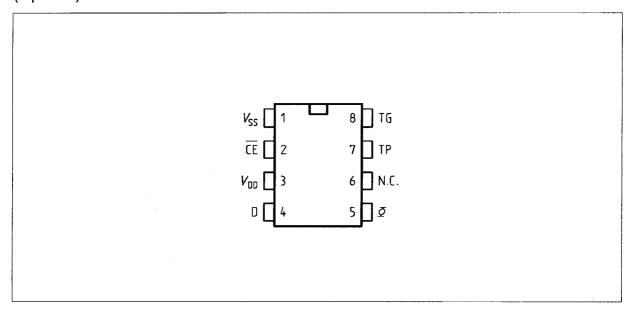

## **Pin Configurations**

(top view)

## **Pin Definitions and Functions**

| Pin | Symbol           | Function                                                                             |  |  |  |  |  |

|-----|------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| 1   | $V_{\rm SS}$     | Ground                                                                               |  |  |  |  |  |

| 2   | CE               | CE = 1 for data input/output, CE = 0 for reprogramming                               |  |  |  |  |  |

| 3   | $V_{	extsf{DD}}$ | + 5 V supply voltage                                                                 |  |  |  |  |  |

| 4   | D                | Data input/output bidirectional data line For reprogramming D = 1 erase, D = 0 write |  |  |  |  |  |

| 5   | Φ                | Clock                                                                                |  |  |  |  |  |

| 6   | N.C.             | Not connected                                                                        |  |  |  |  |  |

| 7   | TP               | Test input, at $V_{\rm SS}$                                                          |  |  |  |  |  |

| 8   | TG               | Test input, remains open                                                             |  |  |  |  |  |

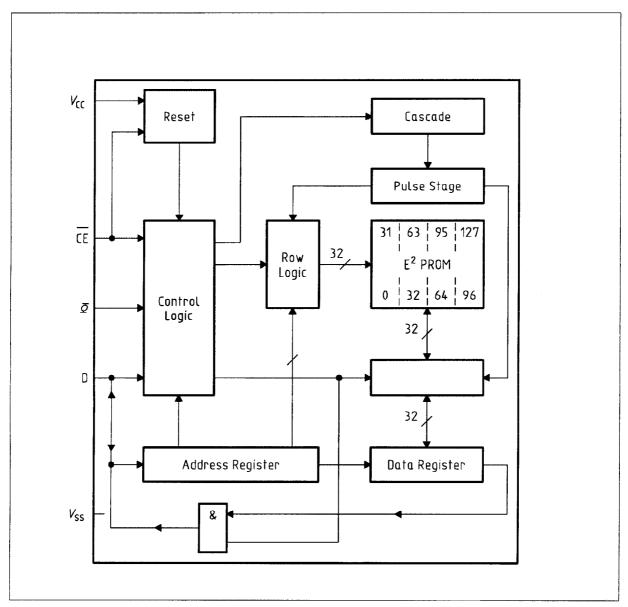

**Block Diagram**

#### **Circuit Description**

#### **Data Transfer and Chip Control**

Three lines having several functions each are required for data transfer between control processor and E<sup>2</sup>PROM memory.

- a) Data line D

- bidirectional serial data transfer

- serial address input

- clocked input of a control information

- direct control input

- b) Clock line Φ

- data input, address input and control bit input

- data output

- start read-out with takeover of data from memory in shift register or start datachange during reprogramming

- c) Chip enable line EC

- chip reset and data input (active high)

- chip enable (active low)

Prior to activating the chip, the data, address and control information is clocked in via the bidirectional data bus. These data are maintained in the shift register during reprogramming and read-out up to the second clock pulse. The following data formats have to be input:

- a) Memory read-out: one 8-bit control word, consisting of

- 7 address bits A0 to A6 (at first A0 being LSB)

- 1 control bit, SB = "0", after A6

- b) Memory reprogramming (erasure and/or writing) 16-bit input information, consisting of

- 8 bits D0 to D7 new memory information (at first D0 being LSB)

- 7 bits A0 to A6 address information (at first A0 being LSB after D7)

- 1 bit control information, SB = "1", after A6

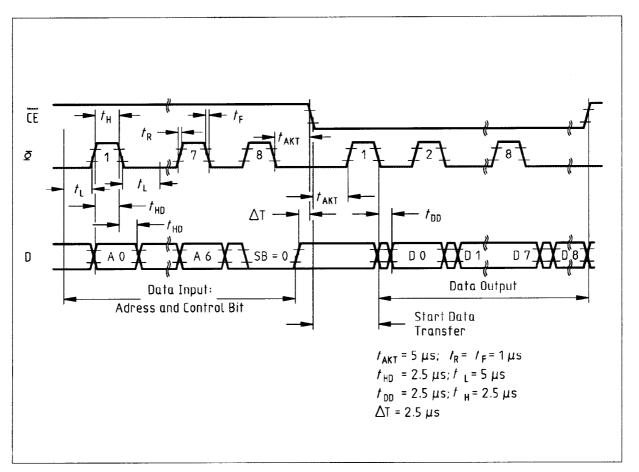

#### **Memory Read-Out**

After data input and with SB = "0" the read-out operation of the selected word address is started by the transition of  $\overline{\text{CE}}$  from "1" to "0". The information being on the data line during chip enable is of no influence.

With the first clock pulse after  $\overline{CE}$  = "0" the data word is taken over from the selected memory address into the shift register. After termination of the first  $\Phi$  pulse the data output is in the low impedance state. With every following clock pulse another data bit is pushed to the output. Through the transition of  $\overline{CE}$  from "0" to "1" the data line returns to the high impedance state.

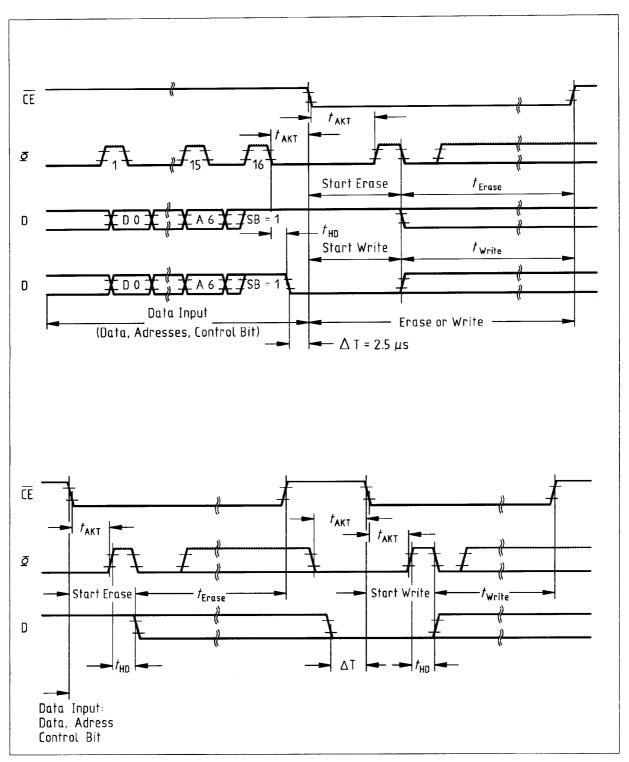

#### Reprogramming

In general, a full reprogramming operation consists of an erasure operation and a subsequent writing operation. During erase all bits of the selected word are set into the uniform "1" state, during writing "0" states are produced according to the information in the shift register.

A reprogramming operation is started when after data input and due to chip activation an information SB = "1" is in the relevant cell. Whether an erase or a writing operation is then taking place depends on the information that is on data line D during chip enable.

For erasure in state "1", a "1" must be present at the data input during transition of  $\overline{CE}$  to low. If, however, a writing process is to be started in state "0", a "0" has to be present at the data line during chip enable.

Afterwards, a start pulse at the clock input  $\Phi$  is required for the programming start. The control information has to remain stable at D until the leading edge of the start pulse is reached. The active data change starts with the trailing edge of this start pulse. The programming process is terminated by suppression of the chip enable, i.e. by  $\overline{\text{CE}}$ .

The reprogramming of a word is initiated with start and followed by an erase procedure.  $\overline{CE}$  = "1" stops erasure. The control bit SB = "1" (in the shift register), which is also necessary for the write process, remains stable even after the termination of erasure. Thus, for writing the selected word, only the data line D has to be changed from "1" to "0", the chip has to be enabled again by  $\overline{CE}$  = "0" and the data change has to be started by the start pulse.

An erase and a write process can also be executed separately. In order to obtain a safe "1" in all 8 bits of the selected memory address by the erase process, a data word is, however, to be entered with 8 times "1" before erasure. During the writing of a word which has not been erased before, the "0" states of the previous and the actual information are added.

#### **Test Mode - Total Erasure**

The test mode is activated, if the input TP (pin 7) is set from 0 V to 5 V =  $V_{\rm DD}$ . To erase the entire memory, the test mode is to be turned on and the address 0 (A0 to A6) together with the control bit SB = 1 is to be entered. The subsequent program sequence is identical to the erasure of address 0. As soon as the erase procedure has terminated due to  $\overline{\rm CE}$  changing from 0 to 1, the test mode is to be turned off.

#### **RESET**

A memory which has not been selected is automatically in reset state by state  $\overline{CE}$  = "1". All flipflops of the sequence control are reset. However, the information in the shift register is maintained and will only be changed by shifting the data. The reset state is also set in the case of the turning-on of the memory (power-on) by an on-chip circuit.

# **SIEMENS**

## **Absolute Maximum Ratings**

| Parameter                                   | Symbol                           | Lin            | Unit        |     |

|---------------------------------------------|----------------------------------|----------------|-------------|-----|

|                                             |                                  | min.           | max.        |     |

| Supply voltage<br>Input voltage             | $V_{	extsf{DD}} \ V_{	extsf{I}}$ | - 0.3<br>- 0.3 | 6           | V   |

| Power dissipation                           | $P_{D}$                          |                | 40          | mW  |

| Storage temperature<br>Junction temperature | $T_{stg} \ T_{j}$                | - 55           | 125<br>125  | °C  |

| Thermal resistance<br>system - air          | $R_{thSA}$                       |                | 100         | K/W |

| Operating Range                             |                                  |                |             |     |

| Supply voltage<br>Ambient temperature       | $V_{	extsf{DD}} \ T_{	extsf{A}}$ | 4.75<br>- 40   | 5.25<br>110 | °C  |

## Characteristics

$T_{\rm A}$  = 25 °C

| Parameter                   | Symbol           | Limit Values |      |      | Unit | Test Condition          |

|-----------------------------|------------------|--------------|------|------|------|-------------------------|

|                             |                  | min.         | typ. | max. |      |                         |

| Supply voltage              | $V_{	extsf{DD}}$ | 4.75         | 5    | 5.25 | V    |                         |

| Supply current              | I <sub>cc</sub>  |              |      | 3    | mA   | $V_{\rm DD}$ = 5.25 V   |

| Inputs                      |                  |              |      |      |      |                         |

| Input voltage<br>(D, Φ, CE) | $V_{L}$          |              |      | 0.8  | V    |                         |

| Input voltage<br>(D, Φ, CE) | $V_{H}$          | 2.4          | !    |      | V    |                         |

| Input current<br>(D, Φ, CE) | I <sub>H</sub>   |              |      | 10   | μА   | V <sub>H</sub> = 5.25 V |

# Characteristics (cont'd)

$T_{\Delta}$  = 25 °C

| Parameter                                                                                       | Symbol                                   | Limit Values |      |                | Unit                     | Test Condition                                        |

|-------------------------------------------------------------------------------------------------|------------------------------------------|--------------|------|----------------|--------------------------|-------------------------------------------------------|

|                                                                                                 |                                          | min.         | typ. | max.           |                          |                                                       |

| Data Output D<br>(open drain)                                                                   |                                          |              |      |                |                          |                                                       |

| L-output current<br>H-output current                                                            | $I_{L}$ $I_{H}$                          |              |      | 0.5<br>10      | mA<br>μA                 | $V_{\rm L} = 0.8  \rm V$<br>$V_{\rm H} = 5.25  \rm V$ |

| Clock Pulse <b>Φ</b>                                                                            |                                          |              |      |                |                          |                                                       |

| H-clock period<br>L-clock period                                                                | t <sub>H</sub> t <sub>L</sub>            | 2.5<br>5     |      | 60             | μ <b>S</b><br>μ <b>S</b> |                                                       |

| Edge spacing CE to D Edge spacing CE to Φ                                                       | $\Delta t$ $t_{AKT}$                     | 2.5<br>5     |      |                | μs<br>μs                 |                                                       |

| Data hold time (before/after $\Phi$ trailing edge) Data delay time (after $\Phi$ trailing edge) | $t_{HD}$                                 | 2.5<br>2.5   |      |                | μs<br>μs                 |                                                       |

| Rise time<br>Fall time                                                                          | t <sub>r</sub>                           |              |      | 1              | μ <b>S</b><br>μ <b>S</b> |                                                       |

| Chip erase duration Write duration Full erasure duration                                        | $t_{ m er}$ $t_{ m wr}$ $t_{ m tot  er}$ | 5<br>5<br>20 |      | 20<br>20<br>25 | ms<br>ms<br>ms           |                                                       |

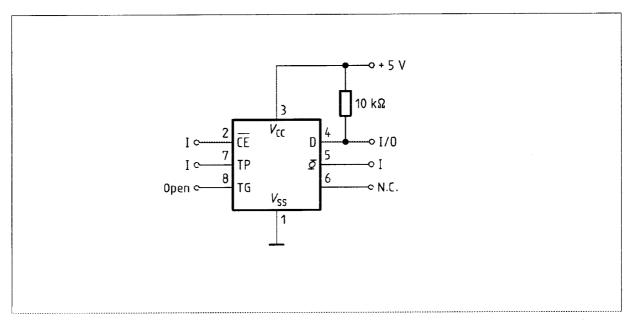

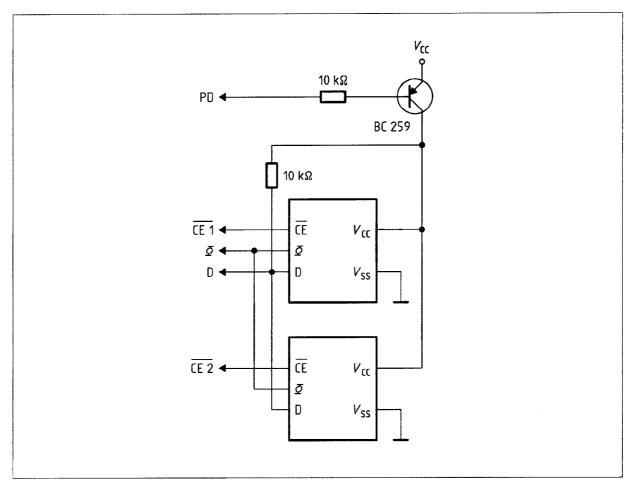

## **Test Circuit**

**Application Circuit**

Diagram Read

Diagram Reprogramming