## Advance Information

# 16K x 15 Bit Cache Tag RAM for Pentium™ Processors

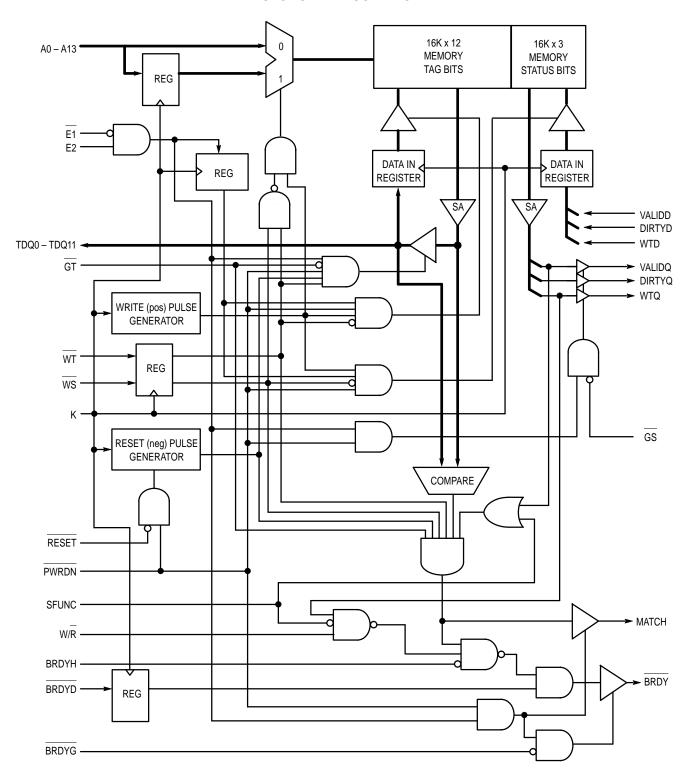

The MCM67T415 is a 245,760 bit cache—tag static RAM designed to support Pentium microprocessors at bus speeds up to 66 MHz. It is organized as 16K words of 15 bits each and is fabricated using Motorola's high performance, silicon gate BiCMOS technology. There are twelve common I/O tag bits and three separate I/O status bits. A 12—bit comparator is on—chip to allow fast comparison of the 12 stored tag bits with the current tag input data. An active high MATCH output is generated when the valid bit is true and these two groups of data are the same for a given address.

This high–speed MATCH signal, with t<sub>AVMV</sub> times as fast as 9 ns, provides the fastest possible enabling of secondary cache accesses.

The three separate I/O status bits (VALID, DIRTY, and WT) can be configured for either dedicated or generic functionality, depending on the SFUNC input pin. With SFUNC low, the status bits are defined and used internally by the device, allowing easier determination of the validity and use of the given tag data. SFUNC high releases the defined internal status bit usage and control, allowing users to configure the status bit information to fit their system needs. A synchronous RESET pin, when held low at a rising clock edge, will reset all status bits in the array for easy invalidation of all tag addresses.

The MCM67T415 also provides the option for burst ready (BRDY) generation within the cache tag itself, based upon MATCH, VALID bit, WT bit, and other external inputs provided by the user. This can significantly simplify cache controller logic and minimize cache decision time. Match and read operations are both asynchronous in order to provide the fastest access times possible, while write operations are synchronous for ease of system timing.

The MCM67T415 uses a 5 V power supply on V<sub>C</sub>C and V<sub>SS</sub>, with separate V<sub>CCQ</sub> pins provided for the outputs to offer compliance with both 5 V TTL and 3.3 V LVTTL logic levels. The PWRDN pin offers a low–power standby mode, which provides significant system power savings.

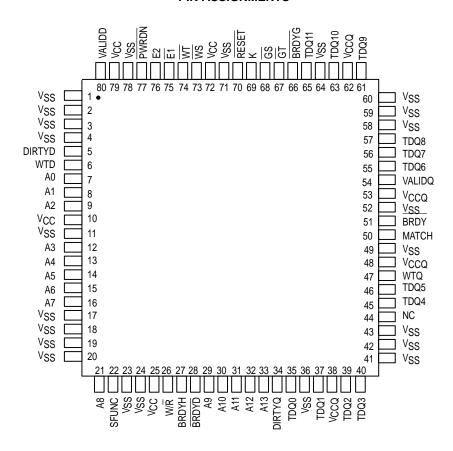

The MCM67T415 is offered in a space saving 80–pin thin quad flat pack (TQFP) package.

- 16K x 15 Configuration:

- 12 Tag Bits

- Three Status Bits (Valid, Dirty, and WT)

- Valid Bit used to Qualify Match Output

- <u>High</u>-Speed Address-to-Match Comparison Times 9/10/12 ns

- BRDY Circuitry Included Inside the Cache—Tag for the Highest Speed Operation

- Asynchronous Read/Match Operation and Synchronous Write and Reset Operation

- Separate Write Enable for Tag Bits and Status Bits

- · Separate Output Enable for Tag Bits, Status Bits, and BRDY

- Synchronous RESET Pin for Invalidation of all Tag Entries

- Dual Chip Selects for Easy Depth Expansion with No Performance Degradation

- I/O Pins Both 5 V TTL and 3.3 V LVTTL Compatible with VCCQ Pins

- PWRDN Pin to Place Device in Low-Power Mode

- Drop-In Replacement for IDT71215

- Packaged in an 80-Pin Thin Quad Flat Pack (TQFP)

Pentium is a trademark of Intel Corp.

This document contains information on a new product. Motorola reserves the right to change or discontinue this product without notice. 9/10/96

# MCM67T415

## **FUNCTIONAL BLOCK DIAGRAM**

MCM67T415 MOTOROLA FAST SRAM

#### **PIN ASSIGNMENTS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and the are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

### How to reach us:

**USA/EUROPE/Locations Not Listed:** Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 INTERNET: http://Design-NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298