# 128K x 9 Bit Separate I/O Synchronous Fast Static RAM

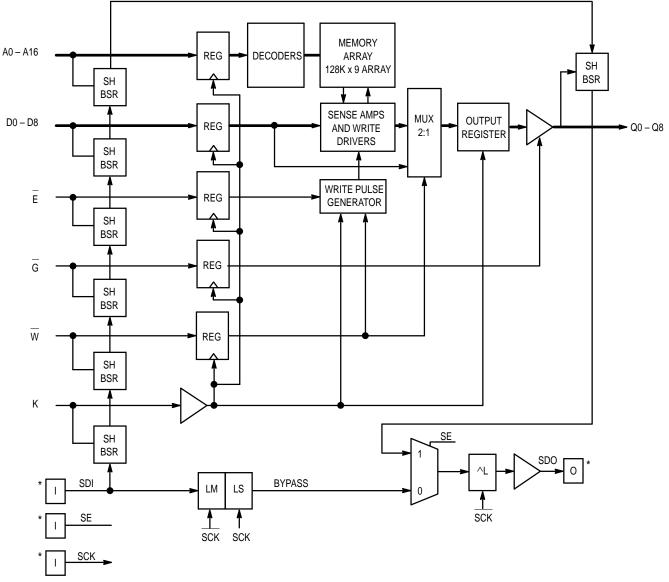

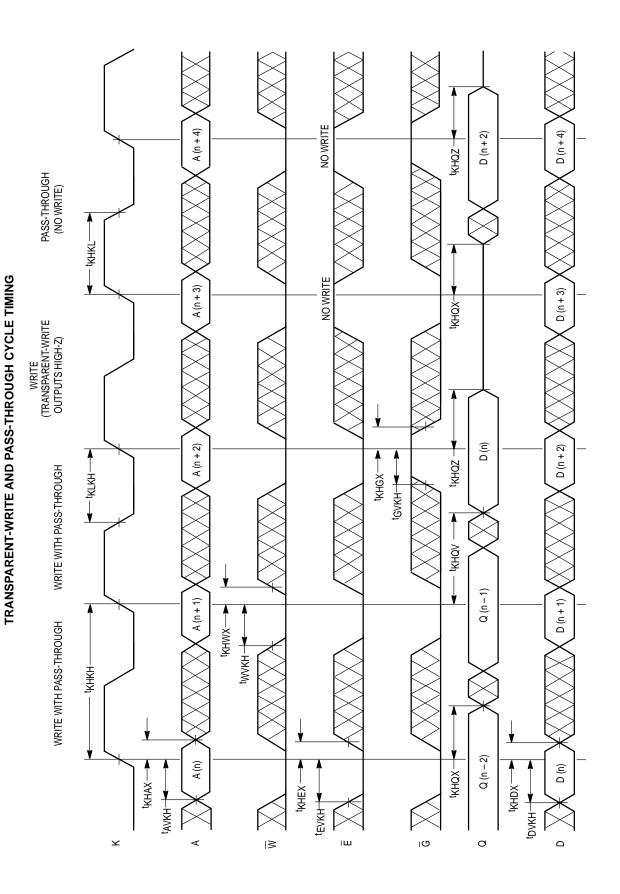

The MCM67Q709A is a 1,179,648—bit static random access memory, organized as 131,072 words of 9 bits. It features separate TTL input and output buffers, which drive 3.3 V output levels and incorporates input and output registers on–board with high speed SRAM. It also features transparent—write and data pass—through capabilities.

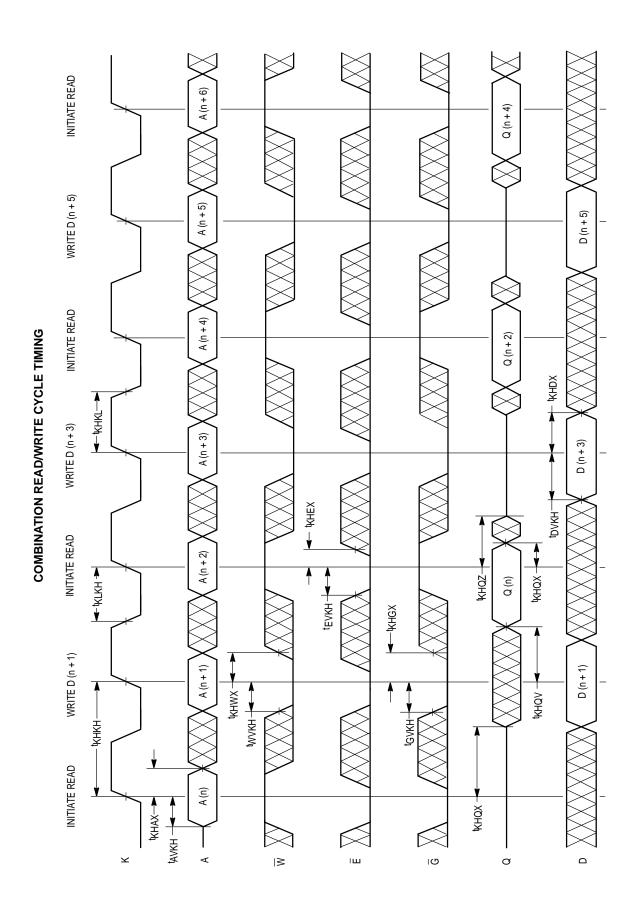

The synchronous design allows for precise cycle control with the use of an external single clock (K). The addresses (A0 - A16), data input (D0 - D8), data output (Q0 - Q8), write enable (W), chip enable (E), and output enable (G), are registered in on the <u>rising edge</u> of clock (K).

The control pins (E, W, G) function differently in comparison to most synchronous SRAMs. This device will not deselect with E high. The RAM remains active at all times. If E is registered high, the output pins (Q0 – Q8) will be driven if G is registered low. The transparent write feature allows the output data to track the input data. E, G, and W must be asserted to perform a transparent write (write and pass—through). The input data is available at the ouputs on the next rising edge of clock (K).

The pass–through function is always enabled. E high disables the write to the array while allowing a pass—through cycle to occur on the next rising edge of clock (K). Only a registered G high will three–state the outputs.

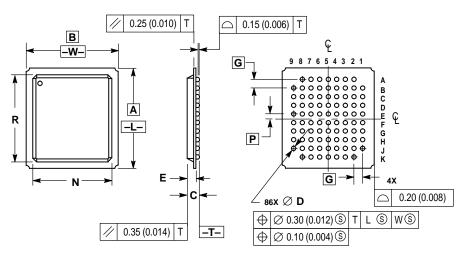

The MCM67Q709A is available in an 86–bump surface mount PBGA (Plastic Ball Grid Array) package.

- Single 5 V ± 5% Power Supply

- · Fast Cycle Time: 10 ns Max

- Single Clock Operation

- TTL Input and Output Levels (Outputs LVTTL Compatible)

- · Address, Data Input, E, W, G Registers On-Chip

- 100 MHz Maximum Clock Cycle Time

- Self-Timed Write

- Separate Data Input and Output Pins

- Transparent-Write and Pass-Through

- High Output Drive Capability: 50 pF/Output at Rated Access Time

- Boundary Scan Implementation

- PBGA Package for High Speed Operation

### **MCM67Q709A**

#### **PIN ASSIGNMENT**

|        | _ | 1                    | 2                       | 3                    | 4               | 5                    | 6                       | 7                       | 8                   | 9                  |   |

|--------|---|----------------------|-------------------------|----------------------|-----------------|----------------------|-------------------------|-------------------------|---------------------|--------------------|---|

| Α      |   |                      | Q<br>E                  | Q<br>W               | O<br>VCC        | O<br>SDI             | O<br>SDO                | O<br>A4                 | O<br>A0             |                    | \ |

| В      |   | O<br>A16             | O<br>A14                | Ω<br>G               | О<br>К          | O<br>V <sub>SS</sub> | O A6                    | O<br>A2                 | O<br>VSS            | O<br>D8            |   |

| С      |   | O<br>D7              | O<br>A15                | O<br>NC              | O<br>Vss        | $^{\circ}_{VSS}$     | $^{\circ}_{\text{VSS}}$ | $^{\circ}_{\text{VSS}}$ | ○<br><b>Q</b> 8     | °<br>Vss           |   |

| D      |   | O<br>VSS             | ○<br>Q7                 | $^{\circ}_{SS}$      | VSS             | $^{\circ}_{SS}$      | $^{\circ}_{SS}$         | $^{\circ}_{\text{VSS}}$ | ○<br><b>Q</b> 6     | D6                 |   |

| Ε      |   | ○<br><b>D5</b>       | $^{\circ}_{\text{VSS}}$ | $^{\circ}_{SS}$      | o<br>Vss        | $^{\circ}_{SS}$      | °<br>V <sub>SS</sub>    | $^{\circ}_{SS}$         | $^{\circ}_{SS}$     | $^{ m ACC}_{ m O}$ |   |

| F      |   | VCC                  | O<br>Q5                 | VSS                  | VSS             | Vss                  | O<br>Vss                | O<br>Vss                | O<br>D4             | O<br>Q4            |   |

| G      |   | O<br>D3              | O<br>Q3                 | o<br>V <sub>SS</sub> | V <sub>SS</sub> | o<br>V <sub>SS</sub> | o<br>V <sub>SS</sub>    | o<br>V <sub>SS</sub>    | O<br>D2             | O<br>Q2            |   |

| Н      |   | o<br>V <sub>SS</sub> | O<br>D1                 | O<br>NC              | $v_{SS}$        | VSS                  | VSS                     | VSS                     | O<br>D0             | °V <sub>SS</sub>   |   |

| J<br>K |   | 0<br>Q1              | O<br><b>A12</b><br>O    | O<br>A10<br>O        | ∨SS<br>○<br>SCK | O<br><b>A9</b><br>O  | A8                      | O<br><b>A5</b><br>O     | O<br><b>A1</b><br>O | O<br>Q0            |   |

| r.     |   |                      | A13                     | A11                  | SČK             | VCC                  | O<br>SE                 | Ă7                      | Ä3                  |                    | / |

TOP VIEW 86-BUMP

Not to Scale

REV 2 12/23/97

#### **BLOCK DIAGRAM**

#### NOTES:

- 1. Bypass mode is entered with SE low and SCK cycled.

- 2. SH BSR = Shadow Bypass Scan Register.

- 3. 39 bumps used in Boundary Scan. V<sub>SS</sub>, V<sub>CC</sub>, NC, SDI, SDO, SE, and SCK not used in Scan Path.

4. SDO Output Sequence A6, A4, A2, A0, D8, Q8, D6, Q6, D4, Q4, D2, Q2, D0, Q0, A1, A3, A5, A7, A8, A9, A10, A11, A12, A13, Q1, D1, Q3, D3, Q5, D5, Q7, D7, A15, A16, A14, E, G, W, K.

<sup>\*</sup> Four added test pins.

#### **TRUTH TABLE**

| E<br>(t <sub>n</sub> ) | W<br>(t <sub>n</sub> ) | G<br>(t <sub>n + 1</sub> ) | Mode                      | D0 – D8<br>(t <sub>n</sub> ) | Q0 – Q8<br>(t <sub>n + 1</sub> )   | V <sub>CC</sub><br>Current |

|------------------------|------------------------|----------------------------|---------------------------|------------------------------|------------------------------------|----------------------------|

| L                      | L                      | Ш                          | Write and<br>Pass–Through | Valid                        | D0 – D8 (t <sub>n</sub> )          | Icc                        |

|                        |                        | Н                          | Write                     | Valid                        | High–Z                             | Icc                        |

| Н                      |                        | L                          | Pass–Through              | Valid                        | D0 – D8 (t <sub>n</sub> )          | Icc                        |

| 11                     | _                      | Н                          | Pass–Through              | Don't Care                   | High–Z                             | Icc                        |

| Х                      | Н                      | L                          | Read                      | Don't Care                   | Q <sub>out</sub> (t <sub>n</sub> ) | Icc                        |

| ^                      |                        | Н                          | Read                      | Don't Care                   | High-Z                             | ICC                        |

#### ABSOLUTE MAXIMUM RATINGS (See Note)

| Rating                                                                 | Symbol                             | Value                          | Unit |

|------------------------------------------------------------------------|------------------------------------|--------------------------------|------|

| Power Supply Voltage                                                   | Vcc                                | - 0.5 to + 7.0                 | V    |

| Voltage Relative to V <sub>SS</sub> for Any Pin Except V <sub>CC</sub> | V <sub>in</sub> , V <sub>out</sub> | - 0.5 to V <sub>CC</sub> + 0.5 | V    |

| Output Current                                                         | l <sub>out</sub>                   | ± 30                           | mA   |

| Power Dissipation                                                      | PD                                 | 1.5                            | W    |

| Temperature Under Bias                                                 | T <sub>bias</sub>                  | - 10 to + 85                   | °C   |

| Operating Temperature                                                  | T <sub>A</sub>                     | 0 to + 70                      | °C   |

| Storage Temperature — Plastic                                          | T <sub>stg</sub>                   | – 55 to + 125                  | °C   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPER-ATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

This is a synchronous device. All synchronous inputs must meet specified setup and hold times with stable logic levels for *ALL* rising edges of clock (K) while the device is selected.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to these high–impedance circuits.

#### DC OPERATING CONDITIONS AND CHARACTERISTICS

$(V_{CC} = 5.0 \text{ V} \pm 5\%, T_A = 0 \text{ to} + 70^{\circ}\text{C}, \text{Unless Otherwise Noted})$

#### RECOMMENDED OPERATING CONDITIONS AND SUPPLY CURRENTS

| Parameter                                                                                                   | Symbol              | Min    | Max                     | Unit |

|-------------------------------------------------------------------------------------------------------------|---------------------|--------|-------------------------|------|

| Supply Voltage (Operating Voltage Range)                                                                    | VCC                 | 4.75   | 5.25                    | V    |

| Input High Voltage                                                                                          | VIH                 | 2.2    | V <sub>CC</sub> + 0.3** | V    |

| Input Low Voltage                                                                                           | V <sub>IL</sub>     | - 0.5* | 0.8                     | V    |

| Input Leakage Current (All Inputs, V <sub>in</sub> = 0 to V <sub>CC</sub> )                                 | l <sub>lkg(l)</sub> | _      | ± 1.0                   | μΑ   |

| Output Leakage Current (E = V <sub>IH</sub> , V <sub>Out</sub> = 0 to V <sub>CC</sub> )                     | llkg(O)             | _      | ± 1.0                   | μΑ   |

| AC Supply Current (I <sub>out</sub> = 0 mA) (V <sub>CC</sub> = max, f = f <sub>max</sub> ) MCM67Q709A-10 ns | ICCA                | _      | 230                     | mA   |

| Output Low Voltage (I <sub>OL</sub> = + 8.0 mA)                                                             | VOL                 | _      | 0.4                     | V    |

| Output High Voltage (I <sub>OH</sub> = - 4.0 mA)                                                            | Voн                 | 2.4    | 3.3                     | V    |

<sup>\*</sup>  $V_{IL}$  (min) = -0.5 V dc;  $V_{IL}$  (min) = -2.0 V ac (pulse width  $\leq 20$  ns) for  $I \leq 20.0$  mA.

#### CAPACITANCE (f = 1.0 MHz, dV = 3.0 V, T<sub>A</sub> = 25°C, Periodically Sampled Rather Than 100% Tested)

| Parameter                          | Symbol           | Max | Unit |

|------------------------------------|------------------|-----|------|

| Address and Data Input Capacitance | C <sub>in</sub>  | 6   | pF   |

| Control Pin Input Capacitance      | C <sub>in</sub>  | 6   | pF   |

| Output Capacitance                 | C <sub>out</sub> | 8   | pF   |

MOTOROLA FAST SRAM MCM67Q709A

<sup>\*\*</sup>  $V_{IH}$  (max) =  $V_{CC}$  + 0.3 V dc;  $V_{IH}$  (max) =  $V_{CC}$  + 2.0 V ac (pulse width  $\leq$  20 ns) for I  $\leq$  20.0 mA.

#### **AC OPERATING CONDITIONS AND CHARACTERISTICS**

(V<sub>CC</sub> = 5.0 V  $\pm$  5%, T<sub>A</sub> = 0 to + 70°C, Unless Otherwise Noted)

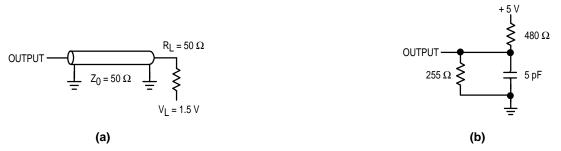

| Input Timing Measurement Reference Level 1.5 V | Output Timing Reference Level 1.5 V          |

|------------------------------------------------|----------------------------------------------|

| Input Pulse Levels 0 to 3.0 V                  | Output Load Figure 1a Unless Otherwise Noted |

| Input Rise/Fall Time                           |                                              |

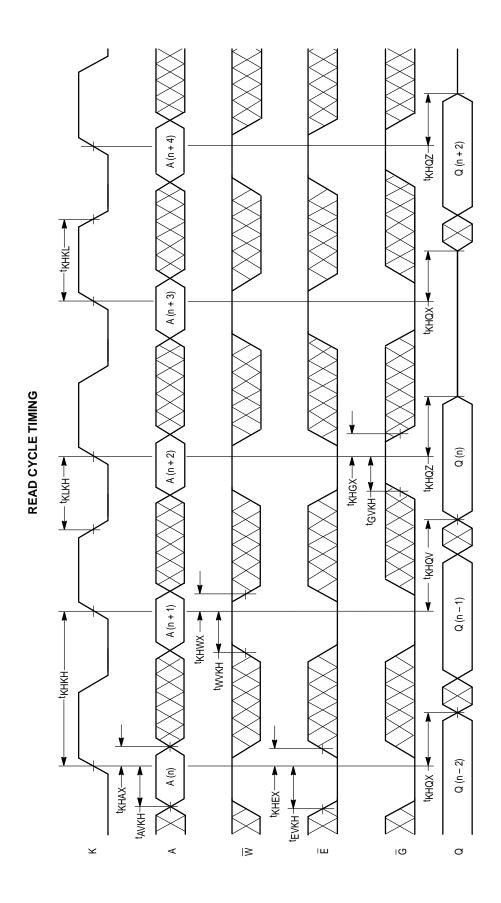

#### READ/WRITE CYCLE TIMING (See Notes 1, 2, and 3)

|                                                                          |                                                                                                       | MCM67Q | 709A-10 |      |       |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------|---------|------|-------|

| Parameter                                                                | Symbol                                                                                                | Min    | Max     | Unit | Notes |

| Cycle Time                                                               | <sup>t</sup> KHKH                                                                                     | 10     | _       | ns   | 1     |

| Clock Access Time                                                        | <sup>t</sup> KHQV                                                                                     | _      | 5       | ns   | 2     |

| Clock Low Pulse Width                                                    | <sup>t</sup> KLKH                                                                                     | 4      | _       | ns   |       |

| Clock High Pulse Width                                                   | <sup>t</sup> KHKL                                                                                     | 4      | _       | ns   |       |

| Clock High to Data Output Invalid                                        | <sup>t</sup> KHQX                                                                                     | 2      | _       | ns   |       |

| Clock High to Data Output High-Z                                         | <sup>t</sup> KHQZ                                                                                     | _      | 5       | ns   | 3     |

| Setup Times:         A           W         E           G         D0 – D8 | <sup>t</sup> AVKH<br><sup>t</sup> WVKH<br><sup>t</sup> EVKH<br><sup>t</sup> GVKH<br><sup>t</sup> DVKH | 2      | _       | ns   | 4     |

| Hold Times: A W E G D0 – D8                                              | <sup>†</sup> KHAX<br><sup>†</sup> KHWX<br><sup>†</sup> KHEX<br><sup>†</sup> KHGX<br><sup>†</sup> KHDX | 1      | _       | ns   | 4     |

#### NOTES:

- 1. All read and write cycles are referenced from K.

- 2. Valid data from Clock High will be the data stored at the address or the last valid read cycle.

- 3. Measured at  $\pm$  200 mV from steady state. Tested per High–Z Test Load (See Figure 1b).

- 4. This is a synchronous device. All synchronous inputs must meet the specified setup and hold times with stable logic levels for ALL rising edges of clock (K) while the device is selected.

Figure 1. Test Loads

MCM67Q709A

MCM67Q709A 5 MOTOROLA FAST SRAM

MOTOROLA FAST SRAM MCM67Q709A 7

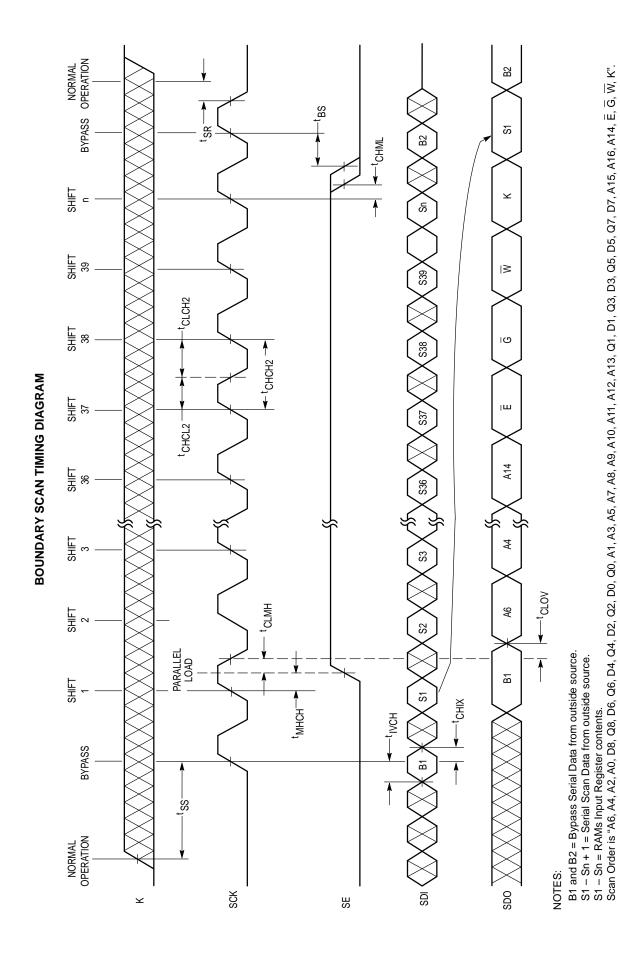

#### **BOUNDARY SCAN CYCLE TIMING**

|                              |                    | MCM67Q709A-10 |     |      |       |

|------------------------------|--------------------|---------------|-----|------|-------|

| Parameter                    | Symbol             | Min           | Max | Unit | Notes |

| Cycle Time                   | <sup>t</sup> CHCH2 | 100           | _   | ns   |       |

| Clock High Pulse Width       | <sup>t</sup> CHCL2 | 40            | _   | ns   |       |

| Clock Low Pulse Width        | <sup>t</sup> CLCH2 | 40            | _   | ns   |       |

| Scan Mode Setup Time         | tSS                | 10            | _   | ns   | 1     |

| Bypass Mode Setup Time       | t <sub>BS</sub>    | 10            | _   | ns   | 2     |

| Scan Mode Recovery Time      | t <sub>SR</sub>    | 100           | _   | ns   | 3     |

| SCK Low to SE Hold High      | <sup>t</sup> CLMH  | 10            | _   | ns   | 4     |

| SE High to SCK High Setup    | <sup>t</sup> MHCH  | 10            | _   | ns   | 5     |

| SCK High to SE Low Hold Time | <sup>t</sup> CHML  | 10            | _   | ns   | 6     |

| SDI Valid to SCK High Setup  | <sup>t</sup> IVCH  | 10            | _   | ns   |       |

| SCK High to SDI Don't Care   | tCHIX              | 10            |     | ns   |       |

| SCK Low to SDO Valid         | t <sub>CLOV</sub>  | _             | 20  | ns   |       |

#### NOTES:

- 1. The minimum delay required between ending normal operation and beginning scan operations.

- 2. The minimum delay required between ending Shift Mode and beginning Bypass Mode.

- 3. The minimum delay required before restarting normal RAM operation.

- 4. The minimum delay required before executing a Parallel Load operation.

- 5. The minimum delay required between a Parallel Load operation and a Shift.

- 6. Minimum Shift command hold time.

#### **BOUNDARY SCAN**

#### **OVERVIEW**

Boundary scan is a simple, non-intrusive scheme that allows verification of electrical continuity for each of a clocked RAMs logically active inputs and I/Os without adversely affecting RAM performance. Boundary scan allows the user to monitor the logic levels applied to each signal I/O on the RAM, and to shift them out in a serial bit stream.

#### **OPERATION**

Boundary scan requires four signal pins for implementation: Scan Data In (SDI), Scan Data Out (SDO), Scan Clock (SCK, active high), and Scan Enable (SE, active high).

Boundary scan provides three modes of operation: (1) normal RAM operation, (2) scan, and (3) bypass. For normal RAM operation, SCK and SE must be held low. The RAM will always return to normal operation immediately after the RAM receives a rising edge of the RAM input clock (K) with SCK and SE held low. To enter scan mode, SCK is activated. The first rising edge of SCK is used to latch in the data on the scan registers. SE is then driven high to disable additional input data from entering the scan registers. Every falling edge of SCK serially shifts data through the scan registers and onto the SDO pin. To enter bypass mode simply exercise SCK with SE held low. In this mode, SDI is sampled on the rising edge of SCK. The level found on SDI is then driven out on SDO on the next falling edge of SCK.

MCM67Q709A MOTOROLA FAST SRAM

MOTOROLA FAST SRAM

MCM67Q709A

9

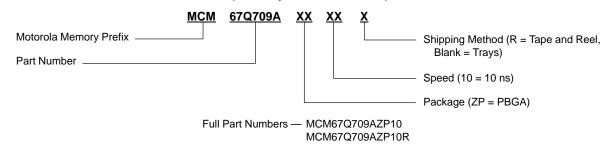

## ORDERING INFORMATION (Order by Full Part Number)

#### PACKAGE DIMENSIONS

ZP PACKAGE 86 PBGA CASE 896A-02

#### NOTES:

- DIMENSIONING AND TOLERANCING

PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER.

|     | MILLIN | IETERS | INC       | HES   |

|-----|--------|--------|-----------|-------|

| DIM | MIN    | MAX    | MIN       | MAX   |

| Α   | 17.78  | BSC    | 0.700     | BSC   |

| В   | 16.26  | BSC    | 0.640     | BSC   |

| С   | 1.84   | 2.44   | 0.073     | 0.096 |

| D   | 0.69   | 0.81   | 0.028     | 0.031 |

| Е   | 1.33   | 1.73   | 0.053     | 0.068 |

| G   | 1.524  | BSC    | 0.060 BSC |       |

| N   | 13.80  | 14.20  | 0.544     | 0.559 |

| Р   | 0.762  | BSC    | 0.030 BSC |       |

| R   | 15.29  | 15.69  | 0.602     | 0.617 |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and manufacture of the part. Motor

How to reach us

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405. Denver. Colorado. 80217. 1-303-675-2140 or 1-800-441-2447

Mfax™: RMFAX0@email.sps.mot.com - TOUCHTONE 1-602-244-6609 Motorola Fax Back System - US & Canada ONLY 1-800-774-1848

– http://sps.motorola.com/mfax/

HOME PAGE: http://motorola.com/sps/

Mfax is a trademark of Motorola, Inc.

**JAPAN**: Nippon Motorola Ltd.: SPD, Strategic Planning Office, 141, 4-32-1 Nishi-Gotanda, Shagawa-ku, Tokyo, Japan. 03-5487-8488

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

CUSTOMER FOCUS CENTER: 1-800-521-6274

MCM67Q709A/D