Order this document by MCD212/D Rev. 0

Advance Information

**MCD212**

Video Decoder and System Controller (with JTAG)

Coming through loud and clear.

How to reach us: USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 **JAPAN**: Nippon Motorola Ltd.; Tatsumi-SPD-JLDC, Toshikatsu Otsuki, 6F Seibu-Butsuryu-Center, 3–14–2 Tatsumi Koto-Ku, Tokyo 135, Japan. 03–3521–8315 MFAX: RMFAX0@email.sps.mot.com - TOUCHTONE (602) 244-6609 HONG KONG: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, INTERNET: http://Design-NET.com 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

MCD212/D

**MOTOROLA**

# MCD212: Video Decoder and System Controller TABLE OF CONTENTS

# SECTION 1 GENERAL DESCRIPTION

| 1.1 | INTRO                | DUCTION 1–                                 | 1 |  |

|-----|----------------------|--------------------------------------------|---|--|

| 1.2 | FEATURES             |                                            |   |  |

| 1.3 | BLOCK                | 【DIAGRAM1−                                 | 3 |  |

| 1.4 | DIFFER               | ENCES BETWEEN THE MCD211 AND THE MCD212 1- | 3 |  |

|     |                      | SECTION 2 PIN DESCRIPTION                  |   |  |

|     |                      |                                            |   |  |

| 2.1 |                      | DUCTION 2-                                 |   |  |

| 2.2 | PIN FUI              | NCTION DESCRIPTION 2-                      |   |  |

|     | 2.2.1                | System Interface 2-                        |   |  |

|     | 2.2.2                | Dynamic RAM Interface 2-                   | 2 |  |

|     | 2.2.3                | Video Interface 2-                         | 2 |  |

|     | 2.2.4                | JTAG Test Signals 2-                       | 3 |  |

|     | 2.2.5                | Miscellaneous Signals                      | 3 |  |

| 2.3 | PIN TYP              | PES 2                                      | 4 |  |

|     |                      | SECTION 3                                  |   |  |

|     |                      | SYSTEM CONTROL                             |   |  |

| 3.1 | RESET                | AND HALT GENERATION 3–                     | 1 |  |

| 3.2 | RESET                | MECHANISM 3-                               | 1 |  |

| 3.3 | VDSC II              | NITIALIZATION SEQUENCE 3-                  | 2 |  |

| 3.4 | MEMORY SWAPPING 3-2  |                                            |   |  |

| 3.5 | ADDRESS DECODING 3–3 |                                            |   |  |

| 3.6 | DATA A               | CKNOWLEDGE GENERATION 3-                   | 3 |  |

| 3.7 | BUS ERROR GENERATION |                                            |   |  |

| 3.8 |                      | RUPT GENERATION                            |   |  |

|     |                      |                                            |   |  |

© Motorola, Inc., 1995

# SECTION 4 DRAM CONTROL

| 4.1 | DRAM CONFIGURATION 4–1          |                |                                             |       |  |  |

|-----|---------------------------------|----------------|---------------------------------------------|-------|--|--|

| 4.2 | DRAM ACCESS AND ARBITRATION 4-2 |                |                                             |       |  |  |

| 4.3 | DRAM TIMING 4–4                 |                |                                             |       |  |  |

| 4.4 | DRAM DESELECT 4-5               |                |                                             |       |  |  |

| 4.5 | DRAM IM                         | PLEMENTA       | ATION                                       | 4–5   |  |  |

|     |                                 |                | SECTION 5                                   |       |  |  |

|     |                                 | I              | IMAGE DISPLAY CONTROL                       |       |  |  |

| 5.1 | IMAGE FO                        | ORMATS .       |                                             | 5–1   |  |  |

|     | 5.1.1                           | NTSC/PAI       | L                                           | . 5–1 |  |  |

| 5.2 | RESOLUT                         | ΓΙΟΝ           |                                             | 5–2   |  |  |

|     | 5.2.1                           | HORIZON        | ITAL RESOLUTION                             | 5–2   |  |  |

|     | 5.2.2                           | VERTICAL       | L RESOLUTION                                | 5–3   |  |  |

| 5.3 | TIMING .                        |                |                                             | 5–4   |  |  |

| 5.4 | SOFTWA                          | RE             |                                             | 5–6   |  |  |

|     | 5.4.1                           | ICA CONT       | FROL                                        | 5–6   |  |  |

|     | 5.4.2                           | DCA CON        | ITROL                                       | . 5–7 |  |  |

|     | 5.4.3                           | ICA/DCA        | INITIALIZATION                              | . 5–7 |  |  |

|     | 5.4.4                           | ICA/DCA        | INSTRUCTIONS                                | 5–8   |  |  |

|     |                                 | 5.4.4.1        | h80-hBF CLUT COLOR REGISTER 0-63            |       |  |  |

|     |                                 | 5.4.4.2        | hC0 IMAGE CODING METHOD REGISTER            | 5–11  |  |  |

|     |                                 | 5.4.4.3        | hC1 TRANSPARENCY CONTROL REGISTER           | _     |  |  |

|     |                                 | 5.4.4.4        | hC2 PLANE ORDER REGISTER                    |       |  |  |

|     |                                 | 5.4.4.5        | hC3 CLUT BANK REGISTER                      |       |  |  |

|     |                                 | 5.4.4.6        | hC4-hC6 TRANSPARENT COLOR REGISTER          |       |  |  |

|     |                                 | 5.4.4.7        | hC7-hC9 MASK COLOR REGISTER                 | 5–13  |  |  |

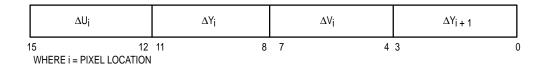

|     |                                 | 5.4.4.8        | hCA, hCB DELTA YUV ABSOLUTE START VALUE     | - 44  |  |  |

|     |                                 | <b>5</b> 4 4 0 | REGISTER                                    |       |  |  |

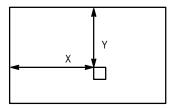

|     |                                 | 5.4.4.9        | hCD CURSOR POSITION REGISTER                |       |  |  |

|     |                                 | 5.4.4.10       | hCE CURSOR CONTROL REGISTER                 |       |  |  |

|     |                                 | 5.4.4.11       | hCF CURSOR PATTERN REGISTER                 |       |  |  |

|     |                                 | 5.4.4.12       | hC0-hD7 REGION CONTROL REGISTER 0-7         |       |  |  |

|     |                                 | 5.4.4.13       | hC8 BACKDROP COLOR REGISTER                 | _     |  |  |

|     |                                 | 5.4.4.14       | hD9, hDA MOSAIC PIXEL HOLD FACTOR REGISTER. |       |  |  |

|     |                                 | 5.4.4.15       | hDB-hDC WEIGHT FACTOR REGISTER              | 5–18  |  |  |

# SECTION 5 (continued) IMAGE DISPLAY CONTROL

| 5.5 | BITMAP .                   | 5–19                             |  |

|-----|----------------------------|----------------------------------|--|

| 5.6 | 6.6 EFFECT OF STANDARD BIT |                                  |  |

|     | 5.6.1                      | EFFECT ON VERTICAL TIMING        |  |

|     | 5.6.2                      | EFFECT ON HORIZONTAL TIMING 5–19 |  |

| 5.7 | VIDEO S                    | YNCHRONIZATION 5–20              |  |

|     |                            | SECTION 6                        |  |

|     |                            | SECTION 6 DISPLAY FILE DECODER   |  |

| 6.1 | BITMAP I                   | FILE 6–1                         |  |

| 6.2 | RUN-LEN                    | NGTH FILE 6–2                    |  |

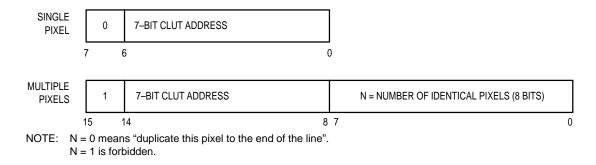

|     | 6.2.1                      | RUN-LENGTH 7-BIT CLUT FILES      |  |

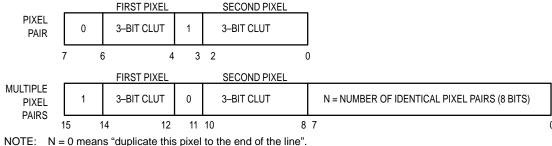

|     | 6.2.2                      | RUN-LENGTH 3-BIT CLUT FILES      |  |

| 6.3 | MOSAIC                     | FILE 6–3                         |  |

| 6.4 | PIXEL O                    | JTPUT 6–4                        |  |

|     |                            |                                  |  |

|     |                            | SECTION 7 REAL-TIME DECODER      |  |

| 7.1 | DELTA Y                    | UV DECODER 7–1                   |  |

| 7.2 | CLUT DE                    | CODER 7–3                        |  |

| 7.3 | DIRECT F                   | RGB555 7–4                       |  |

| 7.4 | DECODIN                    | NG COMBINATIONS 7–5              |  |

| 7.5 | BACKDR                     | OP 7–6                           |  |

| 7.6 | CURSOR                     | 7–6                              |  |

|     |                            |                                  |  |

|     |                            | SECTION 8 VISUAL EFFECTS         |  |

|     |                            |                                  |  |

| 8.1 | PLANES                     | 8–1                              |  |

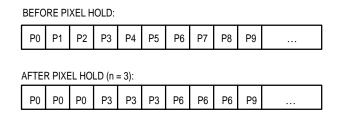

| 8.2 | PIXEL HO                   | DLD 8–1                          |  |

| 8.3 | REGIONS                    | 8-2                              |  |

| 8.4 | TRANSP                     | ARENCY 8–3                       |  |

| 8.5 | OVERLA                     | Y AND MIXING 8–3                 |  |

# SECTION 9 REGISTER DESCRIPTION

| 9.1         | REGISTER MAP 9-        |                                             |  |

|-------------|------------------------|---------------------------------------------|--|

|             | 9.1.1                  | CONTROL REGISTERS CSR1W AND CSR2W 9–2       |  |

|             | 9.1.2                  | STATUS REGISTERS CSR1R AND CSR2R 9–3        |  |

|             | 9.1.3                  | DISPLAY COMMAND REGISTERS DCR1 AND DCR2 9-4 |  |

|             | 9.1.4                  | DISPLAY DECODER REGISTERS DDR1 AND DDR2 9-6 |  |

|             | 9.1.5                  | VIDEO START REGISTERS VSR1 AND VSR2 9–7     |  |

|             | 9.1.6                  | DCA POINTERS DCP1 AND DCP2 9–8              |  |

|             |                        | SECTION 10                                  |  |

|             |                        | PIN LIST                                    |  |

| 10.1        | PIN FUNC               | TION TABLE 10–1                             |  |

| 10.2        | PIN CONFIGURATION 10-2 |                                             |  |

|             |                        | SECTION 11                                  |  |

|             |                        | ELECTRICAL SPECIFICATION                    |  |

| 11.1        | ABSOLUT                | TE MAXIMUM RATINGS 11–1                     |  |

| 11.2        | DC ELEC                | TRICAL CHARACTERISTICS11–2                  |  |

| 11.3        | AC CHAR                | ACTERISTICS 11–2                            |  |

|             |                        | SECTION 12                                  |  |

|             |                        | PACKAGE DIMENSIONS                          |  |

|             |                        | APPENDIX A                                  |  |

| <b>A.</b> 1 | DELTA VI               | JV ENCODING A-1                             |  |

| A.1<br>A.2  |                        | DDING A-1                                   |  |

| H.Z         | DELIA C                | ווטכוווע                                    |  |

## **LIST OF FIGURES**

| Fig.<br>No. | Page Title No.                                                      |

|-------------|---------------------------------------------------------------------|

| 1–1         | System Block Diagram 1–1                                            |

| 1–2         | Internal Block Diagram 1–3                                          |

| 3–1         | Reset and Halt Timing Chart 3–1                                     |

| 3–2         | CLK2 Clocking and Resetting                                         |

| 3–3         | Memory Swapping Timing Chart 3–2                                    |

| 3–4         | Bus Error Timing                                                    |

| 4–1         | DRAM Access 4–2                                                     |

| 4–2         | DRAM Cycles 4–3                                                     |

| 4–3         | DRAM Timing 4–4                                                     |

| 4–4         | DRAM Banks Validation/Devalidation 4–5                              |

| 5–1         | Four Video Planes of the Displayed Image 5–1                        |

| 5–2         | Example of Normal and Double Resolution Pixels 5–2                  |

| 5–3         | Line Display of Interlace versus Non-interlace Modes 5–3            |

| 5–4         | HSYNC and BLANK Timing                                              |

| 5–5         | VSYNC and BLANK Timing 5–4                                          |

| 5–6         | CSYNC Timing in the 50 Hz (FD = 0), Non-interlace Mode (SM = 0) 5-5 |

| 5–7         | CSYNC Timing in the 60 Hz (FD = 1), Non-interlace Mode (SM = 0) 5-5 |

| 5–8         | CSYNC Timing in the 50 Hz (FD = 0), Interlace Mode (SM = 1)         |

| 5–9         | CSYNC Timing in the 60 Hz (FD = 1), Interlace Mode (SM = 1) 5-6     |

| 5–10        | Cursor Position                                                     |

| 5–11        | Cursor Pattern Diagram 5–16                                         |

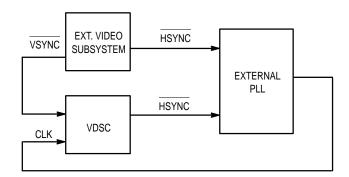

| 5–12        | VDSC in Slave Mode with an External PLL for Clock Generation        |

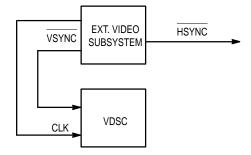

| 5–13        | VDSC in Slave Mode with an External Clock 5–20                      |

| 6–1         | Bitmap Serialization in 8 Bits/Pixel                                |

| 6–2         | Bitmap Serialization in 4 Bits/Pixel 6–2                            |

| 6–3         | Run–length Format in 7 Bits/Pixel                                   |

| 6–4         | Run-length Format in 3 Bits/Pixel 6–3                               |

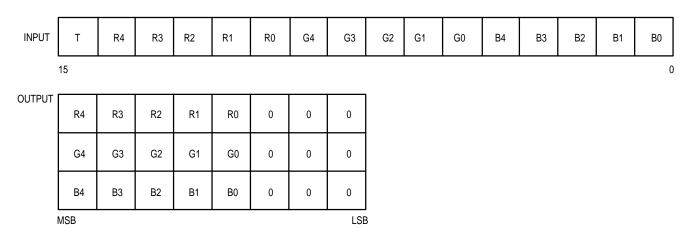

| 7–1         | Data Structure of DYUV Decoder Input and Output Pixel-pair 7-2      |

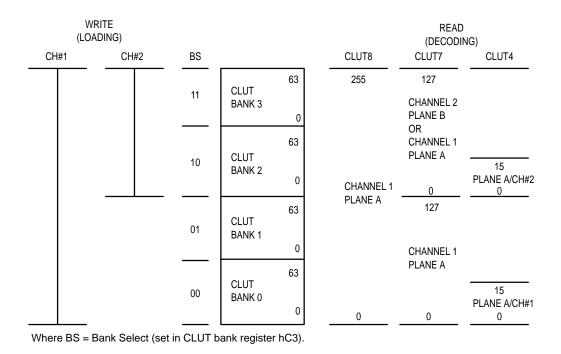

| 7–2         | CLUT Organization 7–3                                               |

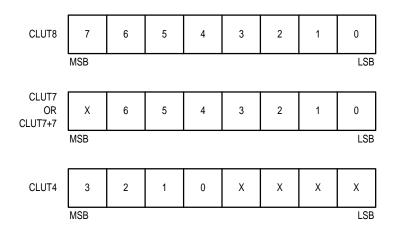

| 7–3         | Data Structure of Input CLUT Pixel                                  |

| 7–4         | Data Structure of RGB555 Input and Output Pixel                     |

# **LIST OF FIGURES (continued)**

| Fig.<br>No. | Title                                                   | Page<br>No. |

|-------------|---------------------------------------------------------|-------------|

| 8–1         | Pixel Hold Example for N = 3                            | 8–1         |

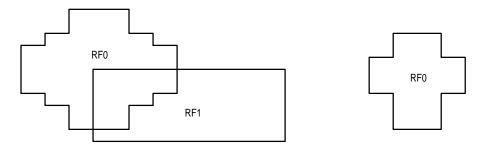

| 8–2         | Example Showing Overlapping and Non-overlapping Regions | 8–2         |

| 8–3         | Implicit Control of Region Flags (NR = 1)               | 8–2         |

| 8–4         | Explicit Control of Region Flags (NR = 0)               | 8–2         |

| 8–5         | Plane Order                                             | 8–3         |

| 8–6         | Overlay and Mixing — One Color Component                | 8–4         |

| 11–1        | Clock Timing                                            | 11–5        |

| 11–2        | Video Timing                                            | 11–5        |

| 11–3        | CPU Read Cycle Timing                                   | 11–6        |

| 11–4        | CPU Write Cycle Timing                                  | 11–6        |

| 11–5        | System Timing                                           | 11–6        |

| 11–6        | DRAM Timing                                             | 11–7        |

| 11–7        | Reset and Halt Timing                                   | 11–7        |

## **LIST OF TABLES**

| Table<br>No. | Page Title Page                                   |

|--------------|---------------------------------------------------|

| 3–1          | Address Map 3–3                                   |

| 3–2          | DTACK Delay for ROM         3–3                   |

| 4–1          | Address Map of the DRAM Banks 4–2                 |

| 4–2          | Memory Address Distribution 4–4                   |

| 4–3          | CAS1 and CAS2 Assertion 4–4                       |

| 4–4          | Implementing 256K x 4 DRAM 4–5                    |

| 4–5          | Implementing 1M x 4 DRAM 4–6                      |

| 4–6          | Implementing 256K x 16 DRAM 4–6                   |

| 5–1          | Normal Full–screen Display Resolution             |

| 5–2          | Horizontal Resolution 5–2                         |

| 5–3          | Scan Modes                                        |

| 5–4          | Vertical Resolution in the Non-interlace Mode     |

| 5–5          | Horizontal Synchronization Timing 5–4             |

| 5–6          | Vertical Synchronization Timing (in lines) 5–5    |

| 5–7          | Vertical Synchronization Timing (in lines) 5–5    |

| 5–8          | ICA Pointer Addresses 5–6                         |

| 5–9          | ICA1/DCA1 and ICA2/DCA2 Modes                     |

| 5–10         | Possible DCA1/DCA2 Fetches per Line 5–8           |

| 5–11         | ICA Control Instructions 5–8                      |

| 5–12         | DCA Control Instructions 5–9                      |

| 5–13         | Register Map 5–10                                 |

| 5–14         | CLUT Color Register 0–63 — Address h80 – hBF 5–10 |

| 5–15         | CLUT RAM Addresses 5–11                           |

| 5–16         | Image Coding Method Register – Address hC0        |

| 5–17         | CM1x, CM2x: Coding Method for Plane A, B          |

| 5–18         | Transparency Control Register – Address hC1       |

| 5–19         | Transparency Control Register – Address hC1       |

| 5–20         | Plane Order Register – Address hC2                |

| 5–21         | Plane Order 5–13                                  |

| 5–22         | CLUT Bank Register – Address hC3                  |

| 5–23         | Bank Select                                       |

| 5–24         | Transparent Color Register – Address hC4 – hC6    |

# **LIST OF TABLES (continued)**

| Table<br>No. | Title                                                       | Page<br>No. |

|--------------|-------------------------------------------------------------|-------------|

| 5–25         | Mask Color Register – Address hC7 – hC9                     | 5–13        |

| 5–26         | Delta YUV Absolute Start Value Register – Address hCA – hCB | 5–14        |

| 5–27         | Cursor Position Register – Address hCD                      | 5–14        |

| 5–28         | Cursor Control Register – Address hCE                       | 5–15        |

| 5–29         | Cursor Color                                                | 5–15        |

| 5–30         | Cursor Pattern Register – Address hCF                       | 5–16        |

| 5–31         | Region Control Register – Address hD0 – hD7                 | 5–16        |

| 5–32         | Operation Control Codes                                     | 5–17        |

| 5–33         | Background Color Register – Address hD8                     | 5–17        |

| 5–34         | Color of Background Plane                                   | 5–18        |

| 5–35         | Mosaic Pixel Hold Factor Register – Address hD9, hDA        | 5–18        |

| 5–36         | Weight Factor Register – Address hDB – hDC                  | 5–18        |

| 5–37         | Bitmap Width for Bitmap Files                               | 5–19        |

| 5–38         | Synchronization Modes                                       | 5–20        |

| 6–1          | File Type of Display 1                                      | . 6–1       |

| 6–2          | File Type of Display 2                                      | . 6–1       |

| 6–3          | Mosaic Factor of Display 1                                  | . 6–3       |

| 6–4          | Mosaic Factor of Display 2                                  | . 6–3       |

| 6–5          | Output Modes of Channel 1                                   | . 6–4       |

| 6–6          | Output Modes of Channel 2                                   | . 6–4       |

| 7–1          | Dequantizer                                                 | . 7–2       |

| 7–2          | Display Modes for Plane A                                   | . 7–5       |

| 7–3          | Display Modes for Plane B                                   | . 7–5       |

| 7–4          | Possible Combinations of Display Modes                      | . 7–5       |

| 7–5          | Possible Cursor and Background Colors                       | . 7–6       |

| 9–1          | Register Summary                                            | . 9–1       |

| 9–2          | Register Bitmap                                             | . 9–2       |

| 9–3          | Control Register 1 – Write, 4FFF0                           | . 9–2       |

| 9–4          | DTACK Delay                                                 |             |

| 9–5          | Control Register 2 – Write, 4FFFE0                          | . 9–3       |

| 9–6          | Status Register CSR1R – Read, 4FFFF1                        |             |

| 9–7          | Status Register CSR2R – Read, 4FFFE1                        | . 9–4       |

#### **LIST OF TABLES (continued)**

| Table<br>No. | Title                                         | Page<br>No. |

|--------------|-----------------------------------------------|-------------|

| 9–8          | Display Command Register DCR1 – Write, 4FFFF2 | 9–4         |

| 9–9          | Crystal Frequency                             | 9–4         |

| 9–10         | Scan Mode                                     | 9–5         |

| 9–11         | Channel 1 Color Mode                          | 9–5         |

| 9–12         | ICA1/DCA1 Enable                              | 9–5         |

| 9–13         | Display Command Register DCR2 – Write, 4FFFE2 | 9–5         |

| 9–14         | Channel 2 Color Mode                          | 9–5         |

| 9–15         | ICA1/DCA1 Enable                              | 9–5         |

| 9–16         | Display Decoder Register 1 – Write, 4FFF8     | 9–6         |

| 9–17         | Channel 1 Mosaic Factor                       | 9–6         |

| 9–18         | Channel 1 Display File Type                   | 9–6         |

| 9–19         | Display Decoder Register 2 – Write, 4FFFE8    | 9–6         |

| 9–20         | Channel 2 Mosaic Factor                       | 9–7         |

| 9–21         | Channel 2 Display File Type                   | 9–7         |

| 9–22         | Video Start Register 1 – Write, 4FFFF4        | 9–7         |

| 9–23         | Video Start Register 2 – Write, 4FFFE4        | 9–7         |

| 9–24         | Display Control Pointer 1 – Write, 4FFFA      | 9–8         |

| 9–25         | Display Control Pointer 2 – Write, 4FFFEA     | 9–8         |

| A-1          | 16-bit Quantization Table                     | A-2         |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

## **GENERAL DESCRIPTION**

#### 1.1 INTRODUCTION

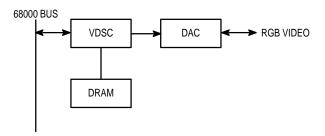

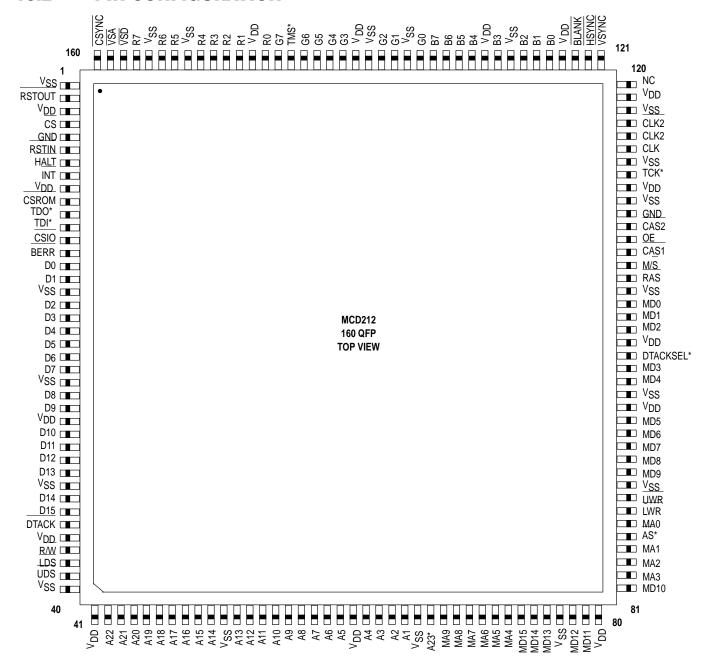

The Video Decoder and System Controller with JTAG (VDSC/JTAG) is a CMOS device integrating a 680X0 family system controller and video graphics decoder, see Figure 1–1 below.

The MCD212 is a programmable, multi–scan video device that can function as either a master or a slave. It is functionally equivalent to the MCD211 with the addition of JTAG testing. The MCD212 is a drop–in replacement for the MCD211 if the JTAG functionality is not required. It can directly drive up to 5M bytes<sup>1</sup> of memory and provides chip–select signals for system ROM and peripherals. The on–chip DRAM controller can support up to 4M bytes DRAM and controls access to the unspecialized System or Video DRAM. The CPU can access any memory location, even during active video display lines, thereby boosting system performance.

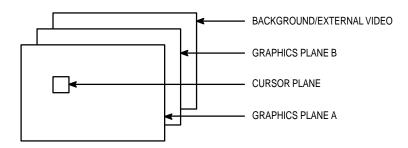

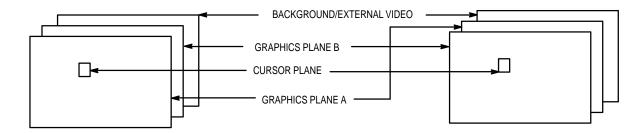

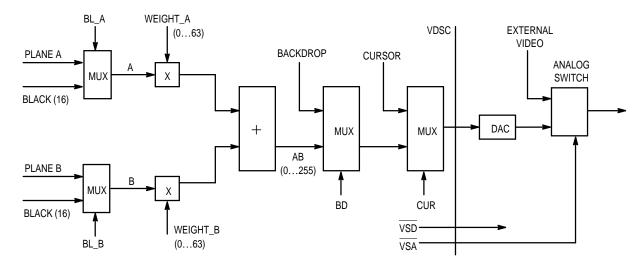

The video image is made up of four separate video planes: the cursor, two graphics planes (A and B), and one background plane. The video decoder receives two independent video channels from the Video DRAM. Each channel has a real–time file decoder permitting the display of normal, run–length, and mosaic compressed files. The resulting files can contain DYUV, CLUT, or direct RGB data. After decoding the resulting planes, A and B can be combined with a cursor and background allowing for visual effects like dissolves, mosaics, partial updates, etc., under software control. The resulting display is available in Red, Green, and Blue components, each being eight bits in length. The display resolution is programmable up to 768 x 560.

Figure 1–1. System Block Diagram

<sup>1.</sup> In this document a word is defined as 16 bits and a long—word as 32 bits. Hexadecimal figures are indicated by an h in front.

#### 1.2 FEATURES

#### **System Interface:**

- Direct Interface for 680X0 Bus Compatible Devices

- 1M Byte ROM Control

- 1K Byte I/O Control

- Reset Sequencer, Including ROM Shadowing

- Watchdog Timer

#### **DRAM Interface:**

- 4M Byte DRAM Direct Drive

- 256K x 4, 1M x 4, and 256K x 16 DRAM Types Can be Used

#### Video Interface:

- Up to 768 x 560 Screen Resolution

- Capability to Display Run–length Coded Files

- Mosaic Effect

- 256-entry Color Look Up Table (CLUT)

- Two Delta YUV Decoders

- · Cursor Shape, Color, and Blink Control

- Overlaying of Four Video Planes

- Special Effects via Weight Control, Priority Control, etc.

- Dynamic Programmable Registers and CLUT Reload in Retrace Period

- Digital RGB Output (8 Bits per Component)

- Synchro Generator for 50 and 60 Hz Scan

- · Synchronization with External Video

#### General:

- CMOS Technology

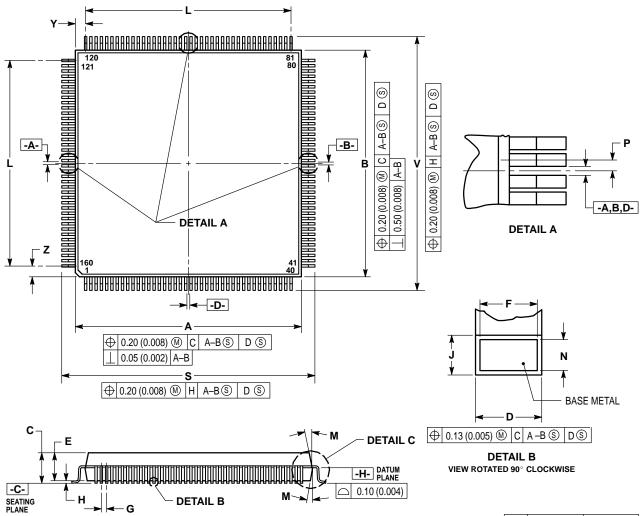

- 160-pin Quad Flat Pack Plastic Package

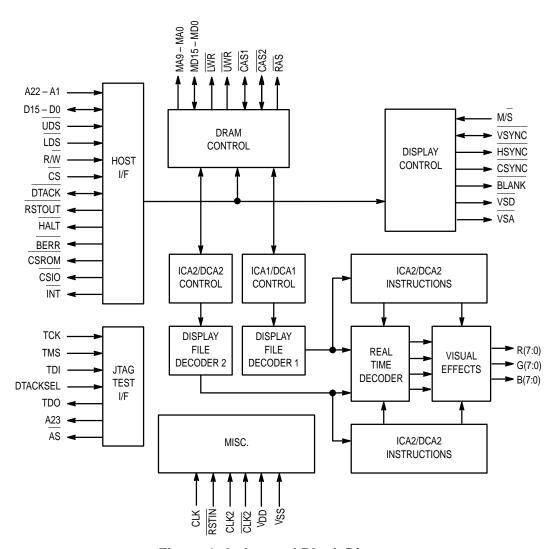

#### 1.3 BLOCK DIAGRAM

Figure 1-2. Internal Block Diagram

#### 1.4 DIFFERENCES BETWEEN THE MCD211 AND THE MCD212

There are two differences between the parts:

- JTAG testing has been added for automated board testing. The additional pins required to do this

were VSS pins on the MCD211. Hence, the MCD212 can be put in place of an MCD211 and will

function identically. The functionality of the R/W, LDS, UDS, A1 A22, RAS pins have been enhanced. (See Chapter 2 for the names of the new pins and the changes in functionality.)

- 2. Also, the processor interface timing has been improved to allow operation with higher speed processors. This is detailed in Section 11.3.

#### 2.1 INTRODUCTION

"Active" and "inactive" or "asserted" and "negated" are referred to in this user manual independent of whether the signal is active in the high (logic 1) state or the low (logic 0) state. The definition of the active level of each signal may be found in the individual pin descriptions.

#### 2.2 PIN FUNCTION DESCRIPTION

### 2.2.1 System Interface

| Mnemonic | Type | Name and Function                                                                                                                                                                                                           |  |  |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

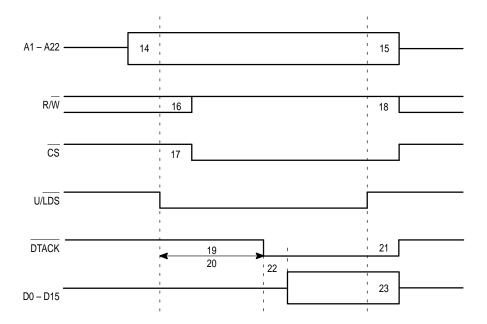

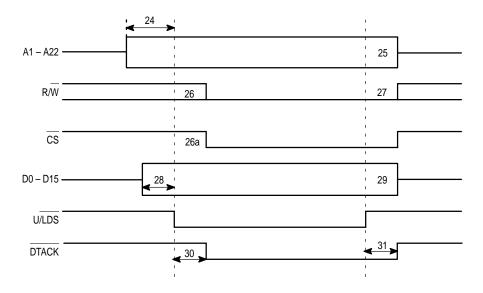

| A1 – A22 | I    | System address lines. Provides address for access from the system bus. Must be stable when UDS and/or LDS are asserted.                                                                                                     |  |  |

| D0 – D15 | I/O  | Bidirectional data bus, three–state. Used to transfer DATA between system bus and VDSC. Must be stable when UDS or LDS is asserted during write access. Driven by VDSC during read cycles. D0 is the least significant bit. |  |  |

| UDS      | I    | Upper Data Strobe. Active low. When asserted, UDS indicates that data is being addressed on D8 to D15.                                                                                                                      |  |  |

| LDS      | I    | Lower Data Strobe. Active low. When asserted, LDS indicates that data is being addressed on D0 to D7.                                                                                                                       |  |  |

| R/W      | I    | Read/Write. This input indicates transfer on the system bus. When low, indicates data is to be written into VDSC controlled resources or internal registers. When high, indicates a read is taking place.                   |  |  |

| CS       | I    | Chip Select. Active low. When asserted, indicates data transfer between system bus and VDSC controlled resources is enabled. Validates address decode for system access.                                                    |  |  |

| DTACK    | I/O  | Data Transfer Acknowledge signal. Active low, three–state. Asserted by VDSC when the system bus cycle, concerning VDSC controlled resources, can be continued. This pin must be pulled up externally.                       |  |  |

| RSTOUT   | 0    | Reset output. Active low, open drain. Asserted by the VDSC reset sequencer during the reset procedure. This pin must be pulled up externally.                                                                               |  |  |

| HALT     | 0    | Halt line output. Active low, open drain. Asserted by the VDSC reset sequencer during the reset procedure. This pin must be pulled up externally.                                                                           |  |  |

| BERR     | Ο    | Bus Error output. Active low, three—state. Asserted, when enabled, by the VDSC watchdog timer circuit if UDS or LDS is still asserted at the end of the time—out period. This pin must be pulled up externally.             |  |  |

| CSROM | Ο | Chip Select ROM output. Active low. Asserted by <u>an access on the</u> system bus in the ROM address area, and when UDS and/or LDS are asserted. |

|-------|---|---------------------------------------------------------------------------------------------------------------------------------------------------|

| CSIO  | 0 | Chip Select I/O output. Active low. Asserted by an access on the system bus in the I/O area, and when UDS and/or LDS are asserted.                |

| INT   | 0 | Interrupt request output. Active low, three–state. Used to generate interrupts to the CPU. This pin must be pulled up externally.                 |

# 2.2.2 Dynamic RAM Interface

| Mnemonic      | Туре | Name and Function                                                                                                                                                                                                              |

|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA0 –<br>MA9  | 0    | Memory Address lines. Multiplexed row/column address line outputs for DRAM control.                                                                                                                                            |

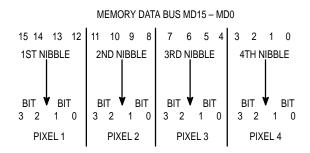

| MD0 –<br>MD15 | I/O  | Bidirectional Memory Data bus, three–state. Used to transfer data between DRAM bus and VDSC. Stable when LWR and/or UWR is asserted during a write cycle. Driven by VDSC during read cycles. MD0 is the least significant bit. |

| RAS           | 0    | Row Address Strobe. Active low. Validates the DRAM row address on the falling edge.                                                                                                                                            |

| CAS1          | I/O  | Column Address Strobe for memory bank 1. Active low, three–state. Validates the DRAM column address on the falling edge. Input during reset sequence to select/deselect memory bank 1. Active high validates bank inputs.      |

| CAS2          | I/O  | Column Address Strobe for memory bank 2. Active low, three–state. Validates the DRAM column address on the falling edge. Input during reset sequence to select/deselect memory bank 2. Active high validates bank inputs.      |

| UWR           | 0    | Write signal for DRAM. Active low. It is asserted when writing MD8 – MD15 to the DRAM.                                                                                                                                         |

| LWR           | 0    | Write signal for DRAM. Active low. It is asserted when writing MD0 – MD7 to the DRAM.                                                                                                                                          |

## 2.2.3 Video Interface

| Mnemonic | Type | Name and Function                                                                                                                                                                       |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0 – R7  | 0    | Red color output (R7 = MSB, R0 = LSB). Three–state.                                                                                                                                     |

| G0 – G7  | 0    | Green color output (G7 = MSB, G0 = LSB). Three–state.                                                                                                                                   |

| B0 – B7  | 0    | Blue color output (B7 = MSB, B0 = LSB). Three–state.                                                                                                                                    |

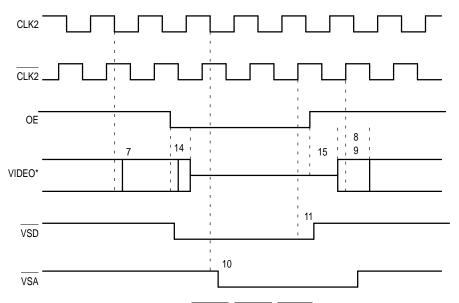

| OE       | I    | Output Enable. Active high. It disables three-state of RGB output.                                                                                                                      |

| VSYNC    | I/O  | Vertical Synchronization. Active low. In master mode, this output is used as vertical synchronization signal for monitor. In slave TV mode it becomes a vertical synchronization input. |

| HSYNC    | 0    | Horizontal Synchronization. Active low. This output is used as a horizontal synchronization signal.                                                                                     |

| CSYNC    | 0    | Composite synchronization. Active low. This output is used as a composite synchronization signal.                                                                                       |

| BLANK | 0 | Blanking output. Active low. It is asserted during vertical and horizontal blanking periods and high the rest of the time.                                               |

|-------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSD   | 0 | Video Select for digital video. Active low. This signal is synchronous to the digital video output.                                                                      |

| VSA   | 0 | Video Select for analog video. <u>Active</u> low. This signal is a CLK2 clock cycle delayed version of VSD and synchronous to analog video after clocked D/A conversion. |

| M/S   | I | Master/Slave TV mode selection. When high, the VDSC generates the video timing. When low the vertical synchronization can be slaved to an external video timing.         |

# 2.2.4 JTAG Test Signals

| Mnemonic | Type | Name and Function                                                                                                                                                                                                                  |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK      | I    | JTAG Test Clock input. Provides the clock for the test logic defined by IEEE Std. 1149.1–1990. 100 k $\Omega$ internal pull–up.                                                                                                    |

| TMS      | I    | JTAG Test Mode Select input. The signal decoded by the TAP controller to control test operations, defined by IEEE Std. 1149.1–1990. 100 k $\Omega$ internal pull–up.                                                               |

| TDI      | I    | JTAG Test Data input. Pin at which serial test instructions and data are received by the test logic, defined by IEEE Std. 1149.1–1990. 100 k $\Omega$ internal pull–up.                                                            |

| TDO      | ОТ   | JTAG Test Data output. Three–state. Serial output for test instructions and data from the test logic defined by IEEE Std. 1149.1–1990.                                                                                             |

| A23      | ОТ   | System Address line (three–stated in functional mode). During JTAG EXTEST, A23 may drive system address line A23 off–chip.                                                                                                         |

| ĀS       | ОТ   | System Address strobe (three–stated in functional mode). During JTAG EXTEST, AS may drive the system address strobe line AS off–chip.                                                                                              |

| DTACKSEL | I    | Selects advance time of the falling edge of DTACK before data (read) is valid on pins D0 – D15. For designs using 68000/68070–16 or 68340/341–16 series processors, tie DTACKSEL low; for 68340/341–25 designs, tie DTACKSEL high. |

# 2.2.5 Miscellaneous Signals

| Mnemonic | Type | Name and Function                                                             |

|----------|------|-------------------------------------------------------------------------------|

| CLK      | Ī    | External clock input.                                                         |

| RSTIN    | I    | Reset input. Active low. Schmitt trigger. Initiates a reset sequence.         |

| CLK2     | 0    | CLK/2 clock output. Frequency is CLK frequency divided by 2.                  |

| CLK2     | 0    | CLK/2 clock output. Frequency is CLK frequency divided by 2. Inverse of CLK2. |

| $V_{DD}$ | I    | Power supply pins (5 V).                                                      |

| Vss      | I    | Power and signal ground pins.                                                 |

NOTE: All the pins are TTL compatible, except for CLK and RSTIN, which use CMOS levels.

#### 2.3 PIN TYPES

CMOS input :CLK

CMOS Schmitt :RSTIN

input

TTL input :all inputs except CLK, RSTIN

6 mA output :<u>D0 - D15, RSTOUT, HALT, BERR, INT, MD0 - MD15, MA0 - MA9,</u>

LWR, UWR, R0 - R7, G0 - G7, B0 - B7, BLANK, CSYNC, HSYNC,

VSYNC, VSD, CLK2, CLK2

12 mA output : CSIO, CSROM

16 mA output : RAS, CAS1, CAS2

The VDSC performs several 680X0 system control functions.

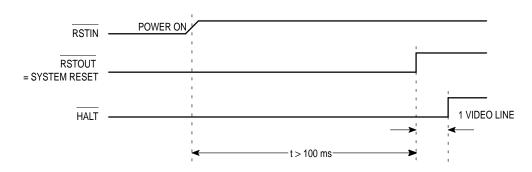

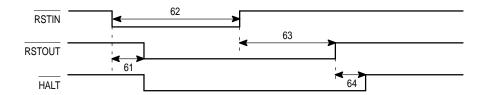

#### 3.1 RESET AND HALT GENERATION

When the RSTIN pin is released, the timing chain counts eight video frames (= 8 x 312 x 112 x 16 CLK cycles) in the default internal configuration at power on before the RSTOUT (reset output) pin is released, i.e., 160 ms with a 28 MHz crystal, 150 ms with a 30 MHz crystal, or 148 ms with a 30.2097 MHz crystal. The HALT pin is released one video line later. At RESET, VDSC registers are configured in the state indicated in Section 3.2.

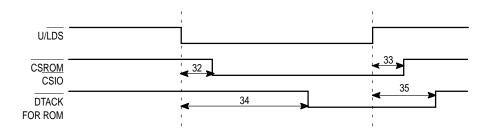

Figure 3-1. Reset and Halt Timing Chart

#### 3.2 RESET MECHANISM

The following bits in these control registers are reset by the RESET input:

Image Coding Method Register: (hCO): bits 0, 1, 2, 3, 8, 9, 10, 11, 18 (plane A and B off,

external video disabled)

Cursor Control Register: (hCE): bit 23 (cursor disabled)

Background Color Register: (hD8): bits 0, 1, 2, 3 (black backdrop)

The following bits in internal registers are reset by the RESET input:

CSR1W: DI1, DD1, DD2, TD, DD, ST, BE

CSR2W: DI2

DCR1: DE, CF, FD, SM, CM1, IC1, DC1

DCR2: CM2, IC2, DC2

DDR1: MF1, MF2, FT1, FT2

DDR2: MF1, MF2, FT1, FT2

The result of a reset will be a constant black level at the RGB outputs and no video synchronization output.

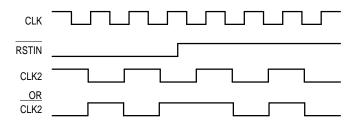

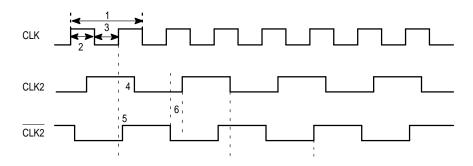

The active low reset pin must be connected to the system reset signal. The RSTIN also has an effect on the clock output CLK2 (see Figure 3–2). Two different waveforms for CLK2 are possible. It can be seen that CLK2 is present during and after reset.

Figure 3–2. CLK2 Clocking and Resetting

<u>CLK2</u> is <u>clocked</u> by the positive edge of CLK. Its phase after reset is related to the rising edge of RSTIN. CLK2 is always the inverse of CLK2.

#### 3.3 VDSC INITIALIZATION SEQUENCE

In order to have a proper start-up, register CSR1W must be initialized to the DRAM used. Display and control data must be loaded in DRAM.

Register DCR1 must be initialized to the required display mode at a rising edge of the DA-bit (CSR1R register). At a falling edge of the DA-bit (CSR1R register), the DE-bit (DCR1 register) must be set. Now video synchronization is generated. On the next rising edge of the DA-bit, the IC1 bit (DCR1 register) and IC2-bit (DCR2 register) must be set and on the next falling edge of the DA-bit the DC1-bit (DCR1 register) and DC2-bit (DCR2 register) must be set. Now the RGB outputs will generate a picture.

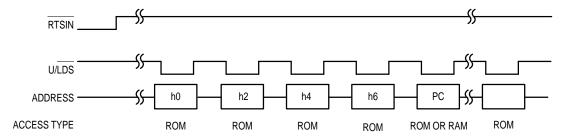

#### 3.4 MEMORY SWAPPING

After RSTIN is released the first four 680X0 word accesses are counted. If  $\overline{\text{CS}}$  is asserted at such a word access, a chip select to the ROM is given.

The 680X0 first four accesses correspond to the SSP (System Stack Pointer) and the PC (Program Counter). The SSP and PC must be located at address h400000 and h400004 which are decoded during the swapping. Address h0 to h7 are normally decoded afterwards.

Figure 3-3. Memory Swapping Timing Chart

#### 3.5 ADDRESS DECODING

The VDSC is connected to the system bus via 22 address lines and upper and lower data strobes. The address decoding is validated by CS.

Table 3-1. Address Map

| h000000 – h3FFFFF | DRAM (4M byte)               |

|-------------------|------------------------------|

| h400000 – h4FFBFF | System ROM (1M byte)         |

| h4FFC00 – h4FFFDF | System I/O (1K byte)         |

| h4FFFE0 – h4FFFEF | Channel 2 internal registers |

| h4FFFF0 – h4FFFFF | Channel 1 internal registers |

NOTE: The system ROM decoding asserts the CSROM pin that is not sensitive to the R/W signal. This allows the use of static RAM in the ROM mapping area. The system I/O decoding asserts the CSIO pin.

#### 3.6 DATA ACKNOWLEDGE GENERATION

A data transfer is initiated by an upper and/or lower data strobe (U/LDS) from the system. A data transfer is acknowledged by the VDSC via DTACK. A data transfer is terminated by U/LDS becoming inactive followed by DTACK becoming inactive.

The VDSC generates the data acknowledge (DTACK) depending on the addressed area:

- Access to the DRAM is acknowledged as soon as it is certain that data can be read or written by the system.

- Access to the system ROM is acknowledged after a programmable number of clock or CLK cycles. The DTACK delay is controlled by Control Register CSR1W.

If U/LDS becomes inactive before DTACK is generated by the VDSC, DTACK will not be generated.

Table 3–2. DTACK Delay for ROM

| DD | DD1 | DD2 | CLK Cycles |

|----|-----|-----|------------|

| 0  | х   | х   | 11 ≥ 12    |

| 1  | 0   | 0   | 3 ≥ 4      |

| 1  | 0   | 1   | 5≥6        |

| 1  | 1   | 0   | 7≥8        |

| 1  | 1   | 1   | 9 ≥ 10     |

NOTE: Access to the SYSTEM I/O device (CSIO pin) is not acknowledged by the VDSC but by the addressed device.

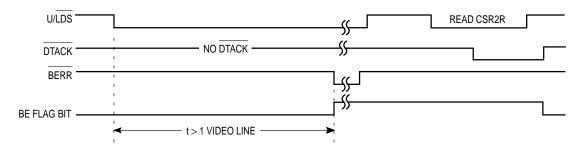

#### 3.7 BUS ERROR GENERATION

The BERR signal is asserted if enabled by writing a 1 in the BE (bus error) bit of the control register CSR1W and if a data transfer is not acknowledged for at least one entire video line (approximately 64  $\mu$ s) after selection. The <u>BE flag bit is then</u> set in the CSR2R register. The BERR pin is released as soon as the CPU releases UDS and LDS. The BE flag is reset when the CPU reads the CSR2R status register.

Figure 3-4. Bus Error Timing

#### 3.8 INTERRUPT GENERATION

The VDSC can generate interrupts to the CPU by asserting its INT pin. The following conditions can generate an interrupt:

- The ICA1/DCA1 controller fetches an interrupt instruction. Then, the IT1 bit of the CSR2R register is set. If the DI1 bit in the CSR1W register is reset to 0, the IT1 bit of the CSR2R register can generate an interrupt on the INT pin.

- The ICA2/DCA2 controller fetches an interrupt instruction. Then, the IT2 bit of the CSR2R register is set. If the DI2 bit in the CSR2W register is reset to 0, the IT2 bit of the CSR2R register can generate an interrupt on the INT pin.

INT = not((not(DI1) and IT1) or (not(DI2) and IT2))

The IT1 bit and IT2 bit are reset after the CPU reads the CSR2R register. The INT pin is inactive when both IT1 and IT2 are reset (see equation above).

# 4 DRAM CONTROL

The VDSC has an on-chip dynamic RAM (DRAM) controller. It supports several DRAM configurations and performs DRAM arbitration, address multiplexing, timing generation, and refresh.

#### 4.1 DRAM CONFIGURATION

The DRAM types the VDSC can drive are  $256K \times 4$ ,  $1M \times 4$  and  $256K \times 16$ . They always form a 16—bit data bus. The devices can be configured in one or two banks. Six configurations are possible:

- 4 Devices 256K x 4 (512K byte)

- 8 Devices 256K x 4 (1M byte)

- 4 Devices 1M x 4 (2M byte)

- 8 Devices 1M x 4 (4M byte)

- 1 Device 256K x16 (512K byte)

- 2 Devices 256K x16 (1M byte)

The TD (type of device) bit of the CSR1W register selects either 256K x 4, 256K x 16 (TD = 0), or  $1M \times 4$  (TD = 1) DRAM type.

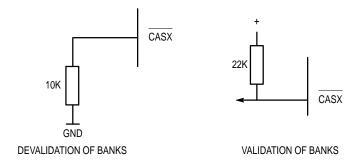

The selection between one or two banks is done by fixing the CAS1 and CAS2 pins to a logical level during reset. CAS1 corresponds to bank 1 and CAS2 corresponds to bank 2. See Table 4–1 for the address map of the DRAM banks. No DTACK is generated for addresses outside a certain configuration.

Table 4-1. Address Map of the DRAM Banks

| Address Range     | A22 | A21 | A20 | A19 | A18 | TD = 0 | TD = 1 |

|-------------------|-----|-----|-----|-----|-----|--------|--------|

| h000000 - h03FFFF | 0   | 0   | 0   | 0   | 0   | bank 1 | bank 1 |

| h040000 – h07FFFF | 0   | 0   | 0   | 0   | 1   | bank 2 | bank 1 |

| h080000 – h0BFFFF | 0   | 0   | 0   | 1   | 0   |        | bank 1 |

| h0C0000 - h0FFFFF | 0   | 0   | 0   | 1   | 1   |        | bank 1 |

| h100000 - h13FFFF | 0   | 0   | 1   | 0   | 0   |        | bank 2 |

| h140000 – h17FFFF | 0   | 0   | 1   | 0   | 1   |        | bank 2 |

| h180000 – h1BFFFF | 0   | 0   | 1   | 1   | 0   |        | bank 2 |

| h1C0000 - h1FFFFF | 0   | 0   | 1   | 1   | 1   |        | bank 2 |

| h200000 - h23FFFF | 0   | 1   | 0   | 0   | 0   | bank 1 | bank 1 |

| h240000 – h27FFFF | 0   | 1   | 0   | 0   | 1   | bank 2 | bank 1 |

| h280000 – h2BFFFF | 0   | 1   | 0   | 1   | 0   |        | bank 1 |

| h2C0000 - h2FFFFF | 0   | 1   | 0   | 1   | 1   |        | bank 1 |

| h300000 - h33FFFF | 0   | 1   | 1   | 0   | 0   |        | bank 2 |

| h340000 – h37FFFF | 0   | 1   | 1   | 0   | 1   |        | bank 2 |

| h380000 – h3bFFFF | 0   | 1   | 1   | 1   | 0   |        | bank 2 |

| h3c0000 – h3FFFFF | 0   | 1   | 1   | 1   | 1   |        | bank 2 |

#### 4.2 DRAM ACCESS AND ARBITRATION

The VDSC allows the DRAM to be used simultaneously as both video and system memory so that a CPU can access any location of the entire memory space even during active video display time. Additionally, the DRAM bus can be accessed by several masters and an arbitration scheme is implemented to provide each master with a guaranteed access time.

The various masters are:

- The System Bus (CPU or DMA cycles)

- Display Decoder 1

- Display Decoder 2

- ICA/DCA Controller 1

- ICA/DCA Controller 2

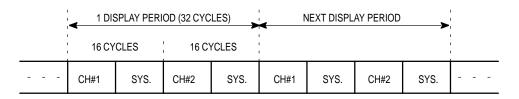

- The DRAM Refresh Controller

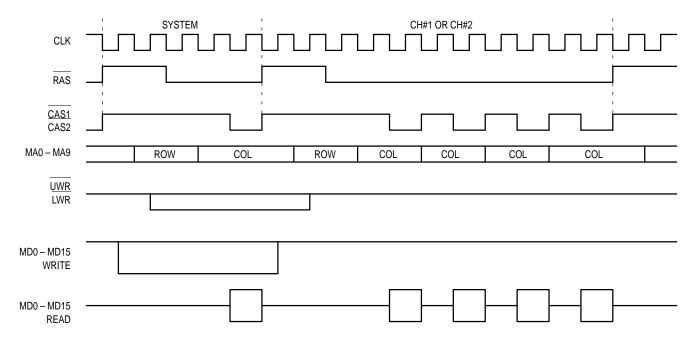

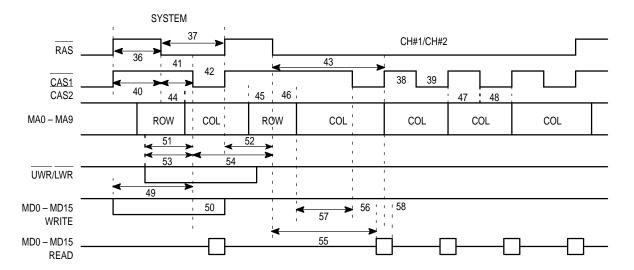

The DRAM access consists of consecutive display periods of 32 CLK cycles, which are subdivided into four slots (see Figure 4–1). The CH#1 slot is used by a video related function of channel 1 (display decoder 1 or ICA/DCA controller 1). The CH#2 slot is used by a video related function of channel 2 (display decoder 2 or ICA/DCA decoder 2). The DRAM refresh controller uses the CH#1 and CH#2 slots for RAS only refresh with two DRAM rows per slot. The system slots are available for a DRAM access from the system bus (e.g., CPU or DMA cycles) once every 16 CLK periods.

Figure 4–1. DRAM Access

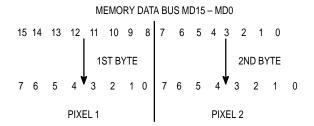

Eleven CLK periods are used for accessing CH#1 or CH#2 data, as shown in Figure 4–3. This represents four DRAM accesses for data. These four 16–bit words can represent varying amounts of pixel data in plane #1 or plane #2. For example, when using RGB555 data type, the four accesses represent color information for four pixels. (NOTE: Only plane 2 is available with RGB555 data; therefore, one complete display period contains color information for eight pixels.) The remaining five CLK periods are used for one DRAM access for system data.

When no video or refresh functions are required, the access to DRAM is free-running with no display periods, so that a system bus access can be accepted at any time. Examples of this are after a stop instruction in ICA/DCA or during run-length files.

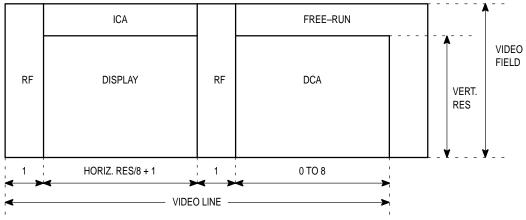

The selection between display, ICA, DCA, and refresh is done according to Figure 4–2, the time domain of a video frame.

#### NOTES:

- 1. RF is the refresh time area. Eight DRAM rows are refreshed per video line.

- 2. ICA and DCA only exist if enabled.

- The free—run area starts when the ICA/DCA is completed or when an ICA/DCA stop instruction is encountered.

- 4. If the display is not enabled, the entire area is free-run except the refresh areas.

- 5. Each number is the number of display periods (32 CLK cycles).

- 6. Horizontal resolution is the number of pixels in normal resolution.

Figure 4-2. DRAM Cycles

#### **Example:**

The ICA time is at the beginning of each vertical field as shown in Figure 4–2. If there are no ICA instructions to execute, then this is free–run time. There is one display period when eight row addresses can be refreshed. Then, to calculate the maximum number of display periods in the display area, divide the normal resolution by 8 and add 1 (i.e., 384/8 = 48). Then there is one display period for refresh. Next is the DCA time if it has been enabled. The number of pixel periods of the DCA is programmed in the DCR register, with 8 (= 64 bytes) being the maximum. The rest of the video line time is then available as free—run time.

#### 4.3 DRAM TIMING

The DRAM timing is based on the CLK clock (see Figure 4–3).

Figure 4–3. DRAM Timing

In the CH#1/CH#2 slot a burst of four words are read in fast page mode. If a page break occurs, the burst is incomplete. In the system slot a random read or write is possible.

The memory address bus (MA) is multiplexed in order to present the row address on RAS falling edge and the column address on CAS1 or CAS2 falling edge. The correspondence between memory address bus, MA0 – MA9 and system address A1 – A22 is indicated in Table 4–2. CAS1 and CAS2 function as bank select signals (see Table 4–3).

Table 4–2. Memory Address Distribution

|     | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | MA6 | MA7 | MA8 | MA9 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| RAS | A11 | A12 | A13 | A14 | A15 | A16 | A17 | A18 | Ax  | A19 |

| CAS | A1  | A2  | А3  | A4  | A5  | A6  | A7  | A8  | A9  | A10 |

$Ax = A10 \text{ for TD} = 0 (256K \times 4, 256K \times 16)$  $Ax = A18 \text{ for TD} = 1 (1M \times 4)$

Table 4–3. CAS1 and CAS2 Assertion

| TD = 0 | CAS1 asserted if validated and A18 = 0, A19 = 0, A20 = 0, A22 = 0 CAS2 asserted if validated and A18 = 1, A19 = 0, A20 = 0, A22 = 0 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| TD = 1 | CAS1 asserted if validated and A20 = 0, A22 = 0 CAS2 asserted if validated and A20 = 1, A22 = 0                                     |

#### 4.4 DRAM DESELECT

<u>During</u> the reset period, banks can be devalidated if their corresponding <u>CAS</u> pin is grounded. No DTACK is generated for devalidated banks. A pull—up is needed to validate banks.

Figure 4–4. DRAM Banks Validation/Devalidation

#### 4.5 DRAM IMPLEMENTATION

Tables 4-4 thru 4-6 show how the 256K x 4, 1M x 4, and 256K x 16 type DRAMs are connected to the VDSC.

|             |         | Bar     | nk 1    |         | Bank 2  |         |         |         |

|-------------|---------|---------|---------|---------|---------|---------|---------|---------|

|             | DRAM 1  | DRAM 2  | DRAM 3  | DRAM 4  | DRAM 5  | DRAM 6  | DRAM 7  | DRAM 8  |

| MD0 – MD3   | D0 – D3 |         |         |         | D0 – D3 |         |         |         |

| MD4 – MD7   |         | D0 – D3 |         |         |         | D0 – D3 |         |         |

| MD8 – MD11  |         |         | D0 – D3 |         |         |         | D0 – D3 |         |

| MD12 – MD15 |         |         |         | D0 – D3 |         |         |         | D0 – D3 |

| MA0 – MA8   | A0 – A8 |

| LWR         | W       | W       |         |         | W       | W       |         |         |

| UWR         |         |         | W       | W       |         |         | W       | W       |

| RAS         | RAS     | RAS     | RAS     | RAS     | RAS     | RAS     | RAS     | RAS     |

| CAS1        | CAS/OE  | CAS/OE  | CAS/OE  | CAS/OE  |         |         |         |         |

| CAS2        |         |         |         |         | CAS/OE  | CAS/OE  | CAS/OE  | CAS/OE  |

Table 4-4. Implementing 256K x 4 DRAM

Table 4–5. Implementing 1M x 4 DRAM

|             |         | Bar     | nk 1    |         | Bank 2  |         |         |         |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|---------|--|

|             | DRAM 1  | DRAM 2  | DRAM 3  | DRAM 4  | DRAM 5  | DRAM 6  | DRAM 7  | DRAM 8  |  |

| MD0 – MD3   | D0 – D3 |         |         |         | D0 – D3 |         |         |         |  |

| MD4 – MD7   |         | D0 – D3 |         |         |         | D0 – D3 |         |         |  |

| MD8 – MD11  |         |         | D0 – D3 |         |         |         | D0 – D3 |         |  |

| MD12 – MD15 |         |         |         | D0 – D3 |         |         |         | D0 – D3 |  |

| MA0 – MA9   | A0 – A9 |  |

| LWR         | W       | W       |         |         | W       | W       |         |         |  |

| UWR         |         |         | W       | W       |         |         | W       | W       |  |

| RAS         | RAS     | RAS     | RAS     | RAS     | RAS     | RAS     | RAS     | RAS     |  |

| CAS1        | CAS/OE  | CAS/OE  | CAS/OE  | CAS/OE  |         |         |         |         |  |

| CAS2        |         |         |         |         | CAS/OE  | CAS/OE  | CAS/OE  | CAS/OE  |  |

Table 4–6. Implementing 256K x 16 DRAM

|            | Bank 1<br>DRAM 1 | Bank 2<br>DRAM 2 |

|------------|------------------|------------------|

| MD0 – MD15 | D0 – D15         | D0 – D15         |

| MA0 – MA8  | A0 – A8          | A0 – A8          |

| LWR        | LW               | LW               |

| UWR        | UW               | UW               |

| RAS        | RAS              | RAS              |

| CAS1       | CAS/OE           |                  |

| CAS2       |                  | CAS/OE           |

## IMAGE DISPLAY CONTROL

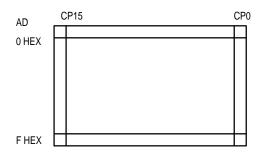

The VDSC is programmable on a line-by-line (DCA) and/or field-by-field (ICA) basis. The image displayed by the VDSC is made up of four distinct, programmable graphics planes, as indicated in Figure 5–1. The foremost is the cursor plane, behind which are two video planes (A and B), and behind them is a background plane. The data for plane A is handled by CH#1, while CH#2 handles the B plane data. The order in which graphics planes A and B are displayed is controllable via the plane order register (hC2) through CH#1.

Figure 5-1. Four Video Planes of the Displayed Image

The VDSC is programmable for several pre–defined modes of display and contains two video start address registers (VSR1 and VSR2) to locate the video displays within the DRAM address space. The display logic reads words from the video display area and sends them to the display file decoder which serializes the data, either nibble per nibble or byte per byte. This programmability and flexibility allows the VDSC to do various special effects such as subscreens, windowing, mosaics, overlay and mixing, and transparency, among others.

#### 5.1 IMAGE FORMATS

The VDSC supports NTSC monitor, NTSC TV, and PAL TV formats as well as providing a means to display images in one format that were created in the other. This compatibility feature allows this part to be used throughout the world. Also, interlace and non–interlace displays are supported.

#### 5.1.1 NTSC/PAL

NTSC is the North American and Japanese standard for broadcast TV. The display is made up of 525 horizontal lines, counted in the vertical direction, displayed 30 times in one second. NTSC Monitor is a little-used standard in North America for in-studio use on monitors. It is also made up of 525 horizontal lines.

PAL is the European standard for broadcast TV. Its display is made up of 625 horizontal lines, counted in the vertical direction, but only displayed 25 times each second. Both systems allow for an image (or frame) to be made up of two fields, an odd and an even field. The field rate is twice the frame rate (60 Hz for NTSC and 50 Hz for PAL). Although each frame is made up of 525/625 lines, only 480/560 are visible on the screen.

#### 5.2 RESOLUTION

The normal full-screen resolution of the VDSC is shown in Table 5-1.

Table 5-1. Normal Full-Screen Display Resolution

| Display       | Number of Pixels<br>Horizontally | Number of Pixels<br>Vertically |

|---------------|----------------------------------|--------------------------------|

| NTSC Monitors | 360                              | 240                            |

| NTSC TVs      | 384                              | 240                            |

| PAL TVs       | 384                              | 280                            |

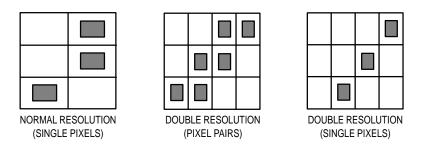

In addition to normal resolution, the VDSC provides both double resolution and high resolution modes. Double resolution is defined as twice the normal resolution in the horizontal direction, whereas high resolution is defined as twice the resolution in both horizontal and vertical directions. Although most TVs are not capable of clearly displaying single pixels in double resolution mode, this mode is useful in two areas:

- · Where double resolution pixel pairs can give increased positional accuracy.

- Where a single pixel's reduced display quality does not reduce the identifiability of the graphic object or character (i.e., Kanji characters).

Figure 5–2. Example of Normal and Double Resolution Pixels

#### 5.2.1 Horizontal Resolution

The horizontal resolution can be different between the two graphics planes (A and B) but both are controlled by various factors; the CF (Crystal Frequency) bit in the DCR1 register, the ST (Standard) bit in the CSR1W register, the CM1(Color Mode 1) bit in the DCR1 register, the CM2 (Color Mode 2) bit in the DCR2 register, and the frequency of the crystal. The effects of the various bits on the resolution are shown in Table 5–2.

Table 5-2. Horizontal Resolution

|    |    | Frequency  | Pixels/Line |        | Active Line | Display      |  |

|----|----|------------|-------------|--------|-------------|--------------|--|

| CF | ST |            |             | CM = 1 | <b>(μs)</b> | System       |  |

| 0  | х  | 28         | 360         | 720    | 51.4        | NTSC Monitor |  |

| 1  | 0  | 30/30.2097 | 384 768     |        | 51.2/50.84  | PAL/NTSC TV  |  |

| 1  | 1  | 30/30.2097 | 360         | 720    | 48/47.67    | PAL/NTSC TV  |  |

#### **5.2.2 Vertical Resolution**

The vertical resolution is dependent on the SM (Scan Mode) bit of the DCR1 register, the FD (Frame Duration) bit which is also in the DCR1 register, and the ST (Standard) bit which is in the CSR1W register.

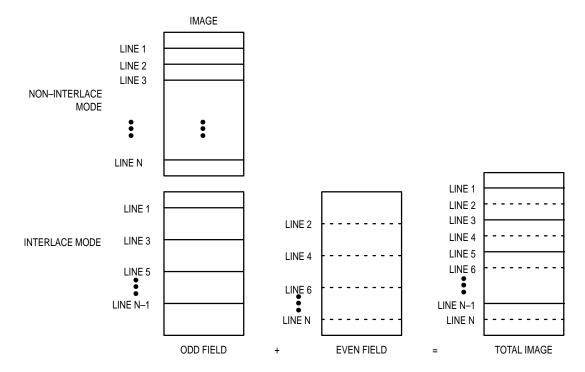

The SM bit controls the scan mode of the VDSC by selecting between the interlace mode and the non-interlace mode as described in Table 5–3 and shown in Figure 5–3.

Table 5-3. Scan Modes

| SM | SCAN Mode Description                                   |  |  |  |  |

|----|---------------------------------------------------------|--|--|--|--|

| 0  | Non-interlace mode. One image is composed of one field. |  |  |  |  |

| 1  | Interlace mode. One image is composed of two fields.    |  |  |  |  |

Figure 5-3. Line Display of Interlace versus Non-interlace Modes

The FD bit and the ST bit only affect the display in the non-interlace mode. They are shown in Table 5-4.

Table 5-4. Vertical Resolution in the Non-interlace Mode

| FD | ST | # of Video Lines | Frame Duration (ms) | Image<br>Frequency (Hz) | Display Type |

|----|----|------------------|---------------------|-------------------------|--------------|

| 0  | 0  | 280              | 18                  | 50                      | PAL          |

| 1  | 1  | 240              | 15.3                | 50                      | PAL          |

| 1  | х  | 240              | 15.3                | 60                      | NTSC         |

#### 5.3 **TIMING**

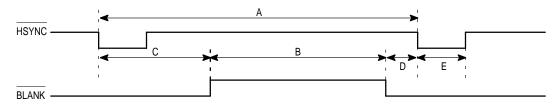

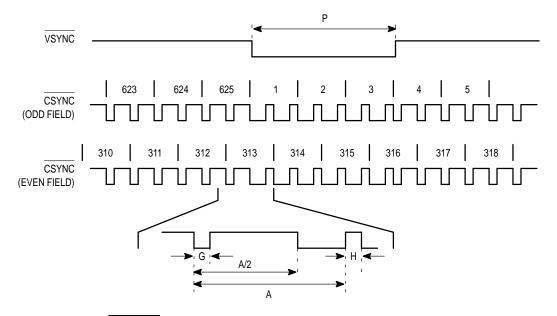

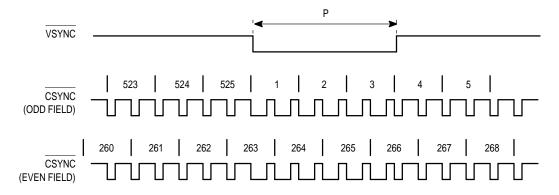

<u>The following tables</u> and figures depict the horizontal and vertical timing for the  $\overline{\text{HSYNC}}$ ,  $\overline{\text{VSYNC}}$ , CSYNC, and BLANK signals in the master mode.

- NOTES:

A: total horizontal line duration

B: active horizontal line duration

- 1 cycle = 16 CLK periods

- 1 cycle = 571.43 ns (CLK = 28 MHz NTSC monitor)

- 1 cycle = 533.33 ns (CLK = 30 MHz PAL TV)

- 1 cycle 529.63 ns (CLK = 30.2097 MHz NTSC TV)

Figure 5-4. HSYNC and BLANK Timing

Table 5-5. Horizontal Synchronization Timing

|   | CF = 0<br>(Cycles) | CLK=<br>28 MHz<br>(μs) | CF = 1<br>ST = 0<br>(Cycles) | CLK =<br>30 MHz<br>(μs) | CLK =<br>30.2097 MHz<br>(μs) | CF = 1<br>ST = 1<br>(Cycles) | CLK =<br>30 MHz<br>(μs) | CLK =<br>30.2097 MHz<br>(μs) |

|---|--------------------|------------------------|------------------------------|-------------------------|------------------------------|------------------------------|-------------------------|------------------------------|

| Α | 112                | 64.0                   | 120                          | 64.0                    | 63.56                        | 120                          | 64.0                    | 63.56                        |

| В | 90                 | 51.43                  | 96                           | 51.2                    | 50.84                        | 90                           | 48.0                    | 47.67                        |

| С | 19                 | 10.9                   | 20                           | 10.7                    | 10.59                        | 23                           | 12.3                    | 12.18                        |

| D | 3                  | 1.71                   | 4                            | 2.13                    | 2.12                         | 7                            | 3.7                     | 4.77                         |

| Ε | 8                  | 4.57                   | 9                            | 4.8                     | 4.77                         | 9                            | 4.8                     | 4.77                         |

| G | 4                  | 2.29                   | 4                            | 2.13                    | 2.12                         | 4                            | 2.13                    | 2.12                         |

| Н | 8                  | 4.57                   | 9                            | 4.8                     | 4.77                         | 9                            | 4.8                     | 4.77                         |

#### NOTES:

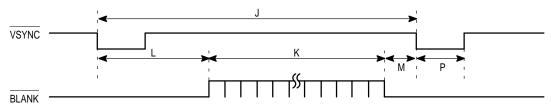

- J = Total Vertical Display Period

- K = Active Vertical Display

- P = Vertical Sync Width

Figure 5–5. VSYNC and BLANK Timing

Table 5–6. Vertical Synchronization Timing (in lines)\*

|   | 50 Hz ( |        |                |

|---|---------|--------|----------------|

|   | ST = 0  | ST = 1 | 60 Hz (FD = 1) |

| J | 312     | 312    | 262            |

| K | 280     | 240    | 240            |

| L | 26      | 46     | 18             |

| М | 6       | 26     | 4              |

| Р | 2.5     | 2.5    | 3              |

<sup>\*</sup> Non-interlace mode (SM = 0)

Table 5–7. Vertical Synchronization Timing (in lines)

|   |           | 50 Hz (    | 60 Hz (FD = 1) |                     |          |            |  |

|---|-----------|------------|----------------|---------------------|----------|------------|--|

|   | Odd Field | d (PA = 1) | Even Fiel      | Even Field (PA = 0) |          | Even Field |  |

|   | ST = 0    | ST = 1     | ST = 0         | ST =1               | (PA = 1) | (PA = 0)   |  |

| J | 312.5     | 312.5      | 312.5          | 312.5               | 262.5    | 262.5      |  |

| K | 280       | 240        | 280            | 240                 | 240      | 240        |  |

| L | 26        | 46         | 26.5           | 46.5                | 18       | 18.5       |  |

| М | 6.5       | 26.5       | 6              | 26.5                | 4.5      | 4          |  |

| Р | 2.5       | 2.5        | 2.5            | 2.5                 | 3        | 3          |  |

<sup>\*</sup> Interlace Mode (SM = 1)

#### NOTES:

To determine the time from the number of display lines, simply multiply the number of lines by the total line width (not the active display width). For instance, in an NTSC system with a  $63.56\,\mu s$  (from Table 5–5) line width, the total vertical display time for an interlace display is:

63.56 μs x 262.5 lines = 16.6845 ms

or the display rate is: 59.94 Hz.

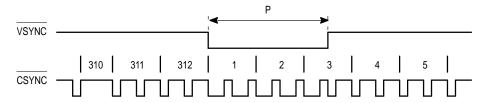

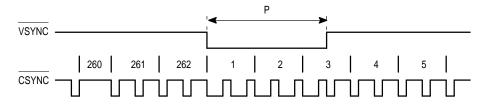

Figure 5-6. CSYNC Timing in the 50 Hz (FD = 0), Non-interlace Mode (SM = 0)

Figure 5–7. CSYNC Timing in the 60 Hz (FD = 1), Non-interlace Mode (SM = 0)

Figure 5–8. CSYNC Timing in the 50 Hz (FD = 0), Interlace Mode (SM = 1)

Figure 5–9. CSYNC Timing in the 60 Hz (FD = 1), Interlace Mode (SM = 1)

#### 5.4 SOFTWARE

The VDSC offers the possibility to fetch control information during vertical and horizontal retrace periods from the Image Control Area (ICA) and Dynamic Control Area (DCA), respectively. Each video channel has its associated ICA and DCA. For channel 1 this is ICA1 and DCA1, and for channel 2 this is ICA2 and DCA2. ICA/DCA control is identical and independent for both channels.

#### 5.4.1 ICA Control

ICA control consists of fetching long-word instructions during the vertical retrace period. The ICA pointers are indicated in Table 5–8.

Table 5–8. ICA Pointer Addresses

NOTE: Odd and even fields are indicated by the PA bit in the CSR1R register.

The possible number of ICA fetches is equal to the lines during vertical retrace times the display line width expressed in long words.

#### Example:

The number of crystal periods needed for a long-word access depends on the type of data being fetched. However, for example, if each access required five crystal periods then the following numbers would apply.

From Table 5–5: the total number of (16 CLK period) cycles = 120 per line. So, there are  $120 \times 16 = 1920$  crystal periods.

From Table 5–6: the number of lines in vertical blanking is 262 - 240 = 22 lines for the non–interlace mode.

Therefore, there are:  $22 \times 1920 = 42,240$  crystal periods during vertical blanking and 42,240/16 = 2640 memory fetches.

The video start register is also used as an ICA pointer after a "reload VSR" instruction to perform indirect ICA addressing during ICA instruction fetches to allow for linking blocks of instructions. All "reload VSR" instructions must contain an address with A0 = 0, A1 = 0, and A2 = 0. Each block ending with a "reload VSR" instruction must contain an even number of instructions including the "reload VSR" instruction, except for the first block.

#### 5.4.2 DCA Control

The instruction fetch takes place in the horizontal retrace period. The DCA size is 64 bytes/line.

The DCA is completely independent of the bit map or display file areas. The DCA pointer (DCP) points to the first line of the DCA. The second DCA line is pointed to automatically by DCP + 64 bytes. The DCP can be changed at any time by the "reload DCP and stop" instruction. This allows for linking blocks of instructions on a line—by—line basis.

#### 5.4.3 ICA/DCA Initialization

The ICA and DCA are enabled by the DE bit in the DCR1 register. The IC and DC bits of the DCR register control three possible ICA/DCA modes.

|    | ICA1/DCA1 Modes |     |      |      | ICA2/DCA2 Modes |     |     |      |      |

|----|-----------------|-----|------|------|-----------------|-----|-----|------|------|

| DE | IC1             | DC1 | ICA1 | DCA1 | DE              | IC2 | DC2 | ICA2 | DCA2 |

| 1  | 0               | х   | No   | No   | 1               | 0   | х   | No   | No   |

| 1  | 1               | 0   | Yes  | No   | 1               | 1   | 0   | Yes  | No   |

| 1  | 1               | 1   | Yes  | Yes  | 1               | 1   | 1   | Yes  | Yes  |

| 0  | Х               | х   | No   | No   | 0               | х   | х   | No   | No   |

Table 5-9. ICA1/DCA1 and ICA2/DCA2 Modes

When IC and DC are set to 1, the number of possible DCA fetches can be limited by the line retrace duration as indicated in the following tables.

Table 5-10. Possible DCA1/DCA2 Fetches per Line

| Pos | sible DCA1 F | etches Per L | _ine               | Pos | sible DCA2 F | etches Per L | ine                |

|-----|--------------|--------------|--------------------|-----|--------------|--------------|--------------------|

| IC1 | DC1          | CF           | DCA1<br>(in bytes) | IC2 | DC2          | CF           | DCA2<br>(in bytes) |

| 0   | х            | х            | 0                  | 0   | х            | х            | 0                  |

| 1   | 0            | х            | 0                  | 1   | 0            | х            | 0                  |

| 1   | 1            | 0            | 32                 | 1   | 1            | 0            | 32                 |

| 1   | 1            | 1            | 64                 | 1   | 1            | 1            | 64                 |

NOTE: An automatic stop instruction is performed at the end of the available area (when the effective DCA is larger than indicated). The allocated memory size is always 64 bytes even if the possible number of fetches is lower.

#### **5.4.4 ICA/DCA** Instructions

ICA/DCA instructions are contained in the system RAM. They are long—word aligned and long—word wide. The most significant byte indicates which register or registers are updated by the information contained in the other bytes. The instructions can be divided into two groups. The instructions from the first group affect the control of the instruction fetches, the display parameters, and interrupt generation (see Table 5–11). The instructions from the second group affect the video decoder and visual effects part (see Chapter 11). The control of the instructions fetches and display parameters can also be affected by the system (CPU). None of the registers can be read by the system.

Table 5-11. ICA Control Instructions

| Instruction<br>(Bit 31 – 0)              | Acronym                      | Action                                                                                                                                  |

|------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0000                                     | STOP                         | Stop the control sequence. The instruction fetches are stopped until the next field.                                                    |

| 0001                                     | NOP                          | No operation.                                                                                                                           |

| 0010 —— — pp pppp<br>pppp pppp ppp pp —  | RELOAD DCP                   | Reload the DCP register and its associated address counter with the specified pointer (p).                                              |

| 0011 —— — pp pppp<br>pppp pppp pppp pp — | RELOAD DCP and<br>STOP       | Reload the DCP register and its associated address counter with the specified pointer (p) and stop control fetches as STOP instruction. |

| 0100 —— — pp pppp<br>pppp pppp pppp      | RELOAD VSR                   | Reload ICA pointer. It functions as a jump instruction. It does not affect the VSR pointer.                                             |

| 0101 —— — pp pppp<br>pppp pppp pppp      | RELOAD VSR and<br>STOP       | Reload the VSR register and the video address counter with the specified pointer and stop the control fetches as STOP instruction.      |

| 0110                                     | INTERRUPT                    | Set IT bit in CSR register.                                                                                                             |

| 0111 1                                   | RELOAD DISPLAY<br>PARAMETERS | b = CM c = MF1 d = MF2 e = FT1<br>f = FT2                                                                                               |

Table 5–12. DCA Control Instructions

| Instruction<br>(Bit 31 – 0)              | Acronym                      | Action                                                                                                                                  |

|------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0000                                     | STOP                         | Stop the control sequence. The instruction fetches are stopped until the next field.                                                    |