# 18-Bit Switchable Active SCSI Bus Terminator (110 $\Omega$ )

The MCCS142235<sup>TM</sup> is a precision 18–bit switchable active SCSI bus terminator. It is used in conjunction with a 2.85V regulator (MC34268). Also provided is a Local–V<sub>CC</sub> (LV<sub>CC</sub>) low voltage sense circuit to latch the enable state when a peripheral is shut down or loses power. When the device is enabled according to the truth table below, the MCCS142235 provides 110 $\Omega$  precision resistor pull–ups to a 2.85V reference for termination of 18–bits in a SCSI standard bus system interface. When the switch is disabled, the device is in a High Impedance State on all 18 bits.

The low voltage sense circuit gives the device the ability to latch the current output state when power is removed from the LV<sub>CC</sub> pin. As long as TERMPWR remains, there is no interruption to the SCSI bus when powering down a SCSI peripheral, because the proper termination condition remains.

In 8-bit SCSI applications ("A" cable), only one '2235 is needed at each end of the SCSI cable in order to terminate the 18 active signal lines. In 16-bit WIDE SCSI applications ("P" cable), one '2235 and one '2234 (or two '2235s) would be needed at each end of the SCSI cable in order to terminate the 27 active signal lines.

For information on "Power Dissipation for Active SCSI Terminators," refer to Motorola Application Note AN1408/D, available through the Motorola Design-NET Fax System, or through the Motorola Literature Distribution Center.

- Complies With SCSI and SCSI–2 Standards

- 18 Switchable 110Ω Terminating Resistors

- Operating Temperature Range: 0°C to 70°C

- Operating Voltage Range: 2.75 to 2.95V

- Resistor Tolerance ±5.0% (Over Temperature and Supply Voltage Ranges)

- Local-VCC (LVCC) Low Voltage Sense Circuit

# MCCS142235

18-BIT ACTIVE SCSI TERMINATOR (110 $\Omega$ )

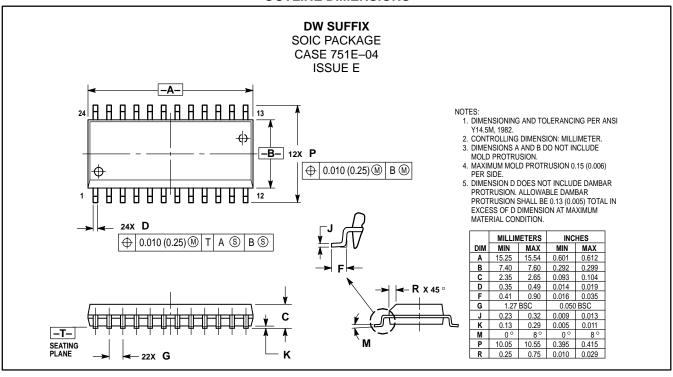

**DW SUFFIX** 24-LEAD WIDE SOIC PACKAGE CASE 751E-04

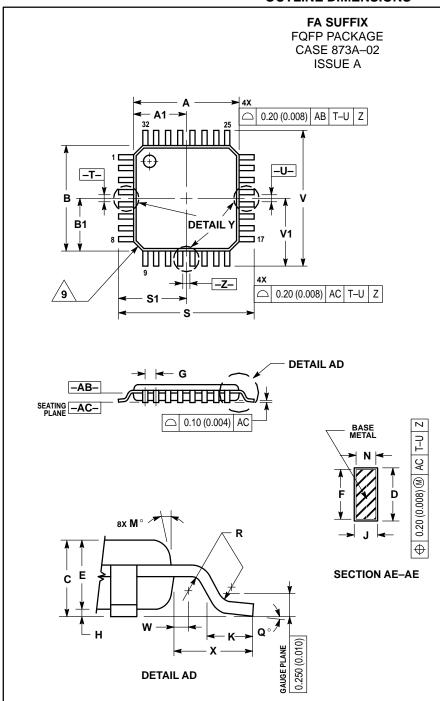

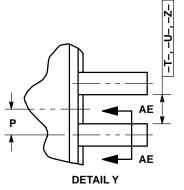

**FA SUFFIX** 32-LEAD PLASTIC FQFP PACKAGE CASE 873A-02

#### **TRUTH TABLE**

|              | Test     | Enable | Output     |  |

|--------------|----------|--------|------------|--|

| Active       | Active 0 |        | Z          |  |

| Mode         | 0        | 1      | Terminated |  |

| Test<br>Mode | 1        | Х      | Test Mode  |  |

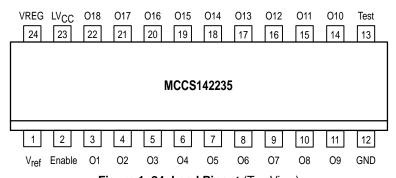

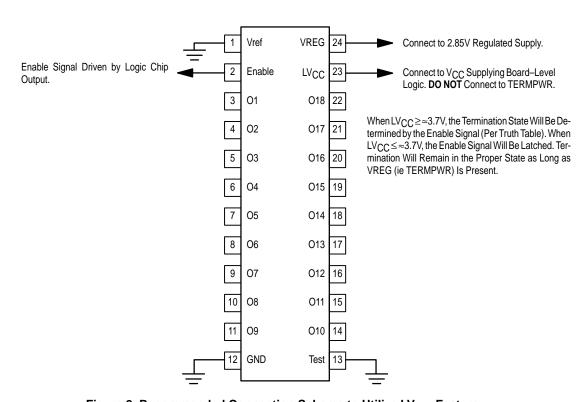

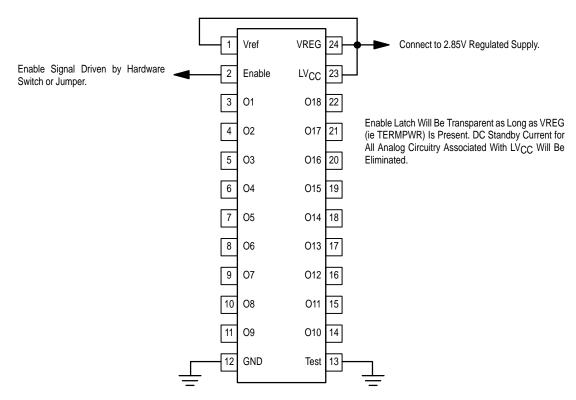

Figure 1. 24-Lead Pinout (Top View)

MCCS and Mfax are trademarks of Motorola. Inc.

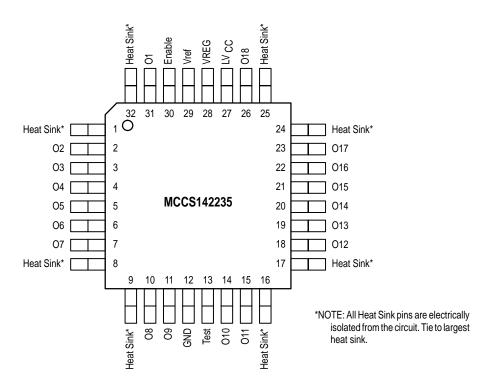

Figure 2. 32-Lead Pinout (Top View)

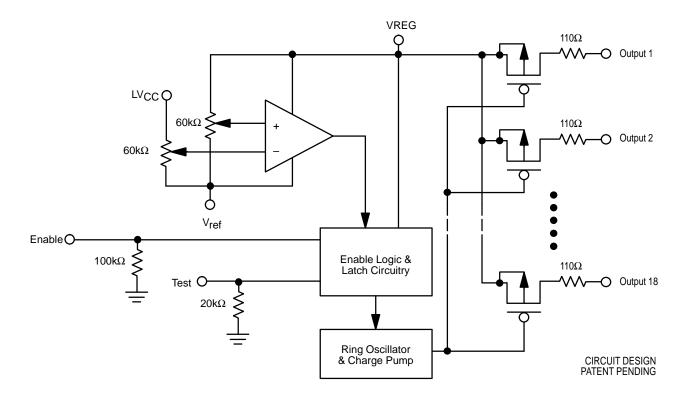

Figure 3. MCCS142235 Block Diagram

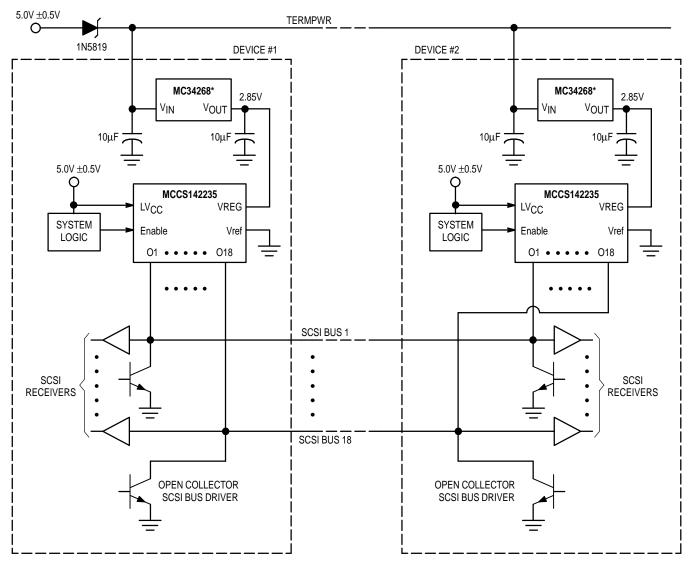

\*For More Application Information Refer to the MC34268 Datasheet.

Figure 4. Typical SCSI Bus Configuration Using the MCCS142235

### **MAXIMUM RATINGS\***

| Symbol           | Parameter                                                              | Value               | Units |

|------------------|------------------------------------------------------------------------|---------------------|-------|

| VREG             | DC Regulated Power Voltage (Referenced to GND)                         | -0.5 to 3.0         | V     |

| V <sub>in</sub>  | DC Input Voltage (Referenced to GND) for Test/V <sub>ref</sub> pins    | - 0.5 to VREG + 0.5 | V     |

| V <sub>in</sub>  | DC Input Voltage (Referenced to GND) for LV <sub>CC</sub> /Enable pins | - 0.5 to + 6.0      | V     |

| V <sub>out</sub> | DC Output Voltage (Referenced to GND)                                  | – 0.5 to VREG +0.5  | V     |

| l <sub>in</sub>  | DC Input Current, per pin                                              | ± 20                | mA    |

| l <sub>out</sub> | DC Output Current, per pin                                             | ± 35                | mA    |

| ICC              | DC Supply Current, VREG and GND pins                                   | ± 500               | mA    |

| T <sub>stg</sub> | Storage Temperature                                                    | - 65 to + 150       | °C    |

| TL               | Lead Temperature, 1mm from case for 10 seconds                         | 260                 | °C    |

<sup>\*</sup> Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

### RECOMMENDED OPERATING CONDITIONS

| Symbol                             | Parameter                                                  | Min  | Max      | Units |

|------------------------------------|------------------------------------------------------------|------|----------|-------|

| VREG                               | DC Regulated Power Voltage (Referenced to GND)             | 2.75 | 2.95     | V     |

| V <sub>in</sub> , V <sub>out</sub> | DC Input Voltage (Test/V <sub>ref</sub> Inputs)            | 0    | VREG     | V     |

| V <sub>in</sub>                    | DC Input Voltage (Enable, LV <sub>CC</sub> Inputs)         | 0    | 5.5      | V     |

| TA                                 | Operating Temperature                                      | 0    | 70       | °C    |

| t <sub>r</sub> , t <sub>f</sub>    | Input Rise and Fall Time (All inputs but LV <sub>CC)</sub> |      | 500      | ns    |

| t <sub>r</sub> , t <sub>f</sub>    | Input Rise and Fall Time (LV <sub>CC)</sub>                | 0    | no limit | ns    |

#### **DC CHARACTERISTICS**

|                 |                                                                      | VREG | 25  | 5°C   | 0°C to | + 70°C |      |                                                                            |

|-----------------|----------------------------------------------------------------------|------|-----|-------|--------|--------|------|----------------------------------------------------------------------------|

| Symbol          | Parameters                                                           | (V)  | Min | Max   | Min    | Max    | Unit | Condition                                                                  |

| VIH             | Min High-Level Input Voltage                                         | 2.85 | 2.0 |       | 2.0    |        | V    | Per Truth Table                                                            |

| V <sub>IL</sub> | Max Low-Level Input Voltage                                          | 2.85 |     | 0.8   |        | 0.8    | V    | Per Truth Table                                                            |

| l <sub>in</sub> | Max Input Leakage Current<br>(Enable Input)                          | 2.85 |     | ±0.10 |        | ±1.0   | μА   | V <sub>in</sub> = GND                                                      |

|                 | Max Input Leakage Current<br>(Test Input)                            | 2.85 |     | ±0.10 |        | ±1.0   | μА   | V <sub>in</sub> = GND                                                      |

|                 | Max Input Leakage Current (LV <sub>CC</sub> Input)                   | 2.85 |     | ±0.10 |        | ±1.0   | μА   | V <sub>in</sub> = GND<br>V <sub>ref</sub> = GND                            |

|                 |                                                                      | 2.85 |     | ±100  |        | ±200   | μА   | V <sub>in</sub> = 5.5V<br>V <sub>ref</sub> = GND                           |

|                 | Max Input Leakage Current (V <sub>ref</sub> Input)                   | 2.85 |     | ±0.10 |        | ±1.0   | μА   | V <sub>in</sub> = VREG<br>LV <sub>CC</sub> = VREG                          |

| loz             | Max Output Leakage Current                                           | 2.85 |     | ±0.50 |        | ±5.0   | μА   | Per Truth Table<br>V <sub>out</sub> = GND or VREG                          |

| Icc             | Max Quiescent Supply Current                                         | 2.85 |     | 1.0   |        | 10     | μА   | V <sub>ref</sub> /LV <sub>CC</sub> = VREG<br>Enable/Test = GND             |

|                 | Max Quiescent Supply Current (Comparator Active)                     | 2.85 |     | 100   |        | 200    | μА   | Enable/V <sub>ref</sub> /Test = GND<br>LV <sub>CC</sub> = 5.0V             |

|                 | Max Quiescent Supply Current (Comparator Active/ Termination Active) | 2.85 |     | 800   |        | 1000   | μА   | Test/ $V_{ref}$ = GND<br>Enable/ $LV_{CC}$ = 5.0V<br>$I_{out}$ = 0 $\mu$ A |

#### **TERMINATION RESISTOR CHARACTERISTICS**

|        |                                        | VREG (V) |      | 35°C               |                    | 0°C to + 70°C |       |      |                 |

|--------|----------------------------------------|----------|------|--------------------|--------------------|---------------|-------|------|-----------------|

| Symbol | Parameters                             | Min      | Max  | Min                | Max                | Min           | Max   | Unit | Condition       |

| R110   | Output Termination Impedance (Note 1.) | 2.75     | 2.95 | 108.9<br>(Note 1.) | 111.1<br>(Note 1.) | 104.5         | 115.5 | Ω    | Per Truth Table |

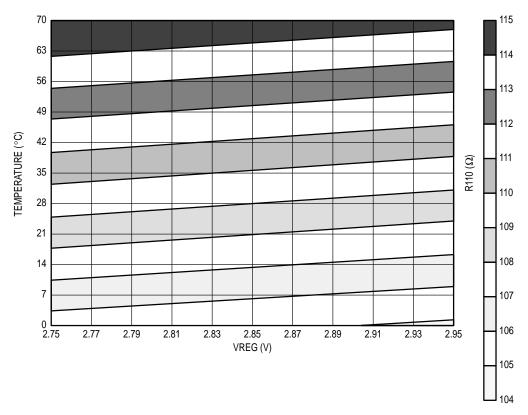

<sup>1.</sup> See Figure 5, Termination resistance versus regulated supply voltage and temperature. 110 $\Omega$  Resistor Target Is at 35°C. Temperature coefficient of resistance  $T_C = 0.135 \Omega/^{\circ}C$  typical.

Figure 5. Termination Resistance R110 ( $\Omega$ ) versus Regulated Supply Voltage VREG (V) and Temperature (°C) (Model Adj R-Sq = 0.9995)

## DC CHARACTERISTICS

| Symbol           | Parameter                              | VREG<br>(V) | Typical @ +25°C | Unit | Condition                    |

|------------------|----------------------------------------|-------------|-----------------|------|------------------------------|

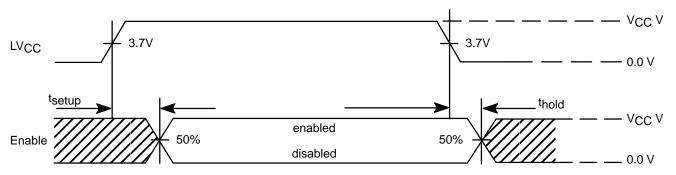

| VT               | Latch Voltage (LV <sub>CC</sub> Input) | 2.85        | 3.70            | V    | Per Truth Table              |

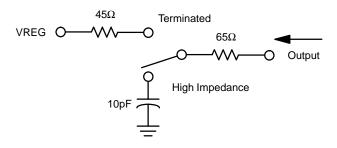

| C <sub>out</sub> | Output Capacitance High Impedance      | 2.85        | 8.0             | pF   | Per Truth Table, Output = 0V |

Figure 6. Output Impedance Model

AC CHARACTERISTICS (VREG = 2.85,  $C_L = 50$  pF,  $t_f = t_f = 6$  ns)

| Symbol                 | Parameters                                                                    | 0°C to + 70°C | Unit | Condition       |

|------------------------|-------------------------------------------------------------------------------|---------------|------|-----------------|

| <sup>t</sup> (Enable)  | Max Propagation Delay,<br>High Impedance to Termination,<br>Enable to Outputs | 100           | μs   | Per Truth Table |

| <sup>t</sup> (Disable) | Max Propagation Delay,<br>Termination to High Impedance,<br>Enable to Outputs | 1.0           | μs   | Per Truth Table |

#### **TIMING REQUIREMENTS** (VREG = 2.85, $C_L = 50$ pF, $t_f = t_f = 6$ ns)

| Symbol             | Parameters                                 | 25°C | 0°C to + 70°C | Unit | Condition      |

|--------------------|--------------------------------------------|------|---------------|------|----------------|

| t <sub>setup</sub> | Min Setup Time, LV <sub>CC</sub> to Enable | 200  | 500           | ns   | (See Figure 7) |

| <sup>t</sup> hold  | Min Hold Time, LV <sub>CC</sub> to Enable  | 50   | 100           | ns   | (See Figure 7) |

\* If LVCC Enable is grounded then the LVCC feature is disabled.

Figure 7. Timing Requirements

# MCCS142235 Applications Information

## Proper Use of the LV<sub>CC</sub> Feature

The Motorola Active SCSI Terminator chip incorporates features not available in competitor designs. A primary feature, known as "Local V<sub>CC</sub> sensing", facilitates future migration to reliable software control of the termination state (either terminated or high impedance). When the Enable pin is driven by internal logic within the SCSI peripheral, it is essential that the peripheral be powered up. Otherwise the enable signal to the termination chip may be invalid causing system bus failure due to improper termination. Imagine a SCSI system with a disk drive at one end of the bus which is providing termination to the bus via the MCCS142235 device. A "smart" drive will be providing an enable signal to the termination chip through internal logic circuitry to ensure termination is present. In the event this same disk drive is

powered down by a user while the bus is active, what becomes of the termination located within that drive? Does it remain terminated? Does it change state causing the system to crash? Or does it go into an undetermined state?

The termination power supply is always present on an operating SCSI bus through the dedicated TERMPWR line. But the "Local VCC" power supply within each peripheral may be powered down at any time while the SCSI bus is in operation. It is this local supply which powers the peripheral's logic chips and provides the enable signal to the SCSI terminator chip. Therefore, it is essential to maintain the proper enable signal to the switchable terminator even during peripheral power down.

To avoid rendering the system inoperable while powering down a terminating peripheral, Motorola has an exclusive "Local VCC sensing" circuit on the MCCS142235 which latches the enable state of the termination permanently during peripheral power loss. A comparator within the MCCS142235 can be connected to the local power supply via the LVCC input. The LVCC level is monitored against an internal reference, and the current enable state is latched should LVCC drop below a predetermined value ( $\approx\!\!3.70\mathrm{V}$ ). This comparator threshold is set sufficiently high to ensure that a valid logic state still exists on the TTL–level Enable pin prior to latching. Upon return of the local power supply, the enable path automatically becomes transparent, and the termination state returns to system control!

The Local V<sub>CC</sub> sensing feature has been designed to draw as little DC current as possible. Flexibility has been designed into the MCCS142235 to allow the Local V<sub>CC</sub> sensing feature to be disabled when not required. In this disabled state, the DC bias current is completely removed and the enable latch remains transparent at all times.

Figure 8 shows the recommended connection scheme to utilize the LV $_{\rm CC}$  latch feature. Figure 9 shows the recommended connection scheme for applications in which the LV $_{\rm CC}$  feature is not required – the LV $_{\rm CC}$  and V $_{\rm ref}$  pins are shorted to VREG and the enable path remains permanently transparent.

Figure 8. Recommended Connection Scheme to Utilize LV<sub>CC</sub> Feature

Figure 9. Recommended Connection Scheme to Disable LV<sub>CC</sub> Feature

| Enable Input Application                        | Result                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A. No Connection to Enable                      | Enable input will be pulled "LOW" internally. Termination will be disabled causing all outputs to be high impedance.                                                                                                                                                                                                                     |

| B. Single Pole Switch to Supply                 | Enable input will be pulled "LOW" internally when the switch is open. Enable input will be held "HIGH" when the switch is closed. The supply source in this case could be TERMPWR, VREG or $V_{\hbox{CC}}$ .                                                                                                                             |

| C. Double Pole Switch Between<br>Supply and GND | This is a more expensive way to accomplish application B. above. It is more economical to allow the internal pulldown to provide the "LOW" input level. The Supply Source in this case could be TERMPWR, VREG or $V_{CC}$ .                                                                                                              |

| D. Hardwired "Low"                              | The MCCS142235 will be permanently disabled causing all outputs to be high impedance.                                                                                                                                                                                                                                                    |

| E. Hardwired "High"                             | The MCCS142235 will be permanently enabled providing 110 $\!\Omega$ nominal impedance to each bus line.                                                                                                                                                                                                                                  |

| F. External Logic Driven                        | With LV <sub>CC</sub> input connected to the local power supply and V <sub>ref</sub> connected to GND, the Local–V <sub>CC</sub> sensing and Enable latching feature will be active. If this feature is not desired, tie LV <sub>CC</sub> and V <sub>ref</sub> to VREG (per Figure 9), and the Enable state will follow the Truth Table. |

#### **OUTLINE DIMENSIONS**

#### NOTES:

- 1 DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2 CONTROLLING DIMENSION: MILLIMETER.

- 2 CONTROLLING DIMENSION: MILLIMETER.

3 DATUM PLAME AB- IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

4 DATUMS T. U., AND Z- TO BE DETERMINED AT DATUM PLANE AB-.

5 DIMENSIONS S AND V TO BE DETERMINED AT SEATING PLANE AC-.

6 DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.250 (0.010) PER SIDE. DIMENSIONS A AND B DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE AB-.

- DO INCLUDE MOLD MISMAICH AND ARE

DETERMINED AT DATUM PLANE AB-.

7 DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. DAMBAR PROTRUSION SHALL

NOT CAUSE THE D DIMENSION TO EXCEED

0.520 (0.020).

- 8 MINIMUM SOLDER PLATE THICKNESS SHALL BE

- MINIMUM SOLDER PLATE TRICKNESS SHALL

0.0076 (0.0003).

EXACT SHAPE OF EACH CORNER MAY VARY

FROM DEPICTION.

|     | MILLIN | IETERS | INCHES    |           |  |  |

|-----|--------|--------|-----------|-----------|--|--|

| DIM | MIN    | MAX    | MIN MAX   |           |  |  |

| Α   | 7.000  | BSC    | 0.276 BSC |           |  |  |

| A1  | 3.500  | BSC    | 0.138     | BSC       |  |  |

| В   | 7.000  | BSC    | 0.276     | BSC       |  |  |

| B1  | 3.500  | BSC    | 0.138     | BSC       |  |  |

| С   | 1.400  | 1.600  | 0.055     | 0.063     |  |  |

| D   | 0.300  | 0.450  | 0.012     | 0.018     |  |  |

| Е   | 1.350  | 1.450  | 0.053     | 0.057     |  |  |

| F   | 0.300  | 0.400  | 0.012     | 0.016     |  |  |

| G   | 0.800  | BSC    | 0.031     | BSC       |  |  |

| Н   | 0.050  | 0.150  | 0.002     | 0.006     |  |  |

| J   | 0.090  | 0.200  | 0.004     | 0.008     |  |  |

| K   | 0.500  | 0.700  | 0.020     | 0.028     |  |  |

| M   | 12°    | REF    | 12° REF   |           |  |  |

| N   | 0.090  | 0.160  | 0.004     | 0.006     |  |  |

| Р   | 0.400  | BSC    | 0.016 BSC |           |  |  |

| Q   | 1°     | 5°     | 1°        | 5°        |  |  |

| R   | 0.150  | 0.250  | 0.006     | 0.010     |  |  |

| S   | 9.000  | BSC    | 0.354     | BSC       |  |  |

| S1  | 4.500  | BSC    | 0.177 BSC |           |  |  |

| ٧   | 9.000  | BSC    | 0.354 BSC |           |  |  |

| V1  | 4.500  | BSC    | 0.177 BSC |           |  |  |

| W   | 0.200  | REF    | 0.008     | REF       |  |  |

| X   | 1.000  | REF    | 0.039     | 0.039 REF |  |  |

#### **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights or others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and was negligent regarding the design or manufacture of the part. Motorola and Parameters of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

**USA/EUROPE/Locations Not Listed:** Motorola Literature Distribution; P.O. Box 5405; Denver, Colorado 80217. 303–675–2140 or 1–800–441–2447

Mfax™: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 INTERNET: http://Design-NET.com **JAPAN**: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 81–3–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298

MCCS142235/D