### **Product Preview**

# **Analog Multiplexer** / **Demultiplexer**

### **High-Performance Silicon-Gate CMOS**

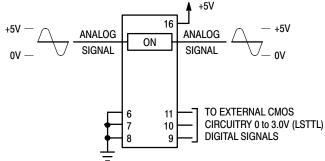

The MC74LVXT4053 utilizes silicon–gate CMOS technology to achieve fast propagation delays, low ON resistances, and low OFF leakage currents. This analog multiplexer/demultiplexer controls analog voltages that may vary across the complete power supply range (from  $V_{CC}$  to  $V_{EE}$ ).

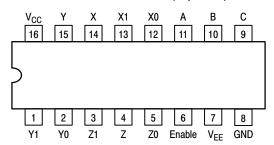

The LVXT4053 is similar in pinout to the LVXT8053, HC4053A, and the metal–gate MC14053B. The Channel–Select inputs determine which one of the Analog Inputs/Outputs is to be connected, by means of an analog switch, to the Common Output/Input. When the Enable pin is HIGH, all analog switches are turned off.

The LVXT control inputs are compatible with TTL levels.

The LVXT4053 control input structures provide protection when voltages between 0 V and 5.5 V are applied, regardless of the supply voltage. These input structures help prevent device destruction caused by supply voltage — input/output voltage mismatch, battery backup, hot insertion, etc.

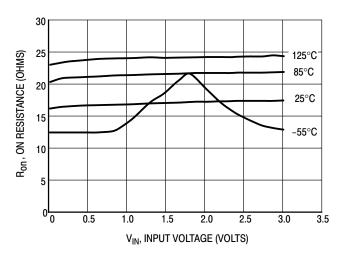

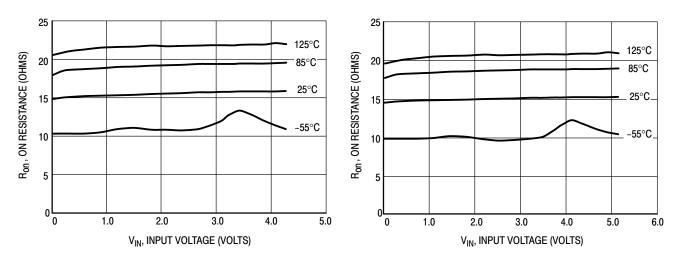

This device has been designed so that the ON resistance  $(R_{on})$  is more linear over input voltage than  $R_{on}$  of metal-gate CMOS analog switches, or High-Speed CMOS analog switches.

- Fast Switching and Propagation Speeds

- Low Crosstalk Between Switches

- TTL-Compatible Inputs:  $V_{IL} = 0.8 \text{ V}$ ;  $V_{IH} = 2.0 \text{ V}$

- Analog Power Supply Range  $(V_{CC} GND) = 2.0$  to 6.0 V

- Digital (Control) Power Supply Range  $(V_{CC} GND) = 2.0$  to 6.0 V

- Improved Linearity and Lower ON Resistance Than Metal–Gate, HSL, or VHC Counterparts

- Low Noise

- Latchup Performance Exceeds 300 mA

- ESD Performance: HBM > 2000 V; Machine Model > 200 V

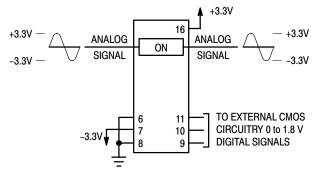

- Designed to Operate on a Single Supply with  $V_{EE}$  = GND, or Using Split Supplies up to  $\pm$  3.3 V

http://onsemi.com

#### MARKING DIAGRAMS

SOIC-16 D SUFFIX CASE 751B

TSSOP-16 DT SUFFIX CASE 948F

SOIC EIAJ-16 M SUFFIX CASE 966

A = Assembly Location

L, WL = Wafer Lot Y, YY = Year W, WW = Work Week

#### ORDERING INFORMATION

| Device           | Package         | Shipping        |

|------------------|-----------------|-----------------|

| MC74LVXT4053D    | SOIC-16         | 48 Units/Rail   |

| MC74LVXT4053DR2  | SOIC-16         | 2500 Units/Reel |

| MC74LVXT4053DT   | TSSOP-16        | 96 Units/Rail   |

| MC74LVXT4053DTR2 | TSSOP-16        | 2500 Units/Reel |

| MC74LVXT4053M    | SOIC<br>EIAJ-16 | 48 Units/Rail   |

| MC74LVXT4053MEL  | SOIC<br>EIAJ-16 | 2000 Units/Reel |

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

# PIN CONNECTION AND MARKING DIAGRAM (Top View)

#### **FUNCTION TABLE**

| Control Inputs |    |             |        |          |          |          |

|----------------|----|-------------|--------|----------|----------|----------|

| Enable         | С  | Select<br>B | t<br>A | ON       | l Chanr  | nels     |

| L              | L. | Ļ           | L      | Z0       | Y0       | X0       |

| L              | L  | Н           | H<br>L | Z0<br>Z0 | Y0<br>Y1 | X1<br>X0 |

| L<br>L         | L  | H<br>L      | H<br>L | Z0<br>Z1 | Y1<br>Y0 | X1<br>X0 |

| Ĺ              | H  | L<br>H      | H      | Z1<br>Z1 | Y0<br>Y1 | X1<br>X0 |

| L              | Н  | Н           | Н      | Z1       | Y1       | X1       |

| Н              | X  | X           | X      |          | NONE     |          |

X = Don't Care

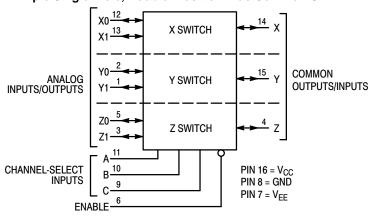

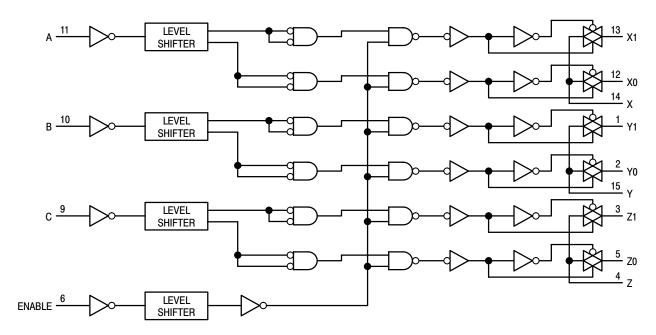

# LOGIC DIAGRAM Triple Single-Pole, Double-Position Plus Common Off

NOTE: This device allows independent control of each switch. Channel–Select Input A controls the X–Switch, Input B controls the Y–Switch and Input C controls the Z–Switch

#### **MAXIMUM RATINGS\***

| Symbol           | Parameter                                                                       | Value                                        | Unit |

|------------------|---------------------------------------------------------------------------------|----------------------------------------------|------|

| V <sub>EE</sub>  | Negative DC Supply Voltage (Referenced to GND)                                  | - 7.0 to + 5.0                               | V    |

| V <sub>CC</sub>  | Positive DC Supply Voltage (Referenced to GND) (Referenced to V <sub>EE</sub> ) | - 0.5 to + 7.0<br>- 0.5 to + 7.0             | V    |

| V <sub>IS</sub>  | Analog Input Voltage                                                            | $V_{EE} - 0.5 \text{ to} $<br>$V_{CC} + 0.5$ | V    |

| V <sub>in</sub>  | Digital Input Voltage (Referenced to GND)                                       | $-0.5$ to $V_{CC} + 0.5$                     | V    |

| I                | DC Current, Into or Out of Any Pin                                              | ± 20                                         | mA   |

| P <sub>D</sub>   | Power Dissipation in Still Air, SOIC Package† TSSOP Package†                    | 500<br>450                                   | mW   |

| T <sub>stg</sub> | Storage Temperature Range                                                       | - 65 to + 150                                | °C   |

| T <sub>L</sub>   | Lead Temperature, 1 mm from Case for 10 Seconds                                 | 260                                          | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range GND  $\leq$  ( $V_{in}$  or  $V_{out}$ )  $\leq$   $V_{CC}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or  $V_{CC}$ ). Unused outputs must be left open.

#### RECOMMENDED OPERATING CONDITIONS

| Symbol                          | Parameter                                                 |                                                                                          | Min             | Max             | Unit |

|---------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------|-----------------|------|

| V <sub>EE</sub>                 | Negative DC Supply Voltage                                | (Referenced to GND)                                                                      | -6.0            | GND             | V    |

| V <sub>CC</sub>                 | Positive DC Supply Voltage                                | (Referenced to GND)<br>(Referenced to V <sub>EE</sub> )                                  | 2.0<br>2.0      | 6.0<br>6.6      | V    |

| V <sub>IS</sub>                 | Analog Input Voltage                                      |                                                                                          | V <sub>EE</sub> | V <sub>CC</sub> | V    |

| V <sub>in</sub>                 | Digital Input Voltage (Referenced to GND)                 |                                                                                          | 0               | V <sub>CC</sub> | V    |

| V <sub>IO</sub> *               | Static or Dynamic Voltage Across Switch                   |                                                                                          |                 | 1.2             | V    |

| T <sub>A</sub>                  | Operating Temperature Range, All Package Types            |                                                                                          | - 55            | + 125           | °C   |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise/Fall Time<br>(Channel Select or Enable Inputs) |                                                                                          |                 |                 | ns/V |

|                                 |                                                           | $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$<br>$V_{CC} = 5.0 \text{ V} \pm 0.5 \text{ V}$ | 0<br>0          | 100<br>20       |      |

<sup>\*</sup>For voltage drops across switch greater than 1.2 V (switch on), excessive V<sub>CC</sub> current may be drawn; i.e., the current out of the switch may contain both V<sub>CC</sub> and switch input components. The reliability of the device will be unaffected unless the Maximum Ratings are exceeded.

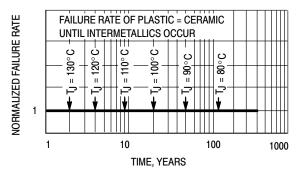

The  $\theta_{JA}$  of the package is equal to 1/Derating. Higher junction temperatures may affect the expected lifetime of the device per the table and figure below.

### DEVICE JUNCTION TEMPERATURE VERSUS TIME TO 0.1% BOND FAILURES

| Junction<br>Temperature °C | Time, Hours | Time, Years |

|----------------------------|-------------|-------------|

| 80                         | 1,032,200   | 117.8       |

| 90                         | 419,300     | 47.9        |

| 100                        | 178,700     | 20.4        |

| 110                        | 79,600      | 9.4         |

| 120                        | 37,000      | 4.2         |

| 130                        | 17,800      | 2.0         |

| 140                        | 8,900       | 1.0         |

Failure Rate vs. Time Junction Temperature

<sup>\*</sup>Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

<sup>†</sup>Derating — SOIC Package: – 7 mW/°C from 65° to 125°C TSSOP Package: – 6.1 mW/°C from 65° to 125°C

#### DC CHARACTERISTICS — Digital Section (Voltages Referenced to GND)

|                 |                                                                      |                                                                                             | V <sub>cc</sub>   | Guaranteed Limit     |                      |                      |      |

|-----------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------|----------------------|----------------------|----------------------|------|

| Symbol          | Parameter                                                            | Condition                                                                                   | V                 | –55 to 25°C          | ≤85°C                | ≤125°C               | Unit |

| V <sub>IH</sub> | Minimum High-Level Input Voltage,<br>Channel-Select or Enable Inputs | R <sub>on</sub> = Per Spec                                                                  | 3.0<br>4.5<br>5.5 | 1.4<br>2.0<br>2.0    | 1.4<br>2.0<br>2.0    | 1.4<br>2.0<br>2.0    | V    |

| V <sub>IL</sub> | Maximum Low–Level Input Voltage,<br>Channel–Select or Enable Inputs  | R <sub>on</sub> = Per Spec                                                                  | 3.0<br>4.5<br>5.5 | 0.53<br>0.80<br>0.80 | 0.53<br>0.80<br>0.80 | 0.53<br>0.80<br>0.80 | V    |

| I <sub>in</sub> | Maximum Input Leakage Current,<br>Channel–Select or Enable Inputs    | V <sub>in</sub> = V <sub>CC</sub> or GND,                                                   | 5.5               | ± 0.1                | ± 1.0                | ± 1.0                | μА   |

| Icc             | Maximum Quiescent Supply<br>Current (per Package)                    | Channel Select, Enable and V <sub>IS</sub> = V <sub>CC</sub> or GND; V <sub>in</sub> = 0 V  | 5.5               | 4                    | 40                   | 160                  | μΑ   |

| Ісст            | Quiescent Supply Current                                             | Channel Select, Enable<br>V <sub>IS</sub> = V <sub>CC</sub> or GND; V <sub>in</sub> = 3.4 V | 5.5               | 1.35                 | 1.50                 | 1.65                 | mA   |

#### DC ELECTRICAL CHARACTERISTICS Analog Section

|                  |                            |                                            |     |      | Gu      | aranteed Lii           | mit     |      |

|------------------|----------------------------|--------------------------------------------|-----|------|---------|------------------------|---------|------|

|                  |                            |                                            | Vcc | VEE  | – 55 to |                        |         |      |

| Symbol           | Parameter                  | Test Conditions                            | V   | V    | 25°C    | ≤ <b>85</b> ° <b>C</b> | ≤ 125°C | Unit |

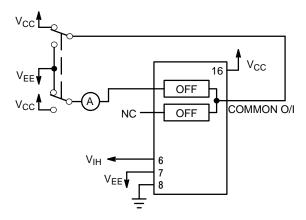

| R <sub>on</sub>  | Maximum "ON" Resistance    | $V_{in} = V_{IL} \text{ or } V_{IH}$       | 3.0 | 0    | 20      | 25                     | 30      | Ω    |

|                  |                            | $V_{IS} = V_{CC}$ to $V_{EE}$              | 4.5 | 0    | 10      | 15                     | 20      |      |

|                  |                            | $ I_S  \le 10.0 \text{ mA (Figures 1, 2)}$ | 5.5 | 0    | 7       | 10                     | 15      |      |

|                  |                            |                                            | 3.3 | -3.3 | 4.0     | 10                     | 15      |      |

|                  |                            | $V_{in} = V_{IL} \text{ or } V_{IH}$       | 3.0 | 0    | 20      | 25                     | 30      |      |

|                  |                            | $V_{IS} = V_{CC}$ or $V_{EE}$ (Endpoints)  | 4.5 | 0    | 10      | 15                     | 20      |      |

|                  |                            | $ I_S  \le 10.0 \text{ mA (Figures 1, 2)}$ | 5.5 | 0    | 7       | 10                     | 15      |      |

|                  |                            |                                            | 3.3 | -3.3 | 4.0     | 10                     | 15      |      |

| $\Delta R_{on}$  | Maximum Difference in "ON" | $V_{in} = V_{IL} \text{ or } V_{IH}$       | 3.0 | 0    | 5       | 5                      | 5       | Ω    |

|                  | Resistance Between Any     | $V_{IS} = 1/2 (V_{CC} - V_{EE})$           | 4.5 | 0    | 1       | 1.2                    | 1.5     |      |

|                  | Two Channels in the Same   | $ I_S  \leq 10.0 \text{ mA}$               | 5.5 | 0    | 1       | 1.2                    | 1.5     |      |

|                  | Package                    |                                            | 3.3 | -3.3 | 1       | 1.2                    | 1.5     |      |

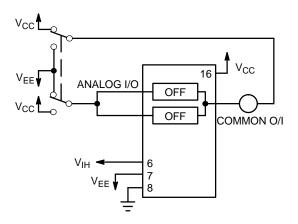

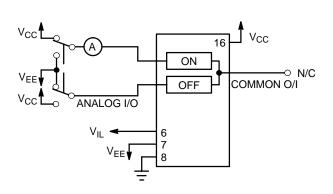

| I <sub>off</sub> | Maximum Off-Channel        | $V_{in} = V_{IL} \text{ or } V_{IH};$      | 5.5 | 0    | 1       | 10                     | 1000    | nA   |

|                  | Leakage Current, Any One   | $V_{IO} = V_{CC}$ or GND;                  | 3.3 | -3.3 | 1       | 10                     | 1000    |      |

|                  | Channel                    | Switch Off (Figure 3)                      |     |      |         |                        |         |      |

|                  | Maximum Off–Channel        | $V_{in} = V_{IL} \text{ or } V_{IH};$      | 5.5 | 0    | 1       | 10                     | 1000    |      |

|                  | Leakage Current,           | $V_{IO} = V_{CC}$ or GND;                  | 3.3 | -3.3 | 1       | 10                     | 1000    |      |

|                  | Common Channel             | Switch Off (Figure 4)                      |     |      |         |                        |         |      |

| I <sub>on</sub>  | Maximum On-Channel         | $V_{in} = V_{IL} \text{ or } V_{IH};$      | 5.5 | 0    | 1       | 10                     | 1000    | nA   |

|                  | Leakage Current,           | Switch-to-Switch =                         | 3.3 | -3.3 | 1       | 10                     | 1000    |      |

|                  | Channel-to-Channel         | V <sub>CC</sub> or GND; (Figure 5)         |     |      |         |                        |         |      |

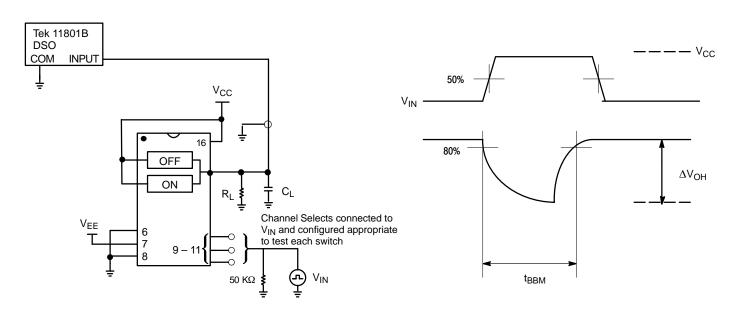

| t <sub>BBM</sub> | Minimum Break-Before-      | $V_{in} = V_{IL} \text{ or } V_{IH}$       | 3.0 | 0.0  | 1       | TBD                    | TBD     | ns   |

|                  | Make Time§                 | $V_{IS} = 1/2 (V_{CC} - V_{EE})$           | 4.5 | 0.0  | 0.2     | TBD                    | TBD     |      |

|                  | (Figure 13)                | $R_L = 300 \Omega, C_L = 35 pF$            | 5.5 | 0.0  | 0.2     | TBD                    | TBD     |      |

|                  |                            |                                            | 3.3 | -3.3 | 0.2     | TBD                    | TBD     |      |

§Guaranteed by design.

#### AC CHARACTERISTICS ( $C_L = 50 \text{ pF}$ , Input $t_r = t_f = 3 \text{ ns}$ )

|                    |                                                            | V <sub>CC</sub> | V <sub>EE</sub> | Guaranteed Limit |       | nit    |      |

|--------------------|------------------------------------------------------------|-----------------|-----------------|------------------|-------|--------|------|

| Symbol             | Parameter                                                  | V               | V               | –55 to 25°C      | ≤85°C | ≤125°C | Unit |

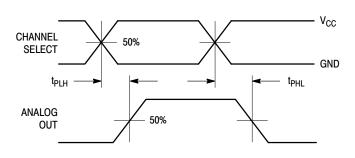

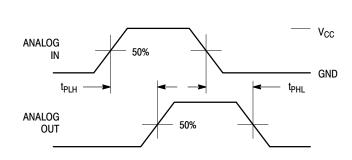

| t <sub>PLH</sub> , | Maximum Propagation Delay, Channel–Select to Analog        | 2.0             | 0               | 30               | 35    | 40     | ns   |

| t <sub>PHL</sub>   | Output                                                     | 3.0             | 0               | 20               | 25    | 30     |      |

|                    | (Figure 9)                                                 | 4.5             | 0               | 15               | 18    | 22     |      |

|                    |                                                            | 5.5             | 0               | 15               | 18    | 20     |      |

|                    |                                                            | 3.3             | -3.3            | 10               | 12    | 15     |      |

| t <sub>PLH</sub> , | Maximum Propagation Delay, Analog Input to Analog Output   | 2.0             | 0               | 1.0              | 1.0   | 2.0    | ns   |

| t <sub>PHL</sub>   | (Figure 10)                                                | 3.0             | 0               | 1.0              | 1.0   | 2.0    |      |

|                    |                                                            | 4.5             | 0               | 1.0              | 1.0   | 1.0    |      |

|                    |                                                            | 5.5             | 0               | 1.0              | 1.0   | 1.0    |      |

|                    |                                                            | 3.3             | -3.3            | 1.0              | 1.0   | 1.0    |      |

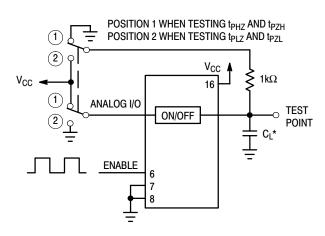

| t <sub>PLZ</sub> , | Maximum Propagation Delay, Enable to Analog Output         | 2.0             | 0               | 30               | 35    | 40     | ns   |

| t <sub>PHZ</sub>   | (Figure 11)                                                | 3.0             | 0               | 20               | 25    | 30     |      |

|                    |                                                            | 4.5             | 0               | 15               | 18    | 22     |      |

|                    |                                                            | 5.5             | 0               | 15               | 18    | 20     |      |

|                    |                                                            | 3.3             | -3.3            | 10               | 12    | 15     |      |

| $t_{PZL}$ ,        | Maximum Propagation Delay, Enable to Analog Output         | 2.0             | 0               | 20               | 25    | 30     | ns   |

| t <sub>PZH</sub>   | (Figure 11)                                                | 3.0             | 0               | 12               | 14    | 15     |      |

|                    |                                                            | 4.5             | 0               | 8.0              | 10    | 12     |      |

|                    |                                                            | 5.5             | 0               | 8.0              | 10    | 12     |      |

|                    |                                                            | 3.3             | -3.3            | 5.0              | 8.0   | 10     |      |

| C <sub>in</sub>    | Maximum Input Capacitance, Channel–Select or Enable Inputs |                 |                 | 10               | 10    | 10     | pF   |

| C <sub>I/O</sub>   | Maximum Capacitance Analog I/O                             |                 |                 | 35               | 35    | 35     | pF   |

|                    | (All Switches Off) Common O/I                              |                 |                 | 50               | 50    | 50     | 1    |

|                    | Feedthrough                                                |                 |                 | 1.0              | 1.0   | 1.0    |      |

| $C_{PD}$ |                                            | Typical @ 25°C, V <sub>CC</sub> = 5.0 V, V <sub>EE</sub> = 0V | pF |

|----------|--------------------------------------------|---------------------------------------------------------------|----|

|          | Power Dissipation Capacitance (Figure 18)* | 45                                                            |    |

<sup>\$</sup>Used to determine the no–load dynamic power consumption:  $P_D = C_{PD} \ V_{CC}^2 f + I_{CC} \ V_{CC}$ .

#### ADDITIONAL APPLICATION CHARACTERISTICS (GND = 0 V)

|                   |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                              | v <sub>cc</sub>          | V <sub>EE</sub>           | Limit*                       |                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|------------------------------|------------------|

| Symbol            | Parameter                                                                                                                    | Condition                                                                                                                                                                                                                                                                                                                                                                    | ٧                        | V                         | 25°C                         | Unit             |

| BW                | Maximum On–Channel Bandwidth or<br>Minimum Frequency Response<br>(Figure 6)                                                  | $V_{IS} = \frac{1}{2} (V_{CC} - V_{EE}),$<br>Ref & Test Attn = 10 dB<br>Source Amplitude = 0 dB                                                                                                                                                                                                                                                                              | 3.0<br>4.5<br>5.5<br>3.3 | 0.0<br>0.0<br>0.0<br>-3.3 | 80<br>80<br>80<br>80         | MHz              |

| V <sub>ISO</sub>  | Off–Channel Feedthrough Isolation (Figure 7)                                                                                 | $V_{IS} = \frac{1}{2} (V_{CC} - V_{EE}),$ Adjust Network Analyzer output to 10 dBm on each output from the power splitter                                                                                                                                                                                                                                                    | 3.0<br>4.5<br>5.5<br>3.3 | 0.0<br>0.0<br>0.0<br>-3.3 | -93<br>-93<br>-93<br>-93     | dB               |

| V <sub>ISOC</sub> | Common–Channel Feedthrough Isolation (Figure 8)                                                                              | V <sub>IS</sub> = ½ (V <sub>CC</sub> - V <sub>EE</sub> ),<br>Adjust Network Analyzer output to<br>10 dBm on each output from the power<br>splitter                                                                                                                                                                                                                           | 3.0<br>4.5<br>5.5<br>3.3 | 0.0<br>0.0<br>0.0<br>-3.3 | -93<br>-93<br>-93<br>-93     | dB               |

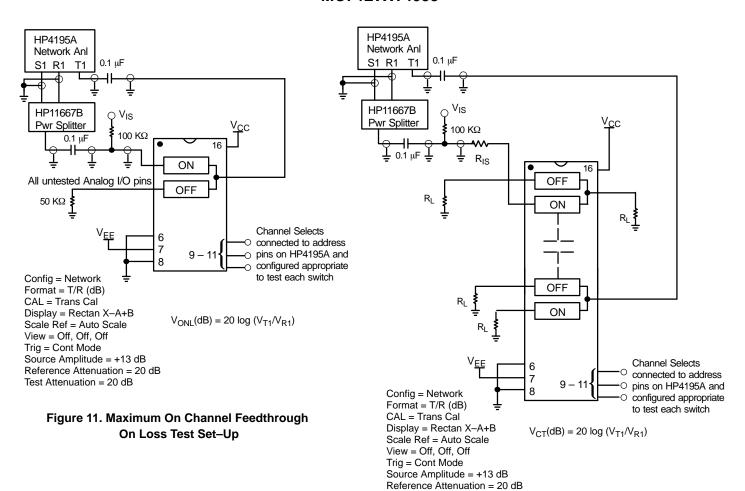

| V <sub>ONL</sub>  | Maximum Feedthrough On Loss (Figure 11)                                                                                      | $V_{IS} = \frac{1}{2} (V_{CC} - V_{EE}),$ Adjust Network Analyzer output to 10 dBm on each output from the power splitter                                                                                                                                                                                                                                                    | 3.0<br>4.5<br>5.5<br>3.3 | 0.0<br>0.0<br>0.0<br>-3.3 | -2<br>-2<br>-2<br>-2         | dB               |

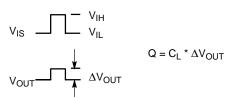

| Q                 | Feedthrough Noise. Channel–Select Input to Common I/O (Figure 9)                                                             | $V_{IN} = V_{CC}$ to $V_{EE}$ , $f_{IS} = 1$ MHz,<br>$t_r = t_f = 3$ ns<br>$R_{IS} = 600 \Omega$ , $C_L = 50$ pF                                                                                                                                                                                                                                                             | 3.0<br>4.5<br>5.5<br>3.3 | 0.0<br>0.0<br>0.0<br>-3.3 | 25<br>40<br>50<br>60         | mV <sub>PP</sub> |

|                   | Feedthrough Noise.<br>Channel–Select Input to Common I/O<br>(Figure 9)                                                       | $V_{IN} = V_{CC}$ to $V_{EE}$ , $f_{IS} = 1$ MHz,<br>$t_r = t_f = 3$ ns<br>$R_{IS} = 10 \Omega$ , $C_L = 10$ pF                                                                                                                                                                                                                                                              | 3.0<br>4.5<br>5.5<br>3.3 | 0.0<br>0.0<br>0.0<br>-3.3 | 35<br>40<br>50<br>60         |                  |

| Q                 | Feedthrough Noise.†<br>Enable Input to Common I/O<br>(Figure 10)                                                             | $\begin{aligned} V_{IN} &= V_{CC} \text{ to } V_{EE},  f_{IS} = 1 \text{ MHz}, \\ & t_r = t_f = 3 \text{ ns} \\ R_{IS} &= 0  \Omega,  C_L = 1000 \text{ pF}, \\ Q &= C_L * \Delta V_{OUT} \end{aligned}$                                                                                                                                                                     | 3.0<br>4.5<br>5.5<br>3.3 | 0.0<br>0.0<br>0.0<br>-3.3 | TBD<br>3.0<br>3.0<br>TBD     | pC               |

|                   | Feedthrough Noise.<br>Channel–Select Input to Common I/O<br>(Figure 9)                                                       | $\begin{aligned} V_{IN} &= V_{CC} \text{ to } V_{EE},  f_{IS} = 1 \text{ MHz}, \\ & t_r = t_f = 3 \text{ ns} \\ R_{IS} &= 0  \Omega,  C_L = 1000 \text{ pF}, \\ Q &= C_L * \Delta V_{OUT} \end{aligned}$                                                                                                                                                                     | 3.0<br>4.5<br>5.5<br>3.3 | 0.0<br>0.0<br>0.0<br>-3.3 | TBD<br>TBD<br>TBD<br>TBD     |                  |

| V <sub>CT</sub>   | Crosstalk Between Any Two Switches (Figure 12)                                                                               | $V_{IS} = \frac{1}{2} (V_{CC} - V_{EE}), f_{IS} = 100 \text{ kHz},$ $R_L = 50 \Omega$                                                                                                                                                                                                                                                                                        | 3.0<br>4.5<br>5.5<br>3.3 | 0.0<br>0.0<br>0.0<br>-3.3 | -96<br>-96<br>-96<br>-96     | dB               |

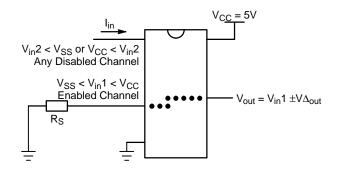

| V∆ <sub>OUT</sub> | Maximum Shift in Output Voltage of<br>Enabled Analog Channel due to injected<br>Current on a Disabled Channel<br>(Figure 17) | $\begin{split} I_{\text{IN}} & \ddagger \leq 1 \text{ mA, R}_{\text{S}} \leq 3.9 \text{ K}\Omega \\ I_{\text{IN}} & \ddagger \leq 10 \text{ mA, R}_{\text{S}} \leq 3.9 \text{ K}\Omega \\ I_{\text{IN}} & \ddagger \leq 1 \text{ mA, R}_{\text{S}} \leq 20 \text{ K}\Omega \\ I_{\text{IN}} & \ddagger \leq 10 \text{ mA, R}_{\text{S}} \leq 20 \text{ K}\Omega \end{split}$ | 5.0<br>5.0<br>5.0<br>5.0 | 0.0<br>0.0<br>0.0<br>0.0  | TBD<br>TBD<br>TBD<br>TBD     | mV               |

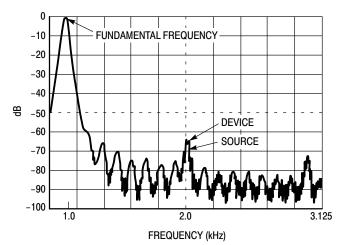

| THD               | Total Harmonic Distortion  THD = THD <sub>MEASURED</sub> – THD <sub>SOURCE</sub> (Figure 19)                                 | $\begin{split} f_{IS} = 1 \text{ MHz, } R_L = 10  K\Omega, C_L = 50 \text{ pF,} \\ V_{IS} = 2.5  V_{PP} \text{ sine wave} \\ V_{IS} = 4.0  V_{PP} \text{ sine wave} \\ V_{IS} = 5.0  V_{PP} \text{ sine wave} \\ V_{IS} = 6.0  V_{PP} \text{ sine wave} \end{split}$                                                                                                         | 3.0<br>4.5<br>5.5<br>3.3 | 0.0<br>0.0<br>0.0<br>-3.3 | 0.10<br>0.08<br>0.05<br>0.05 | %                |

<sup>\*</sup>Limits not tested. Determined by design and verified by qualification.

†Note: Some manufacturers may refer to this specification as Charge Injection.

<sup>‡</sup>Note: I<sub>IN</sub> = Total current injected into all disabled channels.

Figure 1a. Typical On Resistance,  $V_{CC}$  = 3.0 V,  $V_{EE}$  = 0V

Figure 1b. Typical On Resistance,  $V_{CC}$  = 4.5 V,  $V_{EE}$  = 0 V

Figure 1c. Typical On Resistance,  $V_{CC}$  = 5.5 V,  $V_{EE}$  = 0 V

Figure 2. On Resistance Test Set-Up

Figure 3. Maximum Off Channel Leakage Current,

Any One Channel, Test Set-Up

Figure 4. Maximum Off Channel Leakage Current, Common Channel, Test Set-Up

Figure 5. Maximum On Channel Leakage Current, Channel to Channel, Test Set-Up

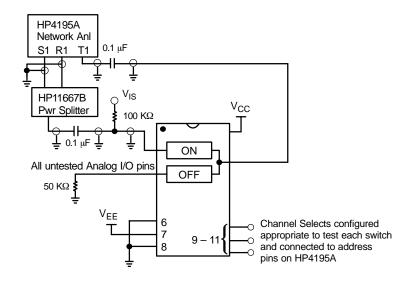

Figure 6. Maximum On Channel Bandwidth, Test Set-Up

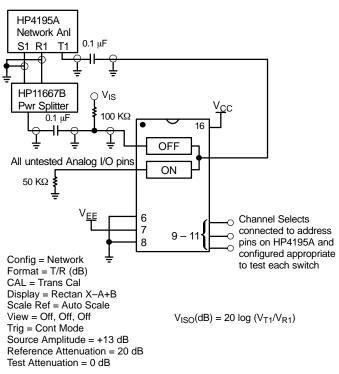

HP4195A Network Anl 0.1 μF S1 R1 T1 HP11667B  $V_{IS}$ Pwr Splitter <u>V\_c</u>c 100 KQ 0.1 μF 16 OFF ON 50 KΩ **\$** All untested Analog I/O pins  $50 \text{ K}\Omega$ **Channel Selects** connected to address 9 8 pins on HP4195A and configured appropriate to test each switch Config = Network Format = T/R (dB) CAL = Trans Cal Display = Rectan X-A+B Scale Ref = Auto Scale View = Off, Off, Off  $V_{ISOC}(dB) = 20 \log (V_{T1}/V_{R1})$ Trig = Cont Mode Source Amplitude = +13 dB Reference Attenuation = 20 dB Test Attenuation = 0 dB

Figure 7. Maximum Off Channel Feedthrough Isolation,Test Set-Up

Figure 8. Maximum Common–Channel Feedthrough Isolation Test Set–Up

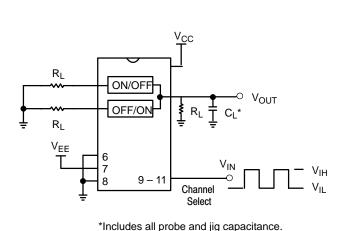

Figure 9. Feedthrough Noise, Channel Select to Common Out, Test Set-Up

\*Includes all probe and jig capacitance.

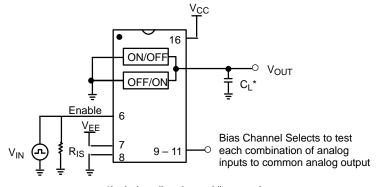

Figure 10. Feedthrough Noise, Enable to Common Out, Test Set-Up

Test Attenuation = 0 dB

Figure 12. Crosstalk Between Any Two Switches

Test Set-Up

Figure 13a. Break-Before-Make Test Set-Up

Figure 13b. Break-Before-Make Time

ANALOG I/O

OFF/ON

TEST

POINT

CL\*

CHANNEL SELECT

\*Includes all probe and jig capacitance

V<sub>CC</sub>

$V_{CC}$

Figure 14a. Propagation Delays, Channel Select to Analog Out

Figure 14b. Propagation Delay, Test Set-Up Channel Select to Analog Out

ANALOG I/O

ON

TEST

POINT

CL\*

TEST

POINT

\*Includes all probe and jig capacitance

Figure 15a. Propagation Delays, Analog In to Analog Out

$\rm V_{\rm CC}$ 90% **ENABLE** 50% 10% GND  $t_{PZL}$  $t_{PLZ}$ HIGH **IMPEDANCE ANALOG** 50% OUT 10%  $V_{OL}$  $t_{\text{PHZ}}$  $t_{PZH}$  $V_{OH}$ 90% **ANALOG** 50% OUT HIGH **IMPEDANCE**

Figure 16a. Propagation Delays, Enable to Analog Out

### Figure 15b. Propagation Delay, Test Set-Up Analog In to Analog Out

Figure 16b. Propagation Delay, Test Set-Up Enable to Analog Out

Figure 17. Maximum Shift in Output Voltage of Enabled Analog Channel due to Injected Current on a Disabled Channel Test Set-Up

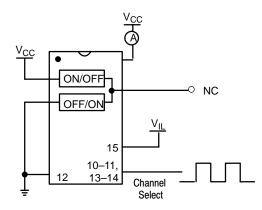

Figure 18. Power Dissipation Capacitance, Test Set-Up

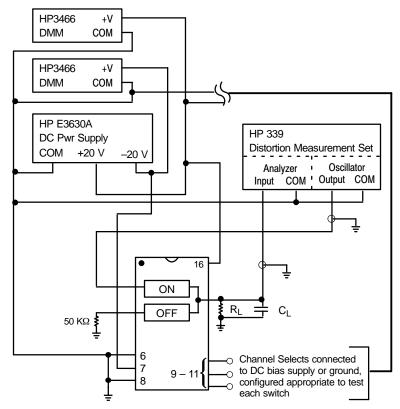

Figure 19a. Total Harmonic Distortion Test Set-Up

Figure 19b. Plot, Harmonic Distortion

#### **APPLICATIONS INFORMATION**

The Channel Select and Enable control pins should be at  $V_{CC}$  or GND logic levels.  $V_{CC}$  being recognized as a logic high and GND being recognized as a logic low. In this example:

$$V_{CC} = +5V = logic high$$

$GND = 0V = logic low$

The maximum analog voltage swing is determined by the supply voltages  $V_{CC}$  and  $V_{EE}$ . The positive peak analog voltage should not exceed  $V_{CC}$ . Similarly, the negative peak analog voltage should not go below  $V_{EE}$ . In this example, the difference between  $V_{CC}$  and  $V_{EE}$  is five volts. Therefore, using the configuration of Figure 15, a maximum analog signal of five volts peak–to–peak can be controlled. Unused analog inputs/outputs may be left floating (i.e., not connected). However, tying unused analog inputs and outputs to  $V_{CC}$  or

GND through a low value resistor helps minimize crosstalk and feedthrough noise that may be picked up by an unused switch.

Although used here, balanced supplies are not a requirement. The only constraints on the power supplies are that:

$$V_{EE}$$

– GND = 0 to –6 volts

$V_{CC}$  – GND = 2 to 6 volts

$V_{CC}$  –  $V_{EE}$  = 2 to 6 volts

and  $V_{EE}$  ≤ GND

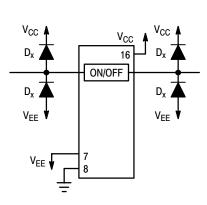

When voltage transients above  $V_{CC}$  and/or below  $V_{EE}$  are anticipated on the analog channels, external Germanium or Schottky diodes  $(D_x)$  are recommended as shown in Figure 16. These diodes should be able to absorb the maximum anticipated current surges during clipping.

Figure 20a. Application Example

Figure 21. External Germanium or Schottky Clipping Diodes

Figure 20b. Application Example

Figure 22. Function Diagram, LVX4053

#### PACKAGE DIMENSIONS

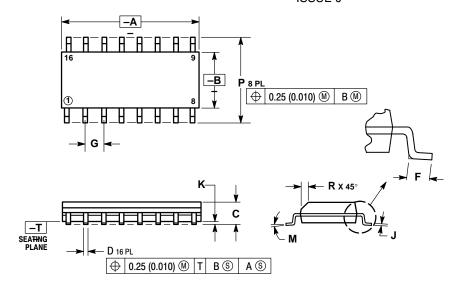

#### SOIC-16 **D SUFFIX** CASE 751B-05 **ISSUE J**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION. SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT

MAXIMUM MATERIAL CONDITION.

|     | MILLIM   | ETERS | INCHES |       |

|-----|----------|-------|--------|-------|

| DIM | MIN      | MAX   | MIN    | MAX   |

| Α   | 9.80     | 10.00 | 0.386  | 0.393 |

| В   | 3.80     | 4.00  | 0.150  | 0.157 |

| С   | 1.35     | 1.75  | 0.054  | 0.068 |

| D   | 0.35     | 0.49  | 0.014  | 0.019 |

| F   | 0.40     | 1.25  | 0.016  | 0.049 |

| G   | 1.27 BSC |       | 0.050  | BSC   |

| J   | 0.19     | 0.25  | 0.008  | 0.009 |

| K   | 0.10     | 0.25  | 0.004  | 0.009 |

| M   | 0°       | 7°    | 0°     | 7°    |

| P   | 5.80     | 6.20  | 0.229  | 0.244 |

| R   | 0.25     | 0.50  | 0.010  | 0.019 |

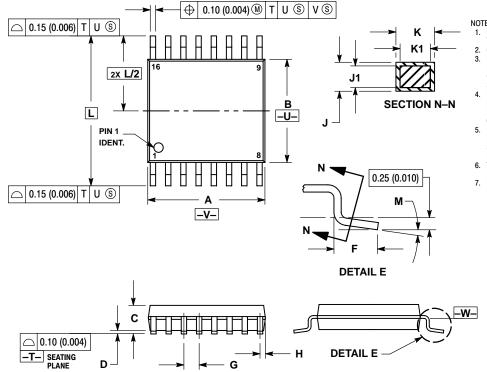

#### TSSOP-16 **DT SUFFIX** CASE 948F-01 **ISSUE O**

16X **K** REF

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A DOES NOT INCLUDE MOLD FLASH.

PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

- DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED

- PHOTHOSION SHALL NOT EXCEED

0.25 (0.010) PER SIDE.

DIMENSION K DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR PROTRUSION

SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K

DIMENSION AT MAXIMUM MATERIAL CONDITION.

TERMINAL NUMBERS ARE SHOWN FOR

- REFERENCE ONLY.

DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.

|     | MILLIN | IETERS   | INC       | HES   |  |

|-----|--------|----------|-----------|-------|--|

| DIM | MIN    | MAX      | MIN       | MAX   |  |

| Α   | 4.90   | 5.10     | 0.193     | 0.200 |  |

| В   | 4.30   | 4.50     | 0.169     | 0.177 |  |

| С   |        | 1.20     |           | 0.047 |  |

| D   | 0.05   | 0.15     | 0.002     | 0.006 |  |

| F   | 0.50   | 0.75     | 0.020     | 0.030 |  |

| G   | 0.65   | 0.65 BSC |           | BSC   |  |

| Н   | 0.18   | 0.28     | 0.007     | 0.011 |  |

| J   | 0.09   | 0.20     | 0.004     | 0.008 |  |

| J1  | 0.09   | 0.16     | 0.004     | 0.006 |  |

| K   | 0.19   | 0.30     | 0.007     | 0.012 |  |

| K1  | 0.19   | 0.25     | 0.007     | 0.010 |  |

| L   | 6.40   |          | 0.252 BSC |       |  |

| M   | 0°     | 8°       | 0°        | 8°    |  |

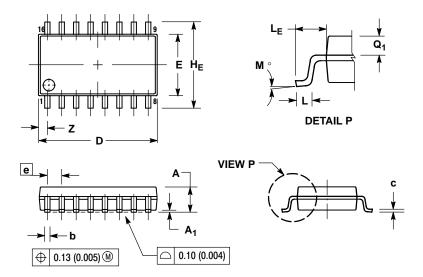

#### PACKAGE DIMENSIONS

#### SOIC EIAJ-16 M SUFFIX CASE 966-01 ISSUE O

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

- 2. DIMENSIONS D AND E DO NOT INCLUDE

MOLD FLASH OR PROTRUSIONS AND ARE

MEASURED AT THE PARTING LINE. MOLD FLASH

OR PROTRUSIONS SHALL NOT EXCEED 0.15

(0.006) PER SIDE.

- (0.006) PER SIDE.

4. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- S. THE LEAD WIDTH DIMENSION (b) DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. SHALL BE 0.88 (0.09) TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46 (0.018).

|                | MILLIMETERS |       | INCHES    |       |

|----------------|-------------|-------|-----------|-------|

| DIM            | MIN         | MAX   | MIN       | MAX   |

| Α              |             | 2.05  |           | 0.081 |

| A <sub>1</sub> | 0.05        | 0.20  | 0.002     | 0.008 |

| b              | 0.35        | 0.50  | 0.014     | 0.020 |

| С              | 0.18        | 0.27  | 0.007     | 0.011 |

| D              | 9.90        | 10.50 | 0.390     | 0.413 |

| E              | 5.10        | 5.45  | 0.201     | 0.215 |

| е              | 1.27 BSC    |       | 0.050 BSC |       |

| HE             | 7.40        | 8.20  | 0.291     | 0.323 |

| L              | 0.50        | 0.85  | 0.020     | 0.033 |

| LE             | 1.10        | 1.50  | 0.043     | 0.059 |

| M              | 0 °         | 10°   | 0 °       | 10 °  |

| $Q_1$          | 0.70        | 0.90  | 0.028     | 0.035 |

| Z              |             | 0.78  |           | 0.031 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor - European Support

German Phone: (+1) 303–308–7140 (Mon–Fri 2:30pm to 7:00pm CET)

Email: ONlit–german@hibbertco.com

French Phone: (+1) 303–308–7141 (Mon–Fri 2:00pm to 7:00pm CET)

Email: ONlit-french@hibbertco.com

English Phone: (+1) 303–308–7142 (Mon–Fri 12:00pm to 5:00pm GMT) Email: ONlit@hibbertco.com

EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781

\*Available from Germany, France, Italy, UK, Ireland

#### CENTRAL/SOUTH AMERICA:

**Spanish Phone**: 303–308–7143 (Mon–Fri 8:00am to 5:00pm MST)

Email: ONlit-spanish@hibbertco.com

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support

Phone: 303–675–2121 (Tue–Fri 9:00am to 1:00pm, Hong Kong Time)

Toll Free from Hong Kong & Singapore:

001–800–4422–3781 Email: ONlit–asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

**Phone**: 81–3–5740–2700 **Email**: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.